SMC Standard SMC-S-010 13 June 2008

-----

Supersedes: New issue

Air Force Space Command

# SPACE AND MISSILE SYSTEMS CENTER STANDARD

# PARTS, MATERIALS, AND PROCESSES TECHNICAL REQUIREMENTS FOR SPACE AND LAUNCH VEHICLES

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION IS UNLIMITED

# **FOREWORD**

- 1. This standard defines the Government's requirements and expectations for contractor performance in defense system acquisitions and technology developments.

- 2. This new-issue SMC standard comprises the text of The Aerospace Corporation report number TOR-2006(8583)-5236.

- 3. Beneficial comments (recommendations, changes, additions, deletions, etc.) and any pertinent data that may be of use in improving this standard should be forwarded to the following addressee using the Standardization Document Improvement Proposal appearing at the end of this document or by letter:

Division Chief, SMC/EAE SPACE AND MISSILE SYSTEMS CENTER Air Force Space Command 483 N. Aviation Blvd. El Segundo, CA 90245

4. This standard has been approved for use on all Space and Missile Systems Center/Air Force Program Executive Office - Space development, acquisition, and sustainment contracts.

James Horejsi, Col, USAF SMC Chief Engineer

# **Table of Contents**

| 1 Scope                                      | 1  |

|----------------------------------------------|----|

| 1.1. Purpose                                 |    |

| 1.2. Baseline Performance                    |    |

| 1.3. Quality                                 |    |

| 1.4. Order of precedence.                    |    |

| 1.5. Application Of The Document             |    |

| 1.6. PMP Management                          |    |

| 2 Referenced Documents                       |    |

|                                              |    |

| 2.1. Referenced Documents                    |    |

| 2.1.1 Government Documents.                  |    |

| 2.1.2 Non-government Documents.              |    |

| 2.1.3 Order Of Precedence                    | 11 |

| 3 Definitions                                | 13 |

| 4 General Requirements                       | 17 |

| 4.1. Application Requirements                | 17 |

| 4.1.1 Electrical Derating.                   | 17 |

| 4.1.2 Mechanical Derating.                   | 18 |

| 4.1.3 End-of-Life.                           | 18 |

| 4.1.4 Aging Sensitivity.                     | 18 |

| 4.1.5 Sealed Packages                        | 19 |

| 4.1.6 Registered PMP                         | 19 |

| 4.1.7 Handling.                              | 19 |

| 4.1.8 Marking                                | 19 |

| 4.1.9 Outgassing Requirements.               | 19 |

| 4.1.10 Alternate QCI Test/Sampling Plan      | 19 |

| 4.2. Part Requirements                       |    |

| 4.2.1 New Technology Insertion Requirements. |    |

| 4.2.2 Suppliers of Class S/V/K/JANS/T-Level Passives.                                  | 20 |

|----------------------------------------------------------------------------------------|----|

| 4.2.3 Parts and Materials Transfer                                                     | 20 |

| 4.3. Part Design and Construction                                                      | 20 |

| 4.3.1 Design                                                                           | 20 |

| 4.3.2 Material Hazards                                                                 | 20 |

| 4.3.3 Surface Finishes and Solder Attachments                                          | 20 |

| 4.3.4 Processes and Controls.                                                          | 21 |

| 4.3.5 Rework During Manufacture of Electronic Parts.                                   | 21 |

| 4.4. Part Quality Assurance Provisions.                                                | 21 |

| 4.4.1 In-Process Controls.                                                             | 21 |

| 4.4.2 Screening (100 Percent).                                                         | 21 |

| 4.4.3 Lot Conformance Tests (or Quality Conformance Inspection).                       | 21 |

| 4.4.4 Destructive Physical Analysis (DPA).                                             | 21 |

| 4.4.5 Qualification Tests.                                                             | 22 |

| 4.5. Material Quality Assurance Provisions.                                            | 22 |

| 4.5.1 In-Process Controls.                                                             | 22 |

| 4.5.2 Screening (100 Percent).                                                         | 22 |

| 4.5.3 Lot Conformance Tests (or Quality Conformance Inspection): Sampling or Periodic. | 22 |

| 4.5.4 Qualification Tests.                                                             | 22 |

| 4.6. Packaging                                                                         | 22 |

| 4.7. Electrostatic-Sensitive Items.                                                    | 22 |

| 4.8. Data and Record Retention.                                                        | 22 |

| 5 Detailed Requirements                                                                | 23 |

| Section 100 Boards, Printed Wiring                                                     | 25 |

| Section 110 Flex and Rigid-Flex Printed Wiring Boards                                  | 30 |

| Section 120 RF (Microwave) Boards, Printed Wiring                                      | 35 |

| Section 200 Capacitors, General                                                                                                                  | 40  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Section 210 Ceramic Capacitors (MIL-PRF-123)                                                                                                     | 42  |

| Section 215 Ceramic Capacitors, High Voltage (HVR) (MIL-PRF-49467)                                                                               | 44  |

| Section 216 Stacked Ceramic Capacitors (SM) (MIL-PRF-49470, T-Level)                                                                             | 47  |

| Section 217 Ceramic Capacitor Arrays for Filter Connectors                                                                                       | 49  |

| Section 230 Metallized Film Capacitors (CRH) (MIL-PRF-83421)                                                                                     | 52  |

| Section 232 Metallized Film Capacitors (CHS) (MIL-PRF-87217)                                                                                     | 55  |

| Section 240 Glass Dielectric Capacitors (CYR) (MIL-PRF-23269)                                                                                    | 57  |

| Section 250 Fixed Mica Capacitors (CMS) (MIL-PRF-87164)                                                                                          | 59  |

| Section 255 Fixed, High-Voltage, Reconstituted Mica Capacitors                                                                                   | 61  |

| Section 260 Fixed Tantalum Foil Capacitors (CLR 25, 27, 35, and 37) (MIL-PRF-39006)                                                              | 64  |

| Section 270 Solid Tantalum Capacitors (CSS) (MIL-PRF-39003/10)                                                                                   | 67  |

| Section 275 Solid Tantalum Chip Capacitors (CWR) (MIL-PRF-55365)                                                                                 | 69  |

| Section 280 Fixed Tantalum-Tantalum Capacitor, Sintered Wet Slug, Tantalum Case (CLR79, CLR81, CLR90 & CLR91) (MIL-PRF-39006/22, /25, /30 & /31) |     |

| Section 300 Connectors                                                                                                                           | 76  |

| Section 310 Connectors, Filtered                                                                                                                 | 83  |

| Section 400 Quartz bulk acoustical wave components (Quartz Crystals & Quartz Hybrid Crystal Oscillators)                                         | 86  |

| Section 500 Diodes                                                                                                                               | 98  |

| Section 600 EMI and RFI Filters (FS) (MIL-PRF-28861, Class S)                                                                                    | 99  |

| Section 700 Fuses                                                                                                                                | 102 |

| Section 800 Magnetic Devices (MIL-STD-981)                                                                                                       | 109 |

| Section 900 Microcircuits                                                                                                                        | 112 |

| Section 910 Integrated Circuits                                                                                                                  | 125 |

| Section 920 Programmable Microelectronic Devices                                                                                                 | 126 |

| Section 960 Hybrids (MIL-PRF-38534, Class K)                                                                                                     | 127 |

| Section 1000 Relays (Current Ratings of 25 Amperes or Less)                                                                                      | 136 |

| Section 1100 Resistors                                                                                                                           | 142 |

| Section 1110 Fixed Composition, Insulated, Carbon Composition (RCR) (MIL-R-39008)               | 145 |

|-------------------------------------------------------------------------------------------------|-----|

| Section 1120 Fixed Film Resistors (RLR) (MIL-PRF-39017)                                         | 147 |

| Section 1125 Fixed Film Resistor Chips (RM) (MIL-PRF-55342, T-Level and MIL-PRF-32159, T-Level) | 150 |

| Section 1130 Fixed Metal Film Resistors (RNC/RNR) (MIL-PRF-55182, T-level)                      | 152 |

| Section 1140 Variable, Nonwire-Wound Resistors (RJR) (MIL-PRF-39035)                            | 154 |

| Section 1150 Variable, Wire-Wound Resistors (RTR) (MIL-PRF-39015)                               | 157 |

| Section 1160 Wire-Wound, Accurate, Resistors (RBR) (MIL-PRF-39005)                              | 161 |

| Section 1170 Wire-Wound, Power-Type Resistors (RWR) (MIL-PRF-39007)                             | 165 |

| Section 1180 Wire-Wound, Chassis-Mounted Resistors (RER) (MIL-PRF-39009)                        | 171 |

| Section 1190 Fixed Film Resistor Network (Rz) (MIL-PRF-83401)                                   | 173 |

| Section 1195 Thermistors (RTH) (MIL-PRF-23648 and MIL-PRF-32192)                                | 179 |

| Section 1200 Switches                                                                           | 183 |

| Section 1210 Sensitive And Push (Snap Action) Switches (MIL-PRF-8805)                           | 186 |

| Section 1220 Thermal Switches (MIL-PRF-24236)                                                   | 188 |

| Section 1230 Pressure Switches (MIL-DTL-9395)                                                   | 194 |

| Section 1300 Active RF and Microwave Devices                                                    | 197 |

| Section 1350 Surface Acoustical Wave Devices                                                    | 220 |

| Section 1360 Coaxial ceramic resonators                                                         | 226 |

| Section 1400 Semiconductors                                                                     | 233 |

| Section 1500 Wire and Cable                                                                     | 239 |

| Section 1600 Photonics                                                                          | 242 |

| Section 1700 Mechanical Piece Parts                                                             | 257 |

| Section 2000 Materials Requirements                                                             | 259 |

| Section 2100 Metals                                                                             | 260 |

| Section 2110 Aluminum and Aluminum Alloys                                                       | 262 |

| Section 2120 Beryllium                                                                          | 263 |

| Section 2130 Magnesium                                                                          | 264 |

| Section 2140 Mercury                                       | 265 |

|------------------------------------------------------------|-----|

| Section 2150 Steels                                        | 266 |

| Section 2160 Titanium                                      | 268 |

| Section 2170 Other Metals                                  | 270 |

| Section 2200 Nonmetals                                     | 271 |

| Section 2210 Elastomers                                    | 272 |

| Section 2220 Foamed Plastics                               | 273 |

| Section 2230 Lubricants                                    | 274 |

| Section 2240 Adhesives, Sealants, Coatings, & Encapsulants | 275 |

| Section 2250 Composites                                    | 276 |

| Section 2260 Glasses and Ceramics                          | 277 |

| Section 2300 Sandwich Assemblies                           | 278 |

| Section 3000 Processes                                     | 279 |

| Section 3100 Adhesive Bonding                              | 280 |

| Section 3200 Welding                                       | 281 |

| Section 3300 Brazing                                       | 282 |

| Section 3400 Fastener Installation                         | 283 |

| Section 3500 Printed Circuit Assembly                      | 284 |

|                                                            |     |

# **APPENDICES**

| Appendix A Radiation Hardness Assurance Requirements                                       | 286 |

|--------------------------------------------------------------------------------------------|-----|

| A.1. Scope                                                                                 | 286 |

| A.2. Referenced Documents                                                                  | 286 |

| A.3. Environments                                                                          | 286 |

| A.3.1 Radiation Environments.                                                              | 286 |

| A.3.2 Radiation Design Margin (R <sub>DM</sub> ).                                          | 287 |

| A.4. Design Requirements And Characterization                                              | 287 |

| A.4.1 Neutron/Proton Induced Displacement Damage (DD) and Total Ionizing Dose (TID) Damage | 287 |

| A.4.2 Part Selection Criteria.                                                             | 287 |

| A.4.2.1 Characterization Test.                                                             | 287 |

| A.4.2.2 Derivation of Radiation Degradation Limits for TID and/or Neutron                  | 288 |

| A.4.2.2.1 Standard Normal Distribution                                                     | 288 |

| A.4.2.2.2 Log Normal Distribution.                                                         | 288 |

| A.4.2.2.3 Combining Neutron and TID Damage                                                 | 289 |

| A.4.2.2.4 Applicability and Exceptions.                                                    | 289 |

| A.4.3 Single Event Effects (SEE) and Prompt Dose.                                          | 289 |

| A.4.3.1 SEE Characterization Test.                                                         | 289 |

| A.4.3.2 Prompt Dose Upset and Survival Characterization Test                               | 289 |

| A.5. Production Acceptance Test                                                            | 290 |

| A.5.1 Radiation Wafer Lot Acceptance Testing (RWLAT).                                      | 290 |

| A.5.2 Conditions for exemption from RWLAT.                                                 | 290 |

| A.5.3 Non-QML/RHA hybrids                                                                  | 290 |

| A.5.4 PMP Hardness Assurance Program Plan.                                                 | 291 |

| A.5.5 Test Documentation.                                                                  | 291 |

| A.6. Materials Selection.                                                                  | 291 |

| Appendix B Rescreening/Quality Conformance Inspection Requirements                         | 292 |

| B.1. Scope                                                                                 | 292 |

| B.2. Application.                                                          | 292 |

|----------------------------------------------------------------------------|-----|

| B.3. Class B/QML Q Microciruit Upscreening/Lot Acceptance Testing.         | 292 |

| B.4. Class H Hybrid Upscreening/Lot Acceptance Testing                     | 292 |

| B.5. JANTXV Transistor And Diode Upscreening/Lot Acceptance Testing.       | 292 |

| Appendix C Alternate QCI Test/Sampling Plan                                | 303 |

| C.1. Scope.                                                                | 303 |

| C.2. Application.                                                          | 303 |

| C.2.1 Supplier.                                                            | 303 |

| C.2.2 Product                                                              | 303 |

| C.2.3 Microcircuits per MIL-PRF-38535                                      | 303 |

| C.2.3.1 Reduced Group B Sample Size                                        | 303 |

| C.2.3.2 Reduced Group D Sample Size.                                       | 303 |

| C.2.4 Diodes and Transistors per MIL-PRF-19500.                            | 303 |

| C.2.4.1 Reduced Group B Sample Size                                        | 303 |

| C.2.4.2 Reduced Group C Sample Size.                                       | 304 |

| Appendix D Notes                                                           | 308 |

| D.1. Intended Use.                                                         | 308 |

| D.2. Tailoring                                                             | 308 |

| D.2.1 Tailored Application                                                 | 308 |

| D.2.2 Tailoring To Contract Phase.                                         | 309 |

| D.2.3 Tailoring Part Specifications.                                       | 309 |

| D.3. Data Items.                                                           | 309 |

| Appendix E EEEE Parts Risk Assessment Matrix for Space Flight Applications | 310 |

# TABLE OF FIGURES

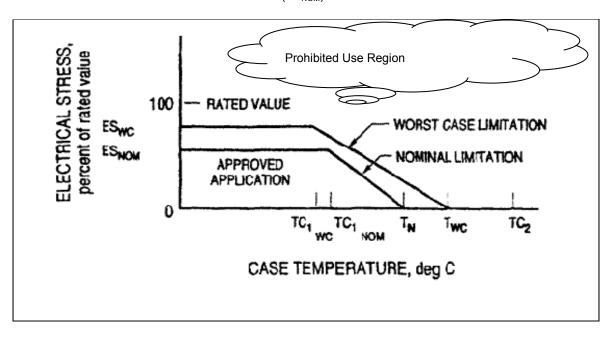

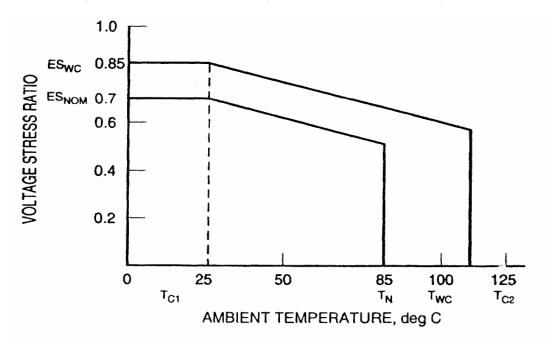

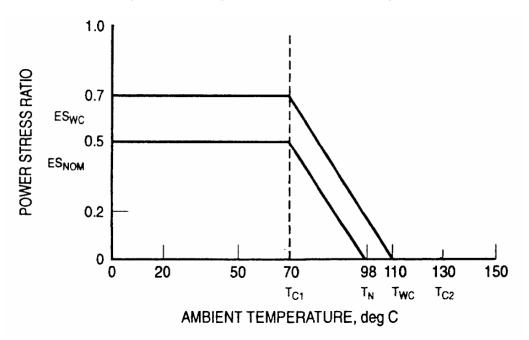

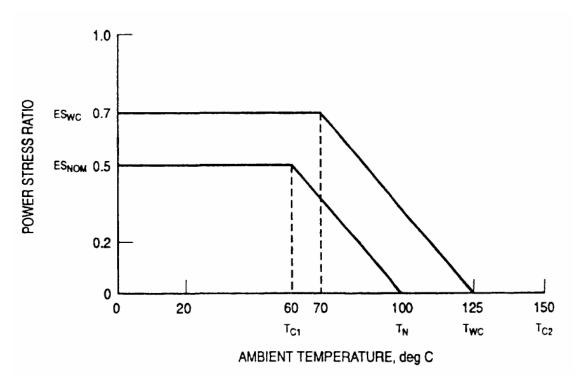

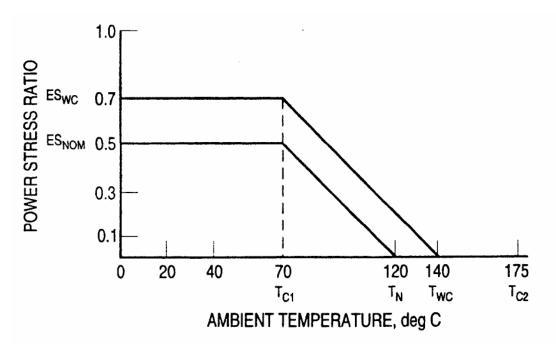

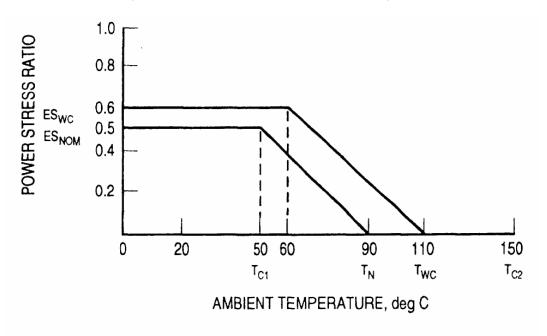

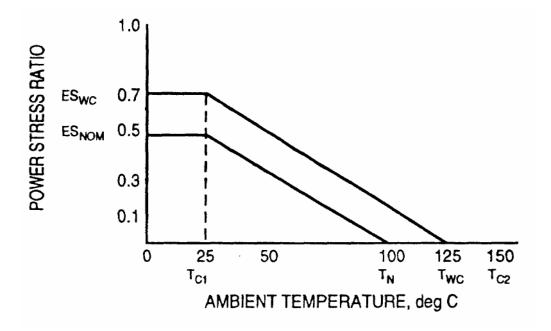

| FIGURE 4-1. Typical Electrical Stress vs Temperature Derating Scheme                                               | 17  |

|--------------------------------------------------------------------------------------------------------------------|-----|

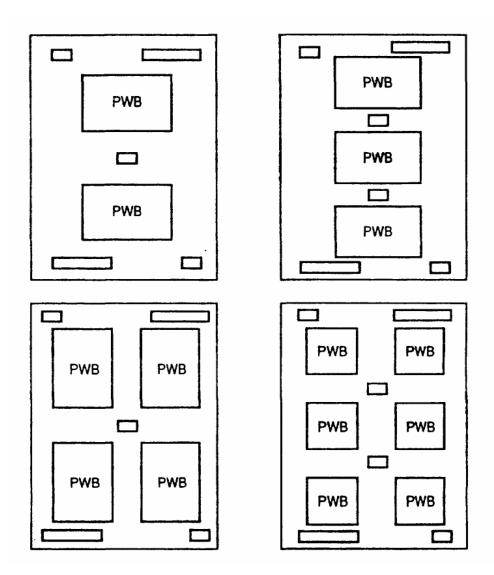

| FIGURE 100-1 Deliverable Coupon Placement                                                                          | 29  |

| FIGURE 240-1. Voltage Derating for Glass Capacitors                                                                | 57  |

| FIGURE 250-1. Voltage Derating for Mica Capacitors                                                                 | 59  |

| FIGURE 260-1. Voltage Derating for Tantalum-Foil Capacitors                                                        | 64  |

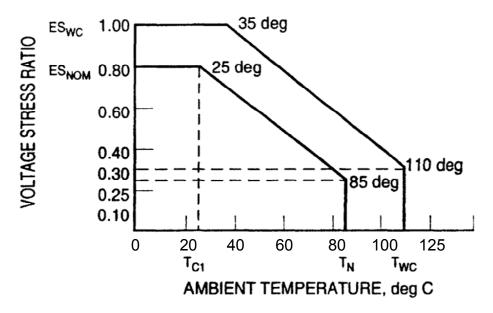

| FIGURE 270-1 Voltage Derating for Solid Tantalum Capacitors                                                        | 67  |

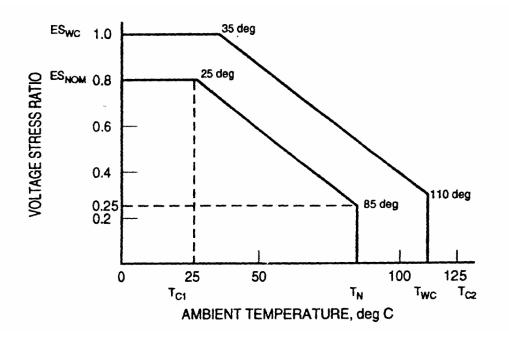

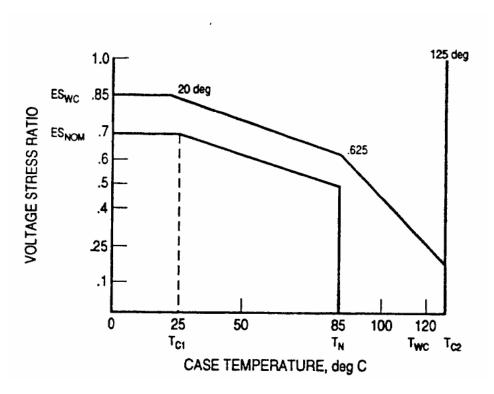

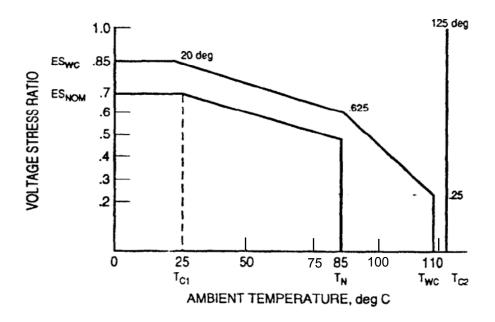

| FIGURE 280-1. Voltage Derating for Tantalum-Tantalum (Sintered Wet Slug) Capacitor                                 | 72  |

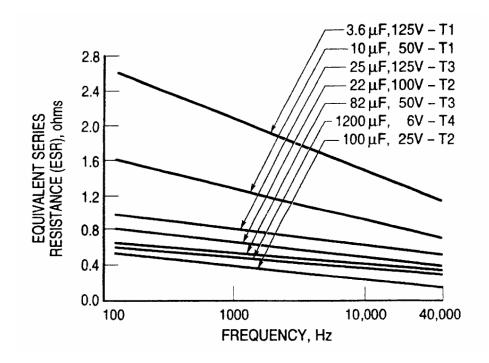

| FIGURE 280-2. ESR versus AC Frequency                                                                              | 73  |

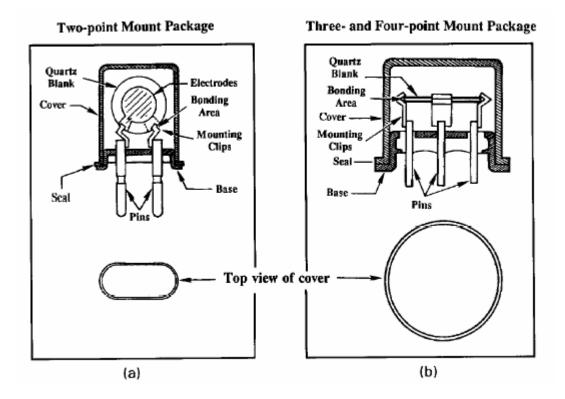

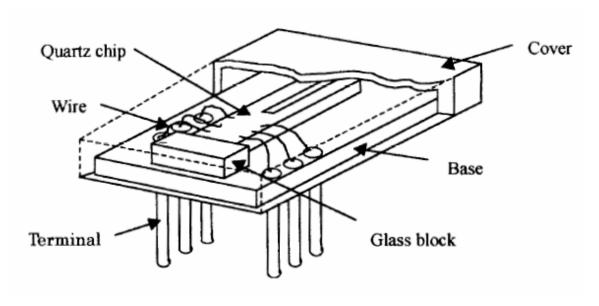

| FIGURE 400-1 Typical Mounting Structures                                                                           | 88  |

| FIGURE 400-2 Typical Cantilever Mount                                                                              | 89  |

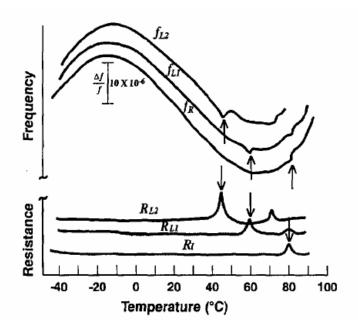

| FIGURE 400-3 Activity Dips vs Temperature                                                                          | 94  |

| FIGURE 1110-1. Power Derating for Carbon Composition Resistors                                                     | 145 |

| FIGURE 1120-1. Power Derating for Film Resistors                                                                   | 147 |

| FIGURE 1130-1. Power Derating for Metal Film Resistors                                                             | 152 |

| FIGURE 1140-1. Power Derating for variable, Non-wirewound Resistors.                                               | 154 |

| FIGURE 1150-1. Power Derating Requirements for Variable, Wire-wound Resistors                                      | 157 |

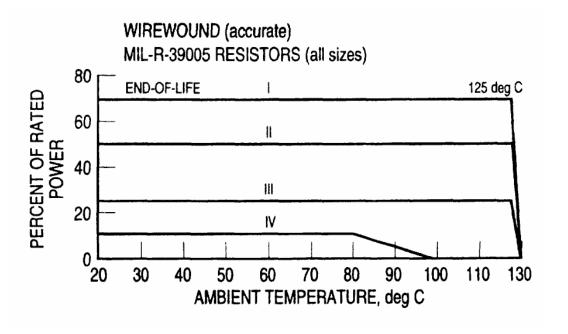

| FIGURE 1160-1. High Temperature Derating Curves for Accurate Wire-wound Resistors                                  | 161 |

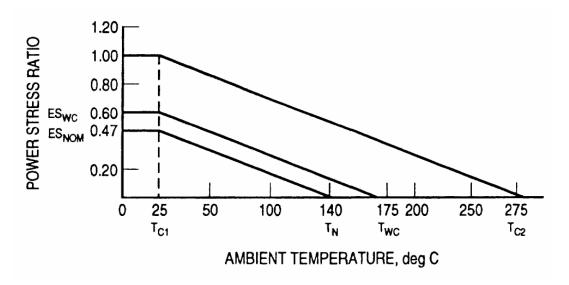

| FIGURE 1170-1. Power Derating Requirements for Wire-wound (Power-type) Resistors                                   | 165 |

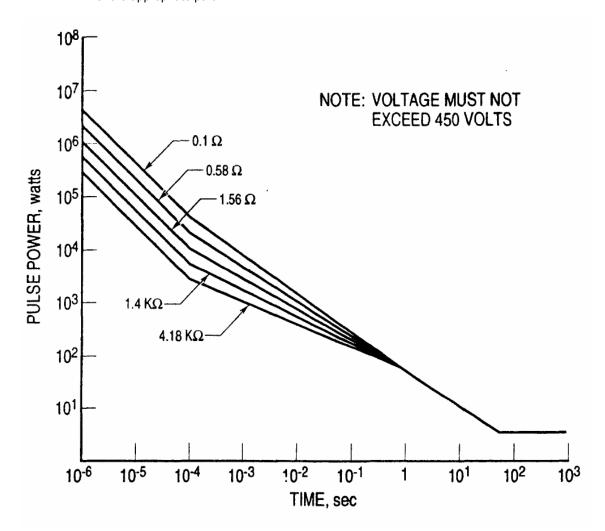

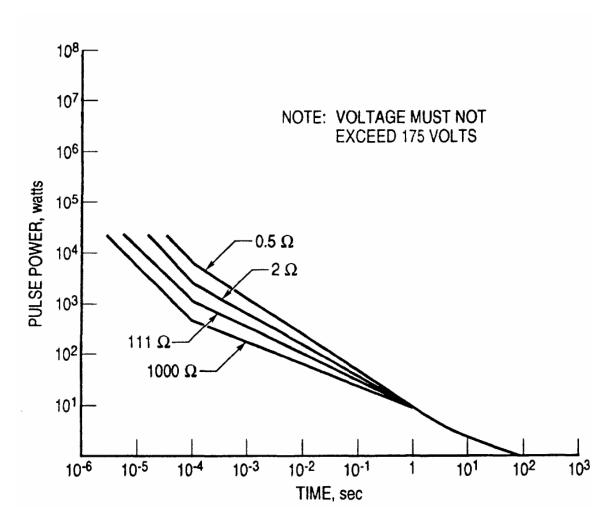

| FIGURE 1170-2. Typical Maximum Pulse Power versus Time for RWR 81 (1-watt) Resistors                               | 166 |

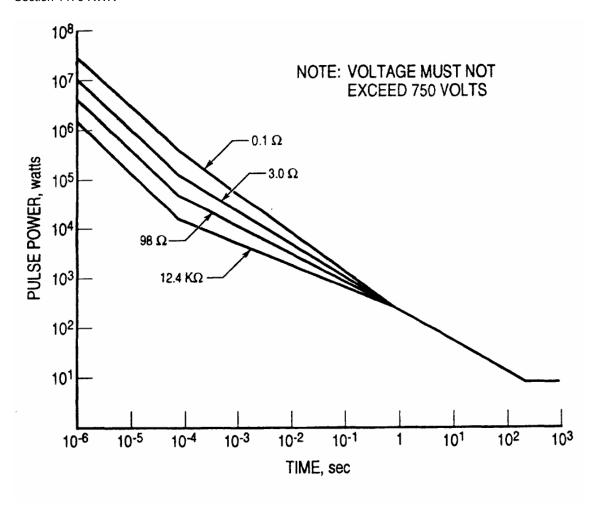

| FIGURE 1170-3. Typical Maximum Pulse Power versus Time for RWR 89 (3-watt) Resistors                               | 167 |

| FIGURE 1170-4. Typical Maximum Pulse Power versus Time for RWR 84 (7-watt) Resistors                               | 168 |

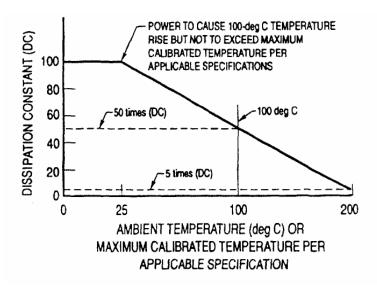

| FIGURE 1195-1 Derating Curve for Negative Coefficient Thermistors                                                  | 179 |

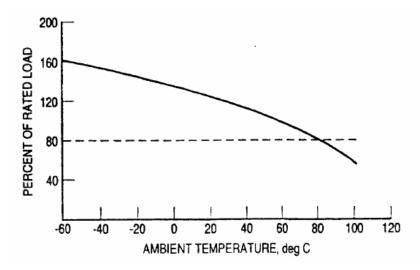

| FIGURE 1200-1. Switch Current Rating versus Temperature for a Typical Switch (not applicable for Thermostat type). |     |

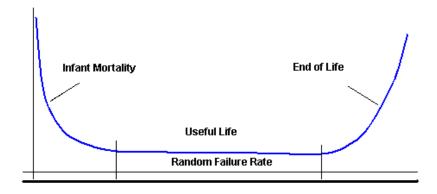

| FIGURE 1300-1 LIFTIME (BATHTUB) CURVE                                                                              | 207 |

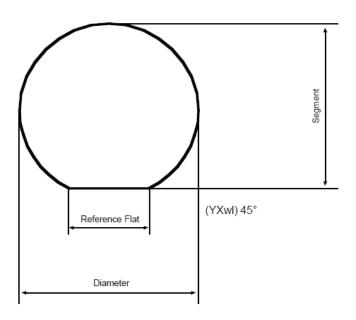

| FIGURE 1350-1. Wafer Requirements                                                                                  | 222 |

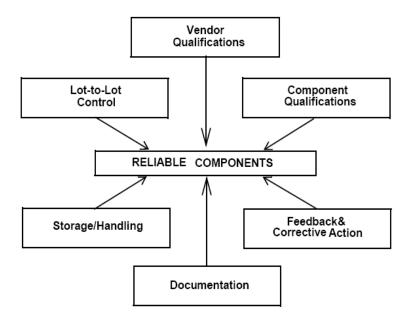

| FIGURE 1600-1. Reliability assurance program elements                                                              | 244 |

# TABLE OF TABLES

| Table 200-1. Capacitor Styles Included in Section 200                               | 40  |

|-------------------------------------------------------------------------------------|-----|

| Table 215-1 Modifications to Group A of MIL-PRF-49467                               | 45  |

| Table 215-2 Additions and Modifications to Group B of MIL-PRF-49467                 | 46  |

| Table 217-I - Group A Requirements                                                  | 50  |

| Table 217-II - Group B Requirements                                                 | 51  |

| Table 230-1. 100 Percent Screening Requirements                                     | 54  |

| Table 255-I - Group A Requirements                                                  | 62  |

| Table 255-la - Burn-in Test Voltage                                                 | 63  |

| Table 255-II - Group B Requirements                                                 | 63  |

| Table 260-1. Additions and Modifications to Group A for Tantalum Foil Capacitors    | 66  |

| Table 260-2 Group B Tests for Tantalum Foil Capacitors                              | 66  |

| Table 275-1. Surge Voltage Ratings                                                  | 69  |

| Table 280-1. Group A for Wet Tantalum Slug Capacitors                               | 74  |

| Table 280-2. Group B Tests of MIL-PRF-39006                                         | 75  |

| Table 310-I - Group A Requirements for EMI Filter Connectors with Ceramic Arrays    | 85  |

| Table 400-1 "As Grown" Quartz Bars Nondestructive Screening                         | 90  |

| Table 400-2 "As Grown" Quartz Bars Destructive Screening                            | 90  |

| Table 400-3 Inspection For Packaged Quartz Bulk Acoustical Wave Components          | 92  |

| Table 700-1 Fuse Derating in Vacuum at +25°C                                        | 103 |

| Table 700-2. 100 Percent Screening Requirements for Hollow Body, Wire Element Fuses | 106 |

| Table 700-3 Chip Fuse Group B Testing                                               | 107 |

| Table 800-1. Additions to Group B Lot Conformance                                   | 111 |

| Table 900-1 Digital Microcircuits Derating                                          | 113 |

| Table 900-2 Linear Microcircuits Derating                                           | 114 |

| Table 900-3 Linear Voltage Regulator Microcircuit Derating                          | 114 |

| Table 900-4 Electron-Migration Failure Mechanism                                    | 118 |

| Table 900-5 Corrosion Failure Mechanism                                             | 119 |

| Table 900-6 Time-Dependence Dielectric Breakdown (TDDB) Failure Mechanism                        | 120 |

|--------------------------------------------------------------------------------------------------|-----|

| Table 960-1. Microcircuit die evaluation requirements.                                           | 130 |

| Table 960-2. Semiconductor die evaluation requirements.                                          | 132 |

| Table 960-3. MIL-PRF-38534 Element Evaluation Requirements for Passive Parts                     | 134 |

| Table 1000-1 Contact Current Derating                                                            | 137 |

| Table 1000-2. 100 Percent Screening Requirements                                                 | 141 |

| Table 1100-1 Resistor Types                                                                      | 142 |

| Table 1120-2. Group A Tests for RLR Style Fixed Film Resistors                                   | 149 |

| Table 1140-1. Additions and Modifications to Group A Tests for Variable, Non-wirewound Resistors | 156 |

| Table 1150-1. MIL-STD-199 Rated Voltages                                                         | 158 |

| Table 1150-2. Group A Tests for Variable, Wire-wound Resistors                                   | 160 |

| Table 1160-1 Resistance Tolerance and Required Derating                                          | 163 |

| Table 1160-2 Group A Tests for Fixed, Wire-wound, Accurate Resistors                             | 164 |

| Table 1170-1. Group A Tests for Wire-wound (Power Type) Resistors                                | 170 |

| Table 1180-1. Group A Tests for Wire-wound, Power-type, Chassis-mounted Resistors                | 172 |

| Table 1190-1. Manufacturer's Element Power, Network Power, and Voltage Ratings                   | 174 |

| Table 1190-2 100% Group A Tests for Fixed-film Resistor Networks                                 | 178 |

| Table 1195-2. Additions to Group B Tests for Thermistors                                         | 182 |

| Table 1200-1 Switch Types                                                                        | 183 |

| Table 1210-1. 100 Percent Screening Requirements                                                 | 187 |

| Table 1220-1. 100 Percent Screening Requirements for Thermal Switches                            | 190 |

| Table 1230-1. 100 Percent Screening Requirements for Pressure Switches                           | 195 |

| Table 1230-2. Lot Conformance Tests for Pressure Switches                                        | 196 |

| Table 1300-1. DERATING FACTORS FOR TRANSISTORS                                                   | 198 |

| Table 1300-2. DERATING FACTORS FOR MMICS                                                         | 200 |

| Table 1300-3I. DERATING FACTORS FOR IMPATTS                                                      | 201 |

| Table 1300-3G. DERATING FACTORS FOR GUNNs                                                        | 201 |

| Table 1300-4 – Quality Assurance                                                                         | 202 |

|----------------------------------------------------------------------------------------------------------|-----|

| Table 1300-5. WAFER FABRICATION                                                                          | 204 |

| Table 1300-6. ASSEMBLY                                                                                   | 205 |

| Table 1300-7. SCREENING                                                                                  | 206 |

| Table 1300-8. QUALITY CONFORMANCE INSPECTION                                                             | 208 |

| Table 1300-9. FAILURE MECHANISMS FOR ACTIVE RF DEVICES                                                   | 209 |

| Table 1300-10. RECOMMENDED ELECTRICAL PARAMETERS                                                         | 211 |

| Table 1300-11. RELIABILITY SUSPECT PARTS                                                                 | 215 |

| Table 1300-12. Electrical Test Criteria for Radio Frequency and Microwave Transistors                    | 218 |

| Table 1400-1. Derating Factors for Transistors                                                           | 234 |

| Table 1400-2. Derating Guidelines for Diodes                                                             | 235 |

| Table 1600-1 General Derating Criteria                                                                   | 243 |

| Table 1600-2 Screening Plan for Packaged Devices                                                         | 247 |

| Table 1600-3A. Conformance inspection (CI) and periodic inspection (PI) for packaged laser devices       | 249 |

| Table 1600-3B. Conformance inspection (CI) and periodic inspection (PI) FOR PACKAGED LASER DEVICES       | 250 |

| Table 1600-3C Special Requirements for fiber pigtailed and connectorized PACKAGED devices                | 251 |

| Table 1600-4A. Typical Electro/Optical Characterization Tests for Laser Diodes. **                       | 253 |

| Table 1600-4B. Typical Electro/Optical Characterization Tests for Laser Modules. *                       | 254 |

| Table 1600-4C. Typical Electro/Optical Characterization Tests for LEDs. **                               | 255 |

| Table 1600-4D. Typical Electro/Optical Characterization Tests for Photodiodes. **                        | 255 |

| Table 1600-5 MTBF Calculation Example                                                                    | 256 |

| Table A-1.RWLAT Methods                                                                                  | 290 |

| Table B-1a. MIL-PRF-38535 Class B/QML Q Microcircuit Upscreening (Test 100%), Test Methods of MIL-STD-8  |     |

| Table B-1b. MIL-PRF-38535 Class B/QML Q Microcircuit Lot Acceptance Testing, (Sample as Specified), Test | 292 |

| Methods of MIL-STD-883                                                                                   | 294 |

| Table B-1c. MIL-PRF-38535 Class B/QML Q Microcircuit Destructive Physical Analysis (DPA)                 | 295 |

| Table B-2a. MIL-PRF-38534 Class H Hybrid Upscreening (Test 100%), Test Methods of MIL-STD-883            | 296 |

| Table B-2b. MIL-PRF-38534 Class H Hybrid Lot Acceptance Testing, (Sample as Specified), Test Methods of STD-883                  |     |

|----------------------------------------------------------------------------------------------------------------------------------|-----|

| Table B-2c. MIL-PRF-38534 Class H Hybrid Destructive Physical Analysis (DPA)                                                     | 298 |

| Table B-3a. MIL-PRF-19500 JANTXV Transistor and Diode Upscreening (Test 100%), Test Methods of MIL-S                             |     |

| Table B-3b MIL-PRF-19500 JANTXV Transistor and Diode Lot Acceptance Testing, (Sample as Specified), Te<br>Methods of MIL-STD-750 |     |

| Table B-3c. MIL-PRF-19500 JANTXV Transistor and Diode Destructive Physical Analysis (DPA)                                        | 302 |

| Table C-1 Reduced Group B Sample Size                                                                                            | 304 |

| Table C-2. Reduced Group D Sample Size 1/                                                                                        | 306 |

#### 1 SCOPE

- 1.1. PURPOSE. This document establishes the minimum technical requirements for electronic parts, materials, and processes (electronic PMP) used in the design, development, and fabrication of space and launch vehicles. Application information, design and construction information, and quality assurance provisions are provided herein. All electronic PMP selected for use in space and launch vehicles shall meet the requirements specified herein, unless otherwise approved by the program. Either the contractor or its subcontractors may accomplish these requirements. However, the prime contractor has the responsibility for ensuring all requirements are met.

- 1.2. BASELINE PERFORMANCE. This document establishes the baseline performance requirements for electronic PMP and the quality and reliability assurance requirements, which must be met for their acquisition. Detailed requirements, specific characteristics of electronic PMP, and other provisions which are sensitive to the particular intended use will be specified within the device specification.

- 1.3. QUALITY.Quality assurance requirements outlined herein are for all electronic PMP built or performed on a manufacturing line that is controlled through a manufacturer's Quality Management (QM). Several levels of product assurance including Radiation Hardness Assurance (RHA) are provided for in this specification.

- 1.4. ORDER OF PRECEDENCE. In the event of a conflict between the text of this document and the references cited herein (except for device specifications), the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

- 1.5. APPLICATION OF THE DOCUMENT. This document is intended for use in acquisition of space and launch vehicles. This document should be cited in the contract statement of work and may be tailored by the acquisition activity for the specific application or program.

- 1.6. PMP MANAGEMENT. Implementation and changes, or modifications to the requirements of this document shall be accomplished in accordance with TOR-2006(8583)-5235 (Parts, Materials, and Processes Control Program for Space and Launch Vehicles), and the requirements of the program.

### 2 REFERENCED DOCUMENTS

### 2.1. REFERENCED DOCUMENTS

2.1.1 <u>Government Documents.</u> Unless otherwise specified, the following specifications, standards, and handbooks of the issue listed in the current version of the Department of Defense Index of Specifications and Standards (DoDISS) specified in the solicitation form a part of this document to the extent specified herein.

# 2.1.1.1 Military Specifications

| MIL-W-22759E(2) | Wire, Electric, Fluoropolymer-Insulated, Copper or Copper Alloy (CANCELED)                                                                 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| MIL-DTL-17      | Cables, Radio Frequency, Flexible and Semirigid, General Specification for                                                                 |

| MIL-PRF-27      | Transformers and Inductors (Audio, Power, and High Power Pulse), General Specification for                                                 |

| MIL-PRF-123     | Capacitors, Fixed, Ceramic Dielectric, (Temperature Stable and General Purpose), High Reliability, General Specification for               |

| MIL-PRF-3098    | Crystal Units, Quartz, General Specification For                                                                                           |

| MIL-DTL-5015    | Connector, Electrical, Circular Threaded, AN Type, General Specification for                                                               |

| MIL-H-6088G(1)  | Heat Treatment of Aluminum Alloys (CANCELED)                                                                                               |

| MIL-PRF-6106    | Relays, Electromagnetic, General Specification for                                                                                         |

| MIL-H-6875H     | Heat Treatment of Steels, Process for (CANCELED)                                                                                           |

| MIL-C-7438      | Core Material, Aluminum, For Sandwich Construction                                                                                         |

| MIL-S-7742D(1)  | Screw Threads, Standard, Optimum Selected Series, General Specification for (INACTIVE)                                                     |

| MIL-B-7883B     | Brazing of Steels, Copper, Copper Alloys, Nickel Alloys, Aluminum and Aluminum Alloys (CANCELED)                                           |

| MIL-PRF-8805    | Switches and Switch Assemblies, Sensitive and Push (Snap Action), Basic, Limit, Push Button and Toggle Switches, General Specification for |

| MIL-W-8939A     | Welding, Resistance, Electronic Circuit Modules (CANCELED)                                                                                 |

| MIL-T-9047G(1)   | Titanium and Titanium Alloy Bars (Rolled or Forged) and Reforging, Forging Stock Aircraft Quality (CANCELED)                                                                                                        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIL-DTL-9395     | Switches, Pressure, (Absolute, Gage and Differential), General Specification for                                                                                                                                    |

| MIL-PRF-15305    | Coil, Fixed and Variable, Radio Frequency, General Specification for                                                                                                                                                |

| MIL-PRF-19500    | Semiconductor Devices, General Specification for                                                                                                                                                                    |

| MIL-PRF-21038    | Transformer, Pulse, Low Power, General Specification for                                                                                                                                                            |

| MIL- A-21180D(1) | Aluminum-Alloy Castings, High Strength (CANCELED)                                                                                                                                                                   |

| MIL-PRF-23269    | Capacitors, Fixed, Glass Dielectric, Established Reliability, General Specification for                                                                                                                             |

| MIL-PRF-23419    | Fuse Cartridge, Instrument Type, General Specification for                                                                                                                                                          |

| MIL-PRF-23648    | Resistors Thermal (Thermistor), Insulated, General Specification for                                                                                                                                                |

| MIL-PRF-24236    | Switches, Thermostatic, (Metallic And Bimetallic), General Specification for                                                                                                                                        |

| MIL-DTL-24308    | Connector, Electrical, Rectangular, Nonenvironmental Miniature Polarized Shell, Rack and Panel, General Specification for                                                                                           |

| MIL-C-26482G(6)  | Connectors, Electrical, (Circular, Miniature, Quick Disconnect, Environment Resisting) Receptacles and Plugs, General Specification for (CANCELED)                                                                  |

| MIL-PRF-28861    | Filters and Capacitors, Radio Frequency/Electromagnetic Interference Suppression, General Specification for                                                                                                         |

| MIL-PRF-31032    | Printed Circuit Board/ Printed Wiring Board, General Specification for                                                                                                                                              |

| MIL-PRF-32159    | Resistors, Chip, Fixed, Film, Zero Ohm, Industrial, High Reliability, Space Level, General Specification for                                                                                                        |

| MIL-PRF-38534    | Hybrid Microcircuits, General Specification for                                                                                                                                                                     |

| MIL-PRF-38535    | Integrated Circuits (Microcircuits) Manufacturing, General Specification for                                                                                                                                        |

| MIL-DTL-38999    | Connector, Electrical, Circular, Miniature, High Density, Quick Disconnect (Bayonet, Threaded, and Breach Coupling), Environment Resistant, Removable Crimp and Hermetic Solder Contacts, General Specification for |

| MIL-PRF-39003    | Capacitors, Fixed, Electrolytic (Solid Electrolyte), Tantalum, Established Reliability, General Specification for                                                                                                   |

| MIL-PRF-39005    | Resistor, Fixed, Wirewound, (Accurate), Nonestablished and Established Reliability, General Specification for                                                                                                       |

| MIL-PRF-39006    | Capacitors, Fixed, Electrolytic (Nonsolid Electrolyte), Tantalum, Established Reliability, General Specification for                                                                                                |

|                  |                                                                                                                                                                                                                     |

| MIL-PRF-39007    | Resistor, Fixed, Wirewound (Power Type), Nonestablished Reliability, Established Reliability and Space Level, General Specification for                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIL-PRF-39009    | Resistor, Fixed, Wirewound (Power Type, Chassis Mounted), Nonestablished Reliability, Established Reliability, General Specification for                                      |

| MIL-PRF-39010    | Coil, Fixed, Radio Frequency, Molded, Established Reliability and Nonestablished Reliability, General Specification for                                                       |

| MIL-PRF-39012    | Connectors, Coaxial, Radio Frequency, General Specification for                                                                                                               |

| MIL-PRF-39015    | Resistors, Variable, Wirewound (Lead Screw Actuated), Nonestablished Reliability and Established Reliability, General Specification for                                       |

| MIL-PRF-39016    | Relays, Electromagnetic, Established Reliability, General Specification for                                                                                                   |

| MIL-PRF-39017    | Resistor, Fixed Film, (Insulated) Nonestablished Reliability and Established Reliability, General Specification for                                                           |

| MIL-C-39029D(1)  | Contacts, Electrical Connector, General Specification for (CANCELED)                                                                                                          |

| MIL-PRF-39035    | Resistor, Variable, Non-wirewound (Adjustment Type), Nonestablished and Established Reliability, General Specification for                                                    |

| MIL-PRF-32192    | Resistors, Chip, Thermal (Thermistor), General Specification for                                                                                                              |

| MIL-I-46058C(7)  | Insulating Compound, Electrical (for Coating Printed Circuit Assemblies) (INACTIVE)                                                                                           |

| MIL-S-46106      | Adhesive-Sealants, Silicone, RTV, One-Component                                                                                                                               |

| MIL-A-46146      | Adhesive Sealants, Silicone, RTV, Non-corrosive (For Use With Sensitive Metals and Equipment)                                                                                 |

| MIL-PRF-49467    | Capacitors, Fixed, Ceramic, Multilayer, High Voltage, (General Purpose), Established Reliability, General Specification for                                                   |

| MIL-PRF-49468(1) | Crystal Units, Quartz, Precision, General Specification for (CANCELED)                                                                                                        |

| MIL-PRF-49470    | Capacitor, Fixed, Ceramic Dielectric, Switch Mode Power Supply (General Purpose and Temperature Stable), Standard Reliability and High Reliability, General Specification for |

| MIL-P-50884D(2)  | Printed Wiring, Flexible, or Rigid-Flex, General Specification for (INACTIVE)                                                                                                 |

| MIL-PRF-55110G   | Printed Wiring Boards, General Specification for (INACTIVE)                                                                                                                   |

| MIL-PRF-55182    | Resistors, Fixed, Film, Non-Established Reliability, Established Reliability, and Space Level, General Specification for                                                      |

| MIL-DTL-55302    | Connector, Printed Circuit Subassembly and Accessories                                                                                                                        |

| MIL-PRF-55310    | Oscillator, Crystal Controlled, General Specification For                                                                                                                     |

| MIL-DTL-27500H(1)<br>NOT 1 | Cable, Power, Electrical and Cable Special Purpose, Electrical Shielded and Unshielded, General Specification for (CANCELED)                                                                                       |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIL-PRF-55342              | Resistor, Chip, Fixed, Film, Established Reliability, General Specification for                                                                                                                                    |

| MIL-PRF-55365              | Capacitor, Electrolytic Fixed Tantalum, Established Reliability and Nonestablished Reliability, General Specification for                                                                                          |

| MIL-T-55631(2)             | Transformer, Intermediate Frequency, Radio Frequency, and Discriminator, General specification for (inactive)                                                                                                      |

| MIL-DTL-81381              | Wire, Electric, Polyimide-Insulated, Copper or Copper Alloy                                                                                                                                                        |

| MIL-T-81556                | Titanium and Titanium Alloys, Extruded Bars, and Shapes Aircraft Quality                                                                                                                                           |

| MIL-F-83142A(4)            | Forging, Titanium Alloys, Premium Quality For Aircraft and Aerospace Applications (CANCELED)                                                                                                                       |

| MIL-PRF-83401              | Resistor Networks, Fixed, Film and Capacitor-Resistor Networks, Ceramic Capacitor and Fixed, Film, Resistors, General Specification for                                                                            |

| MIL-PRF-83421              | Capacitors, Fixed, Metallized, Plastic Film Dielectric, (DC, AC, or DC and AC), Hermetically Sealed in Metal Cases, or Ceramics Cases, Established Reliability, General Specification for                          |

| MIL-PRF-83446              | Coils, Radio Frequency, Chip, Fixed or Variable, General Specification for                                                                                                                                         |

| MIL-DTL-83513              | Connectors, Electrical, Rectangular, Microminiature, Polarized Shell, General Specification for                                                                                                                    |

| MIL-PRF-83536              | Relays, Electromagnetic, Established Reliability, 25 Amperes and Below, General Specification for                                                                                                                  |

| MIL-A-83577B               | Assemblies, Moving Mechanical, for Space and Launch Vehicles, General Specification for (CANCELED)                                                                                                                 |

| MIL-DTL-83723              | Connector, Electrical, (Circular, Environment Resisting), Receptacle and Plugs, General Specification for                                                                                                          |

| MIL-PRF-83726              | Relays, Hybrid and Solid-state, Time Delay, General Specification for                                                                                                                                              |

| MIL-DTL-83733              | Connector, Electrical, Miniature, Rectangular Type, Rack to Panel, Environment Resisting, 200 <sup>O</sup> C Total Continuous Operating Temperature, General Specification for                                     |

| MIL-C-85049A               | Connector Accessories, Electrical, General Specification for (CANCELED)                                                                                                                                            |

| MIL-PRF-87164A(3)          | Capacitors, Fixed, Mica Dielectric, High Reliability, General Specification for (CANCELED)                                                                                                                         |

| MIL-PRF-87217A             | Capacitors, Fixed, Supermetallized Plastic Film Dielectric, Direct Current for Low Energy, High Impedance Applications, Hermetically Sealed in Metal Cases, High Reliability, General Specification for (CANCELED) |

|                            |                                                                                                                                                                                                                    |

# 2.1.1.2 <u>Federal Standards</u>

| FED-STD-209E | Airborne Particulate Cleanliness Classes in Cleanrooms and Clean Zones (CANCELED) |

|--------------|-----------------------------------------------------------------------------------|

|--------------|-----------------------------------------------------------------------------------|

# 2.1.1.3 <u>Military Standards</u>

| MIL-HDBK-5J     | Metallic Materials and Elements for Aerospace Vehicle Structures (CANCELED)                                                                                                |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIL-HDBK-17     | Composite Materials Handbook (Volumes 1 through 5)                                                                                                                         |

| MIL-HDBK-23A(3) | Structural Sandwich Composites (CANCELED)                                                                                                                                  |

| MIL-STD-130     | Identification Marking of U.S. Military Property                                                                                                                           |

| MIL-HDBK-198    | Capacitor, Selection and Use of                                                                                                                                            |

| MIL-HDBK-199    | Resistor, Selection and Use of                                                                                                                                             |

| MIL-STD-202     | Test Method Standard, Electronic and Electrical Component Parts                                                                                                            |

| MIL-HDBK-217    | Reliability Prediction of Electronic Equipment                                                                                                                             |

| MIL-HDBK-263    | Electrostatic Discharge Control Handbook for Protection of Electrical and Electronic Parts, Assemblies, and Equipment (Excluding Electrically Initiated Explosive Devices) |

| MIL-HDBK-339    | Custom Large Scale Integrated Circuit Development and Acquisition for Space Vehicles                                                                                       |

| MIL-STD-403C    | Preparation for and Installation of Rivets and Screws, Rocket and Missile Structures (INACTIVE)                                                                            |

| MIL-STD-750     | Test Method Standard for Semiconductor Devices                                                                                                                             |

| MIL-HDBK-814    | Ionizing Dose and Neutron Hardness Assurance Guidelines for Microcircuits and Semiconductor Devices                                                                        |

| MIL-HDBK-815    | Dose Rate Hardness Assurance Guidelines                                                                                                                                    |

| MIL-STD-866B    | Grinding of Chrome Plated Steel and Steel Parts Heat Treated to 180,000 psi or Over (Inactive)                                                                             |

| MIL-STD-883     | Test Methods and Procedures for Microelectronics                                                                                                                           |

| MIL-STD-889     | Dissimilar Metals                                                                                                                                                          |

| MIL-STD-981     | Design, Manufacturing, and Quality Standards for Custom Electromagnetic Devices for Space Applications                                                                     |

| MIL-HDBK-1331   | Parameters To Be Controlled for the Specification of Microcircuits, Handbook for                                                                                           |

|                 |                                                                                                                                                                            |

| MIL-STD-1346C    | Relays, Selection and Application of (CANCELED)                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIL-STD-1353B(4) | Electrical Connectors Plug-in Sockets and Associated Hardware, Selection and Use of (CANCELED)                                                                           |

| MIL-STD-1580     | Department of Defense Test Methods Standard, Destructive Physical Analysis for Electrical, Electronic, and Electromagnetic Parts                                         |

| MIL-STD-1686     | Electrostatic Discharge Control Program for Protection of Electrical and Electronic Parts, Assemblies and Equipment (Excluding Electrically Initiated Explosive Devices) |

| MIL-STD-1835     | Electronic Component Case Outlines                                                                                                                                       |

| MIL-STD-2154(1)  | Inspection, Ultrasonic, Wrought Metals, Process for (CANCELED)                                                                                                           |

| MIL-STD-2175A    | Castings, Classification and Inspection of (CANCELED)                                                                                                                    |

| MIL-STD-2219     | Fusion Welding for Aerospace Applications                                                                                                                                |

| MIL-HDBK-83377   | Adhesive Bonding (Structural) for Aerospace and Other Systems, Requirements For                                                                                          |

| MIL-HDBK-83575   | General Handbook for Space Vehicle Wiring Harness Design and Testing                                                                                                     |

# 2.1.1.4 Air Force Wright Aeronautical Laboratories (AFWAL)

| ADD436124L | DOD/NASA Structural Composites Fabrication Guide Volume I                                                           |

|------------|---------------------------------------------------------------------------------------------------------------------|

| ADD436125L | DOD/NASA Structural Composites Fabrication Guide Volume II DOD/NASA Advanced Composite Design Guide, Volumes I – IV |

# 2.1.1.5 NASA Publications

| MSFC 40M38277 | Marshall Space Flight Connectors                                                                          |

|---------------|-----------------------------------------------------------------------------------------------------------|

| MSFC 40M38298 | Marshall Space Flight Connectors                                                                          |

| MSFC 40M39569 | Marshall Space Flight Connectors and Hardware                                                             |

| SP-R-0022A    | General Specifications, Vacuum Stability Requirements of Polymeric Materials for Space Craft Applications |

| MSFC-SPEC-250 | Protective Finishes for Space Flight Vehicle Structures and Equipment, General Specification for          |

| MSFC-STD-355  | Radiographic Inspection of Electronic Parts                                                               |

| MSFC-SPEC-469 | Titanium and Titanium Alloys, Heat Treatment of                                                           |

| MSFC-SPEC-522 | Design Criteria for Controlling Stress Corrosion Cracking                                                 |

| NASA-SP-8063    | Lubrication, Friction and Wear                                                                            |

|-----------------|-----------------------------------------------------------------------------------------------------------|

| NASA-STD-8739.1 | Workmanship Standard for Staking and Conformal Coating of Printed Wiring Boards and Electronic Assemblies |

| NASA-STD-8739.2 | Workmanship Standard for Surface Mount Technology                                                         |

| NASA-STD-8739.3 | Soldered Electrical Connectors                                                                            |

| NASA TM X-64755 | Part Derating Guidelines; Department of the Air Force, Air Force Systems Command (AFSC) Pamphlet 800-27   |

Application for copies should be addressed to: Marshall Space Flight Center/ Document Repository (AS24D), Huntsville, AL 35812

NASA Documents can be obtained via www.nepp.nasa.gov

2.1.2 <u>Non-government Documents.</u> The following documents form a part of this document to the extent specified herein. Unless otherwise indicated, the issue in effect on the date of release of this document shall serve as the applicable revision for all listed non-government specifications/standards.

#### 2.1.2.1 Aerospace TOR

| TOR-2006(8583)-5235 | Parts, Materials, and Processes Control Program for Space and Launch |

|---------------------|----------------------------------------------------------------------|

| (See note below)    | Vehicles                                                             |

(Application for copies should be addressed to: The Aerospace Corporation, Library, Circulation Desk, P.O. Box 92957, M1-199, Los Angeles, CA 90009-2957)

## 2.1.2.2 <u>American Society For Testing Material</u>

| ASTM-B-322    | Metal cleaning metals prior to electroplating                                                                                |

|---------------|------------------------------------------------------------------------------------------------------------------------------|

| ASTM-B-571    | Coating, Metallic Qualitative Adhesion Testing of                                                                            |

| ASTM-D-903-98 | Adhesive Bonds, Peel or Stripping Strength of                                                                                |

| ASTM-D-1000   | Tapes Pressure-Sensitive Adhesive-Coated Used For Electrical And Electronic Applications                                     |

| ASTM-E-595-84 | Standard Test Method for Total Mass Loss and Collected Volatile Condensable Material From Outgassing in a Vacuum Environment |

(Application for copies should be addressed to: American Society for Testing Materials, 1916 Race Street, Philadelphia, PA 19111), www.astm.org

#### 2.1.2.3 Electronics Industries Association

NOTE:

8

All reference in this document to Aerospace Report number TOR-2006(8583)-5236 shall refer to SMC Standard number SMC-S-009 (2008).

| EIA-455 | Fiber Optic Fibers, Cables, Transducers, Sensors, Connecting and Terminating Devices, and Other Fiber Optic Components |

|---------|------------------------------------------------------------------------------------------------------------------------|

| EIA-477 | Cultured Quartz                                                                                                        |

| EIA-557 | Statistical Process Control Systems                                                                                    |

(Application for copies should be addressed to: Electronic Industries Association, 2001 Pennsylvania Ave, N.W., Washington, D.C. 20006) www.eia.org

## 2.1.2.4 International Electrotechnical Commission

| CEI/IEC 60410                        | Sampling Plans And Procedures For Inspection By Attributes                                               |

|--------------------------------------|----------------------------------------------------------------------------------------------------------|

| CEI/IEC 60758 Ed. 3<br>Third edition | International Electrotechnical Commission: Synthetic Quartz Crystal – Specification And Guide To The Use |

(Application for copies should be addressed to: American National Standards Industries, 1430 Broadway, New York, NY 10018) www.ansi.org

# 2.1.2.5 IPC – ASSOCIATION CONNECTING ELECTRONIC INDUSTRIES

| IPC-SM-840 | Qualification and Performance of Permanent Polymer Coating (Solder Mask) for Printed Boards                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------|

| IPC-CC-830 | Qualification and Performance of Electrical Insulation Compound for Printed Wiring Assemblies                                 |

| IPC-TM-650 | Test Methods Manual                                                                                                           |

| IPC-CF-152 | Composite Metallic Material Specification for Printed Wiring Boards                                                           |

| J-STD-033  | Handling, Packaging, Shipping and Use of Moisture/Reflow Sensitive Surface Mounted Devices                                    |

| J-STD-020  | Moisture/Reflow Sensitivity Classification of Plastic Surface Mount Devices                                                   |

| J-STD-006  | Requirements for Electronic Grade Solder Alloys and Fluxed and Non-Fluxed Solid Solders for Electronic Soldering Applications |

| J-STD-002  | Solderability Tests for Component Leads, Terminations, Lugs Terminals and Wires                                               |

| J-STD-001C | Requirements for Soldered Electrical and Electronic Assemblies                                                                |

| IPC 2221   | Generic Standard for Printed Board Design                                                                                     |

| IPC 2222   | Sectional Design Standard for Rigid Organic Printed Boards                                                                    |

| IPC 2223   | Sectional Design Standard for Flexible Printed Boards                                                                         |

| IPC 2252  | Design Guide for RF/Microwave Circuit Boards                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------|

| IPC 4101B | Specification for Base Materials for Rigid and Multilayer Printed Boards                                           |

| IPC 4103  | Specification for Base Materials for High Speed/ Frequency Applications                                            |

| IPC 4202  | Flexible Base Dielectric for Use in Flexible Printed Circuitry                                                     |

| IPC 4203  | Adhesive Coated Dielectric Films for Use as Cover Sheets for Flexible Printed Circuitry and Flexible Bonding Films |

| IPC 4204  | Flexible Metal Clad Dielectric for Use in Fabrication of Flexible Printed Circuitry                                |

| IPC 6012B | Qualification and Performance Specification for Rigid Printed Boards                                               |

| IPC 6013A | Qualification and Performance Specification for Flexible Printed Boards                                            |

| IPC 6018A | Microwave End Product Board Inspection and Test                                                                    |

(Application for copies should be addressed to: IPC - 3000 Lakeside Drive, 309 S. Bannockburn, IL 60015) www.ipc.org

# 2.1.2.6 National Aerospace Standards

| NASM 1312 | Fastener, Test Methods                      |

|-----------|---------------------------------------------|

| NASM 1515 | Fastener Systems for Aerospace Applications |

www.nasm.org

# 2.1.2.7 <u>Society Of Automotive Engineers</u>

| SAE-AMS-QQ-A-367 | Aluminum Alloy Forgings                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| SAE-AMS-STD-1595 | Qualification of Aircraft, Missile and Aerospace Fusion Welders                                                 |

| SAE-AS-1933      | Hose Containing Age-Sensitive Elastomeric Material, Age Controls for                                            |

| SAE-ARP-5316     | Seals Assemblies Which Include An Elastomer Element Prior To Hardware Assembly, Storage of Elastomer Seals and  |

| SAE-AMS-F-7190   | Forging, Steel, for Aircraft/Aerospace Equipment and Special Ordnance Applications                              |

| SAE-AS-8879      | Screw Threads, UNJ Profile inch controlled Radius Root With Increased Minor Diameter, General Specification for |

| SAE-AMS-T-9046   | Titanium and Titanium Alloy, Sheet, Strip and Plate                                                             |

| SAE-AMS-S-13165  | Shot Peening of Metal Parts                                                                                     |

| SAE-AMS-A-22771 | Aluminum. Alloy Forgings, Heat Treated         |

|-----------------|------------------------------------------------|

| SAE-AMS-H-81200 | Heat Treatment of Titanium and Titanium Alloys |

# 2.1.2.8 <u>ANSI/IEEE</u>

| ANSI/IEEE 176-1987 | IEEE Standard on Piezoelectricity |

|--------------------|-----------------------------------|

|--------------------|-----------------------------------|

www.ieee.org

2.1.3 Order Of Precedence. In the event of a conflict between the text of this document and the references cited herein, the text of this document shall take precedence.

# 3 DEFINITIONS

Terms are in accordance with the following definitions:

| The acquisition activity is the Government office or contractor acquiring the equipment, system, or subsystem for which this document is being contractually applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The case temperature is the hottest temperature on the external surface of the device's package, and for Surface Mount Devices (SMD), the external surface is the case.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A contracting officer is a person with the authority to enter into, administer, or terminate contracts and make related determinations and findings. The term includes authorized representatives of the contracting officer acting within the limits of their authority as delegated by the contracting officer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Derating of a part is the intentional reduction of its applied stress, with respect to its rated stress, for the purpose of providing a margin between the applied stress and the demonstrated limit of the part's capabilities. Maintaining this derating margin reduces the occurrence of stress-related failures and helps ensure the part's reliability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A Destructive Physical Analysis (DPA) is a systematic, logical, detailed examination of parts during various stages of disassembly, conducted on a sample of completed parts from a given lot, wherein parts are examined for a wide variety of design, workmanship, and processing problems that may not show up during normal screening tests. The purpose of these analyses is to maintain configuration control and determine those lots of parts, delivered by a vendor, which have anomalies or defects such that they could, at some later date, cause degradation or catastrophic failure of a system.                                                                                                                                                                                                                                                                                          |

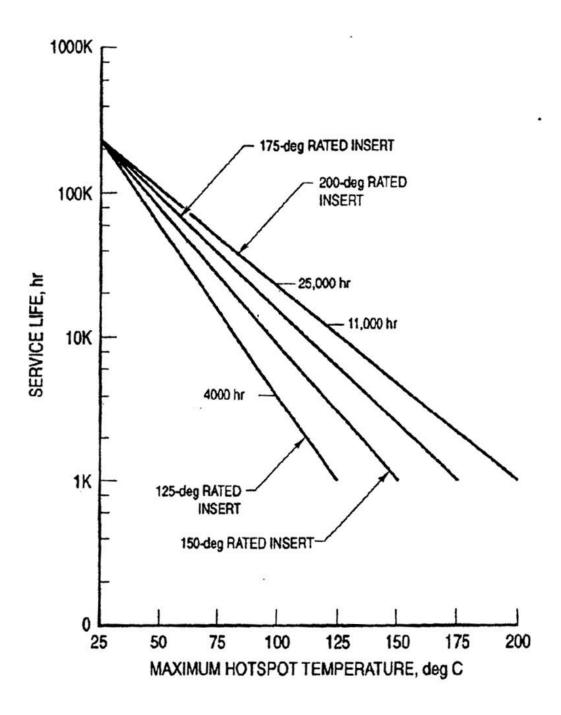

| The term "electronic" is used in a broad sense in this document and includes electrical, electromagnetic, electromechanical, and electro-optical devices (EEEE devices). Connectors are also classified as electronic parts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |