RL-TR-94-232 Final Technical Report December 1994

# R&M DESIGN EXPERT SYSTEM

**Martin Marietta**

Angela M. Kitchen, Jeff Steelhammer, Doug Doskocil, Eric Freeman, Glenn Elias, and Rich Ziegar

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

19950321 157

DITO CHALLEY INSPECTED 1

Rome Laboratory

Air Force Materiel Command

Griffiss Air Force Base, New York

This report has been reviewed by the Rome Laboratory Public Affairs Office (PA) and is releasable to the National Technical Information Service (NTIS). At NTIS it will be releasable to the general public, including foreign nations.

RL-TR-94-232 has been reviewed and is approved for publication.

APPROVED: Dale M. Richards

DALE W. RICHARDS Project Engineer

FOR THE COMMANDER:

JOHN J. BART

James. Bout

Chief Scientist, Reliability Sciences

Electromagnetics & Reliability Directorate

If your address has changed or if you wish to be removed from the Rome Laboratory mailing list, or if the addressee is no longer employed by your organization, please notify RL ( ERSR) Griffiss AFB NY 13441. This will assist us in maintaining a current mailing list.

Do not return copies of this report unless contractual obligations or notices on a specific document require that it be returned.

#### Form Approved REPORT DOCUMENTATION PAGE OMB No. 0704-0188 Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instructions, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington Headquarters Services, Directorate for information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0189), Washington, DC 20503. 3. REPORT TYPE AND DATES COVERED AGENCY USE ONLY (Leave Blank) 2. REPORT DATE Sep 91 - Sep 94 Fina1 December 1994 5. FUNDING NUMBERS 4. TITLE AND SUBTITLE C - F30602 - 91 - C - 0159PE - 62702F R&M DESIGN EXPERT SYSTEM PR - 2338 6. AUTHOR(S) TA - 02Angela M. Kitchen, Jeff Steelhammer, Doug Doskocil, WU - 5G Eric Freeman, Glenn Elias, and Rich Ziegar 8. PERFORMING ORGANIZATION 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) REPORT NUMBER Martin Marietta Martin Marietta Laboratories N/A Moorestown NJ 08057 10. SPONSORING/MONITORING 9. SPONSORING/MONITORING AGENCY NAME(S) AND ADDRESS(ES) AGENCY REPORT NUMBER Rome Laboratory (ERSR) 525 Brooks Rd RL-TR-94-232 Griffiss AFB NY 13441-4505 11. SUPPLEMENTARY NOTES Rome Laboratory Project Engineer: Dale W. Richards/ERSR/(315) 330-3476 12b. DISTRIBUTION CODE 12a. DISTRIBUTION/AVAILABILITY STATEMENT Approved for public release; distribution unlimited. 13. ABSTRACT (Maximum 200 words) This effort investigated and developed a proof-of-concept software system that combines reliability, testability, and maintainability analysis capabilities into a single tool. The system recommends tests and testpoints based on potential faults (associated with a component within the design) and a functional-block description of the design. The system directs the user in injecting faults into a simulation model. The tests and testpoints are then used to perform fault isolation using the results of the simulation. Case-based reasoning techniques were used as a basis for the testability and test coverage aspects of the program. The casebase is a repository of "past knowledge" gained from expert designers and testability experts. The system adds to this repository if an unfamiliar situation occurs, allowing the system to "learn" over time. The expert knowledge was encoded into a Fault Mode Map that represents how the experts relate faulty behavior of the circuits to actual failures. Rome Laboratory Oracle (a reliability prediction tool), Mentor Graphics Design Architect (a schematic capture tool), and Analogy Saber (a circuit simulation tool) were integrated to allow the user to exercise all system capabilities from a single user perspective. The system was tested against Martin Marietta power supply design. 15. NUMBER OF PAGES 14. SUBJECT TERMS Reliability, Testability, Computer-aided design, Case-based 16. PRICE CODE reasoning, Power supplies, Fault analysis, Electronics 18. SECURITY CLASSIFICATION OF ABSTRACT OF THIS PAGE 19. SECURITY CLASSIFICATION 20. LIMITATION OF ABSTRACT 17. SECURITY CLASSIFICATION OF REPORT

UNCLASSIFIED

UNCLASSIFIED

UNCLASSIFIED

NSN 7540-01-280-5500

UL

## **Executive Summary**

The Reliability and Maintainability Design Expert System (R&M Expert System) is a recently concluded, three—year program sponsored by Rome Laboratory. Martin Marietta Laboratories

• Moorestown developed the contract, which resulted in a proof—of—concept system that combined three types of analyses into a single tool; these analyses were reliability, testability, and maintainability.

The R&M Expert System recommends test and test points based on potential faults (a component within the design) and a functional block. It direct users to inject faults into a simulation model, and it uses tests and testpoints defined by users and the results of the simulation to isolate faults. We used a power supply design from a division of Martin Marietta to test the system, which performed to specification.

## Concurrency is the main requirement for testability, reliability, and maintainability (TR&M) issues

Electronic systems designed for TR&M require specialists to participate from the beginning of the design effort; otherwise, they are unable to successfully address issues that may arise. Specification requirements, which include government standards, drive reliability design. Standard testability analysis involves a structured process to evaluate testability performance. Primary testability performance parameters are fault-detection coverage, fault isolation, and false alarm percentage. The designer considers the following when defining a hardware

CRA&I

Justification

Availability Codes

Avail and lor

Special

TAB

Unannounced

Distribution /

NTIS

DTIC

Ву

Dist

Accesion For

testpoint and selecting a software test on the final product:

- Mechanical accessibility considerations

- Testability requirements and analyses

- Hardware/software test design trade-offs

- Test equipment capabilities

- Cost of test and repair processes.

The R&M Expert System program contained three phases:

- Phase I A 12-month effort that defined the system concept based on existing human processes in TR&M design and on tools to support the designer. The effort examined links between human processes and tools so that the concept had maximum impact. Also conducted was a survey of available TR&M tools.

- Phase II An 18-month effort that designed and implemented the skeleton system. Tool interfacing, data extraction, and data representation were major design elements. A critical development was the Fault-to-Failure-Mode Map (FFMM), which was the foundation of the system's knowledge base.

- Phase III A 6-month effort refined system concepts.

## Martin Marietta developed a unique methodology to integrate the three types of analysis

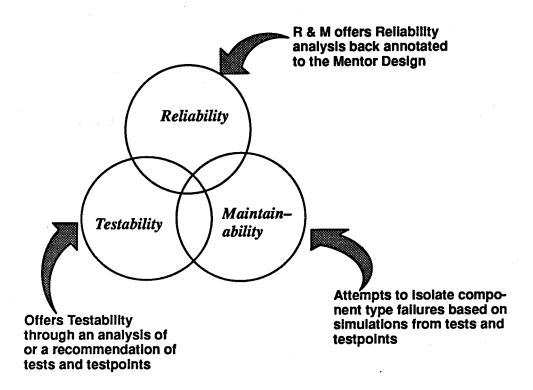

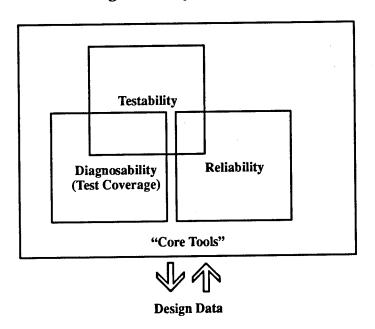

Martin Marietta developed a unique methodology to integrate analyses of testability, reliability, and maintainability. The methodology combined these analyses in new ways; for example, using reliability to guide the maintainability analysis. The R&M Design Expert System is extensible to different designs, but it currently concentrates on power supplies.

Martin Marietta Laboratories • Moorestown developed a method to examine designs from the perspective of TR&M. This allowed a framework to consider how each of the three impacted the others. It also gives designers a new perspective on the design through the combination of the different fields. The methodology allows users to see which areas of TR&M do not have tools to assist the designers.

## We created a casebase of past knowledge that grows with system use

The R&M Expert System uses past knowledge through Case—Based—Reasoning technology. The system's casebase is a repository of past knowledge gained from expert designers and testability and maintainability experts. The system adds data to its repository when unfamiliar situations occur. The system uses its casebase in two ways:

- To recommend tests and test points, based on components and functional blocks

- To isolate faults based on a test, test point, and signature behavior.

The design reduces the number of data repositories, making updates to the casebase easier.

We formed a Fault-to-Failure-Mode Map (FFMM) that represents how experts relate circuit faults to that which may actually be wrong with the circuit. The FFMM is a central part of the R&M System, and it is used by the testability and test coverage modules.

## The Elements in the Cases:

Name: Type of fault (e.g. open diode)

Functional Block: Functional block fault occurred

Failure Mode: Effect on the Circuit

Measurement Point: Point where measurement is taken

Measurement Type: Type of measurement (e.g. DC voltage)

Signature Behaviour: observed behavior

Measurement Devices: devices used in measurements

## The R&M Expert System interfaces with Mentor Graphics' Design Architect, Analogy's Saber, and Rome Laboratory's Oracle

The interface with Mentor Graphics' Design Architect, Analogy's Saber, and Rome Laboratory's Oracle are a significant part of the R&M Expert System. Without this interface, the system would not be able to get the information that is required for the expert system.

The interface with Design Architect is seamless and transparent after initial set—up. Design Architect provides most of the system's information. Martin Marietta implemented the interface early in the program to lay the groundwork for the informational structure used in the program.

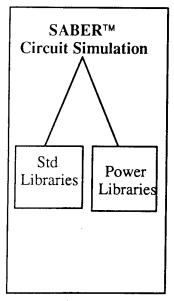

There is a standardized procedure to interface with Saber and Oracle through system files. The Oracle interface allows users to gather reliability data, which reduces mistakes and time required for the analysis. The Saber interface is also transparent by interacting with it solely through automatically generated files. Oracle provides the system with reliability data on the design. Saber provides circuit simulation results for test coverage analysis.

### **Analogy Tools**

Martin Marietta overcame many challenges in developing the R&M Expert System, including interfacing tools, developing a design methodology, and integrating the whole into a useful prototype

A major challenge was interfacing Mentor Graphics' Design Architect, Analogy's Saber analysis tool, and Martin Marietta's R&M system. Issues focused on differing representations of design in each tool. Interfacing the tools was a major accomplishment early in the program; it allowed us to assist the designer for the remainder of the program. Accomplishments also included developing a general interface could enable commercial—off—the—shelf (COTS) tools to replace Mentor Graphics or Analogy tools without a total rework of the system.

A major challenge was developing a way to bring the circuit designer into the TR&M analyses earlier. The prototype is an implementation of the resulting design methodology, which contains areas that were not implemented in the proof—of—concept prototype. However, it clearly defines these areas and how they would interact with the system. The R&M Expert System implemented the areas of reliability, testability, and a subset of maintainability. We were unable to implement the overlapping areas of the methodology.

We developed the prototype system to bring the circuit designer closer to the TR&M practices. The prototype provides a common framework in which designs can perform "what—if" analysis of their designs. By integrating the system with common used CAD/CAE tools, the prototype allows designers full freedom for development.

## **Table of Contents**

| 1. | Introduction                                                                 | 1                                     |

|----|------------------------------------------------------------------------------|---------------------------------------|

|    | 1.1 Program Scope and Objectives                                             | 1                                     |

|    | 1.2 The R&M Design Expert System Concept                                     | 3                                     |

|    | 1.3 Report Overview                                                          | 3                                     |

|    | •                                                                            |                                       |

| 2. | Background                                                                   | 4                                     |

|    | 2.1 The Human Process in Design: An Overview                                 | 4                                     |

|    | 2.1.1 The Specification                                                      | 4                                     |

|    | 2.1.2 Design Process with Testability, Reliability & Maintainability in Mind | 5                                     |

|    | 2.1.2.1 Reliability                                                          | 5                                     |

|    | 2.1.2.2 Testability                                                          | 6                                     |

|    | 2.1.2.3 Test Point and BIT Selection                                         | 7                                     |

|    | 2.1.2.4 Automated Test Equipment -Army and Navy Standards                    | 10                                    |

|    | 2.1.3 Summary                                                                | 10                                    |

|    | 2.2 A Survey Of The Tools That Aid The Design Process                        | 12                                    |

|    | 2.2.1 Overview                                                               | 12                                    |

|    | 2.2.2 Concurrent Engineering And Embedded Tools                              | 12                                    |

|    | 2.2.2.1 Reliability Analysis                                                 | 13                                    |

|    | 2.2.2.2 Maintainability Analysis                                             | 18                                    |

|    | 2.2.2.3 FMECA                                                                | 20                                    |

|    | 2.2.2.4 Testability                                                          | 22                                    |

|    | 2.2.2.5 Other Related Tools                                                  | 23                                    |

|    | 2.2.3 Hierarchy, Division Of Expertise, Data Flow & Concurrent Engineering.  | 23                                    |

|    | 2.2.4 An Observation On The Growth Of R&M Analyses                           | 24                                    |

|    | 2.2.5 Summary                                                                | 25                                    |

|    | 2.2.6 Conclusions                                                            | 26                                    |

|    | 2.3 The Testability Process: A Detailed Look                                 | 27                                    |

|    | 2.3.1 Introduction                                                           | 27                                    |

|    | 2.3.2 Programmatic Testability Issues                                        | 27                                    |

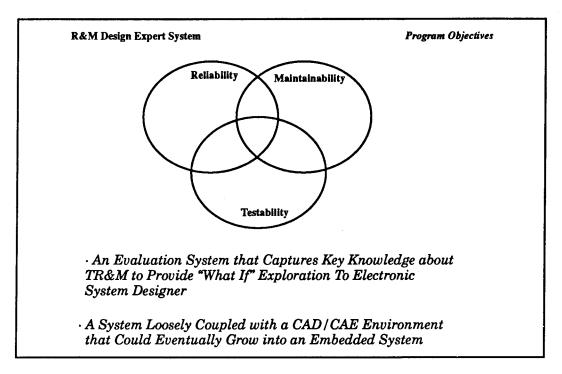

|    | 2.3.3 Fault Coverage Analysis                                                | 28                                    |

|    | 2.3.4 Diagnostic Development Process                                         | 30                                    |

|    | 2.3.5 Technical Testability Issues                                           | 31                                    |

|    | 2.3.6 Typical Fault Coverage Database                                        | 31                                    |

|    | 2.3.7 Multiple Viewpoints of Diagnostic Data                                 | 32                                    |

|    | 2.3.8 Functional and Physical Model Development                              | 33                                    |

|    | 2.3.9 Testability in an Integrated Product Team Environment                  | 34                                    |

|    | 2.3.9.1 R&M Functions in a CAD/CAE Environment                               | 35                                    |

|    | 2.3.10 Summary                                                               | 36                                    |

|    | 20010 Dalminary                                                              | 50                                    |

| 3. | System Concepts and Methodologies                                            | 38                                    |

|    | 3.1 Supportability Analysis                                                  | 38                                    |

|    | 3.1.1 Reliability                                                            | 40                                    |

|    | 3.1.2 Testability                                                            | 41                                    |

|    | 3.1.3 Maintainability Metric                                                 | 41                                    |

|    | 3.1.4 Reliability Metric                                                     | 42                                    |

|    |                                                                              | · · · · · · · · · · · · · · · · · · · |

|    | 3.1.5 Testability Metric                                                                                                                                                                                                                                                                                                                                                                                                                      | 42                                                                               |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|    | 3.1.6 Maintainability Metric                                                                                                                                                                                                                                                                                                                                                                                                                  | 45                                                                               |

|    | 3.1.7 Reliability/Testability Combined Metric                                                                                                                                                                                                                                                                                                                                                                                                 | 46                                                                               |

|    | 3.1.8 Reliability/Maintainability Metric                                                                                                                                                                                                                                                                                                                                                                                                      | 48                                                                               |

|    | 3.1.9 Testability/Maintainability Metric                                                                                                                                                                                                                                                                                                                                                                                                      | 49                                                                               |

|    | 3.1.10 Testability/Reliability/Maintainability Metric                                                                                                                                                                                                                                                                                                                                                                                         | 49                                                                               |

|    | 3.2 The Concept: The R&M Design Expert System                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                               |

|    | 3.2.1 Scope: Focus on Test Selection and Coverage                                                                                                                                                                                                                                                                                                                                                                                             | 50                                                                               |

|    | 3.2.2 Concept Design Drivers: Tools Used in the System                                                                                                                                                                                                                                                                                                                                                                                        | 52                                                                               |

|    | 3.2.2.1 Mentor Tool Suite: The Base CAD/CAE Environment                                                                                                                                                                                                                                                                                                                                                                                       | 52                                                                               |

|    | 3.2.2.2 Saber Analog Simulation                                                                                                                                                                                                                                                                                                                                                                                                               | 52                                                                               |

|    | 3.2.2.3 RL-Oracle                                                                                                                                                                                                                                                                                                                                                                                                                             | 53                                                                               |

|    | 3.2.2.4 ART-IM: The Knowledge-Based System Tool                                                                                                                                                                                                                                                                                                                                                                                               | 53                                                                               |

|    | 3.2.3 Application of Knowledge-Based Tools Electronic System Design                                                                                                                                                                                                                                                                                                                                                                           | 53                                                                               |

|    | 3.2.4 Required System Inputs                                                                                                                                                                                                                                                                                                                                                                                                                  | 54                                                                               |

|    | 3.2.4.1 A Hierarchical Design to Analyze                                                                                                                                                                                                                                                                                                                                                                                                      | 54                                                                               |

|    | 3.2.5 Additional Design Representation                                                                                                                                                                                                                                                                                                                                                                                                        | 55                                                                               |

|    | 3.2.5.1 TR&M Specifications                                                                                                                                                                                                                                                                                                                                                                                                                   | 56                                                                               |

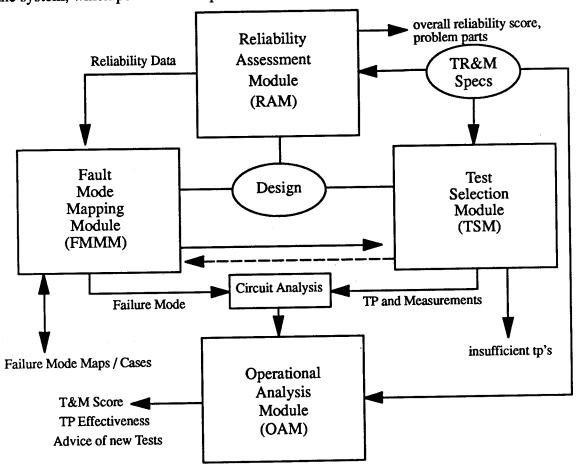

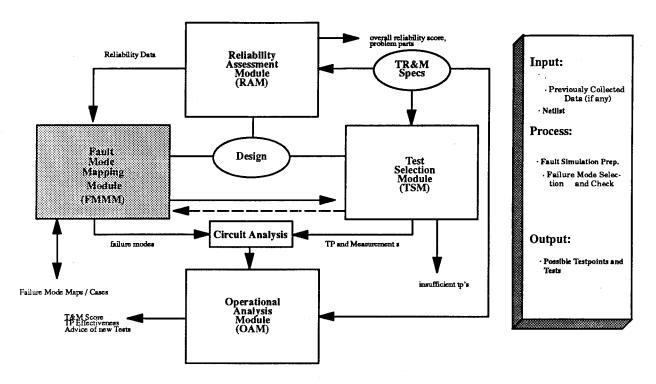

|    | 3.2.6 System Modules                                                                                                                                                                                                                                                                                                                                                                                                                          | 56                                                                               |

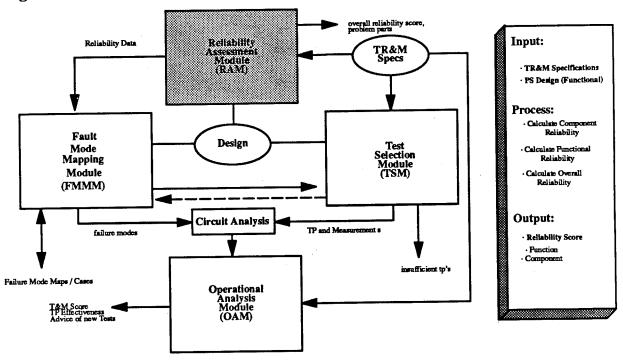

|    | 3.2.6.1 Reliability Assessment Module(RAM)                                                                                                                                                                                                                                                                                                                                                                                                    | 56                                                                               |

|    | 3.2.6.2 Fault Mode Mapping Module (FMMM)                                                                                                                                                                                                                                                                                                                                                                                                      | . 57                                                                             |

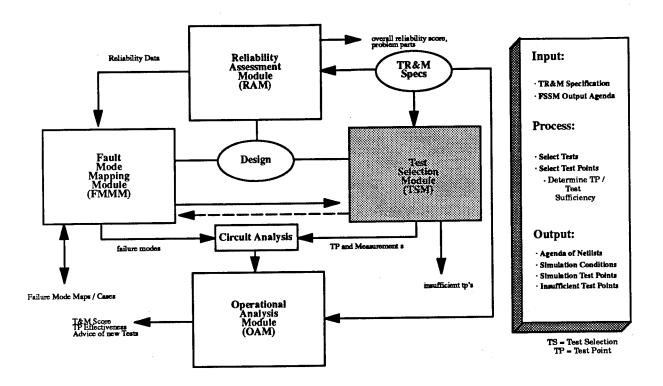

|    | 3.2.6.3 Test Selection Module (TSM)                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                                                               |

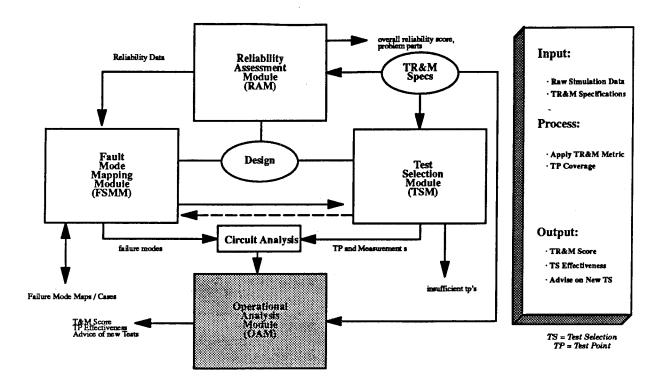

|    | 3.2.6.4 Operational Analysis Module (OAM)                                                                                                                                                                                                                                                                                                                                                                                                     | 59                                                                               |

|    | 3.2.7 Assumptions                                                                                                                                                                                                                                                                                                                                                                                                                             | 60                                                                               |

|    | · •                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| 4. | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                | 61                                                                               |

|    | 4.1 Development Overview                                                                                                                                                                                                                                                                                                                                                                                                                      | 61                                                                               |

|    | 4.2 Interfacing with Mentor Graphics                                                                                                                                                                                                                                                                                                                                                                                                          | 63                                                                               |

|    | 4.3 Interfacing with the Design                                                                                                                                                                                                                                                                                                                                                                                                               | 63                                                                               |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|    | 4.4 Fault—to—Failure—Mode Map                                                                                                                                                                                                                                                                                                                                                                                                                 | 65                                                                               |

|    | 4.4 Fault—to—Failure—Mode Map                                                                                                                                                                                                                                                                                                                                                                                                                 | 66                                                                               |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map                                                                                                                                                                                                                                                                                                                                                                                                  | 66<br>66                                                                         |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map                                                                                                                                                                                                                                                                                                                                                                                                  | 66<br>66<br>67                                                                   |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map                                                                                                                                                                                                                                                                                                                                                                                                  | 66<br>66<br>67<br>68                                                             |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map                                                                                                                                                                                                                                                                                                                                                                                                  | 66<br>66<br>67<br>68<br>68                                                       |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views                                                                                                                                                                                                                                                    | 66<br>66<br>67<br>68<br>68<br>69                                                 |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View                                                                                                                                                                                                                             | 66<br>66<br>67<br>68<br>68                                                       |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View 4.6.2 Test Coverage View                                                                                                                                                                                                    | 66<br>66<br>67<br>68<br>68<br>69                                                 |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View                                                                                                                                                                                                                             | 66<br>66<br>67<br>68<br>68<br>69<br>70<br>70                                     |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View 4.6.2 Test Coverage View 4.7 Reliability Assessment Module                                                                                                                                                                  | 66<br>66<br>67<br>68<br>68<br>69<br>70<br>71<br>71                               |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View 4.6.2 Test Coverage View 4.7 Reliability Assessment Module 4.8 Test Selection Module                                                                                                                                        | 66<br>66<br>67<br>68<br>68<br>69<br>70<br>70<br>71<br>71                         |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View 4.6.2 Test Coverage View 4.7 Reliability Assessment Module 4.8 Test Selection Module 4.9 Operational Analysis Module 4.9.1 OAM Databases 4.9.2 Parsing the Saber Output                                                     | 66<br>66<br>67<br>68<br>68<br>69<br>70<br>70<br>71<br>71<br>72<br>73             |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View 4.6.2 Test Coverage View 4.7 Reliability Assessment Module 4.8 Test Selection Module 4.9 Operational Analysis Module 4.9.1 OAM Databases 4.9.2 Parsing the Saber Output                                                     | 66<br>66<br>67<br>68<br>68<br>69<br>70<br>71<br>71<br>71<br>72<br>73             |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View 4.6.2 Test Coverage View 4.7 Reliability Assessment Module 4.8 Test Selection Module 4.9 Operational Analysis Module 4.9.1 OAM Databases                                                                                    | 66<br>66<br>67<br>68<br>68<br>69<br>70<br>71<br>71<br>72<br>73<br>74             |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View 4.6.2 Test Coverage View 4.7 Reliability Assessment Module 4.8 Test Selection Module 4.9 Operational Analysis Module 4.9.1 OAM Databases 4.9.2 Parsing the Saber Output 4.9.3 Fault Behavior Analysis                       | 66<br>66<br>67<br>68<br>68<br>69<br>70<br>71<br>71<br>71<br>72<br>73             |

|    | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View 4.6.2 Test Coverage View 4.7 Reliability Assessment Module 4.8 Test Selection Module 4.9 Operational Analysis Module 4.9.1 OAM Databases 4.9.2 Parsing the Saber Output 4.9.3 Fault Behavior Analysis 4.9.4 Fault Isolation | 66<br>66<br>67<br>68<br>68<br>69<br>70<br>71<br>71<br>72<br>73<br>74<br>77<br>80 |

| 5. | 4.4.1 Creating the Fault—to—Failure—Mode Map 4.4.2 Using the Mode Map for Testability 4.4.3 Using the Mode Map for Fault Isolation 4.5 Casebase Methodologies and Views 4.6 Casebase Views 4.6.1 Testability View 4.6.2 Test Coverage View 4.7 Reliability Assessment Module 4.8 Test Selection Module 4.9 Operational Analysis Module 4.9.1 OAM Databases 4.9.2 Parsing the Saber Output 4.9.3 Fault Behavior Analysis 4.9.4 Fault Isolation | 66<br>66<br>67<br>68<br>68<br>69<br>70<br>71<br>71<br>72<br>73<br>74             |

|    | 5.2 Using Casebase Reasoning Approach                    | 82  |

|----|----------------------------------------------------------|-----|

|    | 5.3 Testability                                          | 83  |

|    | 5.4 Degrees of Fault Isolation                           | 84  |

|    | 5.5 Importance of Standard Naming Conventions            | 85  |

|    | 5.6 Simulation Software Version or Vendor Changes        | 85  |

|    | 5.7 Simulation Accuracy Versus System Performance        | 86  |

|    | 5.8 Casebase Continuity                                  | 87  |

|    | 5.9 Designer Versus Automation                           | 87  |

|    | 5.10 Simulation and Fault Diagnosis Software Integration | 88  |

|    | 5.11 Measurement Points: Specific to General             | 89  |

|    | 5.12 Effects of Casebase Expansion                       | 89  |

|    | 5.13 Manipulation of Saber Output Files                  | 89  |

|    | 5.14 System Resource Requirements                        | 90  |

|    | 5.15 Conclusions                                         | 90  |

| 6. | Glossary                                                 | 92  |

| 7. | Appendix                                                 | 97  |

|    | Index                                                    | 100 |

## Table of Figures

| Figure 1. Program objectives                                                                                               | 2          |

|----------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 2 Typical testability requirements summary                                                                          | 28         |

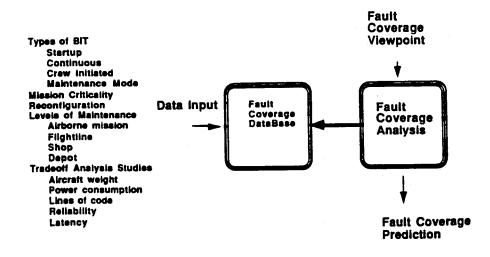

| Figure 3. Fault coverage analysis                                                                                          | 29         |

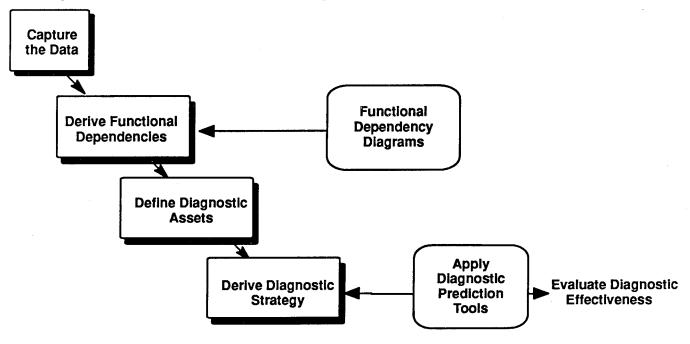

| Figure 4. Diagnostic development process.                                                                                  | 30         |

| Figure 5. Typical fault coverage analysis database                                                                         | 32         |

| Figure 6. Multiple viewpoints of diagnostic data                                                                           | 33         |

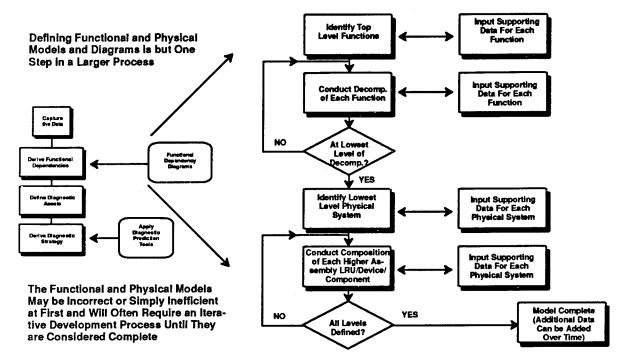

| Figure 7. Functional and physical model development.                                                                       | 34         |

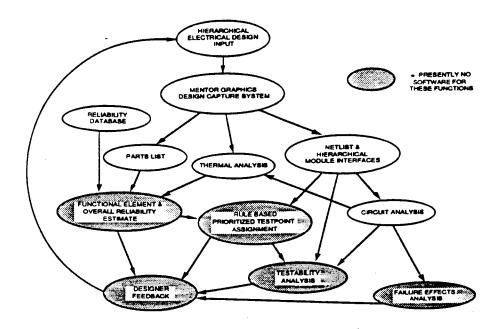

| Figure 8. R&M and design CAD/CAE functions                                                                                 | 36         |

| Figure 9. Design methodology for testability, reliability, and maintainability                                             | 38         |

| Figure 10. Reliability Example                                                                                             | 43         |

| Figure 11. Testability Example                                                                                             | 44         |

| Figure 12 Failure rate weighted testability example.                                                                       | 47         |

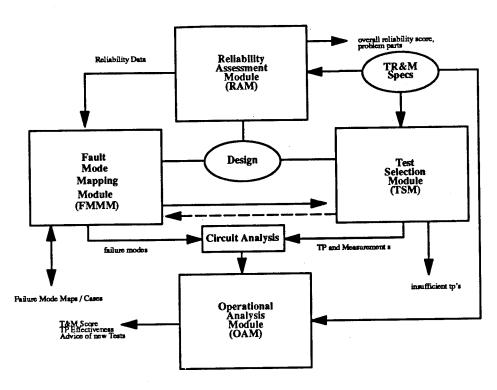

| Figure 13 System concept                                                                                                   | 51         |

| Figure 14. System concept with different view/same functionality Shared Data.                                              | 51         |

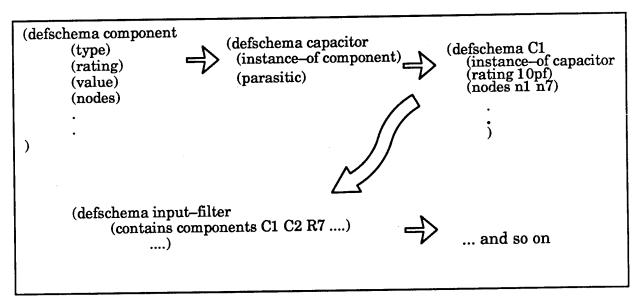

| Figure 15 An example ART-IM representation                                                                                 | 55         |

| Figure 16 Reliability Assessment Module(RAM)                                                                               | 57         |

| Figure 17 Fault Mode Mapping Module (FMMM)                                                                                 | 58         |

| Figure 18 Test Selection Module (TSM)                                                                                      | 59         |

| Figure 19 Operational Analysis Module(OAM)                                                                                 | 60         |

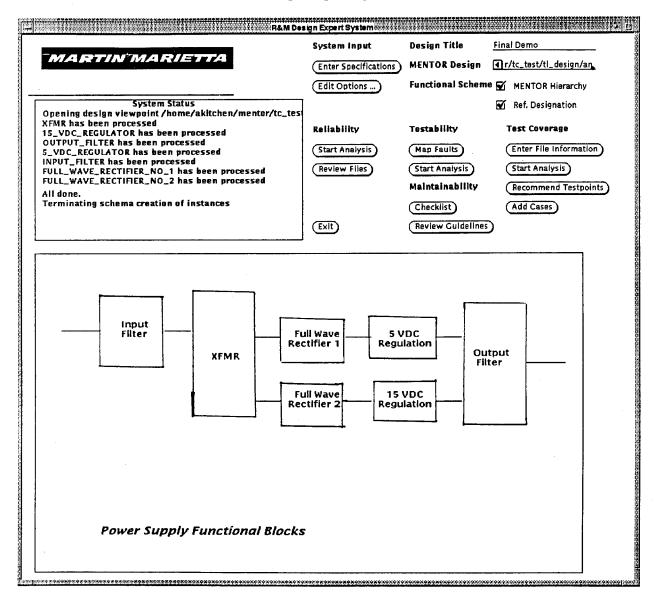

| Figure 20 The R&M Design Expert System.                                                                                    | 62         |

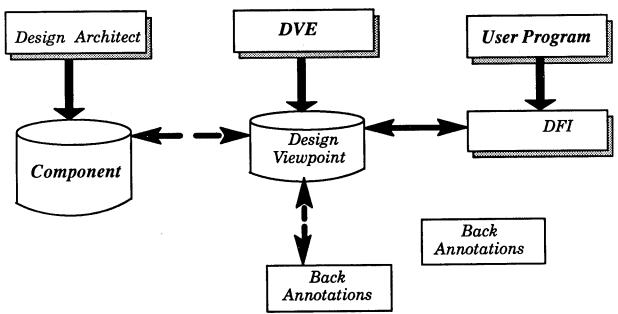

| Figure 21. Relationships used in R&M Expert System Mentor Graphics                                                         | 63         |

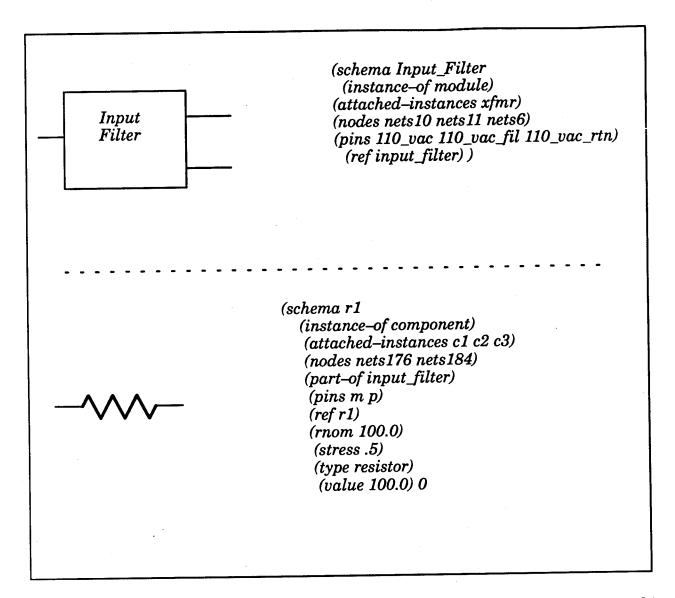

| Figure 22 Examples of the models of functional blocks                                                                      | 65         |

| Figure 23 Example of a Fault—to—Failure—Mode Mapping                                                                       | 66         |

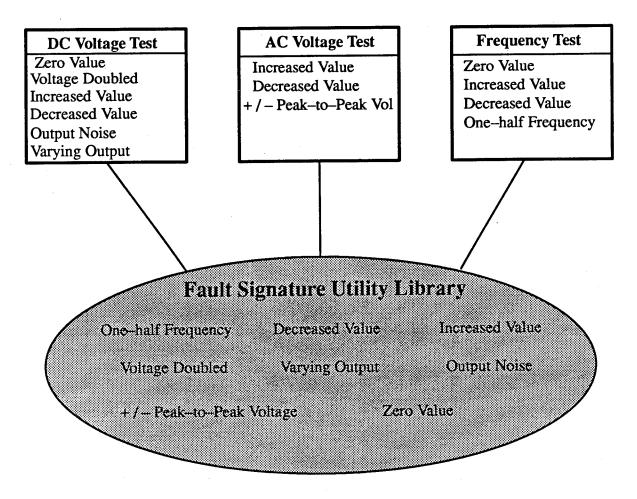

| Figure 24. Structure of the casebase used in the testability and                                                           |            |

| test coverage modules                                                                                                      | 68         |

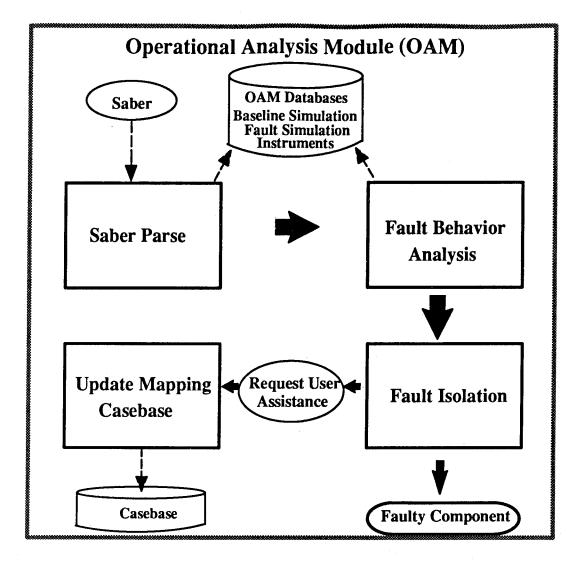

| Figure 25 Architecture of the Operational Analysis Module (OAM)                                                            | 72         |

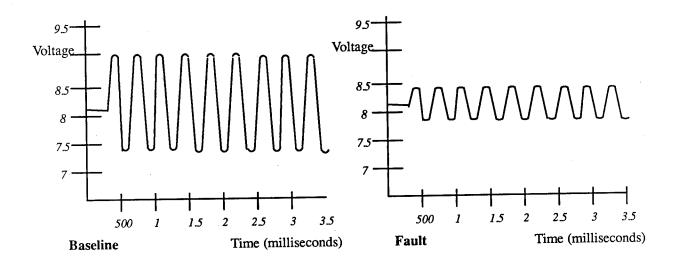

| Figure 26 Time versus Voltage display for the baseline and fault circuits as viewed by the designer during the simulation. | 75         |

| Figure 27 General software architecture of the Fault Behavior                                                              |            |

| Analysis component                                                                                                         | 77         |

| Figure 28 Example of multiple fault signature associations to a single fault                                               | <b>7</b> 9 |

## **Table of Tables**

| Table 1. Test coverage.                         | 45 |

|-------------------------------------------------|----|

| Table 2 Test coverage with lvalues              | 48 |

| Table 3. Failure rate weighted maintainability. | 49 |

#### Acknowledgements

This report was prepared by Martin Marietta Laboratories • Moorestown and Automated Systems Department (ASD). The descriptions of concepts and developments herein are a direct result from the contribution of the following individuals: Doug Doskocil, Eric Freeman, Eldon Sutphin, Robert Harwell, and Lee Stratton at ASD, and Angela Kitchen, Rich Zeiger, Jeff Steelahmmer, Glenn Elias, Virginie Harris, and Bill Tinney from Martin Marietta Laboratories • Moorestown.

### 1. Introduction

## 1.1 Program Scope and Objectives

In recent years, the defense industry has, appropriately, place increased emphasis on reliability, maintainability and testability in order to develop and maintain a more cost—and—mission—effective fighting force. The advent of Integrated Diagnostics has results in methodologies and tools to assist in supportability requirement refinement and tradeoffs, thereby assisting the front end of the system development cycle. Additionally, many tools have been developed for assisting Automatic Test Equipment (ATE) and Test Program Set (TPS) developers to define and implement better system once the system under these has been defined. However, the capabilities of computer—aided design tools have increased exponentially, there has been little associated development in reliability, maintainability and testability tools which apply to the detailed design phase. One of the classic dilemmas facing the industry has been that a specialty engineer cannot evaluate a design until it is at least somewhat complete, and yet once it is complete, his ability to affect it is impaired due to the direction already taken by the designers, as well as the pressure to meet schedule.

Therefore, if is were possible to approach a goal of on-line reliability, maintainability and testability (RM&T) effectiveness feedback to a designer while he is making other related design decisions (such as ASIC/SW, analog/digital, Hybrid/PC, ...) then it would be more likely that the appropriate decisions would be made during the detailed design phase. It is thus a purpose of this program to determine the feasibility of integrating RM&T analysis with computer—aided electronic design tools. Since such tools will continue to be developed, it was important to determine whether the interface of such tools, such as the interconnection list, could be exploited for RM&T analysis.

The R&M Design Expert System (F30602–91–C–0159) was a three—year contract with the United States Air Force/Rome Laboratory to explore issues related to coupling knowledge—based system tools with CAD/CAE tools. The program focused knowledge—based system techniques on improving testability in design(including testpoint selection/review, test scenario and equipment selection, and verification), and using information from testability, reliability, and maintainability (called TR&M analysis). Martin Marietta demonstrated these techniques in analog power design using the following tools:

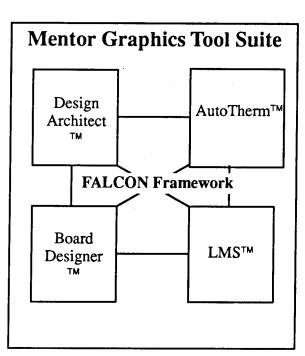

- Mentor Graphics' Falcon Framework™ with Design Architect™ to represent and analyze electronic system designs

- Analogy Inc.'s Saber™ analog circuit simulator to collect data

- Inference Corp.'s ART–IM™ knowledge—based system tool.

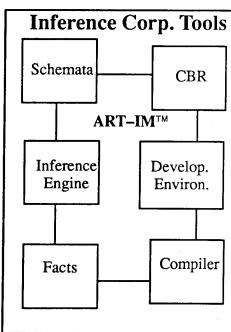

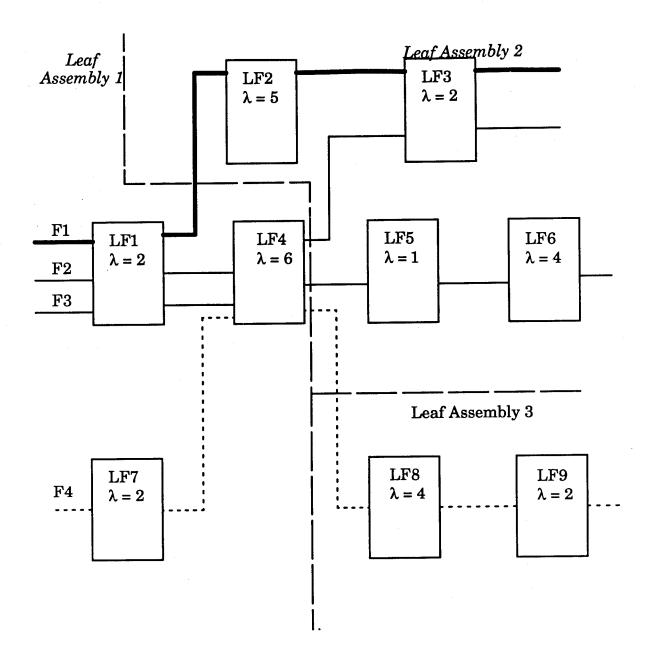

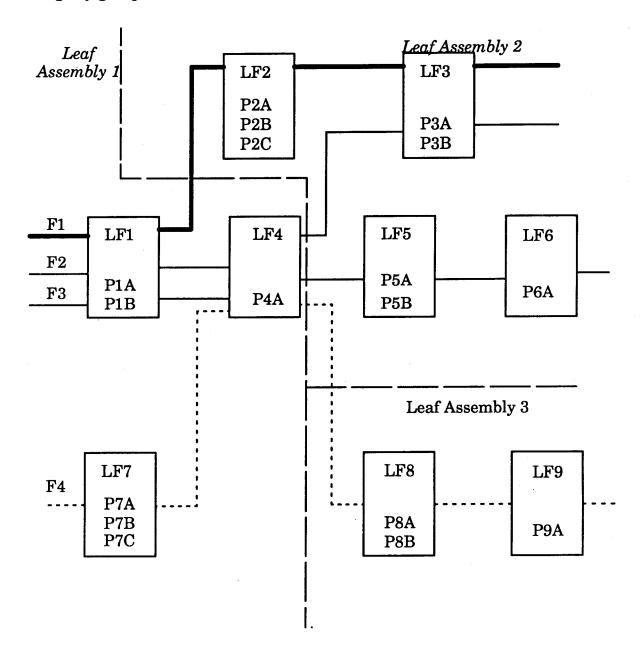

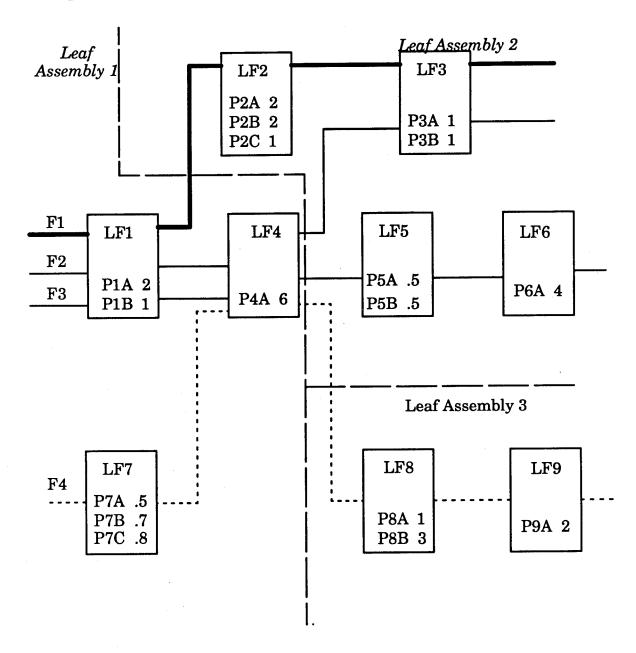

Figure 1. Program objectives.

Figure 1 shows the program objectives, which included developing an experimental system that captures key TR&M knowledge to provide designers, or other potential users within the electronic system design community, with a "what if" exploration capability in a CAD/CAE loosely "coupled" framework. This capability could eventually be fully embedded with the design tool environment.

We tested the R&M Design Expert System on a power supply design from Martin Marietta's AstroSpace division. This power supply consisted of six functional blocks:reset block, power control block, shutdowns, input stage, transformers, and a regulator. The total number of components was approximately 400.

## 1.2 The R&M Design Expert System Concept

Our review of the design and tools available to aid the TR&M process showed that applying knowledge—based system techniques impacted testability the most. There are numerous reliability tools available to electronic system designers, but few tools that aid the design with functional testability.

The R&M Design Expert System concept only addresses the diagnosability subset of maintainability; specifically test coverage (e.g., can the system detect and isolate the fault(s) given the testpoints and associated measures?). The system concept focuses on improving testability in design (including testpoint selection/review, test scenario and equipment selection, and verification), and TR&M analysis (diagnosability subset – test coverage only). The R&M Design Expert System has four main system modules. Though we present it in this document as a serial process for discussion purposes, the system can be thought of as a body of shared, interacting knowledge about TR&M, wrapped around a set of "core tools" that use information available from design data.

## 1.3 Report Overview

Section 2 provides background, including a discussion the human process in design, a survey of available reliability,testability and maintainability tools, and an in–depth look at the testability process.

Section 3 provides an overview of the system concepts and methodologies, including a discussion of our unique TR&Methodology and its application in the Supportability Analysis subsection.

Section 4 details implementing the R&M Design Expert system.

Section 5 discusses the "lessons learned" during the program.

Appendix A list the project deliverables.

## 2. Background

### 2.1 The Human Process in Design: An Overview

The design process, starting with a specification for a module of an electronic system, may include a design engineer, mechanical engineer, reliability and maintainability engineer, testability engineer, and parts control specialist. In this context, module refers to an electronic system part dedicated to a particular function within the design. For example, the power supply is one module of an electronic system.

### 2.1.1 The Specification

In most cases, the specification for an electronic system will:

- Define system requirements, including electrical performance (e.g., input power, output power, fault performance), physical characteristics (e.g., weight, dimensions, connectors), reliability and maintainability requirements, environmental requirements and stress screening, and design and construction materials and processes. Maintainability requirements typically include specific testability requirements, (e.g., fault detection and fault isolation).

- Specify documents applicable to the design process. These may include military standards and handbooks as well as non-government documents such as manuals and procedures guides. For example, MIL—STD—1629, "Procedures for Performing Failure Mode Effects and Criticality Analysis (FMECA)" and MIL—HDBK—217, "Reliability Prediction for Electronic Equipment," are commonly required with respect to reliability. MIL—STD—471, "Maintainability Verification/Demonstration/Evaluation" and MIL—STD—2165, "Testability program for Electronic Systems and Equipment," address maintainability and testability issues.

- Specify quality assurance provisions, such as special tests and examinations, test procedures, equipment, and facilities.

## 2.1.2 The Design Process with Testability Reliability & Maintainability (TR&M) in Mind

Design engineers usually begin the design process by creating a functional block diagram of the design task based on the module—level specification. Following a concept review, each block is designed in detail and the results used to generate a detailed schematic and parts list (usually using a CAD system). A parts control specialist (if part of the team), helps select parts. The parts specialist provides preferred parts, derating and screening criteria, and specifications and source control drawings for specialty parts. (The customer typically stipulates a system—level derating when it is desirable. Derating refers to using an item whose applied stresses are below the rated values or lowering the rating of an item in one stress field to allow an increase in another stress field.) Careful parts selection is one of the primary TR&M efforts during early design stages.

The parts specialist selects the parts and decides the screening process the parts will undergo. The reliability reflects these choices. For example, if the design engineer selects a part for which no military drawing exists, the design engineer will ask the parts specialist if the new part will work under the required conditions. If it will work under the conditions, a specification control drawing describing the types of screening to be done to the part will be made. (In the screening process the part may be burned in, tested, temperature cycled, etc.) Screening enhances the reliability of the part by eliminating, early in the process, specific pieces that may fail from the batch. Screening does not qualify a part type or batch for a higher reliability rating, however.

Concurrent with the detailed electrical design process, the mechanical engineer creates a design for packaging the product to meet environmental and maintainability requirements. This includes power stresses and thermal analysis that may impact both the reliability and electrical performance of the design.

## 2.1.2.1 Reliability

The reliability engineer becomes part of the design process upon a completion of a preliminary parts list, preliminary electrical design, and preliminary mechanical design. Parts must withstand many stresses - temperature, voltage stresses, etc. - that affect their reliability and which must be accounted for by the reliability engineer. To complete the Failure Modes and Effects Analysis (FMEA), possibly with the help of an automated reliability prediction tool, the engineer:

Analyzes operational requirements from the specification (e.g., the system will be used in 70°F at 50% humidity)

- Application requirements stipulated by the design engineer (e.g., apart will be used at 24 volts as opposed to its max rating of 36 volts)

- The parts lists, schematics, and other pertinent documents.

The FMEA analysis is used to predict the effect of failures on system operation. Once the FMEA is complete, the reliability engineer then adds criticality factors and executes MIL—STD—1629 (the FMECA), which is the procedure to assure adherence to MIL—HDBK—217. The FMECA is used to predict the effect of failures on system performance (e.g., effect on mission criticality). It is of little use during the design process because it offers little benefit to module—level fault isolation.

Reliability prediction is done on a given board according to the parts list. It is not check—on functional design; passing the reliability test does not guarantee that a design will work satisfactorily. Note that the interaction between the reliability engineer and others in the design process is often a one—way communication - most often from the design engineer to the reliability engineer. In most cases, if the design meets the specification, the reliability engineer will not suggest design changes since a pass or fail is all that is necessary for the design.

#### 2.1.2.2 Testability

Design practices that enhance design testability include: partitioning circuits, analyzing feed—back loops, and providing test points. If a testability engineer is on the design team, the entrance of the engineer into the process varies and is influenced by several factors. The most important of these is the testability requirements specifications. The system specification sets forth comprehensive testability performance requirements. Testability engineering support is a crucial role early in the system design process. Testability engineers, therefore, are part of a concurrent design effort. From the beginning the process is driven by the specification, in which test requirements are clearly defined for all levels of maintenance.

The maintenance level is defined by who or what detects a failure, where the repair or replacement will be done, and what maintenance actions will take place. For example, usual maintenance levels include:

- User Level- The user will detect fault but will not isolate or repair

- On—Site Repair Team Trained maintenance technician confirms failure, isolates the fault to a line—replaceable unit (LRU), and replaces the unit

- Shop Repair The LRU is taken to a local shop where further fault isolation can be done down to the shop-replaceable unit (SRU)

- Depot or Factory Repair If economically repairable, the SRU is sent back to the factory where the fault will be traced to the component, which is then replaced. Fault isolation is often the most important parameter at the depot–level testing of a module.

The standard for testability analysis is MIL-STD-2165, which describes a structured process to evaluate testability performance. The primary testability performance parameters are fault detection coverage, fault isolation, and false alarm percentage. The system specification should set values for these performance parameters by identifying pertinent requirements at each maintenance level. For example, a specification may address three of the maintenance levels as follows:

- Unit (on-site repair) Detection 97% Isolation to LRU 95% Alarm5%

- Shop Detection n/s -Isolation to 1 SRU 97% Alarm n/s

- Depot or Factory Detection/s Isolation to 1 Part 80% Alarm n/s

n/s = none specified

In this case, a fault detection rate is set at 97%; a 95% rate is required to isolate the detected fault to the LRU with no more than a 5% false alarm rate. If the system is brought to a repair shop with a detected fault, the isolation rate to a single SRU must be 97%. Similarly, the depot or factory should be able to isolate the fault to a single part 80% of the time. The testability engineer influences the system design so that these criteria can be met.

## 2.1.2.3 Test Point and BIT Selection

Hardware test point and software test selection on the final product is generally based on five factors:

- 1. Mechanical accessibility considerations

- 2. Testability requirements and analyses

- 3. Hardware/software test design trade-offs

- 4. Test equipment capabilities

- 5. Cost of the test and repair processes.

Test points are required when part of the system cannot meet its fault detection/ isolation requirements. Test point selection is the result of a trade—off analysis. At the module (or board) level, the first issue is how the module will be tested. For example, a board with a processor and built—in—test (BIT) capability may not be able to execute its built—in—self—test when plugged in to a depot's automated test equipment (ATE), which the depot will use for module—level testing. ATE, without built—in—probe or bed—of—nails—test capability, may also require that test points be brought to connectors. There is a practical limit to the number of test points which can be brought out, and it is usually a small fraction of the number of internal nodes that are candidate test points. Therefore, test point selection is often based upon the weighting of the test value of each candidate node, where the weighting criteria includes predicted failure rates for the components in the fault isolation path (FMEA data), and the richness of the diagnostic information contained in the signal at the testpoint.

In an organization (or project) that does not include testability engineers, the design engineer may select tests and test points. Normally, these will be selected to serve the particular needs of the design engineer in the design process, i.e., to determine if the design will work. The design engineer may not consider fault detection and isolation concerns or, if considered, may not have the tools or knowledge to make effective trade—off decisions.

If concurrent engineering practices are observed, the test engineering group of the manufacturing operation (the people concerned with quality assurance for the system) may choose the tests and test points. They will emphasize system performance verification - not fault detection and isolation. Their test and test point selection will often be based on the nature of the ATE available to them in house so that they can easily hook up and exercise a system. If given input yields expected output, the system will be passed. If a problem is discovered and fault isolation is required, the system is failed and will be sent back to engineering for lab testing.

The ideal case for specification of the tests and test points is a testability engineer aware of the specification's requirements for fault detection and isolation, the FMEA results, the system design, the levels of maintenance required, etc. The testability engineer will combine this information into a cogent basis for test point and test selection at the LRU level. Often this is done with the assistance of automated tools for fault coverage prediction. Several tools exist commercially, and Martin Marietta's Automated Systems division developed tools for this ap-

plication. Each tool has its limitations, caveats, and weaknesses and must be thoroughly understood by users for the results to be valuable. Unfortunately, FMEA results are rarely available in time to be of use in this process. Frequently the design has already gone to production before the FMEA results are completed.

Traditionally, the specifications do not designate what technique is required for testability at the board level. The idea of ATE is relatively new and is an answer to the growing complexity of electronic systems. As ATE become more common, so are detailed testability requirements. For example, the Navy now requires equipment to be designed to be testable on ATE called Consolidated Automated Support System(CASS), the Navy standard test equipment (see below under Automated Test Equipment - Army and Navy Standards). The specification for CASS describes what tests are possible. When fault detection and isolation are considered, the designer should be aware of ATE capabilities to assist in the trade-off of the testpoints. Designers will not design a module to be tested by ATE, but will consider the capabilities and limitations of ATE in developing the support strategy and establishing test coverage within the design.

If done properly, fault detection and isolation requirements at the system level will, in large part, define the requirements at lower maintenance levels. This means establishing the scheme for maintenance by the time the board level is reached. The strategy from the beginning of a proper design process is that the testing specified at the system level by the systems engineer will establish the typeof testing to be done at the subsystem level. These requirements, in turn, drive the type of testing that will be required at the board level. In other words, the test points and tests selected will be those required to meet the needs of the subsystem plus those necessary to fault isolate the particular board.

Tests supported at the system level may have little impact at the module or board because the software available at the system level is not available at the module level. This can make the module—level fault isolation requirements independent from system—level test considerations. Designer in such a case must trade off the value of the board—level fault isolation versus the cost of adding more hardware to the design. Cost usually wins.

If FMEA or FMECA results are available as input to the test and test point selection process, they allow the testability engineer to put fewer testpoints on more of the reliable circuits and vice versa. The magnitude of this change in the test point mix could be as much as ten percent, allowing the engineer to fine—tune the testpoint selection. In addition, the FMEA data may reveal areas that require real—time testing to prevent catastrophic failure. For example, a sensitive circuit that overheats if current is maintained at a certain level could be

protected by a test circuit which alerts the power supply controller of the overheating condition. The controller could then cut power, thereby maintaining board integrity.

## 2.1.2.4 Automated Test Equipment -Army and Navy Standards

The Navy is standardizing on the CASS being built by Martin Marietta in Daytona Beach. CASS provides support for both analog and digital electronic equipment, including radar, navigation gyros, and electro—optic devices. CASS is intended to be a total vertical package; the same instruments and test program sets (TPSs) can be used at certain designated levels of maintenance. (A TPS is the software required to support any interconnect device to the test equipment). A factory element of the CASS system will be developed to enable suppliers of Navy equipment to have a CASS in house. Suppliers may then write TPSs for their own systems, which will support CASS' verticality by providing common software support across maintenance levels.

Similarly, the Army ATE standard is the Intermediate Forward Test Equipment(IFTE) built by Grumman. The objective of IFTE is the same as that of CASS, but IFTE uses a different architecture and implementation and does not offer a total vertical solution. IFTE's components include: 1) a true fixed intermediate system (a rack system), and 2) a base shop test facility (BSTF), which is a van with some complement to the test equipment mounted inside.

### 2.1.3 Summary

Designing electronic systems to meet TR&M requirements requires specialists from the beginning of the design effort. To the extent that TR&M engineers are not involved concurrently in the process, TR&M issues are likely to be disregarded or postponed until it is too late to take effective measures.

The design engineer begins the design process by creating a functional block diagram of the design task. Each block is designed in detail and the results are used to generate a detailed schematic and parts list (usually using a CAD system). If parts control specialists are a part of the design team, they help select parts. Concurrent with the detailed electrical design, the mechanical engineer creates a design for packaging the product to meet environmental and maintainability requirements.

Reliability design is driven by specification requirements that commonly include government standards for reliability. MIL—STD—1629 (Procedures for Performing Failure Mode Effects and Criticality Analysis — FMECA) and MIL—HDBK—217 (Reliability Prediction for Electronic Equipment) address reliability. Using a preliminary parts and electrical design produced by the design engineer, the R&M engineer completes a FMEA. This analysis is used to predict the effect of failures on the system operation. Once the FMEA is complete, the R&M engineer adds criticality factors and execute MIL—STD—1629, which is the FMECA procedure to assure adherence to MIL—HDBK—217.

Design for test typically includes practices to enhance testability, circuit partitioning, feed—back loop analysis, and providing test points. The standard for testability analysis is MIL—STD—2165, which prescribes a structured process to evaluate testability performance. The primary testability performance parameters are fault detection coverage, fault isolation, and false alarm percentage. Hardware test point and software test selection on the final product is generally based on five factors:

- 1. Mechanical accessibility considerations

- 2. Testability requirements and analyses

- 3. Hardware/software test design trade-offs

- 4. Test equipment capabilities

- 5. Cost of test and repair processes.

Test points are required when part of the system cannot otherwise meet its fault detection/isolation requirements. In the ideal case, a testability engineer aware of the specification's requirements for fault detection and isolation, the FMEA results, the system design, the levels of maintenance required, etc., combines this information into a cogent basis for test point and test selection at the LRU level. Often this is done with the assistance of automated tools for fault coverage prediction.

## 2.2 A Survey Of The Tools That Aid The Design Process

#### 2.2.1 Overview

This section contains the results of a survey for TR&M circuit analysis tools potentially useful to analog circuit designers.

Included are tool descriptions with brief evaluations, a discussion on concurrent tools, and how tools specific to R&Mare used and fit into the general realm of electronic design.

### 2.2.2 Concurrent Engineering And Embedded Tools

"Concurrent engineering is an approach to design, manufacture, and support that emphasizes interaction and communication among the various agents involved in these processes. The general nature of this approach is to restructure the design process from one geared toward iterative, sequential tasks into one emphasizing incremental, cooperative processes." [4]

True concurrency has yet to be fully realized in CAD/CAE tools; the single most important aspect of a software product has been its ability to satisfactorily perform its designated function. Only recently have vendors concerned themselves with the first step required to build a concurrent tool: the tool's ease of use and ability to transfer data within and between existing tools.

The ease of data transfer of any software product is directly related to whether it executes on the same platform as other required software. In this case it means that the value of a circuit analysis tool is strongly linked to its availability on the same platform as other CAD/CAE tools. Platforms are now multi–faceted and include windowing software packages and operating system and hardware combinations. Popular examples of windowing packages for engineering workstations include X Windows (including several standards such as Openlook and Motif) and Microsoft Windows. Popular hardware/operating system combination platforms include IBM (DOS), SUN Microsystem (Solaris, Sun OS), VAX/VMS (DCL), etc.

The need for data transfer has led to families of integrated circuit analysis tools offered by a single vendor. The enormous benefit of integrating software tools is clear. When possible, these analysis tools could be integrated with the circuit design tools for a further optimized design flow.

Where complete integration is impossible or impractical, a common platform at least makes inter—machine transfers unnecessary, and also provides a foundation to develop automated format translation programs to patch the data flow. Often such programs require minimal effort to develop, but require the common platform.

A tool with more automated data entry and more flexible file formats is more appealing, as is one that is easy to learn and more user—friendly. These criteria can be used to decide between two tools that have both satisfied the more important requirements.

### 2.2.2.1 Reliability Analysis

Reliability is defined as "the conditional probability, at a given confidence level, that equipment will perform its intended functions satisfactorily or without failure, i.e. within specified performance limits, at a given age, for a specified length of time, function period, or mission time, when used in the manner and for the purpose intended while operating under the specified application and operation environments with their associated stress levels." [4]

"Reliability engineering provides the theoretical and practical tools whereby the probability and capability of parts, components, products, and systems to perform their required functions in specified environments for the desired period without failure can be specified, designed—in, predicted, tested, and demonstrated, and the results fed back to engineering, manufacturing, quality control, inspection, testing, packaging, shipping, purchasing, receiving, sales, and service for improvements and necessary corrective actions." [3]