ADA131358

RADC-TR-83-72 In-House Report March 1983

# THE EVOLUTION AND PRACTICAL APPLICATIONS OF FAILURE MODES AND EFFECTS ANALYSES

Heather B. Dussauit

APPROVED FOR PUBLIC RELEASE: DISTRIBUTION UNLIMITED

ROME AIR DEVELOPMENT CENTER Air Force Systems Command Griffiss Air Force Base, NY 13441

DTT. FILE COPY

83 08 15 080

This report has been reviewed by the RADC Public Affairs Office (PA) and

This report has been reviewed by the RADC Public Affairs Office (PA) and is releasable to the National Technical Information Service (NTIS). At NTIS it will be releasable to the general public, including foreign nations.

RADC-TR-83-72 has been reviewed and is approved for publication.

APPROVED:

ANTHONY J. FEDUCCIA

Chief, Systems Reliability & Engineering Branch

Reliability & Compatibility Division

APPROVED:

EDMUND J. WESTCOTT Technical Director

Reliability & Compatibility Division

FOR THE COMMANDER: <

JOHN P. HUSS

Acting Chief, Plans Office

If your address has changed or if you wish to be removed from the RADC mailing list, or if the addressee is no longer employed by your organization, please notify RADC (REET ) Griffies AFB NY 13441. This will assist us in maintaining a current mailing list.

Do not return copies of this report unless contractual obligations or notices on a specific document requires that it be returned.

# UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered)

| REPORT DOCUMENTATION PAGE                                                                                                        | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                    |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1. REPUAT HUMBER 2. GOVY ACCESSION NO.                                                                                           | 1. RESIPIENT'S CATALOG NUMBER                                  |

| RADC-TR-83-72 AD-413135                                                                                                          | > <i>X</i>                                                     |

| 4. TITLE (und Subtitle)                                                                                                          | S. TYPE OF REPORT & PERIOD COVERED                             |

| THE EVOLUTION AND PRACTICAL APPLICATIONS                                                                                         | In-House Report                                                |

| OF FAILUKE MODES AND EFFECTS ANALYSES                                                                                            | 6. PERFORMING ORG. REPORT NUMBER                               |

|                                                                                                                                  | N/A                                                            |

| 7. AUTHOR(a)                                                                                                                     | 8. CONTRACT OR GRANT NUMBER(s)                                 |

| Heather B. Dussault                                                                                                              | N/A                                                            |

| neather D. Dubbage                                                                                                               | N/A                                                            |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS                                                                                      | 10. PROGRAM ÉLEMENT, PROJECT, TASK<br>ARÉA & WORK UNIT NUMBERS |

| Rome Air Development Center (RBET)                                                                                               | 62702F                                                         |

| Griffiss AFB NY 13441                                                                                                            | 23380212                                                       |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                                                                                          | 12. REPORT DATE                                                |

| Done Alm Devel annual Control (DDDD)                                                                                             | March 1983                                                     |

| Rome Air Development Center (RBET) Griffiss AFB NY 13441                                                                         | 13. NUMBER OF PAGES                                            |

| 14. MONITORING AGENCY NAME & ADDRESS/II different from Controlling Office)                                                       | 18. SECURITY CLASS. (of this report)                           |

| Manifestine neglect frame a neglectic characteristic control                                                                     |                                                                |

| Same                                                                                                                             | UNCLASSIFIED                                                   |

|                                                                                                                                  | 184. DECLASSIFICATION/DOWNGRADING                              |

| 15. DISTRIBUTION STATEMENT (of this Resert)                                                                                      | N/R                                                            |

| Approved for public release; distribution unlim                                                                                  | ited.                                                          |

| 17. DISTRIBUTION STATEP'ENT (of the abetract entered in Block 30, if different free Same                                         | n Report)                                                      |

| 18. SUPPLEMENTARY NOTES                                                                                                          |                                                                |

| None                                                                                                                             |                                                                |

|                                                                                                                                  |                                                                |

|                                                                                                                                  |                                                                |

| 19. KEY WORDS (Continue on reverse side if necessary and identify by birack number)                                              |                                                                |

| FMEA Techniques Sneak Circuit A                                                                                                  | nalysis                                                        |

| Failure Mode Failure Analysis                                                                                                    | s                                                              |

| Failure Effect Matrix FMEA                                                                                                       |                                                                |

| Fault Tree Analysis                                                                                                              |                                                                |

| A. ABSTRACT (Continue on reverse side if necessary and identify by black number) Failure effects analysis allows a product to be | studiod souls: in the                                          |

| design and development stages where undesirable                                                                                  |                                                                |

| identified and readily corrected. This report                                                                                    |                                                                |

| reader a broad, general background in technique                                                                                  |                                                                |

| effects analysis and their usefulness. Sixteen                                                                                   |                                                                |

| ranging from tabular failure modes and effects                                                                                   |                                                                |

| analysis to lesser known and more recently intro                                                                                 |                                                                |

DD 1 JAN 73 1473 EDITION OF 1 NOV 65 IS GESOLETE

UNCLASSIFIED

**UNCLASSIFIED** SECURITY CLASSIFICATION OF THIS PAGE (When Days Error hardware/software interface analysis, are discussed. The current status and prospects for the future of failure effects analysis are also discussed in the report.

UNCLASSIFIED

SECURITY CLASSIFICATION OF THE PAGE (When Date Entered)

#### **PREFACE**

This report surveys the evolution of failure effects analysis techniques from the 1950s to the present. Widely used and established techniques as well as state-of-the-art developments are presented. This report is meant to give the reader a broad, general background in techniques available for failure effects analysis and their usefulness. The report should also give the reader an appreciation of the value of failure effects analysis to the related areas of systems analysis such as: maintainab??ity analysis; testability analysis; reliability predictions; safety analysis; failure analysis; and logistics support.

#### OLO EXECUTIVE SUMMARY

## FAILURE EFFECTS ANALYSIS TECHNIQUES

Failure effects analysis is a very broad area of systems analysis. Simply, a failure effects analysis is an organized and logical study of how a system reacts to failures. Because of the diversity of systems and the range of results which can be obtained, many different techniques have been developed for failure effects analysis. Ultimately, failure effects analysis is a design tool, indicating the strengths and weaknesses in a system design and providing information for allied analyses in maintainability, testability, logistics, reliability prediction, and safety.

#### COMMONLY USED FAILURE EFFECTS ANALYSIS TECHNIQUES

The most commonly used techniques for a failure effects analysis are the tabular Failure Modes and Effects Analysis (FMEA), fault tree analysis, matrix FMEA, and sneak circuit analysis.

# Tabular FMEA

The tabular FMEA is the grandfather of all other failure effects analysis techniques. The tabular FMEA employs a very simple approach. A table, or worksheet, is used to itemize every probable failure mode and its resulting effect. The specific information contained on the worksheet can be tailored to the individual system, but usually includes: item identification, failure mode, probable failure causes, failure effect, method of fault detection, and any remarks concerning corrective actions or design changes. The level of detail contained in the analysis

is determined by the availability of information and the intended application of the results. The analysis can also include an evaluation of the relative importance of failure modes based upon the severity of their effect on the system and their probability of occurrence. The combined analysis is then referred to as a Failure Modes, Effects, and Criticality Analysis (FMECA). FMEA/FMECA is a very versatile technique. It can be used to analyze any system at any stage in its design.

# Fault Tree Analysis

MALAKAKAN MENENDIAN MENENDIAN PERENDIAN MENENDIAN MENEND

Fault tree analysis was so named because the completed analysis resembles a many branched tree. In fault tree analysis a specific undesirable system state or failure (top event) is defined. The fault tree is then developed using deductive reasoning and the principles of Boolean logic. Beginning with the defined top event, the immediate causes of the event are identified and connected to the event by logic operators. Each of the immediate causes then becomes the event to be developed in similar fashion. The fault tree continues to branch out until only events which cannot be further developed remain. Once the fault tree has been constructed it can be analyzed using Boolean algebra to identify which combinations of events result in the occurrence of the undesired event. Like tabular FMEA, fault tree analysis is a versatile The fault tree, however, represents a distinct departure technique. from the tabular FMEA because it uses deductive reasoning rather than inductive and it examines combinations of failures and externally influenced failures.

## Matrix FMEA

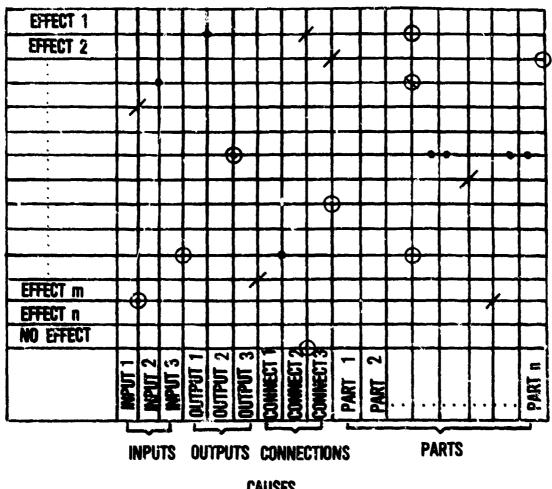

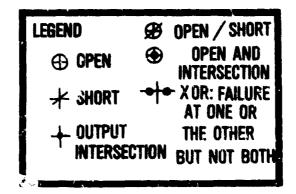

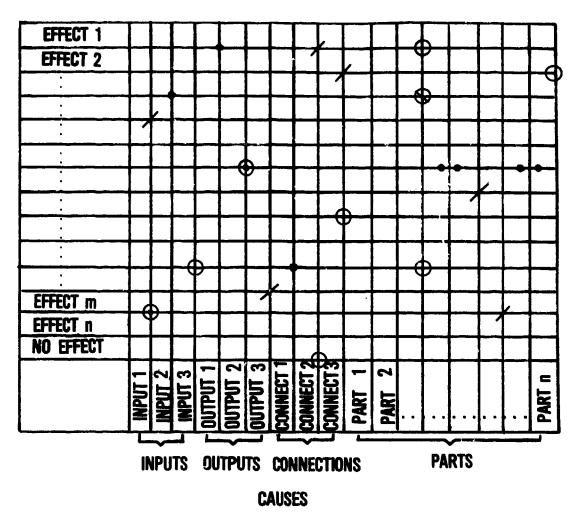

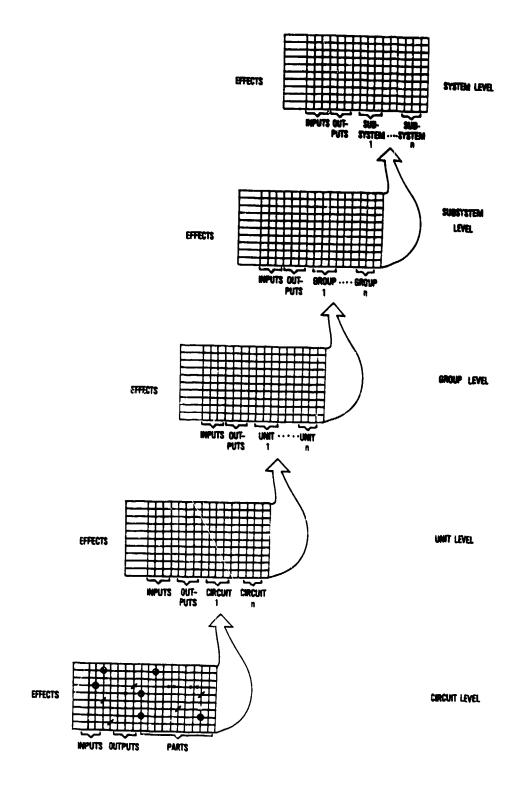

Matrix FMEA is very similar to a tabular FMEA in intent, but differs in its approach. A matrix FMEA is performed using a gridded plot to graphically indicate the relationship of failure modes and failure effects. The horizontal axis of the grid is used to represent inputs, outputs, connections, and parts of the system. The vertical axis of the matrix is used to identify the failure effects. A symbol is placed at grid locations at which the failure of the corresponding part on the horizontal axis produces the associated effect on the vertical axis. Different symbols are used to represent different failure modes. sample matrix FMEA is shown in Figure 1. The analysis proceeds to higher levels of analysis in a "build-up" fashion. The most detailed level of analysis feeds directly into the next higher level analysis. The effects produced by the failure modes of the more detailed analysis become the sources of failure at the next higher level of analysis. The build-up process enables the cause of the ultimate system effects to be directly traced back to the most detailed information available. In short, Matrix FMEA has the versatility of tabular FMEA for electronic systems, and it can also be represented graphically.

FIGURE 1: MATRIX FMEA

**CAUSES**

THE CONTROL OF SECURITY OF SEC

# Sneak Circuit Analysis

をある。 「はながらないと、これではない。」というないが、「はないないない。」というないない。 「はないないない。」というないのでは、これではないない。

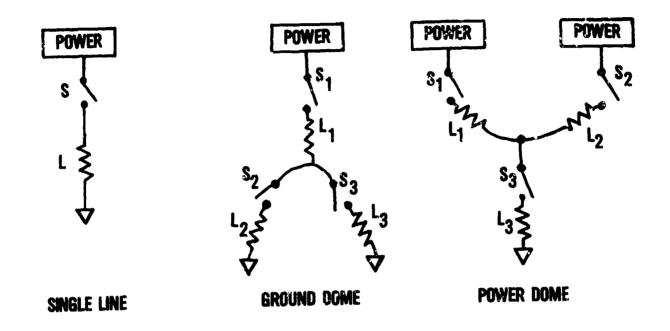

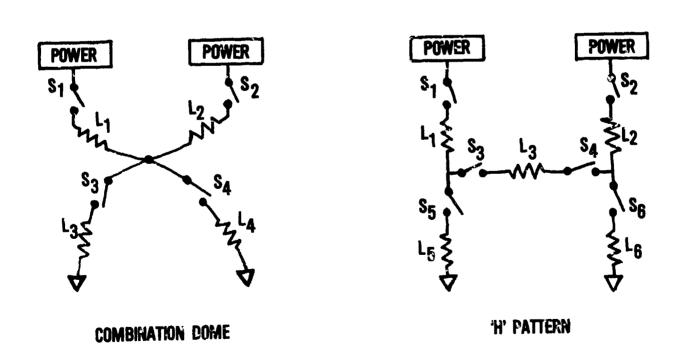

Sneak circuit analysis is used to find design errors which could result in improper or undesirable system operations. The analysis is performed in later design stages for detailed "as-built" circuitry. In sneak circuit analysis the circuit or flow system is characterized as a combination of standard topological patterns. Any circuit can be partitioned into the standard patterns. For each pattern a series of clues has been developed to aid the analyst in identifying the existence of sneaks. Sneaks can be found in four areas: 1) sneak path, which allows current to flow in the wrong direction; 2) sneak timing, which occurs when a circuit function happens at an unexpected time or does not happen when it should; 3) sneak label, which improperly identifies a control or measurement; and 4) sneak indication, which results in incorrect or ambiguous displays of system conditions. Sneak analysis is the only technique which examines design induced errors.

# LESSER KNOWN FAILURE EFFECTS ANALYSIS TECHNIQUES

The lesser known failure effects analysis techniques are not as widely used as the four techniques previously mentioned. That is not to say, however, that the lesser known techniques are not as useful for failure effects analysis.

# System State Phase Modelling

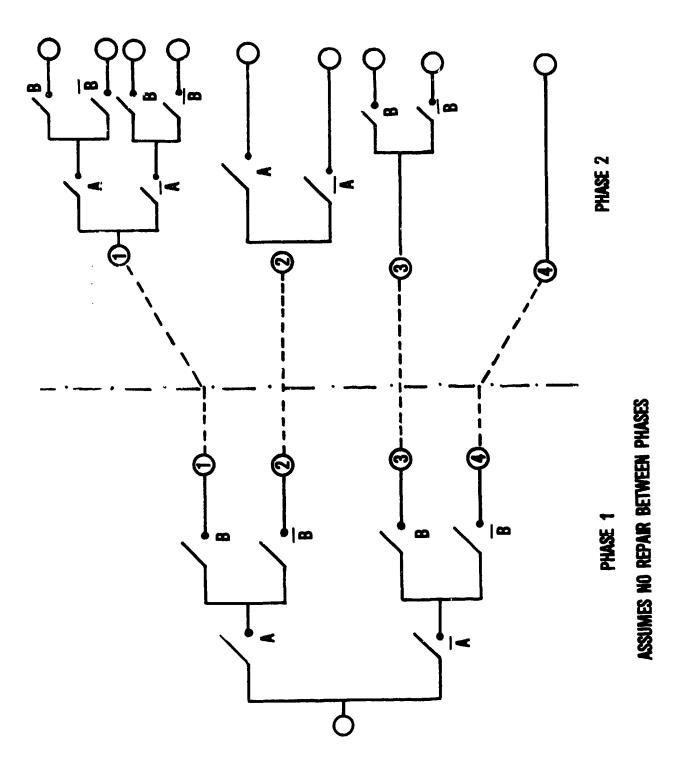

System state phase modelling uses a logic diagram to investigate all possible system states. The logic diagram resembles a tree with switches along each branch. Each switch represents a specific event's

occurrence. Each branch represents a particular order of events occurring in each of the system operating phases. All possible paths are considered for the first operating phase. The paths are then further developed for subsequent phases based upon the previous phases. Once a complete system failure has occurred in a path, the path is not further developed. The logic diagram includes paths for operational, degraded, and failed system states. Unlike previously discussed techniques, system state phase modelling allows the entire operational history of the system to be carried through the analysis.

# Tabular Systems Reliability Analysis

The second secon

CONTRACTOR DESCRIPTION OF THE PROPERTY OF THE

Tabular systems reliability analysis combines aspects of the tabular FMEA, fault tree analysis, and Markov chain theory. The analysis involves partitioning the system into ten or less functional blocks. A tabular format is used to identify all possible operating states for each functional block. The effects of combinations of states from each functional block are then evaluated. Much like fault tree analysis, an overall undesirable effect on the system can be defined, and all those combinations of states which produce the undesirable effect can be determined. Markov chain theory can then be used to numerically evaluate the probability of occurrence of the undesirable effect. Because only a small number of functional blocks are used, the analysis is not intended to be highly detailed. But, unlike tabular FMEA, the technique examines combinations of failures and provides a quantitative system analysis.

# **Event-Sequence Analysis**

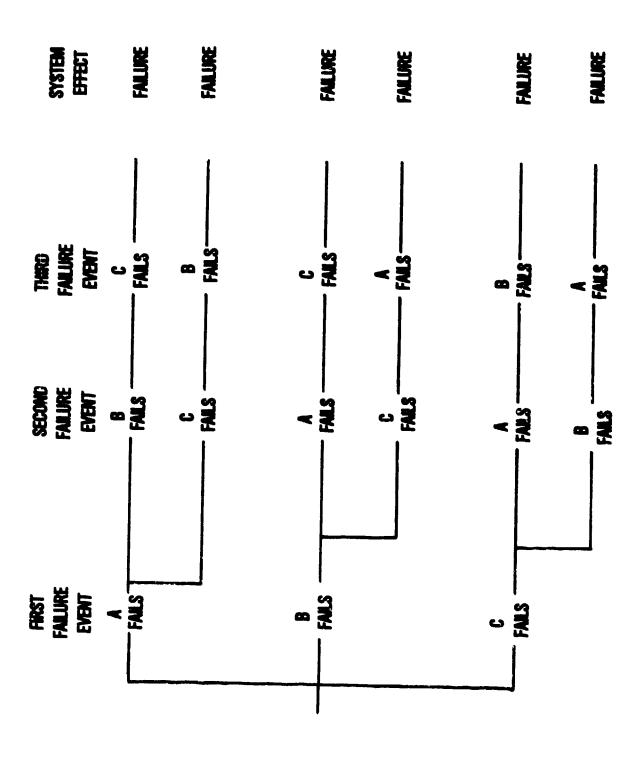

Event-sequence analysis traces the effects of system failures as a function of the order in which they occur. The event-sequence map is a tree-like structure; the branches of the map represent the time sequenced order of faults. The map shows all probable failure histories for system operation. All events examined in event-sequence analysis are dependent, (e.g., given that A and B have previously occurred, now that C has occurred, the effect on the system is ...). The event-sequence map is developed by investigating all possibilities for a first failure event, then all possibilities for a second failure event, and so forth until all branches of the map end in a system failure. Numerical evaluation can be made of the event-sequence map using conditional probabilities of event occurrences. Event-sequence analysis allows the dependencies of failures in a system to be logically analyzed.

# "Testability Analysis"

estables describe brokens brokens lacedes caracas brokens sobjets brokens caracas caracas caracas brokens

Testability analysis is actually a separate systems analysis from failure effects analysis. It has been suggested, however, that an automated program originally intended for testability analysis can replace the need for FMEA in electronic systems. An electronic circuit simulator, such as LAZOR or TEGAS 5, could also be used to simulate faults. The proprietary automated testability program uses detailed "as-built" design information to evaluate the effects of standard electronic failure modes for each part in the system circuitry. The program also evaluates the completeness of fault detection and isolation in the system. No

numerical evaluation or criticality evaluation is presently included in the automated program. The automated program can eliminate much of the effort and tedium involved in performing a tabular FMEA for circuitry. Additional tailoring information and analysis of unconventional failure modes would either have to be sacrificed or externally supplied.

# L.A.M. Technique

The LAM technique evaluates the effect of failures on a system by modelling how failures change the physical properties of the system. Both failed and operational system states are examined. Parametric equations are developed to model system response to failures based on the characteristic physical properties of the system. A specific undesired system state can be defined, and those conditions which can result in the undesired state can be defined either by operational status or by physical characteristics. The LAM technique can be used to provide an integrated analysis of both hardware and physical conditions. A system analyzed using the LAM technique, however, would have to be one that is easily modelled using physical parameters.

# Approachability Analysis

CANCELL RESERVED TO THE PARTY OF THE PARTY O

Approachability analysis is used to evaluate the effects of failures caused by approach. Failures caused by approach are failures caused by the improper relationship of parts, failures caused by the introduction of foreign materials into the system and failures caused by external stresses. The analysis uses a matrix format. Those items susceptible to failures caused by approach or likely to cause an approach are identified

along with external stresses. All items which will fail as a result of an approach are labelled objective parts and placed along one axis of the matrix. The approaching parts and external stresses are placed along the other axis of the matrix. Much as in matrix FMEA, those combinations of objective part and approaching part or external stress which result in a failure are marked. Design and layout changes can be suggested by the results of approachability analysis. Approachability analysis examines types of failures which are often overlooked but which can readily occur as a result of consumer use or operation in other stressful environments.

# Failure Combination Method

The failure combination method evaluates the effects of single, multiple, and externally influenced failures in a system. All the effects of single failures are obtained from a previously performed tabular or matrix FMEA. Those single failures and combinations of failures which produce the same effect are grouped together and called gathered fail-Externally influenced failures are defined as failures which occur in systems outside the analysis which affect the system under study. Overall failures are defined by combining the externally influenced failures and previously defined gathered failures which produce the same overall effect on the system. The grouping scheme allows single, multiple, and external failures which produce the same effect to be identified using an inductive approach.

# HARDWARE/SOFTWARE FAILURE EFFECTS ANALYSIS TECHNIQUES

Hardware/software failure effects analysis techniques have been developed to accommodate the growing need for failure effects analysis in complex hardware/software integrated systems. Hardware/software integrated systems have not proven to be amenable to the more conventional failure effects analysis techniques because of the vast number of possible system configurations.

## Software FMEA

AND THE PROPERTY OF THE PROPER

Software FMEA is very similar to tabular FMEA. Software FMEA defines the functional requirements of the software and then evaluates the causes for failure to meet those requirements and the effect that the function failure will have on the system. Finally, the feasibility of eliminating or guarding against unacceptable failures is investigated. Software FMEA is usually performed during early design stages to verify that software performance requirements are being properly implemented and to identify areas where redundancy or fault tolerance are needed.

# Software Sneak Analysis

Software sneak analysis is very similar to sneak circuit analysis, both in intent and approach. Software sneak analysis identifies design errors or "bugs" in system software. The flow of logic in a computer program is used for the sneak analysis. The logic flow pattern of a program is divided into combinations of the six standard software topological patterns. The same basic types of clues used in sneak circuit analysis are used for software sneak analysis. The results, however, are

much different. Besides locating branch bypasses and infinite loops, software sneak analysis can locate sneak outputs, sneak inhibits, sneak timing, and sneak messages.

# Integrated Critical Path Analysis

Integrated critical path analysis examines hardware/software interrelationships in a system. The technique combines aspects of tabular FMEA, fault tree analysis, and sneak circuit analysis. Integrated critical path analysis begins by developing network tree models, as is done in sneak analysis. The network trees indicate hardware/software interfaces and can be used to update previously performed fault tree analyses. The updated fault trees can then be analyzed to determine critical system failure paths. Operations and maintenance procedures are also reevaluated using a tabular FMEA approach. Finally, any relevant failure analysis is also incorporated into the integrated critical path analysis. Integrated critical path analysis offers a comprehensive evaluation of both hardware and software responses to system failures.

## Hardware/Software Interface Analysis

Hardware/Software interface analysis considers software requirements as a function of hardware failures. Because software cannot respond to unanticipated conditions, it is important to recognize every probable failure condition and to determine how the software should respond. Every failure mode in a previously performed FMEA is examined for potential hardware/software interface problems. A series of questions are asked of every probable failure mode to determine if software

anticipates hardware failures and provides workarounds, if software utilizes the full capability of the hardware, and if the software overstresses the hardware. Hardware/Software interface analysis examines how software can be used to improve system performance.

# Microcomputer FMEA

THE PROPERTY OF THE PROPERTY O

It is often difficult to determine the exact overall system effects resulting from a microcomputer failure. Different operating modes and memory configurations affect the way the system responds to a microcomputer failure. The microcomputer FMEA technique is performed on an operating system. A fault simulator is connected between the hardware system and the microcomputer. With the system running, the fault simulator generates a variety of faults (e.g., open and stuck at ground) for every input and output pin. The effect of each simulated fault can be entered on a tabular type FMEA worksheet.

#### THE STATUS OF FAILURE EFFECTS ANALYSIS

Failure effects analysis is often viewed as a necessary evil. The intent of failure effects analysis is to allow a system to be examined early in its development when undesirable failures can be identified and readily corrected. Unfortunately, the use of failure effects analysis is limited by problems in its application. The most common problems encountered in failure effects analysis include:

- . The analysis is time-consuming and costly;

- The analysis results and recommendations are often obtained too late in the design to be easily instituted;

- . Accurate failure data are difficult to obtain; and

- . The level of detail necessary for a thorough, economical and effective analysis is difficult to accurately determine.

The future of failure effects analysis belongs to the efficient. Efficient guidelines and techniques are needed for the full potential of failure effects analysis to be realized. Guidelines need to be efficient in detailing what is required for specifying, conducting, and reviewing a failure effects analysis. The techniques used for failure effects analysis need to be efficient in:

. time and cost,

- . thoroughness and accuracy; and

- applicability to related analysis areas, such as logistics, testability, and maintainability.

It is important that the potential of failure effects analysis to influence design and to support other analyses be recognized.

# TABLE OF CONTENTS

|       |                                                               | PAGE |

|-------|---------------------------------------------------------------|------|

| 1.0   | INTRODUCTION                                                  |      |

| 1.1   | Background                                                    | 1    |

| 1.1.1 | Why Failure Effects Analysis?                                 | 1    |

| 1.1.2 | Failure Effects Analysis Definition                           | 1    |

| 1.1.3 | Role of Failure Effects Analysis in<br>Design and Development | 2    |

| 1.1.4 | Scope of Report                                               | 2    |

| 1.2   | General Comments on Failure Effects Analysis                  | 3    |

| 1.2.1 | Problems with Failure Effects Analysis                        | 3    |

| 1.2.2 | General Suggestions for Failure Effects<br>Analysis           | 4    |

| 1.3   | Types of Failure Effects Analysis                             | 5    |

| 1.3.1 | Specific Techniques                                           | 5    |

| 1.3.2 | Related Guidelines/Materials                                  | 7    |

| 1.4   | Format of Report                                              | 7    |

| 2.0   | CLASSICAL TABULAR FMEA TECHNIQUES                             | 9    |

| 2.1   | Tabular FMEA                                                  | 9    |

| 2.1.1 | History of Tabular FMEA                                       | 9    |

| 2.1.2 | General Procedure for Tabular FMEA                            | 9    |

| 2.1.3 | Failure Effects Analysis Worksheet                            | 11   |

| 2.1.4 | Related Documents                                             | 12   |

| 2.1.5 | Tabular FMEA Developments                                     | 13   |

| 2.1.6 | Relative Merits of Tabular FMEA                               | 15   |

|       |                                                                       | PAGE |

|-------|-----------------------------------------------------------------------|------|

| 2.2   | Criticality Analysis                                                  | 16   |

| 2.2.1 | History of Criticality Analysis                                       | 16   |

| 2.2.2 | Procedure for Criticality Analysis                                    | 17   |

| 2.2,3 | Developments in Criticality Analysis                                  | 20   |

| 2.2,4 | Relative Merits of Criticality Analysis                               | 22   |

| 2.3   | Hazard Analysis                                                       | 23   |

| 2.3.1 | Preliminary Hazard Analysis                                           | 23   |

| 2.3.2 | Operations Hazard Analysis                                            | 24   |

| 2.3.3 | Fault Hazard Analysis                                                 | 25   |

| 2.3.4 | Relative Merits of Hazard Analysis                                    | 26   |

| 3.0   | FAULT TREE ANALYSIS                                                   | 29   |

| 3.1   | History of Fault Tree Analysis                                        | 29   |

| 3.2   | General Procedure for Fault Tree Analysis                             | 29   |

| 3.3   | Fault Tree Developments                                               | 36   |

| 3.4   | Relative Merits of Fault Tree Analysis                                | 37   |

| 4.0   | MATRIX FMEA                                                           | 39   |

| 4.1   | History of Matrix FMEA                                                | 39   |

| 4.2   | Procedure for Matrix FMEA                                             | 39   |

| 4.3   | Developments in Matrix FMEA                                           | 43   |

| 4.4   | Relative Merits of Matrix FMEA                                        | 45   |

| 5.0   | SNEAK CIRCUIT ANALYSIS                                                | 47   |

| 5.1   | Relationship of Sneak Circuit Analysis to Failure<br>Effects Analysis | 47   |

| 5.2   | History of Sneak Circuit Analysis                                     | 47   |

|       |                                                       | PAGE |

|-------|-------------------------------------------------------|------|

| 5.3   | General Procedure for Sneak Circuit Analysis          | 48   |

| 5.4   | Developments in Sneak Circuit Analysis                | 50   |

| 5.5   | Relative Merits of Sneak Circuit Analysis             | 52   |

| 6.0   | LESSER KNOWN FAILURE EFFECTS ANALYSIS TECHNIQUES      | 55   |

| 6.1   | An Overview of the Lesser Known Techniques            | 55   |

| 6.2   | System State Phase Modelling                          | 56   |

| 6.3   | Tabular Systems Reliability Analysis                  | 59   |

| 6.4   | Event-Sequence Analysis                               | 61   |

| 6.5   | Testability Analysis                                  | 63   |

| 6.6   | LAM Technique                                         | 65   |

| 6.7   | Approachability Analysis                              | 66   |

| 6.8   | Failure Combination Method                            | 68   |

| 7.0   | HARDWARE/SOFTWARE FAILURE EFFECTS ANALYSIS TECHNIQUES | 71   |

| 7.1   | Introduction to Hardware/Software Techniques          | 71   |

| 7.2   | Software Techniques                                   | 71   |

| 7.2.1 | Software FMEA                                         | 71   |

| 7.2.2 | Software Sneak Analysis                               | 73   |

| 7.3   | Integrated Hardware/Software Analysis Techniques      | 74   |

| 7.3.1 | Integrated Critical Path Analysis                     | 75   |

| 7.3.2 | Hardware/Software Interface Analysis                  | 77   |

| 7.4   | Microcomputer FMEA                                    | 79   |

| 8.0   | OVERVIEW OF FAILURE EFFECTS ANALYSIS TECHNIQUES       | 81   |

| 8.1   | Summary of Techniques Discussed                       | 81   |

|        |                                                                    | PAGE |

|--------|--------------------------------------------------------------------|------|

| 8.2    | Current Status of Failure Effects Analysis                         | 84   |

| 8.3    | The Future of Failure Effects Analysis                             | 86   |

| 9.0    | BIBLIOGRAPHY                                                       | 89   |

|        |                                                                    |      |

|        | LIST OF FIGURES                                                    |      |

| FIGURE | TITLE                                                              | PAGE |

| 1.     | Matrix FMEA                                                        | vii  |

| 1.1    | Evolutionary Development of Failure Effects<br>Analysis Techniques | 6    |

| 2.1    | Sample Tabular FMEA Worksheet                                      | 14   |

| 2.2    | Criticality Matrix Schematic                                       | 21   |

| 3.1    | Fault Tree Symbols                                                 | 32   |

| 3.2    | Sample Fault Tree                                                  | 33   |

| 4.1    | Sample Matrix FMEA Sheet                                           | 41   |

| 4.2    | Build-up Process of Matrix FMEA                                    | 42   |

| 5.1    | Standard Topological Patterns Used for<br>Sneak Circuit Analysis   | 51   |

| 6.1    | System State Fhase Modelling Logic Diagram                         | 57   |

| 6.2    | Sample Event-Sequence Map                                          | 62   |

|        |                                                                    |      |

|        | LIST OF TABLES                                                     |      |

| TABLE  | TITLE                                                              | PAGE |

| 8.1    | Summary of Failure Effects Analysis Techniques                     | 82   |

| 8.2    | Summary of Failure Effects Analysis Techniques<br>Characteristics  | 83   |

#### 1.0 INTRODUCTION

THE PARTY OF THE P

#### 1.1. Background

## 1.1.1. Why Failure Effects Analysis?

In the Post-World War II era there were rapid technological advances, but product reliability did not keep up with advancing technology. The examination of failure modes and their effects was a natural outgrowth of the need to increase product reliability. Failure effects analysis allows a product to be studied early in its design and development stages where undesirable failures can be identified and readily corrected.

# 1.1.2 Failure Effects Analysis Definition

failure effects analysis is a very broad area of systems analysis. Very generally, a failure effects analysis can be considered an examination of a design or system in a logical and organized manner. The failure effects analysis can be applied through many approaches. The varied approaches include: an itemization of each part in the system and how each part can fail and the consequence of each failure; a characterization of the system by function and an analysis of how each loss of function would affect the system; a deductive analysis of exactly which failures or combinations of failures will result in an undesirable system state; or a time dependent model of dependent failures and their consequences. Failure effects analysis is a design tool. It can be applied to any system or any procedure which affects the system. An effective failure effects analysis presents a thorough examination of a

Downloaded from http://www.everyspec.com

system's strengths and weaknesses in a timely and understandable manner.

1.1.3. Role of Failure Effects Analysis in Design and Development

The failure effects analysis forms the cornerstone for many further systems analyses. The failure effects analysis provides: a data base for maintainability, logistics support, and safety analyses; a reference point and verification source for testability analysis; a basis for trouble-shooting procedures; a focal point for reliability predictions, even providing the analytical foundations and expressions for evaluation; and a basis for design changes or addition of redundancy in design. When implemented early in the design phases, the failure effects analysis can provide guidance for necessary design changes which otherwise would not become evident until much later in the development cycle. Failure effects analysis is also an iterative design tool. The analysis can evolve as the design evolves and can, when required, provide a means of evaluating proposed engineering design changes.

# 1.1.4 Scope of Report

CONTROL OF THE PROPERTY OF THE

This report will examine the techniques which can be used in a failure effects analysis. Only those techniques which represent a fundamentally different means for analyzing failure effects will be discussed in this report. Sensitivity and tolerance analyses will not be discussed in this report because they do not directly analyze failure causes and effects. Common cause, grounding, and accident analyses will not be treated as separate techniques, since different failure effects analysis techniques incorporate aspects of each analysis. The intent of

the report is to provide an overview of techniques available to assess the effects of failures on a system. The report surveys the evolution of failure effects analysis techniques from the 1950s to the present. Widely used and established techniques as well as state-of-the-art developments are presented. The report discusses the general procedure involved in each technique, developments within the technique, its applications and relative merits.

This report is not meant to be a "cookbook" to be used to perform a failure effects analysis. This report is meant to give the reader a broad, general background in techniques available for failure effects analysis and their usefulness. The report should also give the reader an appreciation of the value of failure effects analysis to the related areas of systems analysis such as: maintainability analysis; testability analysis; reliability prediction; safety analysis; failure analysis; and logistics support.

# 1.2 General Comments on Failure Effects Analysis

# 1.2.1 Problems with Failure Effects Analysis

A failure effects analysis is not intended to be the panacea for all poorly designed and operated systems. It is intended to be a design tool. As with all other analyses, failure effects analyses are subject to inconsistencies and inaccuracies. No one technique provides all the means for deriving a complete analysis for all products and systems. Each technique has a different approach with distinct advantages and disadvantages which dictate its use.

Failure effect analyses also have logistical problems. A failure effects analysis is often expensive, manpower intensive, and time consuming. Massive amounts of paperwork are often generated in the course of the analysis. Interfaces between the analyst and the design engineer are often tenuous, which results in an inefficient and sometimes inaccurate analysis.

# 1.2.2 General Suggestions for Failure Effects Analysis

AND THE PROPERTY OF THE PROPER

It is important to realize that while a failure effects analysis cannot do the entire job, every attempt should be made to assure that the analysis effort has been organized and exhaustive. Each technique presented in this report can be used in a failure effects analysis. No matter which technique is used, the following suggestions can help provide a design- and cost-effective analysis.

- 1. The failure effects analysis should be initiated as early as practical, dependent upon level of analysis and technique employed.

- 2. A thorough understanding of the system and of the analysis technique is necessary.

- 3. The failure effects analysis depends upon the support of management and good engineering practices.

- 4. The failure effects analysis should be performed for all operating modes and mission phases.

- 5. The failure effects analysis should be performed at increasing levels of detail as the design progresses.

- 6. The analysis should be traceable.

- 7. The failure effects analysis should be followed up and updated as the design changes and matures.

# 1.3 Types of Failure Effects Analysis

## 1.3.1 Specific Techniques

PROTECT THE REPORT OF THE PROPERTY OF THE PROP

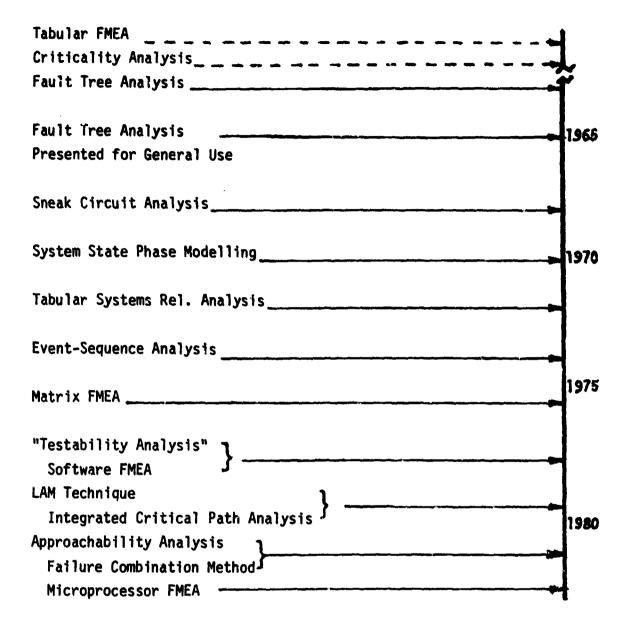

The specific techniques investigated in this report range the entire spectrum of approaches available for a failure effects analysis. In an evolutionary sense, the development of new techniques has not fostered the elimination of earlier techniques, but has served to augment the older techniques or to provide a specific new approach for a specific problem area. This report examines the classical or 'abular failure effects analysis and FMECA (Failure Modes and Effects Criticality Analysis); fault tree analysis; matrix FMEA (Failure Modes and Effects Analysis); sneak circuit analysis; several lesser known techniques, including phase modelling, event-sequence analysis, approachability analysis, and the failure combination method; and new trends in failure effects analysis for software, integrated designs, and microprocessors. Figure 1.1 shows the evolutionary development of the techniques discussed in this report.

Generally, the techniques examined can be applied to any product or system. The results of the failure effects analysis can be both qualitative or quantitative. The broad range of techniques available suggests that selection of a technique for a given project is not simply

EVOLUTIONARY DEVELOPMENT OF FAILURE EFFECTS ANALYSIS TECHNIQUES FIGURE 1.1

a function of new evolutions of techniques or general, acceptable practice. The selection of a technique for a failure effects analysis is dependent upon the level of effort necessary and what type of results are desired.

#### 1.3.2 Related Guidelines/Materials

Further information on failure effects analysis can be found in the sources listed in the Bibliography, Section 9.0. These sources give a more detailed presentation of each technique, and an example is often included with each discussion.

For a more exacting discussion of what is required of a failure effects analysis it is suggested the reader refer to MIL-STD-1629A "Procedures for Performing a Failure Modes, Effects and Criticality Analysis" or any of several other Department of Defense, Nuclear Regulatory Commission, and NASA Standards for specific types of systems (e.g., SAMSO-STD-77-2, "Failure Modes and Effects Analysis for Satellite, Launch Vehicle, and Reentry Systems").

# 1.4 Format of Report

The report examines the major failure effects analysis techniques generally in use today. Tabular FMEA and FMECA are examined in Section 2.0; Fault Tree Analysis is examined in Section 3.0; Matrix FMEA is examined in Section 4.0; and Srieak Circuit Analysis is examined in Section 5.0. Section 6.0 discusses some lesser known techniques. Section 7.0 discusses failure effects analysis for new and rapidly developing areas such as software, microprocessors, and integrated systems. The

History, General Procedure, Future Developments, and Relative Merits of each technique are discussed.

Section 8.0 provides an overview and general evaluation of failure effects analysis, techniques discussed and the current status of failure effects analysis. Section 9.0 provides the Bibliography for the report.

AND THE PROPERTY OF THE PROPER

## 2.0 CLASSICAL TABULAR FMEA TECHNIQUES

# 2.1 Tabular FMEA

# 2.1.1 History of Tabular FMEA

The tabular format was the first technique widely used for FMEA. Because of its longevity and widespread use, the tabular failure effects analysis is often directly associated with failure effects analysis and is often simply referred to as "the" FMEA. The heart of the tabular failure effects analysis technique is the detailed analysis of the effect of a specific failure mode on a system. The detailed analysis is usually presented in a table or worksheet.

The tabular failure effects analysis was the first attempt to develop a technique which gave uniformity to both the procedure used for the analysis and the type of information contained in the analysis. Ine tabular worksheet formats, formalized in the 1950s, are still widely used for the performance of FMEAs.

#### 2.1.2 General Procedure for Tabular FMEA

The tabular failure modes and effects analysis can be initiated at any stage of design or development and at any level of detail. The level of analysis can range from assembly to piece/part indenture. The analysis can begin from the piece/part level and build to the assembly level - the "bottom-up" approach. Or, the analysis can begin from the assembly level and break down into the individual pieces/parts - the

"top-down" approach. Or, the analysis can be initiated at some intermediate level of indenture and proceed either "up" and "down"or some combination of the two.

The tabular analysis can be either hardware or functionally oriented. The hardware approach involves tabulating each individual component, and the effect of every probable failure mode of each component is analyzed. The functional approach involves tabulating equipment functions, and the failure modes contributing to the loss of the function are analyzed. The hardware approach is most often used when detailed design information is available. The functional approach is most often used in conceptual design stages.

A general procedure for performing a tabular FMEA consists of six steps.

- 1. Define the system and its performance requirements.

- Define the assumptions and ground rules to be used in the analysis.

- 3. Develop a block diagram or other simple model of the system.

- 4. Devise the analysis worksheet and complete for every probable failure mode.

- 5. Recommend and evaluate corrective actions and design improvements.

- 6. Summarize the analysis in report form.

The definition of the system, system requirements, and assumptions used in the analysis are necessary for any failure effects

analysis. The definitions establish analysis houndaries, level of indenture, and the range of operating conditions. The block diagram of the system provides the analyst with a simple and useful representation of how the system operates and identifies its inputs, outputs, and interfaces. At the heart of the tabular failure effects analysis is the detailed worksheet. The worksheet is discussed in the following section. If the effects of certain failure modes are unacceptable, corrective actions or design changes can be recommended and their acceptability evaluated. Finally, the analysis should be formally documented and the findings presented in report form.

# 2.1.3 Failure Effects Analysis Worksheet

The major effort in performing a tabular failure effects analysis is the completion of the analysis worksheet. The worksheet usually contains 8-15 columns to be filled in by the analyst. Information to be provided on the form can include:

- 1. Identification of item or function;

- 2. Concise statement of function;

- 3. Operational conditions or mission phases considered;

- 4. Failure modes;

- 5. Failure causes;

- 6. Failure effects;

- 7. Ultimate effects;

- 8. Method of failure detection;

- 9. Possible corrective actions:

- 10. Effect of corrective actions; and

- 11. Remarks.

The identification of the item or function being analyzed is essential to provide traceability and consistency between design drawings and the analysis. A concise statement of the function of the item aids the analyst in recognizing how the item affects overall operation. It is important that all assumed operating conditions be included in the analysis for each failure mode. Different operating conditions can change the effect of failure modes. The itemization of all probable failure modes is the basis of the analysis. The inclusion of possible failure causes can assist in trouble-shooting and failure analysis. The immediate local effect of each failure mode is the principal finding of the analysis. Determining the ultimate effect of the failure can help to identia, the need for corrective action. Noting the method of failure detection can aid in later testability analyses and in showing verifilundancy. In an effort to improve system reliability, corrective able actions can be proposed and evaluated for those failure modes which produce v acceptable effects. The remarks portion of the worksheet allows the analyst to express concerns raised during the analysis.

#### 2.1.4 Related Documents

The worksheet format is often devised according to specific system needs or contractual obligations. A sample tabular failure effects

analysis worksheet is shown in Figure 2.1. Specific procedural requirements and worksheet analysis items can also be found in documents governing the design and development of the specific system. Requirements vary in the amount of detail to be contained in the analysis (e.g., identification of interfaces, compensating features, and critical secondary failures for a non-detectable failure). Requirements also vary in the level of indenture and orientation of the analysis at various design stages.

#### 2.1.5 Tabular FMEA Developments

The tabular FMEA has matured since its inception to include the criticality analysis. Refinements to the tabular FMEA have also been made to tailor each analysis to the specific system or type of system being analyzed. An example of a refined tabular FMEA is the Hitachi Failure Modes, Effects and Criticality Analysis (Hi-FMECA), Reference 24. The analysis incorporates previous experience and a Delphi-type process into the tabular FMEA. Another example of a refined tabular failure effects analysis is the Damage Modes and Effects Analysis (DMEA). In the DMEA the effects of specified threat mechanisms are analyzed for each essential component in the system. The DMEA is most often used to study the survivability and vulnerability of new weapons systems.

FIGURE 2.1 SAMPLE TABULAR FMEA WORKSHEET

| REMARKS                       |  |

|-------------------------------|--|

| CORRECTIVE ACTION NEEDED      |  |

| DETECTION                     |  |

| FALURE EFFECT<br>OCAL ULTMATE |  |

|                               |  |

| FALURE                        |  |

| FALURE                        |  |

| OPERATING<br>PHASE            |  |

| FUNCTION                      |  |

| DENTIFICATION                 |  |

| ПЕМ                           |  |

Currently, efforts are being made to automate the tabular FMEA procedure. The use of word processing and text editing has made it possible for the worksheets to be filled out and updated on a computer terminal. The actual data input and analysis, however, are all performed by the engineer. Word processing has been effective in reducing the amount of time and paperwork involved in the analysis. Computer-aided design can also be used in conjunction with FMEA. Computer generated design drawings can be used with word processing to speed item identification. More sophisticated computer-aided design (CAD) techniques have been used for the analysis of electrical circuits. CAD programs can be useful in performing the analysis of failure effects resulting from opens, shorts, and other electrical faults. The CAD program models the circuit and will analyze the effects of individual faults on the entire system. A CAD program in conjunction with word processing capabilities and failure data base can help to "automate" most portions of a tabular FMEA. Developmental work is continuing in the area of automated FMEA.

#### 2.1.5 Relative Merits of Tabular FMEA

The tabular FMEA is a very versatile and useful design analysis tool. The tabular FMEA can be used on any system and at any stage in design. The worksheet format presents the analysis in a logical and understandable fashion. The tabular FMEA provides a detailed analysis of each single failure at the chosen level of indenture. The nature of the detailed information included in the analysis can be tailored to fit the specific system through the structuring of the worksheet.

The tabular FMEA, however, has several shortcomings. A tabular failure effects analysis can be very costly to perform, generates large amounts of paperwork, and often requires a great deal of time and effort to complete. Further, many standards for the performance of the tabular failure effects analysis are weak and do not provide large amounts of guidance in the selection of indenture level and other ground rules for complex system analysis. The single line analysis of failure modes does not allow for the consideration of human/operator interactions and other system and environmental interactions. The tedium of filling out numerous forms can result in omissions and inaccuracies in the analysis. Multiple fan-outs of failure modes can be overlooked. Often, much time and effort is spent analyzing failure modes which have a negligible effect on system performance or safety.

The automation of the tabular failure effects analysis can help to overcome some of the inadequacies of the technique. Automation can help defray costs, reduce paperwork and time requirements, and help relieve the tedium of filling out the worksheets. Automation would still require the determination of indenture level for computer-aided design or system model. Engineering judgment would still be necessary for evaluating non-traditional failure modes and other special concerns.

# 2.2 Criticality Analysis

# 2.2.1 History of Criticality Analysis

The criticality analysis is often a complementary analysis to the tabular FMEA. Criticality is a relative measure of the importance of a failure mode's effect on the successful operation of the system. The combined analysis is referred to as the Failure Modes, Effects, and Criticality Analysis (FMECA). FMECA was developed by NASA to assure that the hardware used in the space program was sufficiently reliable. Criticality analysis is used to determine the most sensitive or important areas of a design or to indicate where corrective actions should be started. The analysis can be semiqualitative or quantitative. Its results are often presented as a critical items list or in a criticality matrix.

## 2.2.2 Procedure for Criticality Analysis

The procedure used in performing a criticality analysis is straightforward. The difficulty in performing the analysis often comes in supplying the detailed failure rate information. The criticality analysis involves the following nine steps:

- Identify the criticality of each failure mode in the tabular FMEA.

- 2. Supply generic failure rate  $(\lambda_0)$  for item and document the information source.

- 3. Supply operational and environmental failure rate modification factors  $(K_a, K_e)$ .

- 4. Determine fraction of total failure rate attributable to each specific failure mode  $(\alpha)$ .

- 5. Determine conditional probability that if the failure mode occurs the critical failure will occur  $(\beta)$ .

Equation 2.1

- Determine total component operating time (t).

- 7. Calculate criticality of component

$$C_r = \sum_{n=1}^{J} (\alpha K_a K_e \lambda_o t \beta)_n$$

- n = specific failure mode

- j = total number of failure modes for component

- 8. Document the analysis.

- 9. Summarize the analysis results in the form of a critical items list or criticality matrix.

The identification of critical failure modes is accomplished by categorizing the ultimate effect of each failure mode. The military identifies the criticality of each failure mode as one of the four following severities:

- I Catastrophic (A failure which may cause death or system loss)

- II Critical (A failure which may cause minor injury, minor property damage, or system damage which will result in loss)

- III-Marginal (A failure which may cause minor injury, minor property damage, or system damage which will result in delay or degradation)

- IV Minor (A failure which will not cause injury or loss, but which will cause unscheduled maintenance)

Other, more specific, categories can be used for analyses, but the military standard categories are typical of most. The criticality analysis can be pursued for those severity categories of interest.

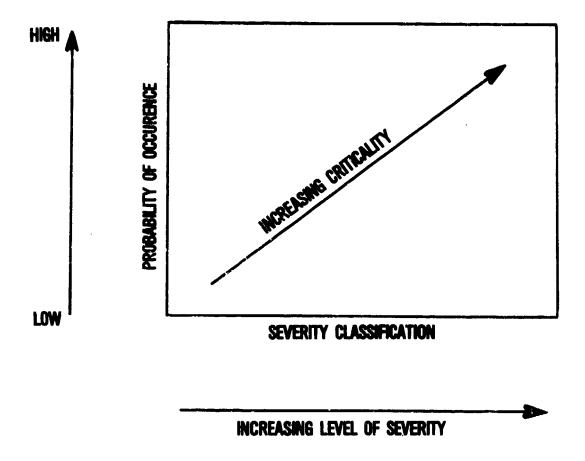

The quantification of criticality can either be explicit or semigualitative. The explicit criticality calculation uses generic failure rate data, from sources such as MIL-HDBK-217, modified by environmental and operating factors, also available from handbooks. fractions of failure rates attributable to specific failure modes can also be found in handbooks. The probability of the critical event occurring given the critical failure mode occurs (B) is determined as part of the analysis. Conservatively, the  $\beta$  term would be assigned a value of 1.0. Once the component operating time has been determined, the component's criticality is a straightforward calculation using Equation The semiqualitative criticality procedure is primarily used for relative comparisons or general rankings when detailed information is not available. In the semigualitative approach the expression for the failure rate and all its associated terms  $(\lambda_{o}^{\beta} K_{e}^{} K_{a}^{})$  is estimated in a very general fashion. One often used estimating scheme (Reference 40) categorizes the failure mode probability as: frequent (>.2); reasonably probable (.1<x<.2); occasional (.01<x<.1); remote (.001<x<.01); or extremely unlikely (<.001). The criticality of each failure mode can then be compared; ranked in a critical items list; placed in a criticalilty matrix; or numerical estimates (median, upper bound, etc.) can be used

THE STATE OF THE PROPERTY OF T

for each category of failure probability, and the numerical analysis can proceed.

Once the calculation of the criticality of each component in the failure effects analysis is completed, the analysis should be formally documented and the results summarized. The formal documentation of the analysis includes completing all the necessary worksheets, including data sources used and assumptions made. The results of the criticality analysis can be presented either in the form of a critical items list or criticality matrix. A critical items list ranks failure modes by their calculated criticality. The criticality matrix places failures on a matrix plot of the probability of occurrence versus severity classification. Figure 2.2 shows a schematic of a criticality matrix.

#### 2.2.3 Developments in Criticality Analysis

The major advances in criticality analysis have not been in the area of techniques, but in the area of data. The increasing volume of failure rate data and modifying factors has helped to make the criticality analysis more rigorous. The inclusion of criticality analysis in an automated tabular failure effects analysis is highly desirable. The automation of criticality analysis would require the creation of a failure rate and modifying factor data base. Engineering input is required to classify the severity of the failure effect and to determine the conditional probability of the critical event occurring given the failure mode occurs. The calculations, however, could all be performed automatically. The computer could also generate a critical items list

FIGURE 2.2 CRITICALITY MATRIX SCHEMATIC

and/or criticality matrix.

AND THE SECOND S

#### 2.2.4 Relative Merits of Criticality Analysis

Criticality analysis is a useful complement to the tabular FMEA. The criticality analysis provides an easy means of ranking the relative importance of failures as a function of both severity of effect and probability of occurrence. The results of the criticality analysis can help in determining the need for corrective action and its priority. The results can also help in determining the need for further part derating or alternate part selection. The automation of criticality analysis in a FMECA would help reduce analysis time and cost.

The criticality analysis has its limitations. The technique described in this report is for use with a tabular failure effects analysis (FMECA). The criticality analysis is not easily incorporated into the other types of failure effects analysis. Because the tabular FMEA examines only the effects of single failures, criticality analysis only examines the criticality of single failures. Human interactions and outside system interactions can not be evaluated by criticality analysis. The criticality analysis can not be more thorough or accurate than the tabular failure effects analysis upon which it is based.

Problems also exist in the quantification of the analysis. While handbooks exist for many types of components, some components have no accurate failure rate data available. The modifying factors and fractions of failures attributable to specific failure modes may be

difficult to locate or estimate. The lack of data can limit the analysis, but the semiqualitative approach and use of best estimates can provide a good basis for relative comparison of component criticalities.

2.3 Hazard Analysis

A type of analysis closely related to the tabular failure effects analysis and criticality analysis is the hazard analysis. Hazard analysis differs from criticality analysis. In criticality analysis the relative importances of failure modes are examined according to both their effect on the system and their probability of occurrence. Hazard analysis is performed to identify potentially hazardous conditions for either the system or system personnel. Three forms of hazard analysis will be briefly discussed: Preliminary Hazard Analysis, Operations Hazard Analysis, and Fault Hazard Analysis. All three analyses can be implemented using a tabular format.

# 2.3.1 Preliminary Hazard Analysis

The Preliminary Hazard Analysis (PHA) is initiated during the conceptual design phase. The intent of the PHA is to identify hazardous conditions for the system and personnel at an early stage in design. Once identified, the hazards can be compensated for, eliminated, or studied further.

The following steps define a general procedure for performing a PHA.

Review hazards identified in similar systems and previous designs. Determine those hazards which may be present in Townloaded from http://www.everyspec.com

the system.

- 2. Identify the events that could potentially create a hazardous condition.

- 3. Evaluate the effects of the hazardous condition.

- 4. Identify available compensation and control for hazard or suggest corrective action.

- 5. Provide results of analysis, corrective actions undertaken, and any additional remarks.

The tabular worksheet is not required to perform a PHA; a fault tree or narrative format may be used instead. The format most often employed, however, is the tabular worksheet.

#### 2.3.2 Operations Hazard Analysis

The Operations Hazard Analysis is performed to identify any potential hazards created by operations on the system. This analysis is usually performed late in the design stages, because detailed knowledge of operations, system configuration, personnel, and conditions is required. A thorough analysis requires insight into all phases of operation and interactions between personnel and other systems.

A "top-down" procedure is used for an Operations Hazard Analysis. The following five steps define a general procedure for an Operations Hazard Analysis.

- 1. Identify all operations performed on the system.

- 2. Determine all potential hazardous conditions associated with the operations. Identification of the hazardous conditions

can be aided by a hazards checklist.

- 3. Break each operation down into its component tasks; each task into its associated procedures; and each procedure into individual steps.

- 4. Identify those elements of each operation which create the hazardous conditions.

- 5. Propose methods by which the hazardous conditions could be alleviated or eliminated.

The tabular worksheet provides a good format for completing the Operations Hazard Analysis in an organized manner.

#### 2.3.3 Fault Hazard Analysis

本書からからから ■のからからから ■ののははないは

The Fault Hazard Analysis is very similar to a FMECA. The Fault Hazard Analysis (FHA) is performed to identify hazardous conditions which may exist as a result of hardware failures. The FHA was developed as an analysis aid for the Minuteman III program. The technique is usually used for projects with many subsystem interfaces. The tabular format is used in the FHA to organize the analysis and to assure thoroughness.

The procedure involved in performing a FHA is very similar to that of a FMEA. Two additional items are part of a FHA: the identification of the upstream component that could command or initiate the fault; and factors that could cause secondary failures. A tabular format suggested by Haas? (Reference 11) consists of the following eight items:

1. Identification of component;

- 2. Evaluation of probability of failure;

- 3. Identification of failure modes;

- 4. Evaluation of percent failures by mode;

- Determination of the effect of failure (including any potential hazards);

- Identification of upstream component that could command or initiate the fault in question;

- 7. Identification of factors that could cause secondary failures; including operational and environmental variables; and

- 8. Remarks.

#### 2.3.4 Relative Merits of Hazard Analysis

Hazard Analysis is a rather specific type of failure effect analysis. The intent of the Hazard Analysis is to assure greater system and personnel safety. The inductive, tabular form of Hazard Analysis is the same format as the tabular FMEA/FMECA. Because of the similarities of the analyses, they share many of the same strengths and weaknesses. The Hazard Analysis technique can present a thorough and logical analysis of all potential hazards in a system. Like the tabular FMEA/FMECA, Hazard Analysis can be exhaustive, but it also can be costly and time consuming.

The Hazard Analysis chould not be performed independently of a tabular FMEA/FMECA. The information obtained in one analysis should be used to assist in further analysis. This information exchange can help to reduce analysis time and core. Automation of the techniques would be

desirable, supplying Hazard Analysis as an additional analysis option.

#### 3.0 FAULT TREE ANALYSIS

#### 3.1 History of Fault Tree Analysis

After the tabular FMEA, Fault Tree Analysis was the next totally new technique to be formally developed for the study of failure effects. Fault Tree Analysis was developed in 1961 by Bell Telephone Laboratories to evaluate the Minuteman Launch Control System. The technique was first presented to the public in 1965 in Seattle. Fault Tree Analysis presented a radically different approach to failure effects analysis than that of the tabular FMEA. The fault tree used deductive reasoning (rather than the inductive approach of the tabular FMEA), and it examined the possibility of multiple failures using formal Boolean logic.

The technique has been given the name fault tree because the analysis begins by defining the ultimate failure effect of interest and then "branching out" to include all combinations of contributory failures. Because it first defines an ultimate effect, Fault Tree Analysis has often been used in safety studies. Its versatility, presentability, and logic have made Fault Tree Analysis a technique widely used for failure effects analysis.

# 3.2 General Procedure for Fault Tree Analysis

Fault Tree Analysis (FTA) can be initiated at any stage in design. The fault tree can be constructed to any level of detail, dependent upon the availability of design information and time and cost constraints. The fault tree can be analyzed mathematically by the same formal logic from which it was constructed. The analysis of the fault

tree can be either qualitative or quantitative.

と、一種においいできた。一種なるなななななな。 こうしゅしゅう

The general procedure for Fault Tree Analysis consists of the following seven steps.

- Define the system, ground rules, and any assumptions to be used in the analysis.

- Develop a simple block diagram of the system showing inputs, outputs, and interfaces.

- Define the top event (ultimate failure effect) of interest.

- 4. Construct fault tree for top event using rules of formal logic. Proceed with analysis to greatest level of detail possible.

- 5. Analyze completed fault tree.

- 6. Recommend any corrective actions or design changes.

- 7. Document the analysis and its results.

Fault tree analysis requires extensive knowledge of system operations and interactions. It is essential that the system boundaries, ground rules, and assumptions be clearly defined before attempting to construct the fault tree. An example of an assumption often used in FTA is that all inputs to the system are correct and within tolerances. A simple block diagram can make it easier to identify system boundaries and the locations of interfaces. The definition of the top event is crucial in determining the success of the analysis. The top event must be

carefully defined to insure that it represents as specific enough condition of interest to be analyzed. A top event which has been defined too generally can cause the analysis to become untractable, overly time consuming, and extremely costly.

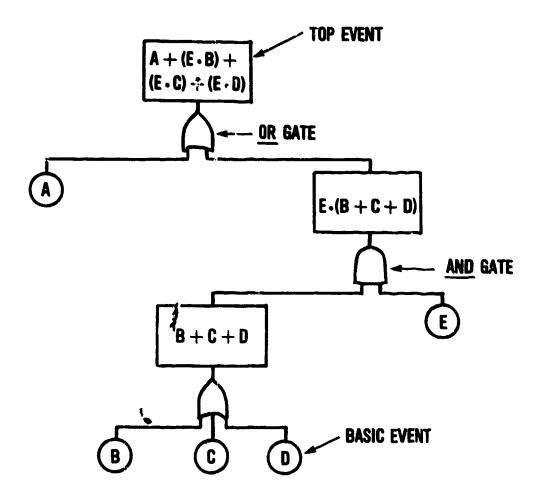

Fault tree construction begins with the definition of the top event and proceeds in a "top-down" manner. The development of the tree is made possible using the principles of Boolean logic. Beginning with the top event, the immediate causes of the event are identified and connected to the top event through a logic operator, or gate. Each of these causes then becomes the event to be developed in similar fashion. The fault tree continues to branch out until only primal events ( events which cannot be developed further) remain. The logic operators (gates) which are used to express how the events are related to each other are shown in Figure 3.1. The logic operators represent an exact algebraic relationship between the underlying causes and the connecting event. A sample fault tree is shown in Figure 3.2.

# FIGURE 3.1 FAULT TREE SYMBOLS

## LOGIC OPERATORS - BATES

| AND BATE: OUTPUT OCCURS IF ALL IMPUT EVENTS OCCUR                                                                   |

|---------------------------------------------------------------------------------------------------------------------|

| OR BATE: OUTPUT OCCURS IF ONE OR MORE IMPUT EVENTS OCCUR                                                            |

| OR PRIORITY AND GATE: OUTPUT OCCURS IF ALL EVENTS OCCUR IN A SPECIFIC ORDER IDENTIFIED BY A CONDITION STATEMENT     |

| OCCURS  OR OF EXCLUSIVE OR GATE: OUTPUT OCCURS IF EXACTLY ONE IMPUT EVENT                                           |

| INHIBIT GATE: OUTPUT OCCURS IF INPUT EVENT OCCURS DURING A SPECIFIED ENABLING CONDITION                             |

| EVENT REPRESENTATIONS                                                                                               |

| EVENT THAT RESULTS FROM A COMBINATION OF FAULT EVENTS                                                               |

| BASIC FAULT                                                                                                         |

| UNDEVELOPED FAULT CONSIDERED BASIC TO TREE                                                                          |

| CONDITIONING EVENT STATEMENT                                                                                        |

| EVENT WHICH IS NORMALLY EXPECTED TO OCCUR IN THE SYSTEM                                                             |

| SIMPLIFICATION OF TREE FOR PURPOSE OF NUMERICAL EVALUATION; TREE HAS BEEN DEVELOPED BUT IS NOT SHOWN IN THE FIGURE. |

FIGURE 3.2 SAMPLE FAULT TREE

Several rules or principles govern the general procedure for the construction of fault trees. Three very general concepts to always consider when constructing a fault tree are:

- Precisely define each event in the analysis; leave no ambiguity in the description; the precision of the event description will allow the construction to proceed logically without introducing extraneous causes;

- 2. Think small; immediate cause thinking will help to prevent the omission or oversight of faults; and

- 3. All basic inputs (or primal events) must be independent; the presence of unidentified or incorrectly represented dependencies invalidates the logic used to construct the tree.

The analysis of the fault tree identifies both the strengths and weaknesses of the system. Numerous methods and algorithms have been developed for the analysis of fault trees. Many variations of algorithms have also been developed to speed computer analysis of fault trees. The analysis results can be expressed qualitatively or quantifactively. The selection of a specific method is dependent upon the complexity of the tree and the type of data which is required for the analysis.

The qualitative analysis of a fault tree is accomplished by applying the rules of logic to the tree construction. The tree can then be reduced into a single analytical expression or into a group of minimum cut sets. A minimum cut set (min-cut) is defined as the smallest number of faults whose failure causes system failure. Correction of any fault

in a minimum cut set will restore the system to a successful state. Minimum cut sets can be used to obtain an expression for system unreliability. They can also be used to establish qualitative importances and critical rankings on the basis of number of elements in each set and the frequency of a particular item's inclusion in the cut sets. The minimum cut sets can also be used for common cause analysis. The susceptibility of the elements of each minimum cut set to common cause failures (such as fire) is examined. The qualitative aspects of fault tree analysis, however, are often overshadowed by the power of quantitative analysis. Several computer algorithms for qualitative fault tree analysis exist. Computer codes in the public domain which perform qualitative fault tree analysis include: PREP, ELRAFT, MOCUS, SETS, and ALLCUTS.

Quantitative fault tree analysis provides an estimate of the probability of occurrence of the TOP event. Direct analytical evaluation, cut set approximations, and Monte Carlo simulation techniques can be used for quantitative fault tree analysis. The major difficulty in any quantitative analysis comes in obtaining the data for the evaluation.

Quantitative analysis, however, can be a very powerful tool. The results also provide quantitative measures of the importance of components and minimum cut sets. Sensitivity studies can be performed to evaluate the effect of part selection, part derating, and other factors which affect reliability. Quantitative analysis using Monte Carlo simulation techniques can provide a statistical evaluation of the fault tree and provide confidence intervals for the probability of the occurrence

of the top event. Many computer programs for the quantitative analysis of fault trees exist. Those which exist in the public domain include: KITT, FRANTIC, WAM-BAM, WAM-CUT, PATREC, PATREC-MC, and SAMPLE.

## 3.3 Fault Tree Developments