RADC-TR-81-318

Final Technical Report

November 1981

17718 000

# PRINTED WIRING ASSEMBLY AND INTERCONNECTION RELIABILITY

IIT Research institute

David W. Coit

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED

ROME AIR DEVELOPMENT CENTER

Air Force Systems Command

Griffiss Air Force Base, New York 13441

REPRODUCED BY

NATIONAL TECHNICAL

INFORMATION SERVICE

U.S. DEPARTMENT OF COMMERCE

SPRINGFIELD, VA. 22161

Downloaded from http://www.everyspec.com

## UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                        |                            | READ INSTRUCTIONS BEFORE COMPLETING FORM                       |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------|--|

| 1. REPORT NUMBER 2. GOVT ACCESSION NO.                                                                                                                                                                                                                                                                                                                                                                                           |                            | O. 3. RECIPIENT'S CATALOG NUMBER                               |  |

| RADC-TR-81-318                                                                                                                                                                                                                                                                                                                                                                                                                   | AD A111214                 |                                                                |  |

| 4. TITLE (and Subtitle)                                                                                                                                                                                                                                                                                                                                                                                                          | •                          | 5. TYPE OF REPORT & PERIOD COVERED Final Technical Report      |  |

| PRINTED WIRING ASSEMBLY AND INT                                                                                                                                                                                                                                                                                                                                                                                                  | TERCONNECTION              | Feb 80 - Aug 81                                                |  |

| RELIABILITY                                                                                                                                                                                                                                                                                                                                                                                                                      |                            | 5. PERFORMING ORG. REPORT NUMBER                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | N/A                                                            |  |

| 7. AUTHOR(s)                                                                                                                                                                                                                                                                                                                                                                                                                     |                            | 8. CONTRACT OR GRANT NUMBER/s)                                 |  |

| David W. Coit                                                                                                                                                                                                                                                                                                                                                                                                                    |                            | F30602-80-C-0078                                               |  |

| 9. PERFORMING ORGANIZATION NAME AND ADDRES                                                                                                                                                                                                                                                                                                                                                                                       | is                         | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |  |

| IIT Research Institute                                                                                                                                                                                                                                                                                                                                                                                                           |                            |                                                                |  |

| 10 West 35th Street                                                                                                                                                                                                                                                                                                                                                                                                              |                            | JO 23380237                                                    |  |

| Chicago IL 60616                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | 12. REPORT DATE                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17. P. \                   | November 1981                                                  |  |

| Rome Air Development Center (RE<br>Griffiss AFB NY 13441                                                                                                                                                                                                                                                                                                                                                                         | SKL)                       | 13. NUMBER OF PAGES:                                           |  |

| 14. MONITORING AGENCY NAME & ADDRESS/II ditter                                                                                                                                                                                                                                                                                                                                                                                   | teem Controlling Office    | 15. SECURITY CLASS, (of this report)                           |  |

| HE MONITORING AGENCY NAME & ADDRESS/F Office                                                                                                                                                                                                                                                                                                                                                                                     | an rum controlling ottice) |                                                                |  |

| Same                                                                                                                                                                                                                                                                                                                                                                                                                             |                            | UNCLASSIFIED                                                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | 15a. DECLASSIFICATION/DOWNGRADING N/ASCHEDULE                  |  |

| 16. DISTRIBUTION STATEMENT (of this Report)                                                                                                                                                                                                                                                                                                                                                                                      |                            |                                                                |  |

| 17. DISTRIBUTION STATEMENT (of the abstract entered in Block 20, if different from Report)  Same                                                                                                                                                                                                                                                                                                                                 |                            |                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                |  |

| 18. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                                                                                                                                                                          | _                          |                                                                |  |

| RADC Project Engineer: John M. McCormick (RBRE)                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                |  |

| 19. KEY WORDS (Continue on reverse side if necessary a                                                                                                                                                                                                                                                                                                                                                                           |                            |                                                                |  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                |                            | Wrapped and Soldered                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | Clip Termination<br>Discrete Wiring                            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | Electroless Deposited PTH                                      |  |

| 20. ABSTRACT (Continue on reverse side if necessary as                                                                                                                                                                                                                                                                                                                                                                           |                            |                                                                |  |

| This report presents reliability prediction models for printed wiring assemblies, solderless wrap assemblies, wrapped and soldered assemblies, and discrete wiring assemblies w/electroless deposited PTH for inclusion in MIL-HDBK-217. Collected field failure rate data were utilized to develop and evaluate the factors. The reliability prediction models are presented in a form compatible with MIL-HDBK-217D, proposed. |                            |                                                                |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                |  |

DD FORM 1473 EDITION OF 1 NOV 55 IS OBSOLETE

Downloaded from http://www.everyspec.com

This report has been reviewed by the RADC Public Affairs Office (PA) and is releasable to the National Technical Information Service (NTIS). At NTIS it will be releasable to the general public, including foreign nations.

RADC-TR-81-318 has been reviewed and is approved for publication.

APPROVED:

JOHN E. MCCORMICK Project Engineer

APPROVED:

EDMUND J. WESTCOTT

Technical Director

Reliability & Compatibility Division

FOR THE COMMANDER:

JOHN P. HUSS Acting Chief, Plans Office

If your address has changed or if you wish to be removed from the RADC mailing list, or if the addressee is no longer employed by your organization, please notify RADC (RBRE) Griffiss AFB NY 13441. This will assist us in maintaining a current mailing list.

Do not return copies of this report unless contractual obligations or notices on a specific document requires that it be returned.

Downloaded from http://www.everyspec.com

## PREFACE

This final report was prepared by IIT Research Institute, Chicago, Illinois, for the Rome Air Development Center, Griffiss AFB, New York, under Contract F30202-80-C-0078. The RADC technical monitor for this program was Mr. John McCormick (RBRE). This report covers the work performed from February 1980 to August 1981.

The principal investigator for this project was Mr. D.W. Coit with valuable assistance provided by Mr. D.W. Fulton, Mr. J.J. Steinkirchner, Mr. R.G. Arno and Mr. E.R. Bangs. Data collection efforts for this program were coordinated by Mr. I.L. Krulac.

Downloaded from http://www.everyspec.com

## TABLE OF CONTENTS

|    |      | TABLE OF CONTENTS                                                                                                                                                                                                                                                                               | Page                                         |

|----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1. | INTR | ODUCTION                                                                                                                                                                                                                                                                                        | 1                                            |

|    |      | Purpose<br>Background                                                                                                                                                                                                                                                                           | 1                                            |

| 2. | THEO | RETICAL ANALYSIS                                                                                                                                                                                                                                                                                | 3                                            |

|    |      | Literature Review Theoretical Discussions 2.2.1 Plated Through Holes 2.2.2 Solder Connections 2.2.3 Printed Wiring Boards 2.2.4 Solderless Wrap Assemblies 2.2.5 Wrapped and Soldered Assemblies 2.2.6 Clip Termination Assemblies 2.2.7 Discrete Wiring Assemblies w/Electroless Deposited PTH | 3<br>4<br>6<br>9<br>10<br>11<br>12           |

| 3. | DATA | COLLECTION AND PRELIMINARY ANALYSIS                                                                                                                                                                                                                                                             | 14                                           |

|    |      | Data Collection and Reduction Failure Rate Distribution Considerations                                                                                                                                                                                                                          | 14<br>17                                     |

| 4. | FAIL | URE RATE PREDICTION MODEL DEVELOPMENT                                                                                                                                                                                                                                                           | 19                                           |

|    | 4.1  | Printed Wiring Assemblies 4.1.1 Proposed Failure Rate Prediction Model 4.1.2 Preliminary Assumptions and Methodology 4.1.3 Environmental Factor 4.1.4 Complexity Factor 4.1.5 Base Failure Rate 4.1.6 Solder Application Factor 4.1.7 Quality Factor                                            | 19<br>19<br>23<br>36<br>41<br>46<br>48<br>59 |

|    | 4.2  | Reflow Soldered Assemblies 4.2.1 Proposed Failure Rate Prediction Model 4.2.2 Model Development Procedure                                                                                                                                                                                       | 60<br>60<br>61                               |

|    | 4.3  | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                         | 65<br>65<br>66                               |

|    | 4.4  | Wrapped and Soldered Assemblies 4.4.1 Proposed Failure Rate Prediction Model 4.4.2 Model Development Procedure                                                                                                                                                                                  | 69<br>69<br>70                               |

|    | 4.5  |                                                                                                                                                                                                                                                                                                 | 74<br>74<br>74<br>74                         |

|    | 4.6  | Discrete Wiring Assemblies w/Electroless Deposited PTH 4.6.1 Proposed Failure Rate Prediction Model 4.6.2 Model Development Procedure                                                                                                                                                           | 77<br>77<br>77<br>78                         |

## TABLE OF CONTENTS

|      |                |       |                                   | Page |

|------|----------------|-------|-----------------------------------|------|

| 5.   | MODE           | EL EV | VALUATION                         | 82   |

| 6.   | CONC           | CLUS  | IONS                              | 86   |

| 7.   | RECO           | OMME  | NDATIONS                          | 87   |

| APPE | NDIX           | 1:    | MIL-HDBK-217D REVISION PAGES      | 91   |

| APPE | NDIX           | 2:    | APPLICABLE STATISTICAL TECHNIQUES | 104  |

| BIBL | I OGR <i>I</i> | YPHY  |                                   | 110  |

# LIST OF FIGURES

|          |        |                                                                                            | Page |

|----------|--------|--------------------------------------------------------------------------------------------|------|

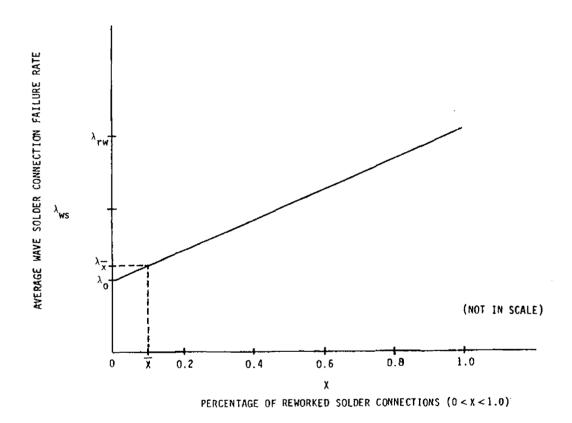

| FIGURE 4 |        | AVERAGE WAVE SOLDER CONNECTION FAILURE RATE VS. REWORK PERCENTAGE                          | 29   |

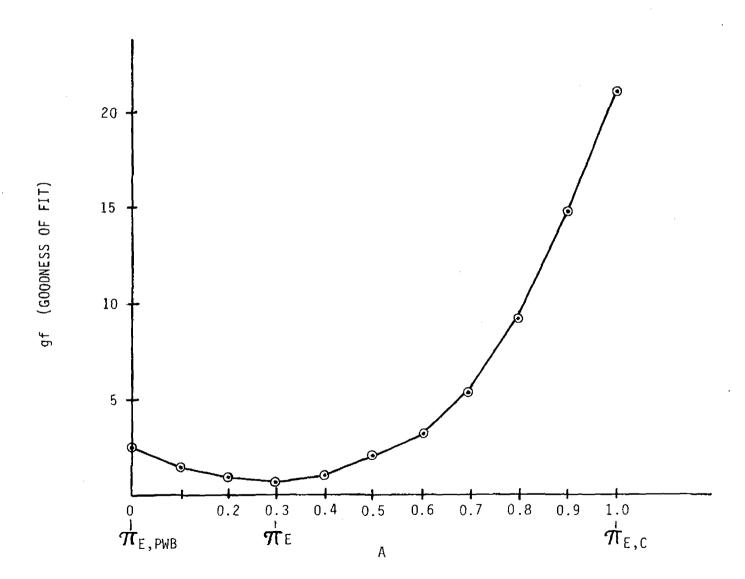

| FIGURE 4 | 1.1-2: | GOODNESS OF FIT VS. ASSUMED ENVIRONMENTAL FACTORS                                          | 42   |

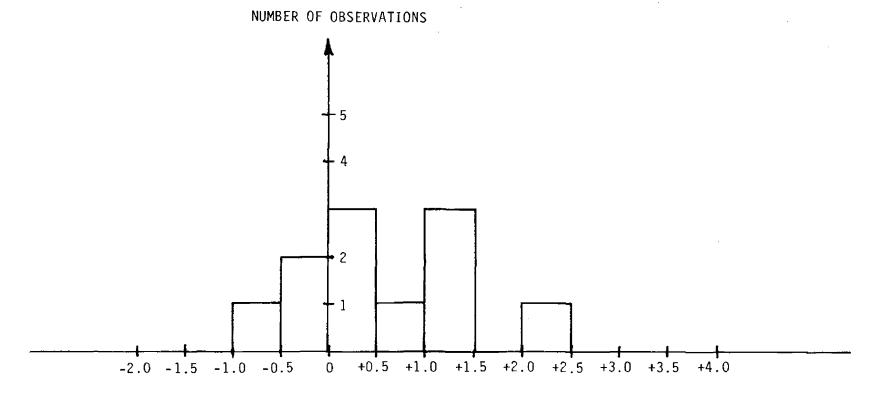

| FIGURE 4 | 1.1-3: | SOLDER APPLICATION FACTOR DENSITY HISTOGRAM                                                | 50   |

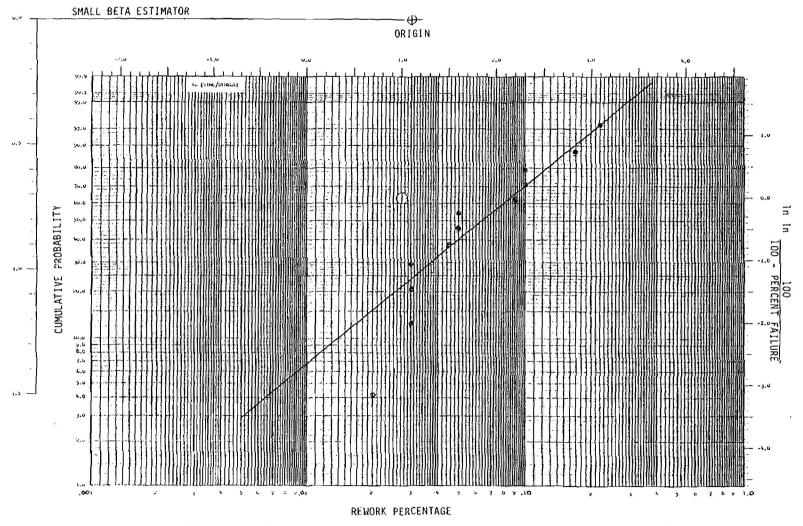

| FIGURE 4 | · -    | WEIBULL CUMULATIVE DENSITY FUNCTION FOR SOLDER REWORK PERCENTAGES                          | 53   |

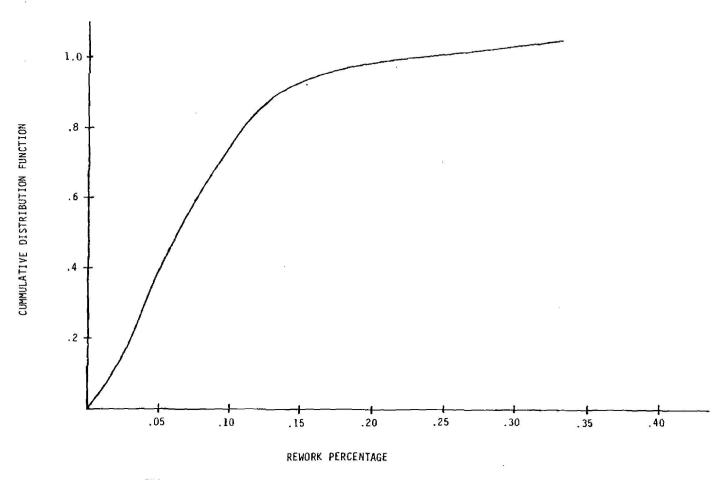

| FIGURE 4 | .1-5:  | REWORK PERCENTAGE CUMULATIVE DISTRIBUTION FUNCTION                                         | 54   |

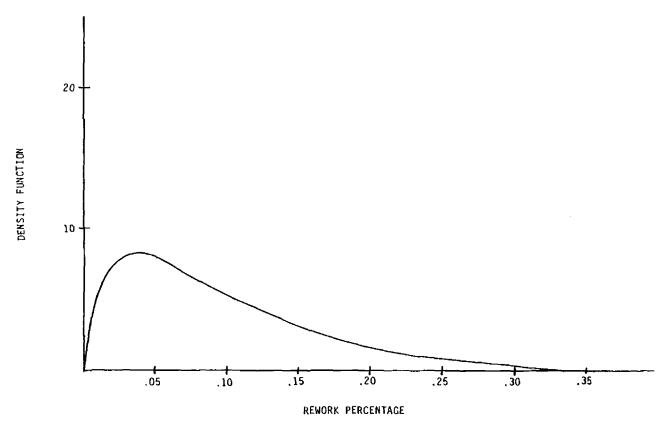

| FIGURE 4 | .1-6:  | REWORK PERCENTAGE DENSITY FUNCTION                                                         | 55   |

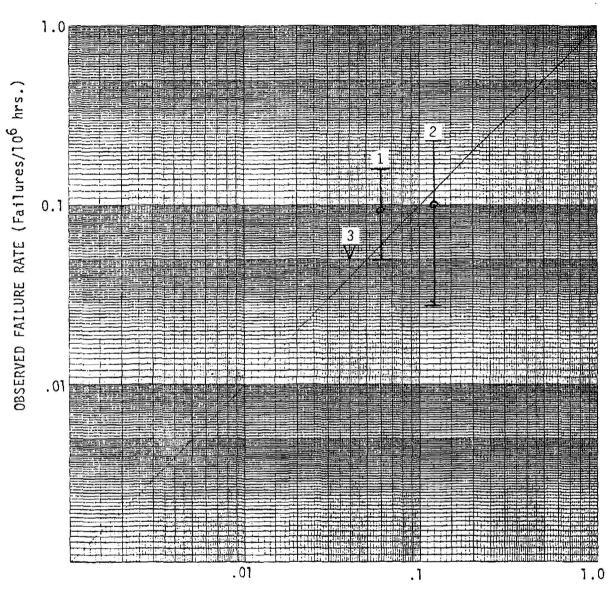

| FIGURE 5 | •      | PRINTED WIRING ASSEMBLY OBSERVED FAILURE RATES VS. PROPOSED MODEL PREDICTION FAILURE RATES | 84   |

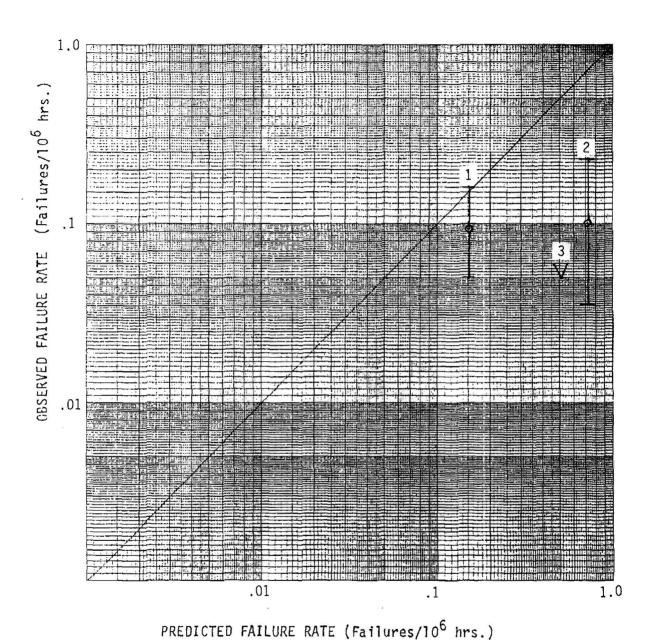

| FIGURE 5 | -      | PRINTED WIRING ASSEMBLY OBSERVED FAILURE RATES VS. MIL-HDBK-217C PREDICTED FAILURE RATES   | 85   |

Downloaded from http://www.everyspec.com

# LIST OF TABLES

|               |                                                                | Page |

|---------------|----------------------------------------------------------------|------|

| TABLE 3.1:    | DATA SUMMARY BY TECHNOLOGY                                     | 16   |

| TABLE 4.1-1:  | COMPLEXITY FACTOR                                              | 20   |

| TABLE 4.1-2:  | SOLDER APPLICATION FACTORS                                     | 21   |

| TABLE 4.1-3:  | QUALITY FACTOR                                                 | 21   |

| TABLE 4.1-4:  | ENVIRONMENTAL FACTOR                                           | 22   |

| TABLE 4.1-5:  | FACTORS INFLUENCING PRINTED WIRING BOARDS AND CONNECTIONS      | 24   |

| TABLE 4.1-6:  | ENVIRONMENTAL FACTOR FOR PRINTED WIRING BOARDS AND CONNECTIONS | 37   |

| TABLE 4.1-7:  | COMPLEXITY FACTOR VS. ASSUMED ENVIRONMENTAL FACTORS            | 39   |

| TABLE 4.1-8:  | SUMMARIZED DATA FOR ENVIRONMENTAL FACTOR DEVELOPMENT           | 39   |

| TABLE 4.1-9:  | BASE FAILURE RATE VS. ENVIRONMENT                              | 47   |

| TABLE 4.1-10: | OBSERVED SOLDER APPLICATION FACTORS                            | 49   |

| TABLE 4.1-11: | BASE FAILURE RATE VS. QUALITY GRADE                            | 59   |

| TABLE 4.2-1:  | ENVIRONMENTAL FACTOR                                           | 61   |

| TABLE 4.2-2:  | FACTORS INFLUENCING REFLOW SOLDERED ASSEMBLY FAILURE RATE      | 62   |

| TABLE 4.2-3:  | REFLOW SOLDERED ASSEMBLY DATA                                  | 64   |

| TABLE 4.3-1:  | FACTORS INFLUENCING SOLDERLESS WRAP ASSEMBLY FAILURE RATE      | 66   |

| TABLE 4.3-2:  | SOLDERLESS WRAP ASSEMBLY DATA                                  | 68   |

| TABLE 4.4-1:  | FACTORS INFLUENCING WRAPPED AND SOLDERED ASSEMBLY FAILURE RATE | 71   |

| TABLE 4.4-2:  | WRAPPED AND SOLDERED ASSEMBLY DATA                             | 72   |

# LIST OF TABLES (Cont'd)

|              |                                                                                       | Page |

|--------------|---------------------------------------------------------------------------------------|------|

| TABLE 4.5-1: | FACTORS INFLUENCING CLIP TERMINATION ASSEMBLY FAILURE RATE                            | 75   |

| TABLE 4.5-2: | CLIP TERMINATION ASSEMBLY DATA                                                        | 76   |

| TABLE 4.6-1: | FACTORS INFLUENCING DISCRETE WIRING ASSEMBLY W/ELECTROLESS DEPOSITED PTH FAILURE RATE | 78   |

| TABLE 4.6-2: | DISCRETE WIRING ASSEMBLY W/ELECTROLESS DEPOSITED PTH DATA                             | 81   |

| TABLE 5.1:   | PRINTED WIRING ASSEMBLY MODEL VALIDATION DATA                                         | 83   |

## 1. INTRODUCTION

1.1 <u>Purpose</u>. The primary objective of this study was to develop a failure rate prediction methodology which could be employed in the reliability assessment of printed wiring assemblies and alternative types of interconnection assemblies currently used in the electronics industry. Different types of interconnection assemblies considered include double-sided and multilayer printed wiring, solderless wrap, wrapped and soldered, clip termination and discrete wiring with electroless deposited plated through holes.

Previously documented field experience has indicated that the current prediction methodology for printed wiring boards and connections as presented in MIL-HDBK-217C, Reliability Prediction of Electronic Equipment, is inaccurate. The current methodology has also proved insufficient in regard to the full spectrum of available technologies. This study involved the development of an interconnection assembly failure rate prediction models which replace the current printed wiring board and connection prediction models, increases prediction accuracy and expands prediction capabilities to previously unexplored areas.

1.2 <u>Background</u>. Advances in the electronics industry dictate that printed wiring assemblies and alternate types of interconnection assemblies be compatible with highly dense circuit designs. Therefore, the use of multilayer printed wiring boards is becoming more and more desirable. However, there is a relatively lengthy time between design submittal and finished product for multilayer printed wiring boards. This is one of the primary reasons for the emergence of alternate types of interconnection assemblies. The alternate interconnection assemblies, most notably discrete wiring boards can also provide other distinct advantages depending on the users particular needs. The choice of which method of interconnection is most suitable for a particular application must be decided after considering many different factors.

In most applications, any advantages offered by a particular type of interconnection assembly are of little or no consequence unless it can also provide reliable service over the expected life of the system. Therefore, there is a need for an accurate reliability prediction methodology capable of considering the full spectrum of available interconnection assemblies. It is particularly essential to accurately predict printed wiring assembly failure rate because that is the most predominately used interconnection technology.

Failure rate and mean time between failure (MTBF) prediction capabilities are necessary in the development and maintenance of reliable electronic equipment. Predictions performed during the design phase yield early estimates of the anticipated equipment reliability and provide a quantitative basis for performing design trade-off analyses, reliability growth monitoring, maintenance action and spares allocation requirements, and life cycle cost studies.

A useful interconnection assembly failure rate prediction methodology should afford the optimal consideration of those qualities common to practical reliability assessment techniques including:

- a relatively uncomplicated approach which is easy to use and does not require intimate knowledge of device characteristics beyond readily available information

- o the appropriate discrimination against device design and usage attributes which contribute to known failure mechanisms

- o a dynamic, flexible expression, which, through simple modification, allows for the evaluation of newly emerging technologies

- o reasonable accuracy over the total range of all parameters considered in the technique.

This report describes the approach, results and conclusions of the study and includes the proposed interconnection assembly reliability prediction models to replace Section 5.1.13 of MIL-HDBK-2170.

## 2. THEORETICAL ANALYSIS

2.1 <u>Literature Review</u>. A comprehensive literature review was performed to identify all published information which is relevant to the reliability of printed wiring boards, solder connections, discrete wiring boards and alternate types of connections and interconnection boards. Literature sources searched include the Reliability Analysis Center automated library information retrieval system, the National Technical Information Service (NTIS), the Defense Technical Information System (DTIS), and the Government Industry Data Exchange Program (GIDEP). Additionally, manufacturers and users of printed wiring and other interconnection assemblies have supplied useful information and test results.

The primary objective of the literature review was to locate references whose content could be used to supplement the data analysis process and to provide the reliability models with a sound theoretical foundation. An effort was undertaken to investigate the fundamental physical and electrical characteristics of each type of interconnection assembly in order to identify the respective failure mechanisms and the parameters having a significant impact on reliability. Once identified, the failure mechanisms were further studied to determine which combinations of the significant parameters would minimize and maximize their frequency of occurance.

Additionally, for types of interconnection assemblies which have been developed more recently and for which there exists limited field data, conclusions obtained through the literature review were merged with the available data to develop a useful prediction model.

## 2.2 Theoretical Discussions.

2.2.1 Plated Through Holes (PTH). The PTH multilayer printed wiring board consists of a number of layers of thin circuit boards which are stacked one above the other and laminated into one monolithic assembly. At the points of proposed interconnection, holes are drilled which pass through the pads on the conductors of the inner layers which are larger than the drilled hole. Drilling exposes a rim of copper around the entire circumference of the hole. The copper on the individual layers in the plated through hole is connected by copper plating. Plated through holes are also used for interconnection on discrete wiring w/PTH assemblies. The discrete wiring boards are plated in an electroless copper bath where copper is deposited to form the component holes and make connections to the discrete wires.

It is not uncommon to encounter manufacturing difficulties which result in PTHs which are subject to the formation of barrel cracks. This tendency to form barrel cracks is generally due either to imperfections in the PTH barrel wall which greatly amplify the level of axial strains, very poor effective ductility of the copper plating, or a combination of these two factors. Poor drilling or excessive acid etching during the hole wall cleaning process can lead to rough barrel walls. A level but thin plating on the rough barrel wall may then result in localized stress concentrations and large plastic strains. For certain copper electro-plating systems, the rough hole wall may also have a detrimental influence on grain growth and may produce locally weakened intergranular boundries which are easily fractured. Even if the PTH walls are smooth, variable electroplating processes may yield copper of very low conductivity.

A primary cause of printed wiring board failures is the mismatch of thermal coefficients of expansion in the plated through hole. The thermal coefficients of expansion for the copper plated through hole and the epoxy glass substrate are not compatible. When exposed to thermal cycling, the copper and the epoxy glass expand and contract at different rates creating

stresses in the plated through hole which can surpass the ultimate strength of the copper plating. Under laboratory conditions, 98% of all multilayer printed wiring board open circuits were found to be from 360° PTH barrel fractures. A possible solution to this problem is the use of polyimide as a board material. Manufacturing difficulties have arisen, however, when printed wiring boards have been made with polyimide and its widespread use has not been observed.

PTH barrel stresses have been observed to be significantly higher in the central portion of the PTH. Approximately 30 times as many PTH failures were observed in the central 50% of the PTH in the laboratory. The tested multilayer printed wiring boards were composed of eight circuit planes. Internal circuit planes inhibiting free expansion and additive loading on PTH lands were considered to be the principal reason for higher centralized stresses. As the number of internal circuit planes increase on a printed wiring board, the stresses in the central plated through hole region become larger.

Surface and internal land fractures were concentrated at the surfaces of the printed wiring board. The larger stresses were observed at the surfaces because those land areas have larger deflection than the internal lands; therefore, a dramatic increase in land fractures is not expected to correspond to an increase in circuit plane quantity. The stresss on the internal lands are less than the stresses on the surface, but the sum total of surface and internal land failures would be expected to increase as the quantity of circuit planes increases.

1,2. Harley, Strong and Young, <u>Reliability Investigation of Thermal Stress/Fatigue Failure in Multilayer Interconnection Boards</u>, RADC-TR-70-192.

Additionally, the thickness of the plating presents an important parameter effecting failure rate. Excessively thin plating in the PTH may result in more observed fractures. Thicker internal lands cause higher barrel stress by subjecting the PTH barrel to repetitive bending stresses during thermal cycling. A precise matching of surface and internal land thickness and barrel plating thickness is required to insure the highest quality PTH.

2.2.2 Solder Connections. There has been considerable work done on failure mechanisms in solder connections by Manko, Beal and Bangs, Ehuwaites, Zakrayck and others. This section briefly discusses several of the solder connection failure mechanisms. More detailed analyses are identified in the bibliography.

Solder connections that contain copper-tin-intermetallics or gold-tin intermetallics have relatively poor reliability characteristics. Test results have shown that solder connection failures are accelerated by pressure on the crack susceptible intermetallic compounds.

It has been shown in tests by Beal and Bangs that low frequency thermal cycling of solder connections promotes cracking in 63 Sn - 37 Pb alloy when cycled in the  $-65^{\circ}$ C to  $150^{\circ}$ C range. The influence of thermal cycling is a primary cause of solder connection failure.

The plating process employed in the coating of leads prior to soldering has frequently been found to be a source for defects that contribute to solder connection failures. In most plating systems, organic polymers form and bath maintenance by carbon treatment is required to eliminate or minimize the presence of organic impurities which can codeposit. Some of these polymers have extremely large molecules with lengths of up to one-half to one micron. These materials usually are readily absorbed by activated carbon and can be removed from the system.

The remaining polymer materials can be co-deposited, which can lead to stresses or faults in the deposit, giving rise to corrosion sites.

Bath cleaniless is essential. If a bath is properly maintained, there should be no problems with the electroplated deposit itself. An interesting fact is that only 5% of the problems arising in corrosion testing are due to plating systems that were not properly maintained, or kept in a clean conditon. Experience has demonstrated that the substrate being plated causes 95% of the subsequent failures. Take as an example a typical screw machine or stamped part. These parts normally have a surface finish of approximately 1um. Couple this with the fact that most metals today are being improperly recycled, thereby causing inclusions of foreign material (foreign metals and oxides of these metals). Accordingly, one must consider not only the surface preparation that is necessary, but also compensate for inclusions within the bulk, and also at the surface of the part.

In wave soldering, the solder is pumped out of a narrow slot to produce a wave or series of waves. The conveyor can be at a small angle to the horizontal to assist drainage of the solder, and double waves or special wave forms may also be used for this purpose. In cascade soldering, the solder flows down a trough by gravity and is returned by pump to the upper reservoir. These wave solder systems are excellent in that a virtually oxide-free solder surface is presented to the part, and removal of flux and vapors is also promoted by the flow of the solder.

Integrated wave soldering systems for printed wiring assemblies provide units that can apply the flux, dry and preheat the board, solder components, and clean the completed assembly. Some of the systems have special features where the flux is applied by passing through a wave, by spraying, by rolling, or by dipping. Several systems employ oil mixed with the solder to aid in the elimination of icicles and bridging between

conductor paths. Another system features dual waves flowing the opposite direction to the board travel.

The principal fluxes used for printed wiring assembly soldering are nonactivated, mildly activated and activated rosin. The choice of flux presents several reliability concerns which are considered briefly.

Noncorrosive fluxes all have rosin as a common ingredient. Rosin has unique physical and chemical properties which make it ideal as a flux. It melts at 1270C (2600F) and remains active in the molten state up to 3150C (6000F). The active constituent of rosin (abietic acid) is inert in the solid state, active when molten, and returns to an inactive state when cooled. Thus it is widely used in the electrical and electronics industries because the flux residue is noncorrosive and non-conductive.

Nonactivated rosin consists of rosin plasticized with an inert plasticizer for core solder or dissolved in an inert solvent as a liquid flux. No additives for the purpose of increasing flux activity are used. This is the mildest of the rosin fluxes, and only extremely clean and solderable metals can be soldered reliably with nonactivated rosin.

Because of the slow fluxing action of nonactivated rosin, mildly activated rosin is also used. It contains additives which improve the fluxing action of the rosin but leave residues which are noncorrosive and nonconducting. Mildly activated rosin is used in high reliability electronic assemblies, and removal of the flux residue is optional. Mildly activated rosin can be plasticized for core solder or dissolved in an organic solvent to provide a liquid flux.

The activated rosin fluxes are the most active of all and depend on the addition of small amounts of complex organic compounds for their increased activity. Hydrohalides of amines such as hydrazine hydrohalide. glutamic acid hydrochlorides, cetyl pyridinium bromide, aniline hydrochloride and organic acids such as benzois and succinic have been disclosed in patent literature as additives for activated rosin fluxes to be used in liquid form or as a core material. Additive amounts varying from 0.2 to 5% have been used.

The use of activated rosin as a noncorrosive flux is based on the theory that the activator is decomposed by heat and that the residue is not electrically conductive and corrosive. High production-line speeds have demanded more highly active fluxes, but the question of harmful flux residues is still a matter of debate in critical applications where corrosion resistance is the foremost consideration.

If rosin residues must be removed, alcohol or chlorinated hydrocarbons may be used. Certain rosin activators are soluble in water but not in organic solvents. These flux residues require removal by organic solvents, followed by a water rinse.

2.2.3 Printed Wiring Boards (PWBs). Processing factors such as chemistry, lamination parameters, etc., have an influence on moisture content within the board material, although no single dominant factor has been identified. Likewise, the effect of assembly processing (baking, fluxing, soldering, cleaning, etc.) have been shown to influence printed wiring board failure rate.

A materials/process related problem of considerable importance is the following: if in raw material manufacture, or multilayer board lamination, contamination from foreign fibers occurs, PWB reliability may suffer. As an inclusion in the dielectric composite, foreign fibers may contact an anodically biased conductor and even bridge to a nearby cathode. Filament growth has often been observed to occur rapidly at accelerated test conditions. Hence, preventing this type of contamination is extremely important.

Other factors relative to PWB configuration should be mentioned here. For example, when conformal coatings are applied to the finished PWB, an intensification of the foreign fiber failure mechanism is often observed, together with a shortening of PWB life. An apparently related observation is that failures in multilayer boards tend to occur first on the most deeply buried innerlayers, and later on the layers closest to the board surfaces. The reasons for this behavior are not yet fully understood.

Another factor which influences failure rate is the spacing between conductor traces on the printed wiring board. It has been shown that as conductor trace spacing drops below approximately 4 mils, the failure rate is adversely effected.<sup>3</sup> Above 4 mils spacing, there appears to be no significant effect on failure rate. Most of the current high density printed wiring boards range between 5 to 10 mils spacing and trace width and spacing are not important failure rate influencing variables.

It is emphasized that this section addressed printed wiring board reliability characteristics not associated with plated through holes. Plated through hole failures account for up to 98% of all printed wiring assembly failures (Section 2.2.1).

- 2.2.4 Solderless Wrap Assembles. The solderless wrap process consists of wrapping a solid conductor around a post with sharp corners. The wire is wrapped while under tension, causing deformation of the wire at the sharp corners of the post. The post is also deformed under the wire. The resulting joint provides a gas tight interface between the wire and the post. Two types of wrap are used. One type has all bare wire wrapped on the post, while the other has an insulated turn (last turn) wrapped on the post. Under dynamic conditions, the deformed wire acts as a stress

- 2 Lanti, Delaney and Hines, <u>The Characteristic Wearout Process in Epoxy-Glass Printed Wiring Circuits for High Density Electronic Packaging</u>, Bell Laboratories.

concentration notch which may result in low fatigue life. The insulated turn prevents deformation of the wire at the last turn, thereby eliminating the stress concentration notch.

The solderless wrap technique is limited to round solid wire since the properties of solid wire are needed to assure the intimate and uniform contact which assures continuity. Control of material properties of the wire, terminals and coatings of these material is necessary to assure reliable solderless wrap connections.

The wire generally used is round soft copper that is plated with tin, tin-lead alloy, silver or gold. Special tools for wrapping are commercially available. Failure mechanisms for solderless wrap assemblies include insufficient tension in the wire and lack of required hardness in the copper wire. These failure mechanisms will cause a voltage drop across the wire and post interface.

2.2.5 Wrapped and Soldered Assemblies. The wrapped and soldered process consists of wrapping an insulated wire around a post with sharp corners. The wrapping process has several physical similarities to the solderless wrap process. But instead of forming a gas tight, tension induced connection, solder is applied to the wraps to form the permanent connection. Controls of material properties of the wire, terminal posts and wire insulation is necessary to assure reliable wrapped and soldered connections. Additionally, tool calibration and surface solderability are important reliability characteristics concerning wrapped and soldered assemblies.

Test information concerning wrapped and soldered assemblies is not available. Possible failure mechanisms concern incomplete removal of insulation or residual carbonized products resulting in a weaker wrapped and soldered connection.

2.2.6 Clip Termination Assemblies. Clip termination assemblies are designed to provide reliable electrical and mechanical terminations for use as an interconnection assembly. The clip termination process briefly consists of a length of wire, automatically stripped, compressed, wiped along the terminal post during the termination process and held in place by a metal clip. The process is accomplished by either hand tool application or by automatic point to point wiring machines. Control of material properties of the wire, the clip and the terminal post is necessary to assure reliable clip termination assemblies.

Results of reliability tests subjecting the clip termination assemblies to vibration, thermal shock, salt spray and humidity do not reveal any inherent weaknesses in the clip termination technology. Potential failure mechanisms for clip termination assemblies include variable gas tight clip characteristics, relaxation of spring tension and dimensional variability (clip vs. wire vs. terminal post).

- 2.2.7 Discrete Wiring Assembly w/Electroless Deposited PTH. A study by R.J. Clarke<sup>4</sup> provided the following theoretical discussions concerning manufacturing processes and failure mechanisms. A discrete wiring assembly with electroless deposited plated through holes is basically a pattern of insulated wires laid down on an adhesive coated substrate by a numerically controlled machine. The wire used is NEMA 34-gauge polyimide insulated wire, equivalent to a .024 inch flat printed circuit conductor of one ounce copper foil. A thin (0.0004 inch) low-flow epoxy-glass pre-peg is laminated to the surfaces of the panel, over the wires, to give added protection to the finished board. The adhesive and pre-peg are then cured by an oven bake to encapsulate the wire. A temporary mask is applied to both surfaces of the board for protection

- 4 Clark, R.J. (General Electric Company), <u>High Speed Logic Packaging</u>

<u>Using Multiwire Interconnection Technology</u>, Presented at the 1976

Wescon Professional Program.

during subsequent chemical cleaning operations. Holes are drilled in the board using conventional printed circuit NC drilling equipment. After drilling, most of the holes have one or two wire cross sections exposed at the wall of the hole.

A cleaning cycle removes epoxy or adhesive smears and etches the polyimide insulation about 0.002 inches to expose a wire stub at the wall of the hole. After cleaning, the drilled boards are plated in an electroless copper bath where copper is deposited to form the component PTH's and electrically connect the PTH to the wires. Typically, 0.0015 inches of copper is plated in the holes, but thicker deposits are possible. After copper plating, the temporary mask is removed and a protective finish is applied to the copper to prevent oxidation and ensure good solderability. The components are then assembled by either a hand soldering or wave soldering operation.

Two failure mode areas in discrete wiring assemblies w/PTH are the wire crossovers and wire ends to PTH interface. The wire crossover potentially can be a source of failure. When one wire crosses another, there is typically 0.0012 inch of polyimide insulation between them. The typical breakdown voltage at a single crossover is 1,500 - 2,000 volts. Photomicrographics of a wire crossover show some deformation of the upper wire due to the motion of the pressure foot at ultrasonic frequencies. The wire is ordinarilly tested by the manufacturer to determine its ability to maintain insulation integrity under extreme conditions. Environmental testing at several testing laboratories has shown no degradation of the insulation resistance between crossovers after thermal shock, thermal cycling, shock vibration, humidity cycling and exposure to salt spray.

Test data accumulated to date indicates that the connection of the wire end to the copper plating in the PTH is very reliable. The cleaning cycle removes the insulation from the wire and exposes about 0.002 inch of the wire. The drilling operation slightly deforms the wire end resulting

in a "nailhead" condition. When electroless copper is deposited in the hole, there is not only the connection formed by the interlocking grain structures of the frontal cross sectional area of the wire and plated copper, but also a mechanical condition formed by the circumferential deposition of copper around the area of the wire end where the insulation was removed.

#### 3. DATA COLLECTION AND PRELIMINARY ANALYSIS

3.1 <u>Data Collection and Reduction</u>. The modification of current failure rate prediction models or the development of new prediction methodologies should be derived from field failure rate data obtained from closely monitered systems. Modeling activities require extensive data resources because failure rate prediction models derived using limited data will reflect the characteristics of only that information. This section presents the data collection procedure followed and the preliminary analysis used to develop a useful interconnection assembly data base.

One of the advantages offered by a printed wiring "assembly" level prediction model was the ability to acquire a more extensive data base. Exhaustive failure analysis is required to differentiate between a plated through hole failure and a solder connection failure. Both types of failures can appear in maintenance reports as a connection open circuit. Most of the available data sources do not perform extensive analysis. But because the intention of the study was to develop a printed wiring "assembly" failure rate prediction model, data sources without failure analysis were included in the data base. This is because failures which could not be classified as either printed wiring board or solder connection failures would still be correctly regarded as an "assembly" failure.

The Reliability Analysis Center operated by the IIT Research Institute at Griffiss Air Force Base was solicited to aid in the data collection process. The Reliability Analysis Center regularly pursues the collection of nonelectronic parts reliability data including printed wiring

boards, solder connections and other pertinent interconnection methods. Data resources which had been collected and summarized prior to the initiation of this study were availabile for analysis. However, the requirements for extensive data resources necessitated additional data collection activities to supplement the existing information.

A survey of commercial, industrial and government organizations was conducted shortly after the beginning of the study. Organizations contacted either manufactured, used or were similarly connected with one or more of the interconnection technologies. Information requested included field experience data, pre-production and production equipment tests, failure analysis reports and physical construction details. A sum total of over 400 organizations were contacted. Approximately 10% of all organizations contacted during the data collection effort submitted information pertaining to printed wiring or alternative types of interconnection assemblies. Additionally, a GIDEP (Government Industry Data Exchange Program), Urgent Data Request was submitted and circulated. However, no significant results came of this action. A primary concern of the majority of contributors was the proprietary nature of the information and the desire to remain anonymous. For this reason, none of the data contributors in this study will be identified.

A prerequisite to the summarization of data was the identification of all parameters and factors influencing the reliability of interconnection assemblies. A task was defined at the beginning of the program whose goal was a reliability evaluation based solely on theoretical considerations. These theoretical studies served to identify the important parameters which were then further investigated using data analysis. Identification of construction details and process controls which were theoretically believed to have an effect on reliability were pursued for each source of data.

All data items received during the data collection efforts were reviewed for completeness of deta—and examined for any inherent biases. Any data submittal which displayed obvious biases was not considered in this study. Those reports lacking sufficient detail were not considered until the necessary additional information was acquired.

A summary of the collected and reduced data is given in Table 3.1. Table 3.1 presents assembly operating hours, connection operating hours and recorded failures for each type of interconnection technology. It is emphasized that the recorded failures for printed wiring assemblies include both printed wiring board and solder connection failures. The number of connection operating hours is obtained simply by multiplying the number of connections on the assembly by the operating hours.

TABLE 3.1: DATA SUMMARY BY TECHNOLOGY

| Technology                                       | Assy. Hrs.<br>(x 10 <sup>6</sup> ) | Connection<br>Hrs. (x 10 <sup>6</sup> ) | Failures |

|--------------------------------------------------|------------------------------------|-----------------------------------------|----------|

| Wave Soldered<br>Printed Wiring                  | 950.876                            | 348,502.940                             | 81       |

| Reflow Soldered<br>Printed Wiring                | *                                  | 48,445.115                              | 4        |

| Solderless Wrap                                  | *                                  | 328,956.105                             | 4        |

| Wrapped and Soldered                             | *                                  | 3,056.630                               | 0        |

| Clip Termination                                 | 16.530                             | 1,670.368                               | 0        |

| Discrete Wiring w/Elec-<br>troless Deposited PTH | 0.546                              | 477.204                                 | 1        |

<sup>\*</sup>Precise values for assembly operating hours not available

3.2 Failure Rate Distribution Considerations. The interconnection assembly data base contains no time-to-failure data. As a result, only the exponential failure rate distribution with its underlying constant failure rate could have been considered to model the predicted failure rate. The exponential distribution provides many advantages in regard to reliability modeling. Use of the exponential distribution is consistent with existing MIL-HDBK-217C failure rate prediction models, provides for maximum data utilization and offers a simple calculation for mean time to failure (MTTF). However, accelerated testing has demonstrated that nonelectronic parts including interconnection assemblies follow an increasing, time dependent failure rate. This section provides a discussion considering whether the exponential distribution can adequately describe the failure rate of printed wiring assemblies.

The test conditions which printed wiring assemblies are often exposed to consist of thermal cycling in the range of roughly -50°C to 100°C. Each thermal cycle creates stress in the copper plated through hole which can exceed the elastic region of the copper stress-strain curve. When the elastic region of the stress-strain curve is exceeded, the plated through hole remains slightly deformed even after the applied stress is eliminated. The continuous cycling induces fatigue type failures resulting from the accumulated effect of each successive thermal cycle. These failures are clearly time dependent. The yield point on the stress-strain curve represents the division between the elastic and plastic ranges. The yield point is estimated at between 20,000 psi to 65,000 psi for the copper plating.

Initially consideration was given to printed wiring assemblies operating in relatively benign conditions. The temperature differences observed in the benign environments do not approach the levels tested in the laboratory. The induced stress in the copper plated through hole does not approach the yield point of the stress-strain curve and fatigue induced failures are not observed. Failures observed in the relatively benign environments generally relate to poor quality copper plating or random

(time independent) high stress levels which exceed the ultimate strength of the plated through holes or the solder connections. While acknowledging that wearout failures will still occur, the conclusion is that the failure rate for printed wiring assemblies operating in benign environments closely follows an exponential distribution over the intended life of the equipment. The environment classifications which are considered relatively benign are ground benign, ground fixed, naval submarine, space flight and naval sheltered.

In the case of application environments which do include severe thermal cycling, time dependent fatigue type failures would be expected to If a fixed population of plated through hole printed wiring assemblies were allowed to complete a life history, an increasing failure rate distribution could be estimated. However, since the state of the art in the electronics industry changes at a rapid rate, electrical equipment that is designed today will be obsolete in roughly ten years. In 1970, the current widespread use of multilayer technology was not observed and with the advent of higher density VLSI circuitry and chip carriers, the present printed wiring boards already face certain unavoidable changes. years of continuous operating time, a single plated through hole would not come close to recording sufficient operating hours to expect even one failure in the harshest avionic environment. Ten years is a relatively short time compared to MTBF for printed wiring assemblies. The conclusion was made that the failure rate for printed wiring assemblies does not become dominated by wearout failures until a long time after the intended use of the equipment. Additionally it was concluded that the failures observed during this study effort were primarily random occurrences of high stress levels and that the exponential distribution can approximate the failure rate of printed wiring assemblies operating in any environment over the intended lifetime of the equipment. Occurrences of random high stress levels which may exceed the ultimate strength of the plated through holes or solder connections would not be unusual in a stressful environment classification such as airborne, uninhabited fighter.

For the purposes of this study, it was concluded that utilization of the exponential distribution for each application provides accurate failure rate predictions.

## 4. FAILURE RATE PREDICTION MODEL DEVELOPMENT

## 4.1 Printed Wiring Assemblies.

4.1.1 Proposed Failure Rate Prediction Model. This section presents the proposed failure rate prediction model for printed wiring assemblies. This recommended addition to the existing MIL-HDBK-217C models is the result of analyses performed on the data base compiled during the study. The failure rate prediction model for printed wiring assemblies is:

$\lambda_{p} = \lambda_{b} \pi_{Q} \pi_{E} \Sigma [N_{i} (\pi_{C} + \pi_{Si})]$  where

$\lambda_b$  = base failure rate = .000041 failures/10<sup>6</sup> hrs.

$\pi_Q$  = quality factor, Table 4.1-3

$\pi_E$  = environmental factor, Table 4.1-4

$N_1$  = quantity of wave soldered plated through holes

$N_2$  . = quantity of hand soldered plated through holes

$\pi_{C}$  = complexity factor, Table 4.1-1

$\pi_{Si}$  = solder application factors, Table 4.1-2

The remaining sections pertaining to printed wiring assembly failure rate prediction model development give the detailed procedures which resulted in the above failure rate prediction model and the numerical values given in Tables 4.1-1 through 4.1-4.

TABLE 4.1-1

COMPLEXITY FACTOR

| # of circuit planes | <sup>π</sup> C |

|---------------------|----------------|

| <u>&lt; 2</u>       | 1              |

| 3                   | 1.3            |

| 4                   | 1.5            |

| 5                   | 1.8            |

| 6                   | 2.0            |

| 7                   | 2.2            |

| 8                   | 2.4            |

| 9                   | 2.6            |

| 10                  | 2.7            |

| 11                  | 2.9            |

| 12                  | 3.1            |

| 13                  | 3.2            |

| 14                  | 3.4            |

| 15                  | 3.5            |

| 16                  | 3.7            |

for greater than 16 circuit planes

$\pi_{C} = 0.65 \text{ l.63}$

l = quantity of circuit planes

TABLE 4.1-2

SOLDER APPLICATION FACTOR

| Process     | Rework Percentage | <sup>π</sup> S |

|-------------|-------------------|----------------|

| Wave Solder | 0 - 5             | 0              |

|             | 6 - 10            | 0.2            |

|             | 11 - 15           | 0.9            |

|             | 16 - 20           | 1.5            |

|             | 21 - 25           | 2.2            |

|             | 26 - 30           | 2.9            |

|             | 31 - 35           | 3.6            |

|             | 36 - 40           | 4.3            |

|             | over 40           | 6.1            |

|             | Unknown           | 6.1            |

| Hand Solder | Not applicable    | 13             |

TABLE 4.1-3

QUALITY FACTOR

| Quality Grade                                        | $Q^{T}$ |

|------------------------------------------------------|---------|

| Manufactured to MIL-SPEC or equivalent IPC standards | 1       |

| Lower quality grade                                  | 10      |

TABLE 4.1-4

ENVIRONMENTAL FACTOR

| Environment | "E  |

|-------------|-----|

| GB          | 1   |

| SF          | 1   |

| GF          | 2.3 |

| NSB         | 4.1 |

| NS          | 5.3 |

| AIT         | 3.8 |

| Мр          | 6.9 |

| MFF         | 8.7 |

| MFA         | 12  |

| $G_M$       | 7.7 |

| NH          | 13  |

| NUU         | 14  |

| AUT         | 8.2 |

| NU          | 12  |

| AIF         | 7.7 |

| ARW         | 19  |

| USL         | 26  |

| AUF         | 16  |

| ML          | 29  |

| $C_L$       | 500 |

4.1.2 Preliminary Assumptions and Methodology. The methodology necessary to extract an accurate and useful failure rate prediction model from the vast number of variables affecting printed wiring assembly reliability is included in this section. Assumptions based on theoretical discussions and/or data analysis are noted as they occur in the prediction model development process.

Variables considered to effect printed wiring assembly failure rate are given in Table 4.1-5. These variables are divided into two major categories: (1) Construction details and process controls, and (2) Environmental stresses. The assumption is made that the printed wiring assembly failure rate  $(\lambda_p)$  can be expressed as a function of construction details and process controls multiplied by a function of environmental stresses. A series of environmental factors  $(\pi_E)$  was used to define the function of environmental stresses. They were normalized to a value of one corresponding to printed wiring assemblies operating in the ground, benign environment. In equation form:

$\lambda_{\rm D}$  = f (construction details, process controls)  $\pi_{\rm E}$

where

$\lambda_p$  = printed wiring assembly failure rate

$\pi_F = environmental factor$

This is consistent with existing MIL-HDBK-217C failure rate prediction models. This is also a necessary assumption because environment conditions such as temperature cycling vary within an environment classification, and that specific information would not be available during the design stage of equipment when failure rate predictions prove most beneficial.

## TABLE 4.1-5

## FACTORS INFLUENCING PRINTED WIRING ASSEMBLY FAILURE RATE

- o Construction Details and Process Controls

- Number of plated through holes (PTH)

- Number of circuit planes

- Foil weight

- PTH plating thickness

- PTH diameter

- Number of solder connections

- Method of solder application

- Amount of rework necessary on solder connections

- Solderability of component leads

- Type of conformal coating, if any

- o Environmental Stresses

- Effect of temperature cycling

- Effect of thermal shock

- Effect of humidity

- Effect of random vibration

- Effect of sine vibration

- Effect of mechanical shock

The function of construction details and process controls was assumed equal to the sum of the failure rate contribution of the plated through hole, the failure rate contribution of the solder connections and the combined other failure rate contributions. In equation form:

$$\lambda p = [\lambda p, pth + \lambda p, ws + \lambda p, other]^{\pi}E$$

where

$\lambda_{p,pth}$  = failure rate contribution of the plated through holes

$\lambda_{p,WS}$  = failure rate contribution of the solder connections

$\lambda_{p,other}$  = combined other failure rate contributions

This assumption considers the three subcomponents of the failure rate equation to be independent. This is a reasonable assumption and will be discussed later in this section.

The three subcomponents which define the function of construction details and process controls were initially considered separately. The plated through hole (PTH) failure rate contribution includes not only plated through hole failures, but PTH associated failures such as open circuits resulting from fractures between the PTH and an internal land.

Both theoretical discussions and data analysis revealed that the two dominant variables affecting PTH failure rate contribution are the total number of PTH's and the total number of circuit planes on the considered printed wiring assembly.

The assumption was made that the failure rate contribution for an individual PTH is independent of the total number of PTH's and is constant for a particular number of circuit planes. The failure rate contribution of the PTHs is given by the following equation:

$$\lambda p, pth = \lambda pth (\ell) N$$

where

$\lambda_{pth}(\ell)$  = individual PTH failure rate as a function of  $\ell$

l = number of circuit planes

N = quantity of PTHs

It is noted that the notation used,  $\lambda_{pth}(\ell)$ , represents failure rate as a function of circuit plane quantity and should not be confused with the use of parenthesis to denote multiplication. This term,  $\lambda_{pth}(\ell)$ , will be the only term which uses this notation.

Next, the failure rate contribution of wave solder connections was considered. The wave solder failure rate contribution is highly variable, depending on the total number of solder connections, the solderability of the component leads, the amount of rework necessary after the printed wiring assembly passes through the solder wave, the printed wiring assembly design and other factors. The assumption was made that the total number of solder connections and the amount of rework are the two dominant variables affecting the failure rate contribution of wave solder connections. Factors such as solderability of component leads and printed wiring assembly design are not included directly in the model. However, the amount of necessary rework gives an indication of solderability and design, and therefore, the influence of these factors was not neglected. Additionally, the amount of rework is important because the reworked solder connection will inherently have a higher failure rate due to the variability of direct human involvement.

The net failure rate contribution of solder connections was assumed proportional to the total number of solder connections. Additionally, the

average failure rate of an individual solder connection was assumed independent of the total number of solder connections. In equation form:

$$\lambda_{D-WS} = \lambda_{WS} n$$

where

$\lambda_{WS}$  = average solder connection failure rate

n = quantity of solder connections

Since the average solder connection failure rate  $(\lambda_{WS})$  is a variable depending on rework percentage, it was desirable to define several special cases. Notation listed below is for  $\lambda_{WS}$  when (1) there is zero necessary rework, (2) there is total or 100% rework and (3) there is an average rework percentage. Additionally, the rework percentage will be denoted as x.

$\lambda_0 = \lambda_{WS}$ , (x = 0, zero rework)

$\lambda_{rw} = \lambda_{ws}$ , (x = 1, total rework)

$\lambda \overline{y} = \lambda_{WS}$ , (x =  $\overline{x}$ , average rework)

$x = rework percentage (0 \le x \le 1)$

$\overline{x}$  = average rework percentage

$\overline{x}$  represents a constant value of rework and therefore  $\lambda_{\overline{X}}$  is a constant value. Similarly,  $\lambda_0$  and  $\lambda_{rw}$  are constant values for the remainder of the model development process.

Average solder connection failure rates for the three special cases have the following relation:

$$\lambda_{rw} > \lambda_{\overline{x}} > \lambda_0$$

It should be intuitively clear that this relation is correct. The relation simply states that failure rate is an increasing function of rework percentage. The inequality is also informative because the zero rework and total rework cases represent the minimum and maximum possible values for average solder connection failure rate ( $\lambda_{WS}$ ). Failure rates for rework percentages not at zero, total or average values were defined as a linear function between the two extremes.

$$\lambda_{WS} = \lambda_{O} (1 - x) + \lambda_{rW} x$$

where all variables have been previously defined

It is noticed that the above equation collapses to the correct values when x = 0, or x = 1, is used. The above relation is shown graphically in Figure 4.1-1.

Although the equation for  $\lambda_{WS}$  is in a simple form, it is desirable to transform the equation in order to simplify the process of adding the failure rate contribution of the plated through holes to the failure rate contribution of the solder connections. The transformed equation is:

$$\lambda_{WS} = \lambda_{\overline{X}} + D$$

where

$\lambda \overline{\chi}$  =  $\lambda_{WS}$  when rework percentage is at an average value

D = deviation from  $\lambda \mathbf{x}$  to complete equality

D must be a function of rework percentage for the given equality.  $\lambda_{\overline{X}}$  can be solved for by using the equation:

$$\lambda_{WS} = \lambda_0 (1 - x) + \lambda_{W} \overline{x}$$

$$\lambda_{\overline{X}} = \lambda_0 (1 - \overline{X}) + \lambda_{rw} \overline{X}$$

FIGURE 4.1-1 AVERAGE WAVE SOLDER CONNECTION FAILURE RATE VS. REWORK PERCENTAGE

This relation can be used to solve for D by the following steps:

$$\lambda_{WS} = \lambda_{\overline{X}} + D$$

$$\lambda_{O} (1 - x) + \lambda_{rW}x = \lambda_{O} (1 - \overline{x}) + \lambda_{rW}\overline{x} + D$$

$$\lambda_{O} + (\lambda_{rW} - \lambda_{O})x = \lambda_{O} + (\lambda_{rW} - \lambda_{O})\overline{x} + D$$

$$(\lambda_{rW} - \lambda_{O})x = (\lambda_{rW} - \lambda_{O})\overline{x} + D$$

$$D = (\lambda_{rW} - \lambda_{O}) (x - \overline{x})$$

Substituting this relation for D into the equation for average solder connection failure rate results in:

$$\lambda_{WS} = \lambda_{\overline{X}} + (\lambda_{rW} - \lambda_0) (x - \overline{x})$$

which is mathematically identical to the original equation for  $\lambda_{WS}$  and is also shown graphically by Figure 4.1-1.

Sustituting into the equation for net failure rate contribution of solder connections, the result is:

$$\lambda_{p,WS} = [\lambda_{\overline{X}} + (\lambda_{rW} - \lambda_0) (x - \overline{x})] n$$

Since it was the objective of this study to formulate a single printed wiring assembly failure rate prediction model, the feasibility of adding the solder connection failure rate contribution term to the relation developed for plated through hole failure rate contribution was considered. Therefore, it was necessary to investigate the ratio of the quantity of solder connections to the quantity of plated through holes (n/N ratio). In many cases this ratio is equal to unity. However, many other examples of printed wiring assemblies exist which have "via" holes or