# **NASA HANDBOOK**

# NASA-HDBK 8739.23 Baseline with Change 1

National Aeronautics and Space Administration Washington, DC 20546

Baseline approved: 2011-02-16 Change 1 approved: 2011-03-29

# NASA COMPLEX ELECTRONICS HANDBOOK FOR ASSURANCE PROFESSIONALS

# **Measurement System Identification: Metric**

APPROVED FOR PUBLIC RELEASE – DISTRIBUTION IS UNLIMITED

**Mars Exploration Rover (2003)**

# **DOCUMENT HISTORY LOG**

| Status   | Document<br>Revision | Approval Date Description |                                                      |

|----------|----------------------|---------------------------|------------------------------------------------------|

| Baseline |                      | 2011-02-16                | Initial Release (JWL4)                               |

|          | Change 1             | 2011-03-29                | Editorial correction to page 2 figure caption (JWL4) |

This document is subject to reviews per Office of Management and Budget Circular A-119, Federal Participation in the Development and Use of Voluntary Standards (02/10/1998) and NPR 7120.4, NASA Engineering and Program/Project Management Policy.

Downloaded from http://www.everyspec.com

NASA-HDBK 8739.23 with change 1

This page intentionally left blank.

NASA-HDBK 8739.23 with change 1

## **FOREWORD**

This NASA Handbook (NASA-HDBK) is approved for use by NASA Headquarters and NASA Centers, including Component Facilities. This NASA-HDBK may be applied on contracts per contractual documentation as a reference or training publication.

Comments and questions concerning the contents of this publication should be referred to the National Aeronautics and Space Administration, Director, Safety and Assurance Requirements Division, Office of Safety and Mission Assurance, Washington, DC 20546.

Requests for information, corrections, or additions to this NASA-HDBK shall be submitted via "Feedback" in the NASA Technical Standards System at http://standards.nasa.gov or to National Aeronautics and Space Administration, Director, Safety and Assurance Requirements Division, Office of Safety and Mission Assurance, Washington, DC 20546.

| s/ Bryan O'Connor                   | February 16, 2011 |

|-------------------------------------|-------------------|

| Bryan O'Connor                      | Approval Date     |

| Chief, Safety and Mission Assurance |                   |

The Office of Safety and Mission Assurance would like to recognize Kalynnda Berens and Richard Plastow for their work in authoring this publication.

Downloaded from http://www.everyspec.com

NASA-HDBK 8739.23 with change 1

This page intentionally left blank.

# **TABLE OF CONTENTS**

| CHAP | TER 1. Overview                                    | 11 |

|------|----------------------------------------------------|----|

| 1.1  | Purpose                                            | 11 |

| 1.2  | Scope                                              | 11 |

| 1.3  | Anticipated Audience                               | 12 |

| 1.4  | Handbook Layout                                    | 12 |

| СНАР | PTER 2. Reference Documents and Links              | 13 |

| 2.1  | Reference Documents                                | 13 |

| 2.2  | Links                                              | 14 |

| СНАР | PTER 3. Definitions and Acronyms                   | 15 |

| 3.1  | Definitions                                        | 15 |

| 3.2  | Acronyms                                           | 20 |

| CHAP | PTER 4. Complex Electronics Overview               | 23 |

| 4.1  | Blurring the Hardware/Software Line                | 23 |

| 4.2  | Programmable versus Designable Devices             | 25 |

| 4.3  | Simple Programmable Logic Devices                  | 27 |

| 4.4  | Complex Programmable Logic Devices (CPLD)          | 28 |

| 4.5  | Field Programmable Gate Array (FPGA)               | 30 |

| 4.6  | Application Specific Integrated Circuit (ASIC)     | 30 |

| 4.7  | System-on-Chip (SoC)                               | 30 |

| 4.8  | Concerns and Issues                                | 31 |

| 4.9  | Summary                                            | 32 |

| CHAP | PTER 5. Design Process                             | 33 |

| 5.1  | Overview of the Complex Electronics Design Process | 33 |

| 5.2  | Requirements and Specifications                    | 36 |

| 5.3  | Design Entry                                       | 37 |

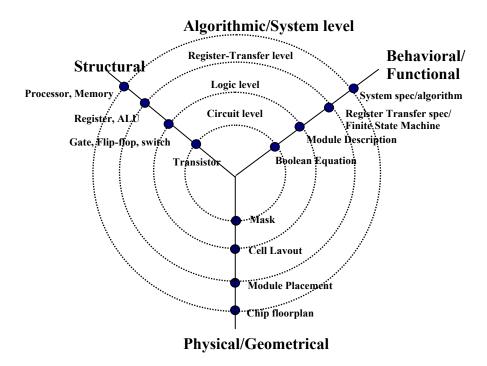

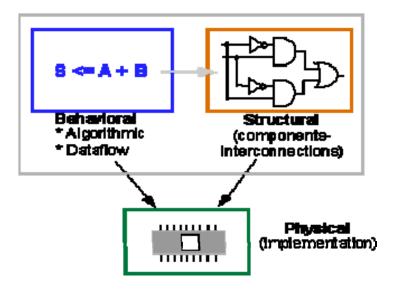

| 5.4  | Abstraction                                        |    |

| 5.5  | Hardware Description Languages                     | 42 |

| 5.6  | Programming Example                                | 48 |

| 5.7  | Synthesis                                          | 48 |

| 5.8  | Implementation                                     | 53 |

| 5.9  | Verification                                       | 58 |

| CHAP'                     | TER 6. Process Assurance                               | 64  |

|---------------------------|--------------------------------------------------------|-----|

| 6.1                       | Process Assurance Overview                             | 64  |

| 6.2                       | Identifying Complex Electronics                        | 67  |

| 6.3                       | Process Assurance Activities                           | 69  |

| CHAP                      | ΓER 7. Future Trends                                   | 79  |

| 7.1                       | Changes in Complex Electronics Design and Verification | 79  |

| 7.2                       | Into the Not so Distant Future                         | 81  |

| 7.3                       | NASA Assurance Changes                                 | 83  |

| APPEN                     | IDIX A Examples                                        | 85  |

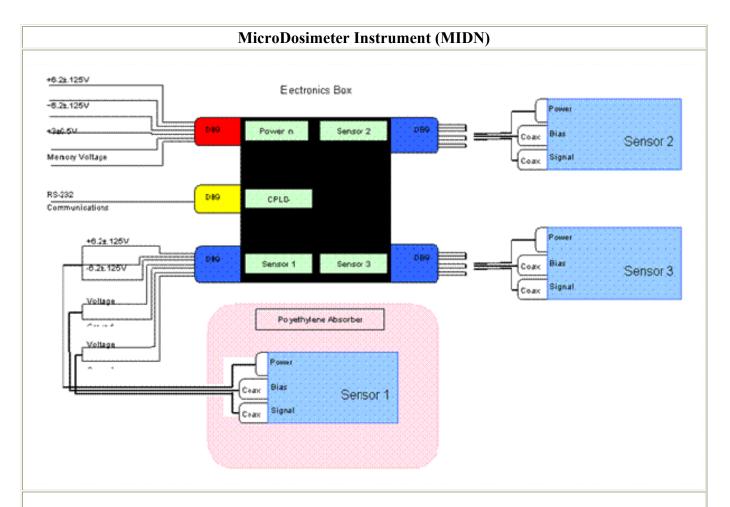

| <b>A</b> .1               | CPLD                                                   | 85  |

| A.2                       | FPGA                                                   | 89  |

| A.3                       | ASIC                                                   |     |

| A.4                       | SoC                                                    | 101 |

| A.5                       | Reconfigurable Computing                               |     |

| APPEN                     | DIX B Coding Style Guidelines                          | 112 |

| B.1                       | Introduction                                           |     |

| B.2 Top-Down Design       |                                                        |     |

| B.3 Signals and Variables |                                                        |     |

| B.4                       | Packages                                               |     |

| B.5                       | Technology-Specific Code (Xilinx)                      |     |

| B.6                       | Coding for Synthesis                                   |     |

|                           | LIST OF TABLES                                         |     |

| Table 1.                  | Compley Electronics Evenules                           | 26  |

| Table 1: Table 2:         | Complex Electronics Examples                           |     |

| Table 3:                  | 1                                                      |     |

| Table 4:                  | VHDL vs. Verilog.                                      |     |

| Table 5:                  | FPGA vs. ASIC Comparison                               | 57  |

| Table 6:                  | Requirement Verification Activities                    |     |

| Table 7:                  |                                                        |     |

| Table 8:                  | Design Synthesis Verification Activities               |     |

| Table 9: Table 10         | Implementation Verification Activities                 |     |

| Table 11                  | $\epsilon$                                             |     |

| 1 4010 11                 | . omple complexity outdomics                           | 00  |

# LIST OF FIGURES

| Figure 1:   | How Complex Electronics Compares.                                       | . 23 |

|-------------|-------------------------------------------------------------------------|------|

| Figure 2:   | Example of PAL Structure                                                | . 27 |

| Figure 3:   | CPLD vs. FPGA Layout                                                    | . 29 |

| Figure 4:   | SoC Example Configuration                                               | . 31 |

| Figure 5:   | CE vs. SW Life Cycles                                                   | . 33 |

| Figure 6:   | Example CE Waterfall Development                                        | . 34 |

| Figure 7:   | Complex Electronics Design Views                                        |      |

| Figure 8:   | Complex Electronics Domains                                             | . 41 |

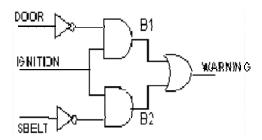

| Figure 9:   | Warning Buzzer Example                                                  | . 41 |

| Figure 10:  | General HDL Development                                                 | . 45 |

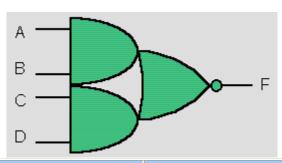

| Figure 11:  | AOI VHDL to Verilog Comparison                                          | . 51 |

| Figure 12:  | External Programmer                                                     | . 56 |

| Figure A-1  | CPLD                                                                    | . 85 |

| Figure A-2  | FGPA                                                                    | . 89 |

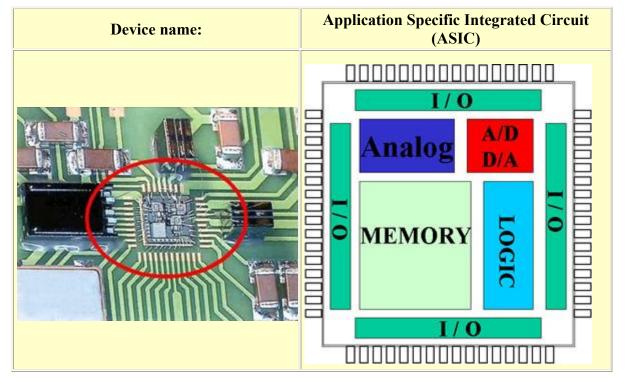

| Figure A-3  | ASIC                                                                    | . 95 |

| Figure A-4  | ASIC Die                                                                | . 96 |

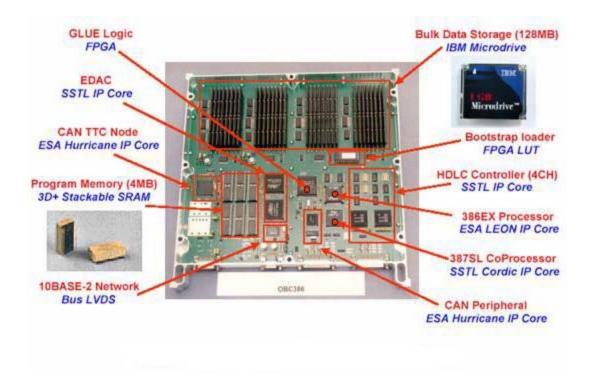

| Figure A-6  | Reconfigurable SoC                                                      | 103  |

| Figure A-7  | ChipSat OBC                                                             | 106  |

| Figure B-1  | Behavioral Code                                                         | 112  |

| Figure B-2  | Structural Code                                                         | 113  |

| Figure B-3  | One Line Per Signal/Named Association                                   | 114  |

| Figure B-4  | Header Template                                                         |      |

| Figure B-5  | Process, Function, and Procedure Header                                 | 115  |

| Figure B-6  | Inline Comments                                                         | 115  |

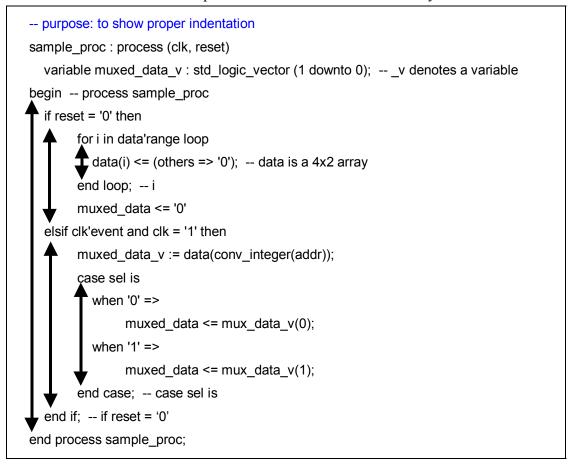

| Figure B-7  | Proper Indentation                                                      | 116  |

| Figure B-8  | Confusing in and out suffixes                                           | 118  |

| Figure B-9  | Internal Signals Representing Output Ports                              | 118  |

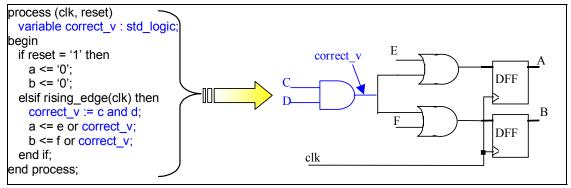

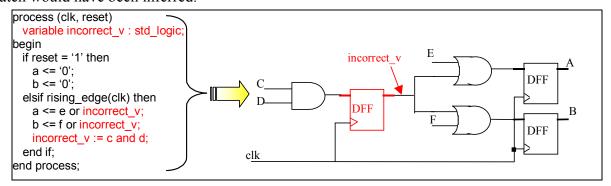

| Figure B-10 | Correct Use of Variables                                                |      |

| Figure B-11 | Incorrect Use of Variables                                              | 122  |

| Figure B-12 | A Constant Guiding the Generation of Logic                              | 123  |

|             | Address Width Defined by a Constant                                     |      |

| Figure B-14 | Modular Function Use                                                    | 125  |

| Figure B-15 | Use of Types and Aliases                                                | 126  |

|             | Three-state Implementation of 4:1 Multiplexer                           | 129  |

| Figure B-17 | Xilinx LUT-RAM Inference                                                | 130  |

|             | LUT-ROM Inference                                                       |      |

| Figure B-19 | Virtex Block RAM inference                                              | 131  |

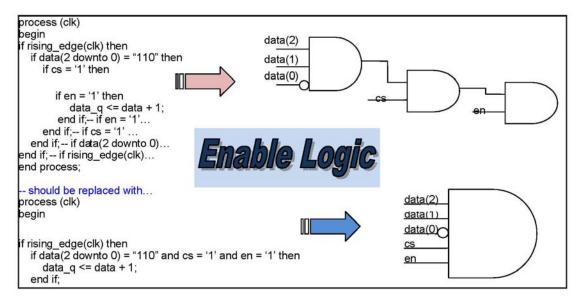

| Figure B-20 | Clock Enable Inference                                                  | 133  |

| Figure B-21 | Inference of Xilinx Shift Register LUT (SRL)                            | 134  |

|             | Local Asynchronous Reset and TC & Well-Behaved Synchronous Reset & CE.  |      |

|             | Well Behaved Local Asynchronous Reset and TC & Well-Behaved Synchronous |      |

| _           | Reset & CE                                                              | 136  |

| Figure B-24 | Priority Encoded Logic                                                  | 141  |

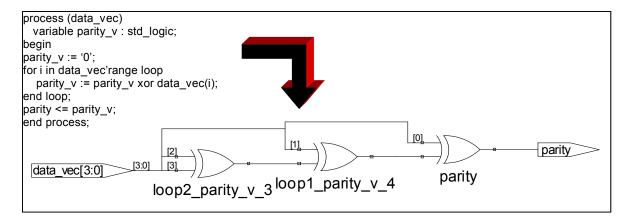

| Figure B-25 | For-Loop Cascaded Logic Implementation                                  | 142  |

|             |                                                                         |      |

# NASA-HDBK 8739.23 with change 1

| Figure B-26 | Latch Inference                            | 143 |

|-------------|--------------------------------------------|-----|

| Figure B-27 | Elimination of Inadvertent Latch Inference | 143 |

# NASA COMPLEX ELECTRONICS HANDBOOK FOR ASSURANCE PROFESSIONALS

#### CHAPTER 1. OVERVIEW

#### 1.1 PURPOSE

Complex electronics (CE) encompasses programmable and designable complex integrated circuits. "Programmable" logic devices (PLDs) can be programmed by the user and range from simple chips to complex devices capable of being programmed on-the-fly. Some types of programmable devices this handbook will address are:

- Field Programmable Gate Array (FPGA)

- Complex Programmable Logic Device (CPLD)

- Application-Specific Integrated Circuit (ASIC)

- System-on-chip (SoC)

"Designable" logic devices are integrated circuits that can be designed but not programmed by the user. The design is submitted to a manufacturer for implementation in the device. ASICs are an example of a designable device.

Development of assurance methodologies for complex electronics is lagging behind the pace of the technology. Complex electronics are commonly used within NASA systems, sometimes in safety-critical systems. Both software assurance and quality assurance engineers need to understand what these devices are, where they are used, and how they are designed. However, the development of assurance activities for complex electronics is lagging behind the pace of the technology. This handbook provides some general suggestions that, if applied, may increase confidence in the quality of complex electronic devices.

#### 1.2 SCOPE

This Handbook will provide an overview of complex electronics, the design process, and assurance activities. It discusses:

- Which devices are "complex electronics," and which are not.

- What each device is and examples of use on NASA projects.

- How electronics engineers design and program the devices.

- What assurance and verification activities can be used for complex electronics.

- Future trends in the design and assurance of complex electronics.

Additional assurance activities for complex electronics devices may be required in the future. While this handbook will not prepare you to perform those activities, it will provide you with a general understanding of the devices and the design and assurance activities. You will be able to "speak the language" when communicating with the hardware design engineers.

#### 1.3 ANTICIPATED AUDIENCE

1.3.1 This handbook is primarily intended for software assurance and quality assurance engineers who do not have significant experience with complex electronics. You do not need a hardware background to understand the material in this handbook. However, being familiar with embedded systems or flight hardware may help you understand some of the concepts.

System safety personnel are encouraged to review this handbook. Modern technology, especially electronics, is changing at a rapid pace. Projects and systems you support will be using these devices in the near future, if they are not already doing so.

Software and electronic engineers are encouraged to review this handbook. An understanding of the assurance activities and concepts discussed in the handbook may be helpful to you in supporting projects and systems.

#### 1.4 HANDBOOK LAYOUT

Chapter 1 provides the purpose, scope, and layout for the handbook.

Chapter 2 provides a list of reference documents and useful links.

Chapter 3 provides definitions and acronyms used in this handbook.

Chapter 4 gives an overview of complex electronics, describes why assurance engineers need to be aware of complex electronics and details some concerns and issues with the current state of assurance activities.

Chapter 5 describes the design process for complex electronics. A short explanation of hardware description languages, along with a simple example, is included.

Chapter 6 provides an overview of current and suggested assurance practices for complex electronics. This section also contains an overview of process assurance.

Chapter 7 discusses some future trends in design and assurance of complex electronics.

Appendix A describes each of the types of complex electronics in detail.

Appendix B contains the Hardware Description Language Coding Standard from Xilinx.

#### CHAPTER 2. REFERENCE DOCUMENTS AND LINKS

## 2.1 REFERENCE DOCUMENTS

The documents listed in this chapter provide additional information supporting this NASA-HDBK. The latest issuance of cited documents should be used unless otherwise stated in this NASA-HDBK. The applicable documents are accessible via the NASA Online Directives Information System at http://nodis3.gsfc.nasa.gov/ or directly from the Standards Developing Organizations (SDO) or other document distributors.

#### **2.1.1 GOVERNMENT DOCUMENTS:**

#### NASA Documents:

NPR 7150.2 NASA Software Engineering Requirements

NASA-STD 2201-91 NASA Software Configuration Management Guidebook

(http://satc.gsfc.nasa.gov/GuideBooks/cmpub.html)

NASA-STD 8709.22 Safety and Mission Assurance Acronyms, Abbreviations, and

**Definitions**

NASA-STD 8719.13 Software Safety Standard

NASA-STD 8739.8 Software Assurance Standard

NASA-GB 8719.13 NASA Software Safety Guidebook

(http://www.hq.nasa.gov/office/codeq/doctree/871913.pdf)

NASA-GB A201 Software Assurance Guidebook

(http://satc.gsfc.nasa.gov/assure/agb.txt)

NASA-GB A301 Software Quality Assurance Audits Guidebook

(http://satc.gsfc.nasa.gov/audit/audgb.txt)

## Other Government Documents:

DO-254 Design Assurance Guidance for Airborne Electronic Hardware (Federal

Aviation Administration (FAA))

MIL-STD 882D Standard Practice for System Safety (Department of Defense (DoD))

#### 2.1.2 INTERNATIONAL CONSENSUS STANDARDS:

## <u>Institute of Electrical and Electronics Engineers (IEEE)</u>

IEEE 830-1998 IEEE Recommended Practice for Software Requirements Specifications

IEEE 1194.1-1990 IEEE Standard Test Access Port and Boundary Scan Architecture

IEEE 1228-1994 IEEE Standard for Software Safety Plans

# 2.2 LINKS

# NASA-related Links

| URL                            | Description                                 |

|--------------------------------|---------------------------------------------|

| http://nepp.nasa.gov/index.cfm | NASA Electronic Parts and Packaging Program |

# Other Links

| URL                                                                                             | Description                       | FPGA | Reconfig.<br>Comput. | VHDL | Verilog | Other |

|-------------------------------------------------------------------------------------------------|-----------------------------------|------|----------------------|------|---------|-------|

| http://klabs.org/richcontent/Tutorial/tutorial.htm                                              | Tutorials<br>Information<br>Links | х    | х                    |      |         | х     |

| http://www.icd.com.au/vhdl.html                                                                 | Tutorials                         | Х    | х                    | Х    |         |       |

| http://www.epanorama.net/links/fpga.html                                                        | Information                       | Х    |                      | Х    |         |       |

| http://www.verilogtutorial.info/                                                                | Tutorial                          |      |                      |      | Х       |       |

| http://www.asic-<br>world.com/verilog/veritut.html                                              | Tutorial                          |      |                      |      | х       |       |

| http://www.gmvhdl.com/VHDL.html                                                                 | Tutorial                          |      |                      | Х    |         |       |

| http://www.doulos.com/knowhow/                                                                  | Tutorial<br>Information           |      |                      | х    | х       | х     |

| http://www.cs.ucr.edu/content/esd/labs/tuto<br>rial/                                            | Information                       |      |                      | х    |         |       |

| http://instruct1.cit.cornell.edu/courses/ee47<br>5/tutorial/VHDLTut.htm                         | Tutorial<br>Links                 |      |                      | х    |         |       |

| http://www.systemc.org/                                                                         | Information                       |      |                      |      |         | Х     |

| http://www.acc-<br>eda.com/vhdlref/refguide/vhdl_examples_g<br>allery/vhdl_examples_gallery.htm | Examples                          |      |                      | x    |         |       |

| http://www.vhdl.org/                                                                            | Information                       |      |                      | Х    | Х       | Х     |

| http://www.vhdl.org/vhdlsynth/vhdlexample s/                                                    | Examples                          |      |                      | х    |         |       |

| http://www.acc-<br>eda.com/vhdlref/refguide/toclist.htm                                         | Information                       |      |                      | х    |         |       |

| http://www.mrc.uidaho.edu/fpga/index.php                                                        | Information                       | Х    |                      |      |         |       |

| http://www.fpga4fun.com/                                                                        | Information                       | Х    |                      |      |         |       |

| http://equipe.nce.ufrj.br/gabriel/vhdlfpga.html                                                 | Links                             | х    |                      | х    |         |       |

| http://www.fuse-<br>network.com/fuse/training/index.html                                        | Training<br>Material              | x    |                      |      |         | х     |

| http://www.radio-<br>electronics.com/info/data/semicond/asic/as<br>ic.php                       | ASIC on-<br>line book             |      |                      |      |         | х     |

| http://www.netrino.com/Articles/RCPrimer/                                                       | Tutorial                          |      | Х                    |      |         |       |

| http://www.cotsjournalonline.com/                                                               | Journal                           |      |                      |      |         | х     |

| http://www.fpgajournal.com/                                                                     | Journal                           | х    |                      |      |         |       |

#### CHAPTER 3. DEFINITIONS AND ACRONYMS

#### 3.1 **DEFINITIONS**

Note: Definitions for safety and mission assurance terms are found in NASA-STD 8709.22, Safety and Mission Assurance Acronyms, Abbreviations, and Definitions. Terms unique to this NASA-Handbook are listed below.

<u>Adequate:</u> When referring to fire protection or life safety, the safeguards necessary to provide facilities and their occupants with protection against all known or recognized hazards.

<u>Antifuse</u>: An electrical device that performs the opposite function as a fuse. Antifuses are widely used to permanently program integrated circuits (ICs) by creating an electrical connection.

<u>Application Specific Integrated Circuit (ASIC):</u> Integrated circuit product customized for a single application.

<u>Architecture</u>: The common logic structure of a family of programmable integrated circuits. The same architecture may be realized in different manufacturing processes.

<u>Asynchronous</u>: A signal whose data is acknowledged or acted upon immediately, irrespective of any clock signal.

**Boundary scan**: Boundary scan is a methodology allowing complete controllability and observability of the boundary pins of a JTAG (Joint Test Action Group)-compatible device via software control. This capability enables in-circuit testing without the need of in-circuit test equipment.

<u>Cell Library</u>: The collective name for the set of logic functions defined by the manufacturer of an ASIC. The designer decides which types of cells should be realized and connected together to make the device perform its desired function.

Chip: Another name for an integrated circuit.

<u>Codec</u>: Short for compressor/decompressor or coder/decoder, a codec is any technology for compressing and decompressing data. Codecs can be implemented in software, hardware, or a combination of both. Some popular codecs for computer video include MPEG (Moving Picture Experts Group), Indeo, and Cinepak.

<u>Combinatorial</u>: A digital function whose output value is directly related to the current combination of values on its inputs. Also known as combinational.

<u>Comparator (digital)</u>: A logic function that compares two binary values and outputs the results in terms of binary signals representing less-than and/or equal-to and/or greater-than.

<u>Complex Programmable Logic Device (CPLD)</u>: Programmable logic devices characterized by an architecture offering high speed, predictable timing, and simple software.

<u>Configurable/Complex Logic Block (CLB)</u>: The array of multi-input and multi-output logic cells to be programmed. CLB is a configurable logic block that consists mainly of Look-up Tables (LUTs) and flip-flops.

<u>Cores</u>: In the semiconductor design industry, refers to predefined functions such as processors or bus interfaces that are typically licensed from the software developer. Cores can be implemented directly in silicon, either in fixed logic or programmable logic devices, and save chip designers time during product development. Synonymous with Intellectual Property.

Die: An unpackaged integrated circuit. The plural of "die" is also "die".

<u>Digital Signal</u>: A digital signal is a signal whose key characteristic (e.g., voltage or current) falling into discrete ranges of values. Most digital systems utilize two voltage levels (low and high values).

<u>Digital Signal Processor (DSP)</u>: A specialized central processing unit (CPU) used for digital signal processing of signals such as sound, video, and other analog signals which have been converted to digital form. Some uses of DSP are to decode modulated signals from modems; to process sound, video, and images in various ways; and to understand data from sonar, radar, and seismological readings.

<u>Electrically-Erasable Programmable Read-Only Memory (EEPROM)</u>: A memory device whose contents can be electrically programmed by the designer. Additionally, the contents can be electrically erased allowing the device to be reprogrammed.

<u>Electro-Static Discharge (ESD)</u>: The term electro-static discharge refers to a charged person, or object, discharging static electricity. Although the current associated with such a static charge is low, the electric potential can be in the millions of volts and can severely damage electronic components.

<u>Erasable Programmable Read-Only Memory (EPROM)</u>: A memory device whose contents can be electrically programmed by the designer. Additionally, the contents can be erased by exposing the die to ultraviolet light through a quartz window mounted in the top of the component's package.

Falling-Edge: A transition from a logic 1 to a logic 0. Also known as a negative edge.

<u>Field Programmable Gate Array (FPGA)</u>: High density PLD containing small logic cells interconnected through a distributed array of programmable switches. This type of architecture produces statistically varying results in performance and functional capacity, but offers high register counts. Programmability typically is via volatile SRAM (Static Random Access Memory) or one-time-programmable antifuses.

*Firmware*: The combination of a hardware device and computer instructions and/or computer data that reside as read-only software on the hardware device.

<u>First-in first-out (FIFO)</u>: Data structure or hardware buffer where items come out in the same order they came in.

*Flash memory*: Non-volatile storage device similar to EEPROM, but where erasing can only be done in blocks or the entire chip.

<u>Flip-flop</u>: A digital logic circuit that can be switched back and forth between two states.

<u>Floorplanning:</u> The process of identifying structures that should be placed close together on a chip, and allocating space for them.

<u>Fuse</u>: An electrical device that performs the same function as a fuse. Fuses are widely used to permanently program integrated circuits by opening an electrical connection.

<u>Gate</u>: In electronic circuitry, a pathway that may be open or closed, depending on the source of the input, the strength of a signal, or the conductivity of chemicals used in semiconductors. Logic gates are programmed to correspond to related "if-then" statements. The state of an open or closed gate is analogous to the binary state of a 0 or a 1. The application of this analogy allows computing machinery with millions of gates to respond conditionally and to perform logical functions.

<u>Gate Array</u>: Integrated circuit that is customized by interconnecting an array of logic elements. Customization is performed by the manufacturer and typically involves non-recurring engineering costs and several design iterations.

<u>Glue</u>: Generic term for any interface logic or protocol that connects two component blocks. Hardware designers call anything used to connect large VLSIs or circuit blocks "glue logic."

<u>Hardware Description Language (HDL)</u>: A kind of language used for the conceptual design of integrated circuits. Examples are VHDL and Verilog.

<u>Integrated Circuit (IC)</u>: A device in which components such as resistors, capacitors, diodes, and transistors are formed on the surface of a single piece of semiconductor.

<u>In-Circuit Reconfigurable (ICR)</u>: An SRAM-based or similar component which can be dynamically reprogrammed on-the-fly while remaining resident in the system.

<u>In-System Programmable (ISP)</u>: An EEPROM-based, flash-based, or similar component which can be reprogrammed while remaining resident on the circuit board.

<u>JHDL</u>: A structurally based hardware description language implemented with the Java programming language. JHDL is a method of describing (programmatically, in Java) the components and connections in a digital logic circuit. More specifically, JHDL provides object classes used to build up circuit structure.

Joint Electronic Device Engineering Council (JEDEC): A council which creates, approves, arbitrates, and oversees industry standards for electronic devices. In programmable logic, the term JEDEC refers to a textual file containing information used to program a device. The file format is a JEDEC approved standard and is commonly referred to as a JEDEC file.

<u>Joint Test Action Group (JTAG)</u>: (or "IEEE Standard 1149.1"). A standard specifying how to control and monitor the pins of compliant devices on a printed circuit board. JTAG is a standard interface used for in-system testing and debugging.

<u>Logic</u>: One of the three major classes of integrated circuits in most digital electronic systems. The other two major classes are microprocessors and memory. Logic is used for data manipulation and control functions that require higher speed than a microprocessor can provide.

<u>Logic Function</u>: A mathematical function that performs a digital operation on digital data and returns a digital value.

*Logic Gate*: The physical implementation of a logic function.

<u>Logic Synthesis</u>: A process in which a program is used to optimize the logic used to implement a design.

<u>Look-Up Table (LUT)</u>: An array or matrix of values that contains data that is searched. An alternative implementation of a CLB; the multiple inputs generate the complex outputs.

<u>Macrocell</u>: A macrocell on most modern CPLDs contains a sum-of-products combinatorial logic function and an optional flip-flop. The combinatorial logic function typically supports four to sixteen product terms with wide fan-in. Thus, a macrocell may have many inputs, but the logic function complexity is limited. On the other hand, most FPGA logic blocks have unlimited complexity, but the logic function only has four inputs.

<u>Mapping:</u> The process of taking the logic blocks and determining what logic gates and interconnections on the device should be used to implement those blocks.

<u>Netlist</u>: A list of names of symbols or parts and their connection points, which are logically connected in each net of a circuit. A file listing parameters extracted from a circuit schematic.

*Noise*: The miscellaneous rubbish that gets added to a signal on its journey through a circuit. Noise can be caused by capacitive or inductive coupling, or from externally generated interference.

<u>Non-volatile</u>: The ability of a memory element to keep its contents when power is removed from the device.

*Onboard*: Contained on the device or on the board.

<u>One Time Programmable</u>: This device can be programmed only once; its contents cannot be changed. While typically these devices are fuse or antifuse based, they can also be low-cost EPROM devices. In this case, typically used for production devices, an inexpensive package is used without a window.

<u>Partial Reprogrammability</u>: The ability to leave some internal logic in place and change another part of the FPGA logic.

<u>Pinout</u>: A diagram that indicates how wires are terminated to pins in a connector; a list that assigns device functions to specific pins.

<u>Place and Route</u>: Converts the results of the synthesis process to the format supported and takes the logic blocks and determines what logic gates and interconnections on the device should be used to implement those blocks.

<u>Programmable Logic</u>: A logic element whose function is not restricted to a particular function. It may be programmed at different points of the life cycle. At the earliest, it is programmed by the semiconductor vendor (standard cell, gate array), by the designer prior to assembly, or by the user, in circuit.

<u>Programmable Logic Controller (PLC)</u>: A control device, usually used in industrial control applications, that employs the hardware architecture of a computer and relay ladder diagram language. Inputs to PLC's can originate from many sources including sensors and the outputs of other logic devices. Also called "programmable controller."

<u>Reconfigurable Computing</u>: A methodology of using programmable logic devices in a system design such that the hardware-based logic can be changed to perform various tasks. Benefits include the use of fewer components, less power, and flexibility. Also allows networked equipment in the field to be upgraded or repaired remotely.

<u>Reprogrammable</u>: These devices can have their configuration loaded more than once. SRAM-based devices may be reloaded without restriction. Many other forms of reprogrammable elements have restrictions on the number of write cycles, although they are high enough not to be of practical concern for most applications.

*Rising-Edge*: A transition from a logic 0 to a logic 1. Also known as a positive edge.

<u>Register Transfer Level (RTL)</u>: A description of a digital electronic circuit in terms of data flow between registers which store information between clock cycles in a digital circuit. RTL description specifies what and where this information is stored and how it is passed through the circuit during its operation. Also called Register Transfer Logic.

<u>Sensor</u>: A transducer that detects a physical quantity and converts it into a form suitable for processing. For example, a microphone is a sensor which detects sound and converts it into a corresponding voltage or current.

<u>Standard Cell</u>: This device differs from the gate array since each cell may be different and optimized for each standard function. There are no standard layers to the device and each layer of the chip is a unique design.

<u>State Machine</u>: The actual implementation (in hardware or software) of a function that can be considered to consist of a set of states through which it sequences.

<u>Static Random Access Memory (SRAM</u>): A type of memory that is faster and more reliable than the more common DRAM (dynamic RAM). The term static is derived from the fact that it doesn't need to be refreshed like dynamic RAM, but it loses its memory if it is powered off.

<u>Switch</u>: A device for making or breaking an electric circuit or for selecting between multiple circuits.

#### Synchronous:

- (1) A signal whose data is not acknowledged or acted upon until the next active edge of a clock signal.

- (2) A system whose operation is synchronized by a clock signal.

<u>System-on-chip (SoC):</u> A complete product that contains all the necessary electronic circuits and parts for a system on a single integrated circuit. Also called "system-on-a-chip" or SoaC

<u>Trace</u>: A line or wire of conductive material – such as copper, silver, or gold – on the surface of, or sandwiched inside, printed circuit board (PCB). An individual trace is often called a run. Traces carry an electronic signal or other forms of electron flow from one point to another.

<u>Translation:</u> Converting the results of the synthesis process to the format supported internally by the chip vendor's place-and-route tools.

<u>Truth Table</u>: A convenient way to represent the operation of a digital circuit as columns of input values and their corresponding output responses.

<u>Verilog</u>: A Hardware Description Language for electronic design and gate-level simulation.

<u>Very High Speed Integrated Circuit (VHSIC) Hardware Description Language (VHDL)</u>: A Hardware Description Language for electronic design and gate-level simulation.

<u>Via</u>: Feed-through. A plated through-hole in a printed circuit board used to route a trace vertically in the board, that is, from one layer to another.

<u>Volatile</u>: A memory element that loses its contents when power is removed from the device. SRAM-based devices are volatile and require another device to store their configuration program.

#### 3.2 ACRONYMS

A/D Analog to Digital

ABEL Advanced Boolean Equation Language

ADC Analog to Digital Converter

ASIC Application Specific Integrated Circuit

BIOS Basic Input/Output System

CE Complex Electronics

CEH Complex Electronic Hardware

CLB Configurable/Complex Logic Block

CM Configuration Management

CMM Capability Maturity Model

CPLD Complex Programmable Logic Device

CUPL Cornell University Programming Language

D/A Digital to Analog

DSP Digital Signal Processor

#### NASA-HDBK 8739.23 with change 1

EELV Evolved Expendable Launch Vehicle

EEPLD Electrically Erasable Programmable Logic Device

EEPROM Electrically Erasable Programmable Read-Only Memory

EHW Evolvable Hardware

EPLD Erasable Programmable Logic Device

EPROM Erasable Programmable Read-Only Memory

FAA Federal Aviation Administration

FIFO First In First Out

FPGA Field Programmable Gate Array

GAL Generic Array Logic

GOES Geostationary Operational Environmental Satellite

GPS Global Positioning System

HDL Hardware Description Language

HESSI High Energy Solar Spectroscopic Imager

I/O Input/Output

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

IP Intellectual Property

ISS International Space Station

IT Information Technology

JEDEC Joint Electronic Device Engineering Council

JHDL Java Hardware Description Language

JTAG Joint Test Action Group

LUT Look-Up Table

MAPLD Military-Aerospace Programmable Logic Devices (a yearly conference)

NRE Non-Recurring Engineering

PAL Programmable Array Logic

PCB Printed Circuit Board

#### NASA-HDBK 8739.23 with change 1

PDA Personal Digital Assistant

PL Programmable Logic

PLA Programmable Logic Array

PLC Programmable Logic Controller

PLD Programmable Logic Device

PROM Programmable Read-Only Memory

QA Quality Assurance

RAM Random Access Memory

RC Reconfigurable Computing

RTL Register Transfer Level

SA Software Assurance

SBIRS-High (-Low) Space Based Infrared System

SEI Software Engineering Institute

SIRTF Space Infrared Telescope Facility, renamed Spitzer Space Telescope

SoaC System-on-a-Chip

SoC System-on-Chip

SOHO Solar and Heliospheric Observatory

SRAM Static Random Access Memory

TDRS Tracking and Data Relay Satellite

VHDL Very High Speed Integrated Circuit Hardware Description Language

VHSIC Very High Speed Integrated Circuit

#### CHAPTER 4. COMPLEX ELECTRONICS OVERVIEW

"Complex electronics" is a term applied to various forms of programmable or designable hardware devices. The two elements of the term - complex and electronics - can be used to help distinguish what devices are, or are not, of interest.

#### 4.1 BLURRING THE HARDWARE/SOFTWARE LINE

Programmable Logic devices are now blurring the hardware/software boundary. These devices can now be programmed to perform tasks that were previously handled in software, such as communication protocols. With increased complexity, the possibility of "software-like" bugs (incorrect logic) or unexpected interactions is more likely. It is vital to be able to assure that the systems are designed and implemented correctly, tested fully, and are reliable.

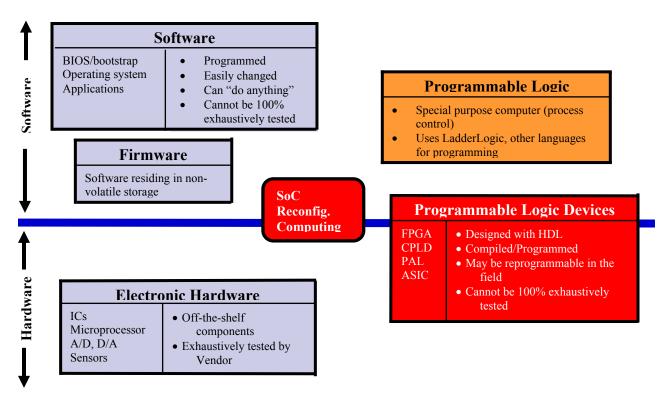

Figure 1 below shows the relationship of software, firmware, Programmable Logic Controllers (PLCs), electronics hardware, and complex electronics (the items in the red boxes). Boxes above the boundary line are software and those below the line are hardware. Complex electronics straddles the line.

Figure 1: How Complex Electronics Compares

The Federal Aviation Administration (FAA) has become concerned about the usage of complex electronic hardware in aviation. A study in 1995 stated, "There are no techniques and methods of design, documentation, testing, and verification identified or recognized by the Federal

Aviation Administration (FAA) for today's complex hardware designs." Since that time, the FAA has worked with other organizations to develop DO-254, "Design Assurance Guidance for Airborne Electronic Hardware," which provides guidelines on the use of process assurance for complex electronic hardware.

The pace of technological change and the new uses that people find for current technology are strong motivators for NASA to begin to define acceptable assurance practices for complex electronics. An example of an assurance challenge is adaptive or reconfigurable computing, in which computers, chips, or systems alter their functionality to adapt to changing applications and situations. Adaptive computing is usually implemented with FPGAs and allows for parallel processing. Adaptive computing is expected to be the next breakthrough in computing. Many applications of the technique for the military are being proposed, and adaptive computing is likely to be used in space systems.

## 4.1.1 How does Programmable Logic differ from Firmware?

Firmware has various definitions, but the most common is found in IEEE 610.12-1990: "The combination of hardware device and computer instructions and data that reside as read-only software on that device."

Complex electronics, such as FPGAs and ASICs, are not firmware because what resides in them is not a software program. Instead, software is used to define the logic structure for a hardware device, which is what these devices become once they are programmed. These devices are better thought of as hybrid hardware/software devices, or "soft hardware."

# Some types of complex electronics are even harder to define, such as System-on-Chip (SoC) and FPGAs:

SoC is a complete product that contains all the necessary electronic circuits and parts for a system on a single integrated circuit. SoCs may include embedded software (i.e., firmware) as part of the device. SoC devices combine a microprocessor, input and output channels, and often an FPGA for programmability.

FPGAs are "soft hardware," except when they are used in reconfigurable or adaptable computing. In that case, they are part of a complex system that is reprogrammed on the fly. The FPGAs replace a microprocessor, and the act of reprogramming them (and the logic that determines the activities) is the software of the system. FPGAs can have from 30,000 to over one million logic gates.

#### 4.1.2 Comparing Complex Electronics and Software

Complex electronics devices do not work in the same way as software. The main difference is that software is serial (one activity is performed after another) and hardware is parallel (multiple operations occur at the same time). It is very important to always remember that the ultimate result of a programmable logic device is hardware. Hardware programming languages, such as VHDL, can be thought of as a virtual or abstract piece of hardware.

However, similarities exist between programming languages for complex electronics (e.g., Verilog or VHDL) and software languages. VHDL, for example, is based on Ada syntax, has

data types common to most higher-level languages, uses objects (e.g., constants and variables), and has sequential statements.

A software assurance engineer reviewing programmable logic "code" should not be lulled by the similarities to regular programming languages. Complex electronics and programmable logic devices are ultimately hardware, and those differences must be acknowledged.

#### 4.2 PROGRAMMABLE VERSUS DESIGNABLE DEVICES

Programmable Logic Devices (PLDs) are hardware integrated circuits that are programmable by the user. They contain configurable logic and flip-flops, which are linked together with programmable interconnects. Memory cells control and define the function that the logic performs and how the various logic functions are interconnected. PLDs can be divided into various categories and range from simple devices to complex devices capable of being programmed on-the-fly. Devices in this category include:

- Programmable Array Logic (PAL)

- Generic Array Logic (GAL)

- Programmable Logic Array (PLA)

- Complex Programmable Logic Device (CPLD)

- Field Programmable Gate Array (FPGA)

Some integrated circuits can be designed by the user and submitted to a manufacturer for creation of multiple copies. This allows specialty circuits to be designed for a device, such as a cell phone. Once created, the devices cannot be reprogrammed by the user. ASICs and System-on-Chip (SoC) are examples of designable devices.

#### **4.2.1** How to Identify Complex Electronics?

The electronics part of this term is fairly easy to identify. Electronics refers to the flow of charge (moving electrons) through nonmetal conductors (mainly semiconductors), as opposed to electrical, which refers to the flow of charge through metal conductors. So all the devices listed above qualify. So do off-the-shelf integrated circuits (ICs), microprocessors, logic gates, analog-to-digital converters, buffers and other components.

The "complex" adjective is used to distinguish between simple devices, such as off-the-shelf ICs and logic gates, and user-creatable devices. More information on distinguishing between simple and complex is presented later in this handbook. For now, a good rule of thumb is, if you can program or design the internal logic of the device and it has more than a few gates and connections, it is probably complex.

Does firmware fall under this category? Firmware has various definitions, but the most common is found in IEEE 610.12-1990: "The combination of hardware device and computer instructions and data that reside as read-only software on that device." In other words, it is software that is placed in a read-only device, such as an EPROM or Flash, from which the software may be read or copied. The EPROM acts solely as a storage device, much like a disk. The software may be complex and reside on electronic components, but it does not affect the internal logic or

configuration of the chips. Firmware is not considered complex electronics. Table 1 gives some examples:

**Table 1:** Complex Electronics Examples

| ltem                                                               | User Interactions                                                               | Complex Electronics?    | Why or Why Not?                                                                                                       |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Complex Programmable Logic Device                                  | Define and program the internal logic elements                                  | Yes                     | Electronic and complex                                                                                                |

| FIFO                                                               | Use it                                                                          | No                      | Electronic, but not complex                                                                                           |

| Microprocessor                                                     | Execute software instructions on it to perform arithmetic and other operations. | No                      | The software executes predefined commands. It does not change the internal logic arrangement of the microprocessor.   |

| Software                                                           | Design, develop, execute                                                        | No                      | Definitely complex, but not electronic                                                                                |

| Application Specific Integrated Circuit (ASIC)                     | Design, use resulting chip                                                      | Yes (above a threshold) | Most ASICs are complex. It is possible to make a simple ASIC, though such devices are likely to be already available. |

| EEPROM (Electrically<br>Erasable Programmable<br>Read-Only Memory) | Program the device with data or software                                        | No                      | The device itself is not complex. The software or data does not change the internal logic of the device.              |

#### 4.2.2 A Bit of History

The story starts with the development of discrete logic. Each logic chip had a purpose (e.g., AND gate, OR gate, flip-flop) and could be wired together with other chips to make the desired circuit. Pinouts on the chip were fixed. Manufacturing such a system took a lot of time because each design change required that the wiring be redone. This usually meant building a new printed circuit board.

The chip makers solved the problem of time-consuming rewiring for design changes by placing an unconnected array of AND-OR gates in a single chip called a programmable logic device (PLD). The PLD contained an array of fuses that could be blown open or left closed to connect various inputs to each AND or OR gate. You could program a PLD to perform the logic functions you needed in your system. Since the PLDs could be rewired internally, there was less of a need to change the printed circuit boards which held them.

#### 4.3 SIMPLE PROGRAMMABLE LOGIC DEVICES

There are a variety of simple PLDs. They are called simple to distinguish them from the Complex PLDs (CPLDs, discussed below), and because they are actually pretty simple devices, as modern integrated circuits go.

#### 4.3.1 Programmable Array Logic

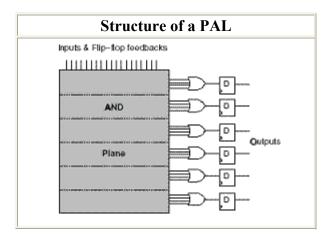

Programmable Array Logic (PAL) chips are a family of fuse-programmable integrated circuits originally developed by MMI (Monolithic Memories, Inc.). The word "Logic" in the name signifies that the chips allow the user to program a set of AND and OR gates (or NAND/NOR) to create the desired logic sequence. PALs consist of a programmable AND array followed by a non-programmable OR array. Inputs are fed into the AND array, which performs the desired AND functions and generates product terms, which are then fed into the OR array. In the OR array, the outputs of the various product terms are combined to produce the desired outputs.

Using a fixed number of OR gates, rather than a completely programmable set, allows the device to be fast. The high speed available in PALs makes them still popular today, despite the abundance of newer chips. Figure 2 shows the structure of the PAL.

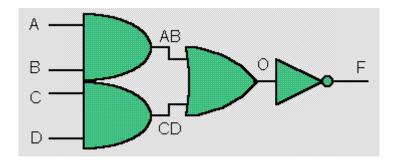

Figure 2: Example of PAL Structure

Fuse-programmable has to do with how PALs are programmed. Connections between the gates in a PAL are made using fuses that are either connected or disconnected (blown). Overvoltage (above the operational limits of the chip) is used to blow the fuses for the connections that are not desired. This operation is permanent, so once programmed, a PAL cannot be reprogrammed.

Fuse maps, which determine what fuses are, or are not, blown for a particular PAL can be generated in several ways. Languages such as PALASM or CUPL can be used, with the resulting logic design compiled into JEDEC (Joint Electronic Device Engineering Council) ASCII/hexadecimal files. Modern support software for PALs allows a direct translation from a schematic, truth table, or state table to the fuse map. Some software even accepts timing diagrams as input. Hardware description languages (HDL) can also be used to synthesize the fuse map. However the map is created, it must be provided as input to a special electronic

programming device, available from either the manufacturer or a third-party, for physical programming of the chip.

## 4.3.2 Generic Array Logic

Generic Array Logic (GAL) was introduced by Lattice Semiconductor. A GAL consists of a reprogrammable AND array, a fixed OR array, and reprogrammable output logic. Electrically Erasable Programmable Read-Only Memory (EEPROM) is used, rather than fuses, to provide the connections. This allows the GAL to be erased and reprogrammed.

The GAL is very useful in the prototyping stage of a design, when any bugs in the logic can be corrected by reprogramming. GALs are programmed and reprogrammed using a PAL programmer, and the same types of languages or processes used for PAL chips. If speed is important (and it usually is), a PAL can be used, once the design is finalized.

## 4.3.3 Programmable Logic Array

Programmable Logic Array (PLA) devices differ from PALs in the OR-gates area. PALs could only be programmed in the AND-plane. With PLA chips, a set of programmable AND planes are linked to a set of programmable OR planes, which can then be conditionally complemented to produce an output. PLA devices allow far more design options than PALs, but the downside is reduced performance.

Like PALs, PLA devices are fuse-based and can be programmed only once. Tools and languages are readily available to translate a logic design into the fuse map required for PLA programming. Table 2 gives a comparison of the simple programmable devices

|                                                       | PROM         | PAL          | GAL          | PLA          |  |

|-------------------------------------------------------|--------------|--------------|--------------|--------------|--|

| Input lines                                           | hard-wired   | programmable | programmable | programmable |  |

| Output lines                                          | programmable | hard-wired   | programmable | programmable |  |

| Versatility                                           | low          | moderate     | moderate     | high         |  |

| Difficulty in manufacturing, programming, and testing | low          | moderate     | low          | high         |  |

| Reprogrammable?                                       | No           | No           | Yes          | No           |  |

**Table 2:** Simple PLD Comparisons

# 4.4 COMPLEX PROGRAMMABLE LOGIC DEVICES (CPLD)

Simple PLDs can only handle up to 10 to 20 logic equations, which is not a very large logic design. Designers need to figure out how to break a larger design apart and fit the pieces into a set of PLDs. This is a time-consuming process, and means you have to interconnect the PLDs with wires. When there were only discrete logic chips, the use of wires meant that any design change will likely require a new circuit board, not just reprogramming the PLDs. To counteract

this constraint, the chip makers began by building much larger programmable chips, including CPLDs and FPGAs.

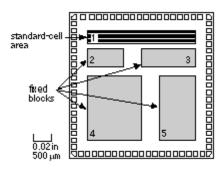

A CPLD contains a set of PLD blocks whose inputs and outputs are connected together by a global interconnection matrix. So a CPLD has two levels of programmability: each PLD block can be programmed, and then the interconnections between the PLDs can be programmed. A key feature of the CPLD architecture is the arrangement of logic cells on the periphery of a central shared routing resource. CPLDs use EEPROM, SRAM, or Flash memory to hold the interconnect information.

CPLDs contain the equivalent of many PALs linked by programmable interconnections, all in one integrated circuit. CPLDs are equivalent to about 50 typical PLD devices and can replace thousands, or even hundreds of thousands, of logic gates.

Programming CPLDs depends on the chip and the application. Some CPLDs can be programmed in a PAL programmer, but that gets difficult if the chip has hundreds of pins, or is surface-mounted. Many CPLDs can be programmed over a serial line from a computer. The CPLD contains a circuit that decodes the data stream and configures the CPLD to perform its specified logic function.

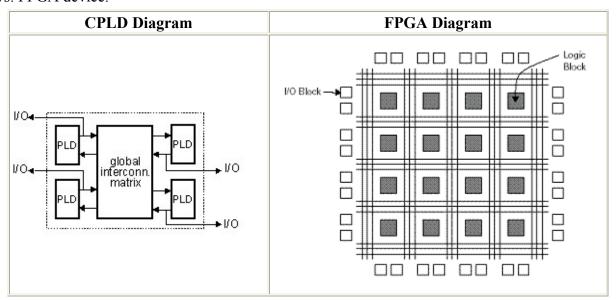

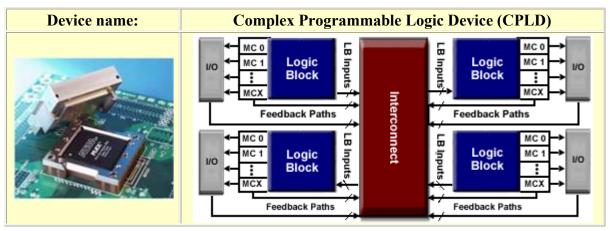

A new interface for programming and testing CPLDs is Joint Test Action Group (JTAG). This interface is defined by the IEEE Standard 1149.1-1990, Test Access Port and Boundary Scan Architecture. Boundary scan is a technique for accessing and stimulating a chip or subsystem via external pins to perform internal test functions on the device. A JTAG interface is primarily used for testing integrated circuits, but it can also be used as a mechanism for debugging embedded systems. A JTAG interface is a special four-pin (data in, data out, clock, test mode select) interface added to a chip. Multiple chips on a board can have their JTAG lines daisy-chained together, so the test probe only needs to connect to a single JTAG port to have access to all chips on a circuit board. Figure 3 shows the difference between the internal layout of a CPLD vs. FPGA device.

Figure 3: CPLD vs. FPGA Layout

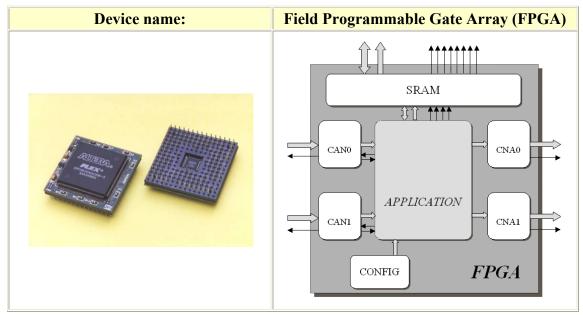

#### 4.5 FIELD PROGRAMMABLE GATE ARRAY (FPGA)

While PALs were busy developing into GALs and CPLDs, a separate stream of development was occurring, based on gate-array technology. The resulting device is the FPGA which was first introduced in the late 1970s. "Field programmable" simply means that the device can be programmed by the user. Many field programmable devices can be programmed with the chip soldered to the circuit board, allowing true in-the-field upgrades to be possible.

FPGAs use a grid of logic gates, similar to that of an ordinary gate array. An FPGA has a collection of simple, configurable logic blocks arranged in an array with interspersed switches that can rearrange the interconnections between the logic blocks. Each logic block is individually programmed to perform a logic function (such as AND, OR, XOR, etc.) and then the switches are programmed to connect the blocks so that the complete logic functions are implemented. FPGAs vary in size from tens of thousands of logic gates to over one million.

The interconnections for the logic blocks are programmable switches. FPGAs may use EEPROM, SRAM, antifuse, or Flash technology to store the programming. In most larger FPGAs the configuration is volatile, and must be re-loaded into the device whenever power is applied or different functionality is required.

FPGAs are typically programmed in hardware description languages (HDLs) like Verilog or VHDL. These high-level languages are used because manual lower level design (such as schematic capture) becomes impractical as designs become large. HDLs also allow the FPGA design to be simulated and tested prior to implementation in the hardware.

## 4.6 APPLICATION SPECIFIC INTEGRATED CIRCUIT (ASIC)

ASICs are integrated circuits (ICs) designed for specific applications. Unlike standard ICs which are produced by the chip manufacturers, ASICs are designed by the end user and then produced in volume. ASICs allow a user to combine many parts and functions into a single chip, reducing cost and improving reliability.

ASICs can be large or small. They are usually produced in large quantities, and it can be very expensive to produce only a few. If you are manufacturing cell phones, it makes sense to develop an ASIC for your specific needs. If you are flying a space experiment and will need at most a few chips, it would be much more economical to use programmable logic, such as FPGA or CPLD devices.

An interesting twist is the production of ASICs that include programmable logic (FPGA, CPLD or PAL) devices as part of the chip. Another new technology that combines ASICs with programmable parts is the System-on-Chip, described below.

## 4.7 SYSTEM-ON-CHIP (SOC)

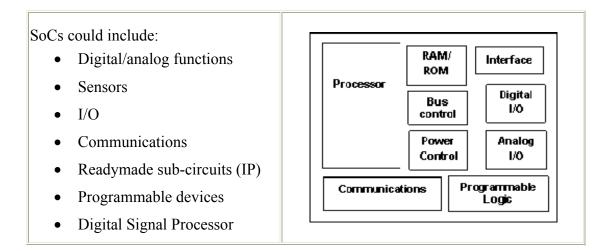

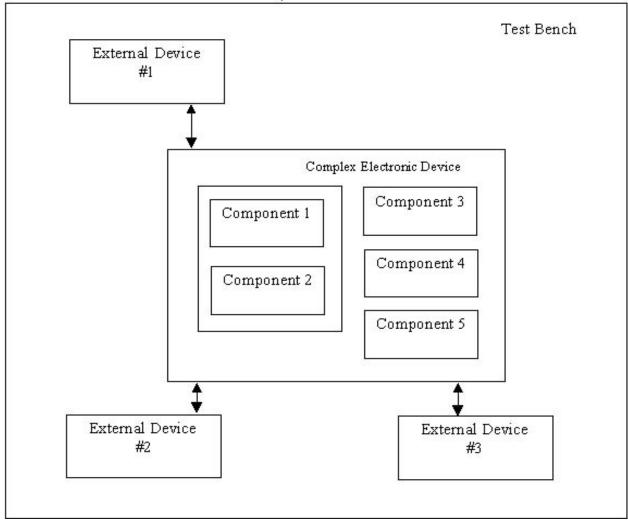

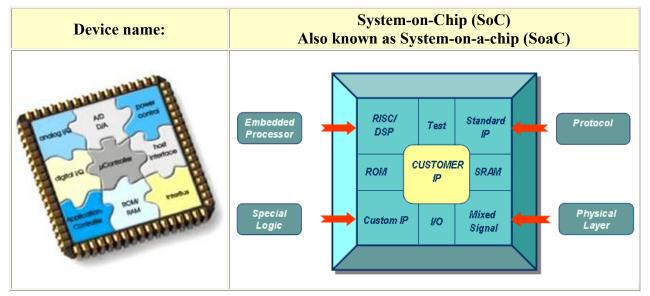

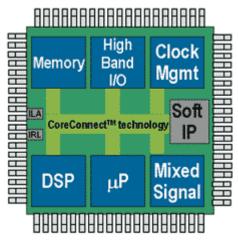

System-on-Chip combines all the electronics for a complete product into a single chip. SoCs include not only the brains (e.g., microprocessor) but also all required ancillary electronics, such as switches, comparators, resistors, capacitors, timing elements, and digital logic. Figure 4 gives a sample configuration for a SoC.

Figure 4: SoC Example Configuration

SoCs are usually ASICs, though they can be designed to include programmable logic components. SoCs can also be implemented on FPGAs. System-on-chip versions have a variety of features:

- Soft Instruction processor architectures allow a designer to customize the CPU architecture. The specific instructions supported, the peripherals available to it, and the number of registers are just some ways these devices can be tailored for your application. Some vendors provide mechanisms to add, delete, and create highly tailored instructions. Design packages for these architectures sometimes include performance tools with instant feedback on the performance, die size, and power requirements of a particular design. With the final architecture residing in silicon, these types of architectures are well suited for high volume, low cost applications which formerly would have used ASICs.

- Configurable processors are FPGA based. In these architectures, standard and customerderived logic engines can be easily added, modified, and extended as needed. By moving discrete logic functionality to internal FPGA, the designer gets a highly flexible logic solver based around a standard processor core. With FPGA logic instead of foundry logic, the logic can be easily revised at any point in the design cycle.

#### 4.8 CONCERNS AND ISSUES

# **4.8.1** Verification Issues with Complex Electronics

Verification means that you have demonstrated that the system or subsystem meets the requirements you have specified. Complex systems, especially those including software, are hard to adequately verify. Complex electronics adds additional verification concerns to the mix:

- Tool-induced design errors occur and can be difficult to detect. Tools are a vital part of complex electronics design, and the designer often does not know what errors a tool could potentially produce.

- Complex functionality cannot be completely simulated, nor the resulting chip completely tested.

- It can be difficult to detect faulty operation of complex electronics due to design or tool-induced errors, unexpected interactions, or even defects in the silicon.

- Due to extremely small ASIC geometries, certain analog and transmission line phenomena occur internal to the ASIC, generating failures that are data-sensitive.

Designers and tools may not account for these effects, which can easily escape notice during test.

## 4.8.2 Assurance Issues with Complex Electronics

In addition to challenges with testing and verifying the designs and implementations of complex electronics, quality assurance professionals are struggling with how to adequately deal with the "software-like" aspects of these devices. Some problems and concerns are:

- ASICs and FPGAs have been used to avoid the rigors of the software approval process. This results in fundamental verification matters being bypassed.

- Complex electronic devices are designed and programmed by engineers, often without quality assurance oversight or configuration management control of the designs. In addition, the development process may not be well defined or followed.

- ASICs, FPGAs, and System-on-Chip (SoC) can contain embedded microprocessor cores with user-supplied software. They combine electronics and firmware into one chip. The presence of this firmware (i.e., software) is not always obvious to assurance personnel.

- High-level languages (e.g., C, C++) are now being used to define complex electronic designs (in whole or in part).

- Hardware quality assurance professionals may not be fully cognizant of the functions, potential problems, and issues with these devices.

- Software assurance personnel are currently not trained to understand complex electronics, and may not be able to provide effective oversight and assurance.

- Meaningful verification efforts require the person performing the verification to be knowledgeable about the complex electronic device and the tool suite used to create and implement the design.

#### 4.9 SUMMARY

Programmable and designable electronics have grown over the years, both in number of devices and in the complexity of the devices. The devices can be roughly grouped by function and complexity.

- Simple, non-programmable logic ICs

- Simple, programmable logic PAL, GAL, PLA

- Complex, programmable logic CPLD, FPGA, reconfigurable computing

- Complex, designable logic ASIC

- Complex, designable, and/or programmable logic SoC

To explore the complex devices in more depth, refer to the descriptions in Appendix A.

#### CHAPTER 5. DESIGN PROCESS

#### 5.1 OVERVIEW OF THE COMPLEX ELECTRONICS DESIGN PROCESS

Creating complex electronics begins where all systems and subsystems begin - with defining the requirements for the device. Without good requirements, the most elegant design or implementation could fail to meet the original need. Designing and implementing complex electronics occurs within the context of the larger system, as shown in Figure 5 below.

Requirements for the complex electronics are driven by the system they are a part of and the environment where they will be used. A simple home appliance will place fewer demands (requirements) on a device than a sophisticated satellite application will. Because these devices are hardware, the process of complex electronics design involves looking at both the chip capabilities and constraints (e.g., how many gates does it have, how much power does it need) and how the design works with and against those constraints and capabilities.

#### **5.1.1** Design Life Cycle

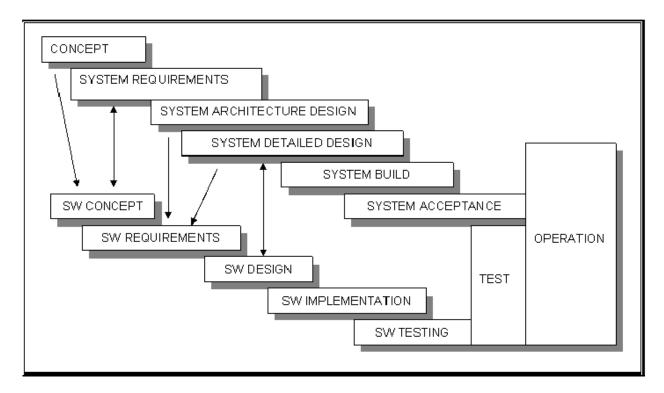

In typical software design, the software requirements are flowed down from the system requirements. Software development may follow a waterfall, iterative, evolutionary, spiral, or other development methodology. Regardless of the development (design) life cycle, the processes of determining the requirements, creating the design, implementing the design, and verifying the implementation are all included. Since it is easy to show graphically, this handbook will use the waterfall life cycle as a generic life cycle. Figure 5 below compares the complex electronics lifecycle to software.

Figure 5: CE vs. SW Life Cycles

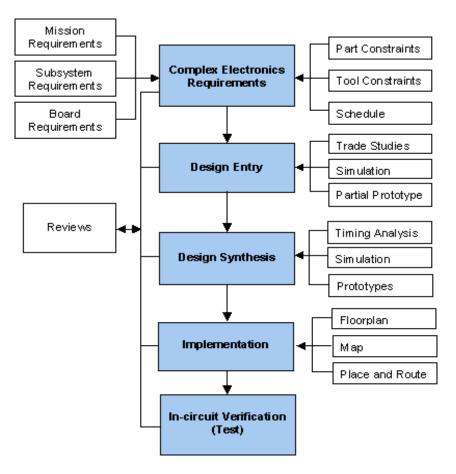

Like software, the design and development life cycle for complex electronics can follow any life cycle methodology. Some of the steps vary from those familiar to software developers. Figure 6 depicts the design process for complex electronics.

Figure 6: Example CE Waterfall Development

The basic design flow starts out very similar to software, with the decomposition of system or subsystem requirements to the particular complex electronic device. After that is completed, the engineers take the requirements and generate a design, often in a hardware description language (design entry). The design has to be "compiled" for the device (design synthesis). Synthesis is more complicated than just running a compiler. During synthesis, the design is mapped to the logic gates of the device. Simulations are used to verify that the design is correct and can meet the requirements and performance goals.

The implementation of complex electronics involves one more level in the mapping of the logic (design) to the chip. The placement of the logic blocks within the chip, and the routing between blocks, are some of the processes that occur during implementation. This process is loosely comparable to the linking step in software, where the compiled program is fixed up for the software environment in which it will operate. At the end of the implementation phase, the final step is to "burn" or program the device.

While the simulation that occurs before the design is committed to hardware can find most defects, the actual hardware device needs to be tested in the circuit. Real signals are applied, and the real output is tested. You usually cannot get the degree of testing with in-circuit verification that you can with simulation, because inputting out-of-range signals might be difficult, access to the hardware pins might not be possible, and, in real projects, someone always wants to use the hardware as soon as it is completed. However, functional testing in a variety of conditions is an important verification step. Errors in the silicon chip are possible. Errors induced by the tools are more likely. Sometimes the real world acts differently than expected and can influence how the device works.

During this process, the tasks of the assurance engineers (quality/hardware) can vary between projects with some only taking a look at the system at a high level, and then verifying that the final device matches the design and that it was programmed according to a defined process. NASA is looking at how to adequately verify the complex electronics device. More information is provided in Section 6.2. Table 3 gives a comparison of the development process for software and complex electronics.

**Table 3:** CE vs. SW Development Phases

|              | Software                                                                                                                                                        | Complex Electronics |                                                                                                                                                                                                                                                                   |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Requirements | Software requirements flow down from system and subsystem requirements.                                                                                         | Requirements        | Requirements for complex electronics flow down from system and subsystem requirements.                                                                                                                                                                            |  |

|              | Architectural and detailed                                                                                                                                      | Design Entry        | The design is created primarily in a hardware description language, such as Verilog or VHDL.                                                                                                                                                                      |  |

| Design       | designs are created, using UML, flow diagrams, and other tools.                                                                                                 | Synthesis           | Synthesis is the process that takes the higher level designs and optimally translates them to a gate-level design which can be mapped to the logic blocks in a complex electronic device.                                                                         |  |

| Code         | The design is translated (manually or automatically) into a programming language (code), and then compiled into an executable module.                           | Implementation      | Implementation is where the design meets the silicon - the mapping created by synthesis is converted into a chip layout. The final step in implementation is to put the design into the chip - either through programming (burning) or manufacturing (for ASICs). |  |

| Test         | The software is tested in individual units and as part of the system. Testing may involve additional software that simulates inputs to the software under test. | Test                | Testing occurs during the design entry, synthesis, and implementation phases, in the form of simulations. Both expected (valid) and unexpected inputs are tested. Once the device is created, it is tested as part of its subsystem (in-circuit testing).         |  |

## 5.2 REQUIREMENTS AND SPECIFICATIONS

The first step in the design process is to understand (and document) the functions the complex electronics device must perform and the constraints under which it operates. The act of documenting the requirements has some useful effects that actually can save you time in the long run. Benefits include:

- The design team thinks through the issues and reaches agreement. Some issues are well understood at a high level, but raise additional questions when working at the hardware level.

- Interfaces to other areas (software, other hardware) are defined and available for review by all affected parties.

- Non-engineers can understand what the chip or device is supposed to do.

- If the trade-offs and rationales are documented, as well as the requirements, future design changes will require less impact assessment.

- The requirements can be reviewed to assure that they provide measurable, testable criteria.

- Requirements traceability into the design and implementation can be performed which is vital in mission- or safety-critical applications.

A good specification for complex electronics will contain:

- A description of how the device fits into the larger system. A block diagram is very helpful.

- A description and list of all the major functions the device will perform. A block and/or flow diagram can be used to show this information.

- A description of the device and interfaces, such as:

- ° Chip physical information (size, type, number of pins, etc.)

- ° I/O pin mapping and description (output drive capability, input threshold level)

- Timing estimates for:

- ° Setup and hold times for input pins

- ° Propagation times for output pins

- Clock cycle time

- High-level estimates and goals

- ° Gate count estimate

- Power consumption target

- Constraints on the device

- Other requirements or criteria the device must implement

- Design-related choices (may be in a management plan)

- ° Tools that will be used at all stages of development

- Hardware Description Language chosen

#### **5.2.1** Assurance Roles