Spacecraft Design and Fabrication Requirements for

# **Electronic Packaging and Cabling**

\* Printed copies of this document may not be current and should not be relied on for official purposes. The current version is in the DMIE Information System at http://dmie

#### This document contains:

|      | Table of Contents                          |

|------|--------------------------------------------|

| 1    | Foreword                                   |

| 2    | Applicable Documents                       |

| 3.1  | Definitions, Terms, and Acronyms           |

| 3.2  | General Requirements                       |

| 3.3  | Mechanical Requirements                    |

| 3.4  | Thermal Requirements                       |

| 3.5  | Surface Mount Technology                   |

| 3.6  | Printed Wiring Boards                      |

| 3.7  | Flexible and Rigid-Flexible Printed Wiring |

| 3.8  | Wire Wrap                                  |

| 3.9  | High-Voltage Requirements                  |

| 3.10 | Radio Frequency                            |

| 3.11 | Hybrid Microelectronics and MCMs           |

| 3.12 | Cabling and Wiring                         |

| 3.13 | Magnetic Packaging Requirements            |

| 3.14 | Component Mounting/Soldering               |

| 3.15 | Rework, Modification, and Repair           |

| 3.16 | Cleaning                                   |

| 3.17 | Polymeric Applications                     |

| 3.18 | Shipping and Handling                      |

Index

January 14, 2002

# **Change Incorporation Log**

| Change<br>Letter | Rele     | ease    | Authority                                           | Pages Affected                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Date     | _        | eering<br>roval |

|------------------|----------|---------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-----------------|

| Letter           | Initials | Section |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | Initials | Section         |

| Α                | JWA      | 648     |                                                     | Init. Rel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10/1/91  | DLW      | 358             |

| В                | JWA      | 644     |                                                     | All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8/1/94   | CJB      | 349             |

| С                | GSR      | 644     | Process<br>Identifica-<br>tion<br>#P03.05.09.<br>00 | All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3/15/97  | CJB      | 349             |

| D                | CD       | 349     |                                                     | All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8/15/98  | CJP      | 349             |

| Е                | CD       | 349     | ISO                                                 | Added ISO requirements to Section 3.2, Section 3.12 needed additional crimp tool tables.                                                                                                                                                                                                                                                                                                                                                                                                 | 3/26/99  | CJB      | 349             |

| F                | CD       | 349     | ISO                                                 | Added new section 3.10, Radio Frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7/26/99  | CJB      | 349             |

| G                | CJB      | 349     | ISO                                                 | Removed Table 3.3-4; rewrote Sections 3.6 and 3.7; corrections to paragraphs 2.1 and 4.2 and equations 7.2.4 and 7.2.6.3 in Section 3.10; corrections to Figure 3.12-1 and Table 3.12-10; and corrected Applicable Documents section as necessary                                                                                                                                                                                                                                        | 9/25/00  | CJB      | 349             |

| Н                | CJB      | 349     | ISO                                                 | Changes to Section 3.6: Added paragraphs 4.8.2.3 and 5.3.8.4; deleted paragraph 4.8.10.2; and made corrections to drawings in Figures 3.6-2 and 3.6-9. Changes to Section 3.7: Replaced paragraphs 1.3 and 3.1.1.3 with corresponding paragraphs from Section 3.6; added paragraphs 4.8.2.3 and 5.3.8.4; deleted paragraph 4.8.9.2; and made corrections to drawing in Figure 3.7-2 Changes to Section 3.12: Added Table 3.12-13, paragraph 2.5.13.4 and paragraphs 2.5.11 thru 2.5.11.4 | 10/26/00 | CJB      | 349             |

| Change<br>Letter | Rele     | ease    | Authority | Pages Affected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Date   | Engineering Date Approval |         |

|------------------|----------|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------|---------|

| Letter           | Initials | Section |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | Initials                  | Section |

|                  | CJB      | 349     | ISO       | Changes to Section 2: Modified paragraph 2.7; made additions to paragraph 4. Changes to Section 3.2: Added paragraph 1.13.6; modified paragraph 1.13.8.1 (1.13.7.1 in Rev. H). Changes to Section 3.5: Modified paragraph 1; altered paragraph 1.1; modified paragraphs 2 and 2.1 and changed paragraph numbering as a consequence; corrected paragraph 2.1.3.5 (2.2.3.5 in Rev. H). Extensive changes made to Section 3.6: much of it has been rewritten. Several new tables were added-Tables 3.6-1, 3.6-9, 3.6-10; Tables 3.6-2, 3.6-3, 3.6-5, and 3.6-7 were modified; paragraph 3.1.1.1 was totally rewritten with Table 3.6-1 added; paragraph 3.1.1.2 was largely rewritten; much of paragraphs 4.4.1, 4.4.1.1, 4.4.2, 4.4.2.1, 4.4.2.2, and 4.4.3 were rewritten. Added new Figures 3.6-4, 3.6-5, 3.6-8, and 3.6-9; paragraphs 4.8.13, 4.8.13.1, 4.8.13.2, 4.8.13.3, 4.8.13.1, 4.8.15.2, 4.8.15.3, and 6.1.4 have been added; paragraphs 4.9.1, 4.9.1.1, and 4.10 have been extensively revised. | 1/7/02 | JKB                       | 349     |

| Change<br>Letter | Rele     | ease    | Authority | Pages Affected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Date   | Engineering<br>Approval |         |

|------------------|----------|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------|---------|

| Letter           | Initials | Section |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | Initials                | Section |

|                  | CJB      | 349     | ISO       | Changes in Section 3.7: Extensive changes made to this section; much of it has been rewritten. New tables 3.7-1, 3.7-9, and 3.7-10 were added; tables 3.7-2, 3.7-3, 3.7-5, and 3.7-7 were modified; paragraph 3.1.1.1 was totally rewritten with table 3.7-1 added; paragraph 3.1.1.2 was largely rewritten; much of paragraphs 4.4.1, 4.4.1.1, 4.4.2, 4.4.2.1, 4.4.2.2, and 4.4.3 were rewritten. Added new Figures 3.7-4, 3.7-5, 3.7-8, and 3.76-9; paragraphs 4.8.13, 4.8.13.1, 4.8.13.2, 4.8.13.3, 4.8.13.4, 4.8.14, 4.8.15, 4.8.15.1, 4.8.15.2, 4.8.15.3, and 6.1.4 have been added; paragraphs 4.9.1, 4.9.1.1, and 4.10 have been extensively revised. Extensive changes were made to Section 3.12: Modified paragraph 1.5.4.7; modified paragraph 2.5.10.14; added paragraph 2.6; added Table 3.12-14; added paragraphs 3.3.5, 3.3.5.1, 3.3.5.2, 3.3.5.3, 3.4, 3.4.1, 3.4.2, 3.4.3, 6.1.1. Several other new paragraphs were added and minor modifications were made. Changes to Section 3.13: This entire section has been totally rewritten. Changes to Section 3.14: Modified paragraph 1: nodified paragraph 1.1: paragraph 1: nodified paragraph 1.1: paragraph 1: nodified paragraph 1: paragraph 1: 2.3.8 and 1.2.3.9 added; corrected paragraph 2.2.1.3 c. (2.2.2.1 c. in Rev. H); modified paragraph 2.2.1; modified paragraph 2.2.2; modified paragraph 3.1. Changes to Section 3.15: Modified paragraph 2.2.1; modified paragraph 2.2.2; modified paragraph 3.1. | 1/7/02 | JKB                     | 349     |

| Change | Change Release |         | Authority | Pages Affected                                                                                                                                                                                                                                                                                                                                            | Date   |          | eering<br>roval |

|--------|----------------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|-----------------|

| Letter | Initials Se    | Section | -         |                                                                                                                                                                                                                                                                                                                                                           |        | Initials | Section         |

| I      | CJB            | 349     | ISO       | Changes to Section 3.16: Modified Table 3.16-1; modified paragraph 4.5.1 and 4.5.1.1 (combined the contents of 4.5.1.1 into 4.5.1); several new paragraphs added such as 4.5.2; modified 4.5.3.1 (4.5.2.1 in Rev. H); modified some of the other paragraphs in 4.5; Table 3.16-3 changed considerably. Changes to Section 3.17: Modified paragraph 1.8.3. | 1/7/02 | JKB      | 349             |

## **Table of Contents**

|   | tion 1 reword                           |      |

|---|-----------------------------------------|------|

|   | Purpose                                 |      |

|   | Structure                               |      |

|   | tion 2<br>plicable Documents            |      |

| 1 | Jet Propulsion Laboratory               | 2-   |

|   | 1.1 Specifications                      |      |

|   | 1.2 Drawings                            | 2-   |

|   | 1.3 Standards                           |      |

|   | 1.4 Miscellaneous                       | 2-   |

| 2 | Commercial                              | 2-   |

|   | 2.1 AMS                                 | 2    |

|   | 2.2 ANSI                                | 2-:  |

|   | 2.3 ANSI/IEEE                           | 2    |

|   | 2.4 ANSI/IPC                            |      |

|   | 2.5 ASTM                                |      |

|   | 2.6 IEEE                                |      |

|   | 2.7 IPC                                 |      |

| _ | 2.8 Miscellaneous                       |      |

| 3 |                                         |      |

|   | 3.1 Specifications                      |      |

|   | 3.2 Standards                           |      |

|   | 3.3 Department of Defense               |      |

| _ | 3.4 Miscellaneous                       |      |

| 4 |                                         |      |

| 5 | Federal                                 | 2-14 |

|   | tion 3.0  cument Structure              |      |

|   | tion 3.1 finitions, Terms, and Acronyms |      |

| 1 | Terms                                   | 3.1- |

| - | 1.1 Exclusions                          |      |

|   | 1.2 Exceptions                          |      |

|   | 1.3 Additions                           |      |

|   |                                         | _    |

|    | 1.4   | Clarifications                                                                | 3.1-4 |

|----|-------|-------------------------------------------------------------------------------|-------|

| 2  | Acı   | ronyms                                                                        | 3.1-5 |

|    | ion 3 |                                                                               |       |

| Ge | nera  | al Requirements                                                               |       |

| 1  | Mi    | nimum Requirements                                                            | 3.2-1 |

|    | 1.1   | Conflicting Requirements                                                      | 3.2-1 |

|    | 1.2   | Redundant Requirements                                                        | 3.2-1 |

|    | 1.3   | Drawing Instructions                                                          | 3.2-1 |

|    |       | 1.3.1 Drawing Conformance.                                                    | 3.2-1 |

|    | 1.4   | Documentation                                                                 |       |

|    |       | 1.4.1 Deliverable Package.                                                    |       |

|    |       | 1.4.2 Manufacturing and Inspection Records                                    | 3.2-1 |

|    |       | 1.4.3 Traceability                                                            | 3.2-2 |

|    | 1.5   | Design Control                                                                | 3.2-2 |

|    |       | 1.5.1 Design Input.                                                           | 3.2-2 |

|    |       | 1.5.2 Design Output.                                                          | 3.2-2 |

|    |       | 1.5.3 Design Changes.                                                         |       |

|    |       | Materials Requirements/Material Selection                                     |       |

|    | 1.7   | Design for X                                                                  |       |

|    |       | 1.7.1 Design For Cleanability (DFC).                                          |       |

|    |       | 1.7.2 Design For Environment (DFE).                                           |       |

|    |       | 1.7.3 Design For Inspectability (DFI).                                        |       |

|    |       | 1.7.4 Design For Manufacturability (DFM).                                     |       |

|    |       | 1.7.5 Design For Reliability (DFR).                                           |       |

|    |       | 1.7.6 Design For Testability (DFT).                                           |       |

|    |       | Fatigue Life                                                                  |       |

|    |       | General Thermal Requirements                                                  |       |

|    |       | Structural Requirements                                                       |       |

|    |       | General Handling, Storage, Packaging, Preservation, and Delivery Requirements |       |

|    | 1.12  | 2 Environmental Conditions                                                    |       |

|    |       | 1.12.1 PWA Requirements                                                       |       |

|    | 1.13  | General Fabrication Requirements                                              |       |

|    |       | 1.13.1 Manufacturers                                                          |       |

|    |       | 1.13.2 Facilities                                                             |       |

|    |       | 1.13.3 Requirements Meeting the Demands of ISO 9001                           |       |

|    |       | 1.13.4 Component Attachment                                                   |       |

|    |       | 1.13.5 Electrostatic Discharge Requirements                                   |       |

|    |       | 1.13.6 Prohibition on the Use of Tin                                          |       |

|    |       | 1.13.7 Marking Requirements                                                   |       |

|    |       | 1.13.8 Outgassing                                                             |       |

|    | 1.14  | General Inspection Criteria Requirements                                      |       |

|    |       | 1.14.1 Visual Inspection.                                                     | 3.2-7 |

#### Section 3.3

## Mechanical Requirements

| De  | sign R  | equirements                                |        |

|-----|---------|--------------------------------------------|--------|

|     | _       | nmental Conditions                         |        |

|     | 1.1.1   | Conformance.                               |        |

|     | 1.1.2   | Analysis                                   | 3.3-1  |

| 1.2 | Structu | ıral Considerations                        |        |

|     | 1.2.1   | Margin of Safety.                          | 3.3-1  |

|     | 1.2.2   | Margin Calculation.                        |        |

|     | 1.2.3   | Stress and Dynamics Considerations         | 3.3-1  |

|     | 1.2.4   | Structural Fasteners                       | 3.3-2  |

| 1.3 | Mecha   | nical Design Layout                        | 3.3-2  |

|     | 1.3.1   | Accuracy.                                  |        |

|     | 1.3.2   | DSP Subchassis                             | 3.3-2  |

|     | 1.3.3   | Versa Module European (VME) Subchassis     | 3.3-2  |

|     | 1.3.4   | Microwave and Radio-Frequency Chassis.     | 3.3-2  |

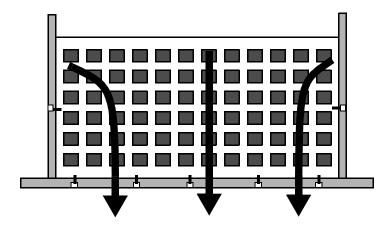

|     | 1.3.5   | Venting.                                   |        |

|     | 1.3.6   | Thermal Considerations                     |        |

|     | 1.3.7   | Detail Chassis Design.                     |        |

| 1.4 | Materi  | als                                        |        |

|     | 1.4.1   | Surface Finishes.                          |        |

| 1.5 | Fasten  | ers                                        |        |

|     | 1.5.1   | Fastener Selection.                        |        |

|     | 1.5.2   | Threaded Fasteners.                        |        |

|     | 1.5.3   | Screw in a Blind Hole                      |        |

|     | 1.5.4   | Screw and Nut Combination                  |        |

|     | 1.5.5   | Screw Length                               |        |

|     | 1.5.6   | Alternate Locking Methods.                 |        |

|     | 1.5.7   | Latent Debris Control                      |        |

|     | 1.5.8   | Fasteners in Electrical Circuits           |        |

|     | 1.5.9   | Rivets                                     |        |

|     | 1.5.10  | Inserts                                    |        |

|     | 1.5.11  | Blind Plate Nut                            |        |

| 1.6 | _       | gular Connectors                           |        |

|     | 1.6.1   | Connector Savers                           |        |

|     | 1.6.2   | Front Mounted "D" Subminiature Connectors. |        |

|     | 1.6.3   | Micro "D" Connectors                       |        |

|     | 1.6.4   | Back Mounted "D" Subminiature Connectors   |        |

| 1.7 | Circula | ar Connectors                              |        |

|     | 1.7.1   | Wall Mounted                               |        |

| 1.8 |         | Connectors                                 |        |

|     | 1.8.1   | Connector Mounting                         |        |

| 1.9 |         | ers for Other Connectors                   |        |

|     | 1.9.1   | Integral Locking.                          |        |

| 1 1 |         | onnections Cabling                         |        |

| 1.1 | 1.10.1  | Cabling Conformance                        |        |

| 1 1 |         | ion Shielding                              | 3.3-20 |

|   | 1.11.1       | Shielding Conformance.                                     | 3.3-20 |

|---|--------------|------------------------------------------------------------|--------|

|   | 1.12 Chassis | s Marking                                                  | 3.3-20 |

| 2 | Fabricati    | on Requirements                                            | 3.3-20 |

|   |              | entation                                                   |        |

|   | 2.1.1        | Completed Package.                                         |        |

|   | 2.1.2        | Manufacturing and Inspection Records                       |        |

|   | 2.1.3        | Materials Certification                                    |        |

|   | 2.1.4        | Traceability                                               |        |

|   | 2.2 Assemb   | blies Intrawiring                                          | 3.3-21 |

|   | 2.2.1        | Cabling Compliance                                         | 3.3-21 |

|   | 2.3 Thread   | ed Fastener Torque Requirements                            |        |

|   | 2.3.1        | Torque Compliance                                          |        |

|   | 2.3.2        | Locking Method                                             | 3.3-22 |

|   | 2.3.3        | Thread Engagement                                          |        |

|   | 2.3.4        | Torque Values                                              | 3.3-22 |

|   | 2.3.5        | Exposed Threads                                            | 3.3-24 |

|   | 2.4 Microv   | vave and RF Chassis Assembly                               | 3.3-24 |

|   | 2.4.1        | Internal Cavities                                          | 3.3-24 |

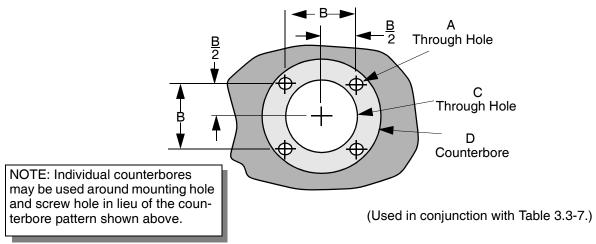

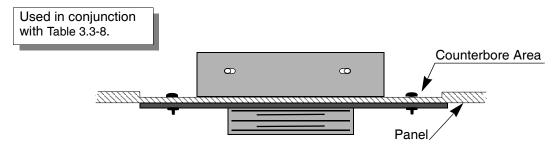

|   | 2.5 Rectan   | gular Connector Mounting                                   | 3.3-25 |

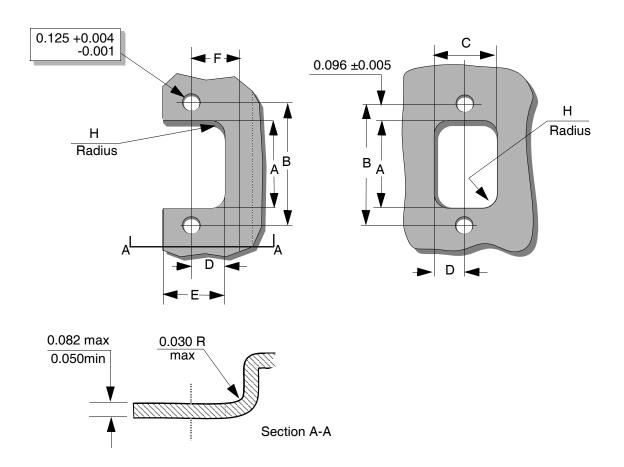

|   | 2.5.1        | Front-Mounted and Through-Hole "D" Subminiature Connectors |        |

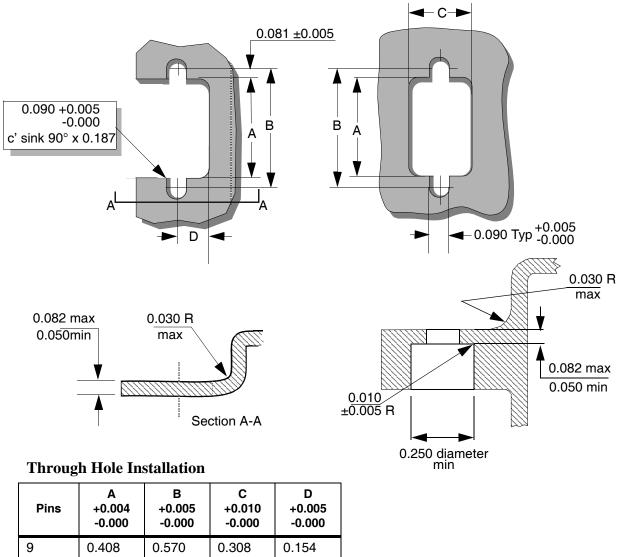

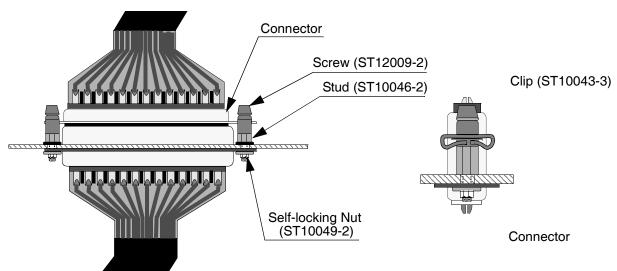

|   | 2.5.2        | Front-Mounted and Through-Hole Micro-D Connectors          | 3.3-25 |

|   | 2.5.3        | Back-Mounted "D" Subminiature Connectors                   | 3.3-25 |

|   | 2.5.4        | Micro-D Connectors                                         | 3.3-25 |

|   | 2.6 Circula  | r Connector Mounting                                       | 3.3-26 |

|   | 2.6.1        | Hermetic Connector Jam Nut Torque                          | 3.3-26 |

|   | 2.6.2        | Connector Backshell Torque                                 | 3.3-26 |

|   | 2.6.3        | Twinax Connectors                                          | 3.3-26 |

|   | 2.6.4        | RF Connectors                                              | 3.3-26 |

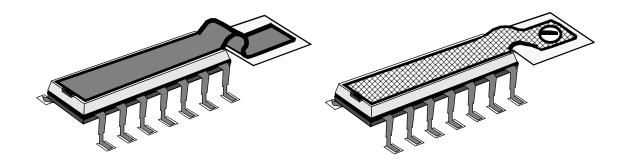

|   | 2.7 Radiati  | on Shields                                                 | 3.3-26 |

|   | 2.7.1        | Mounting Compliance                                        | 3.3-26 |

|   | 2.8 Markin   | g                                                          | 3.3-26 |

|   | 2.8.1        | Marking Compliance                                         | 3.3-26 |

|   | 2.9 Self-cli | nching Studs, Blind Nuts, and Nylon Fasteners              |        |

|   | 2.9.1        | Aluminum Shear Plates                                      | 3.3-26 |

|   | 2.9.2        | Blind Nuts                                                 | 3.3-26 |

|   | 2.9.3        | Nylon Fasteners                                            |        |

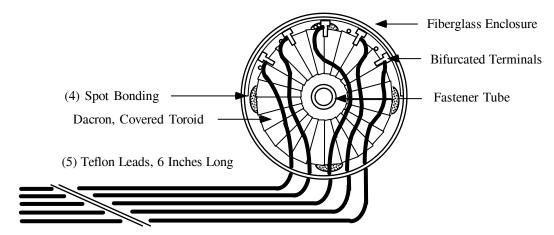

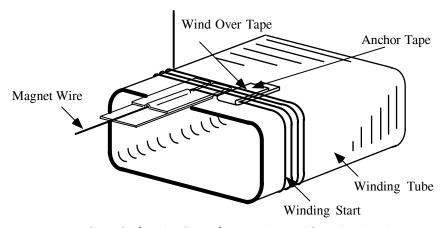

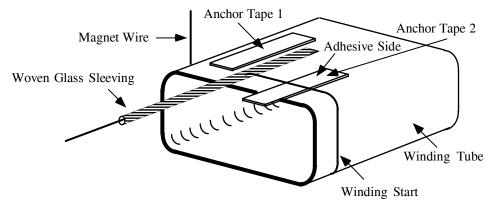

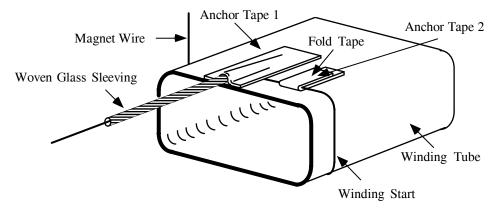

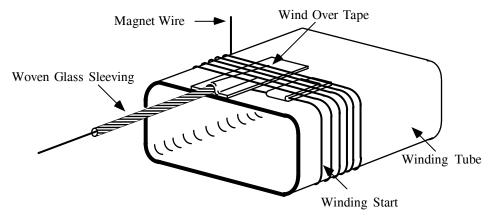

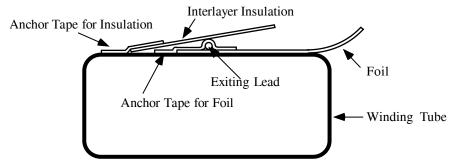

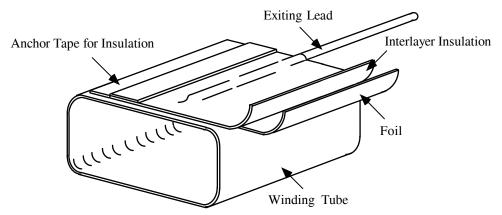

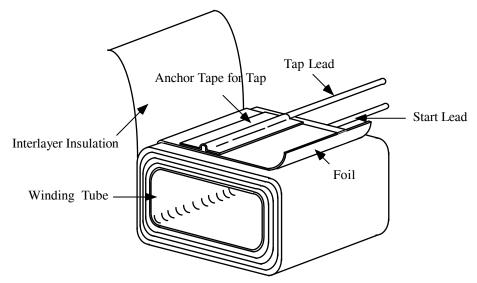

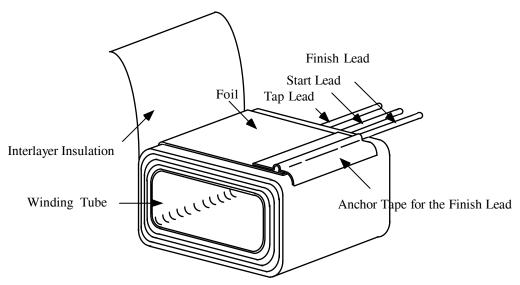

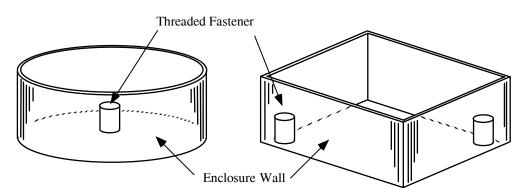

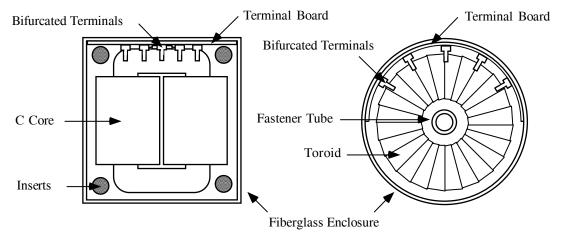

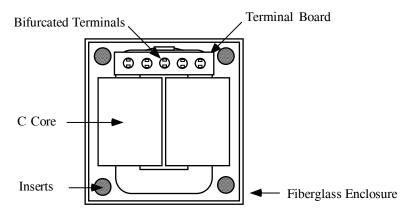

|   | 2.10 Transfo | ormers and Inductors                                       |        |

|   | 2.10.1       | Bonded Transformers and Inductors                          | 3.3-26 |

|   | 2.10.2       | Installation Torque Values                                 |        |

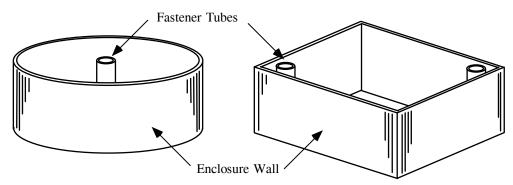

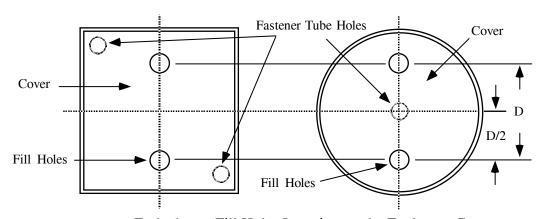

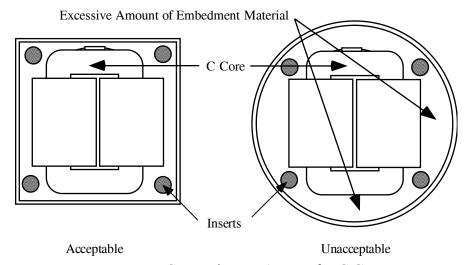

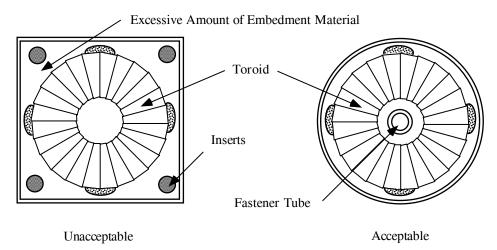

|   | 2.10.3       | Metal Fastener Tubes                                       | 3.3-27 |

|   | 2.11 Cast M  | odule Inserts                                              | 3.3-30 |

|   | 2.11.1       | Torque Values                                              |        |

|   | 2.11.2       | Bonded Cast Modules                                        | 3.3-30 |

|   | 2.12 Cable ( | Clamps                                                     |        |

|   | 2.12.1       | Metal Cable Clamps                                         |        |

|   | 2.12.2       | Nylon Cable Clamps                                         |        |

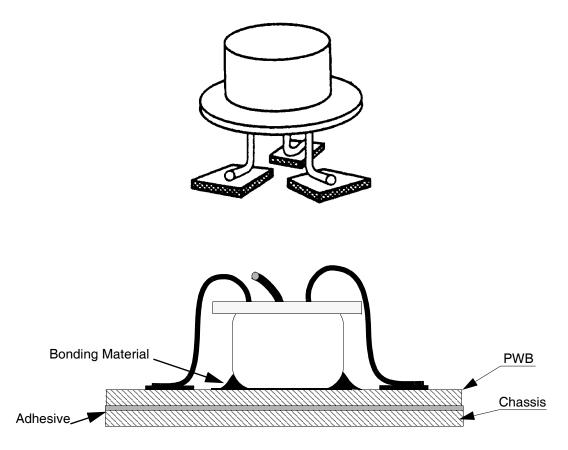

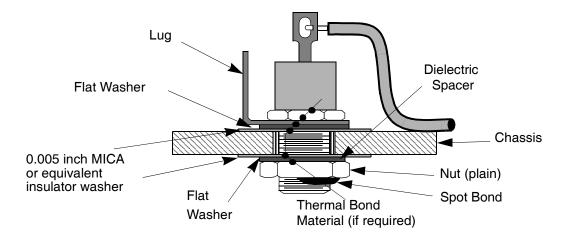

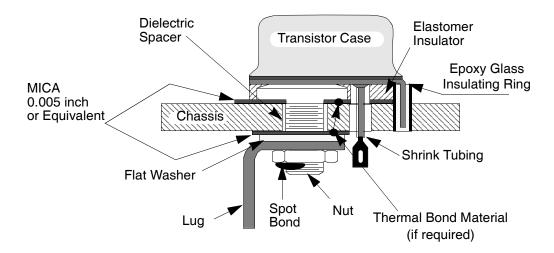

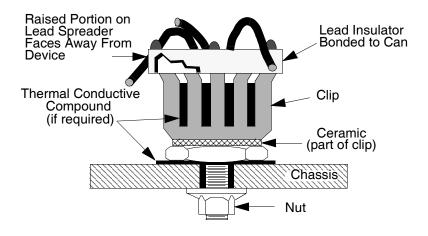

|   | 2.13 Transis | tors and Diodes                                            | 3.3-30 |

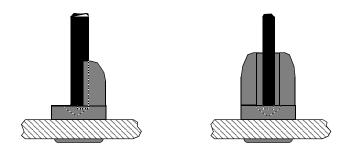

|     | 2.13.1              | Stud Mounted                           |       |

|-----|---------------------|----------------------------------------|-------|

|     | 2.13.2              | Other Stud Mounted Components          |       |

|     | 2.14 Alumi          | num Honeycomb Inserts                  |       |

|     | 2.14.1              | Insert Selection                       |       |

|     | 2.14.2              | Hole Tolerance                         |       |

|     | 2.14.3              | Blind Plate Nuts                       |       |

| 3   | Quality A           | Assurance                              |       |

|     | -                   | cation Methods                         |       |

|     | 3.1.1               | Inspection                             |       |

|     | 3.1.2               | Test                                   |       |

|     |                     |                                        |       |

|     | ion 3.4<br>ermal Re | equirements                            |       |

| 1   |                     | equirements                            |       |

| 1   |                     | onmental Conditions                    |       |

|     | 1.1 Enviro          |                                        |       |

|     |                     | Spacecraft Chassis                     |       |

|     | 1.1.2               | Analysis and Certification.            |       |

|     | 1.1.3               | Junction Temperature Reduction.        |       |

|     |                     | ging/Layout Design                     |       |

|     | 1.2.1<br>1.2.2      | Component Positioning.                 |       |

|     |                     | Subassembly Fasteners.                 |       |

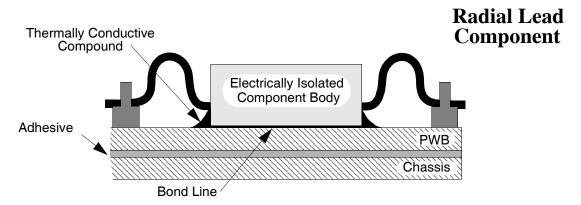

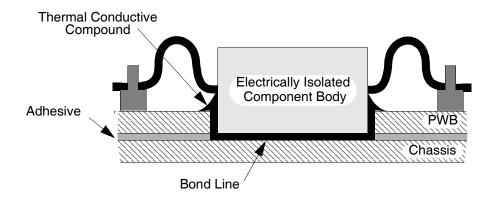

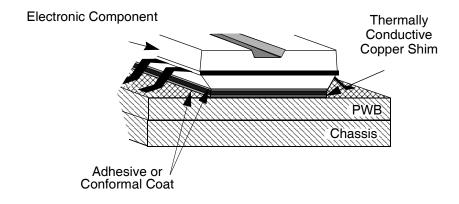

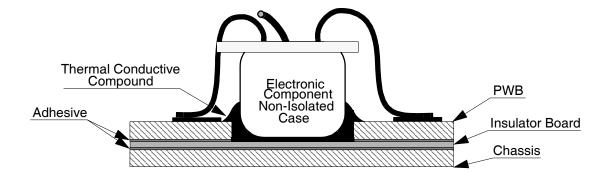

|     | 1.2.3               | Thermally Conductive Mounting Methods. |       |

|     | 1.2.4               | Thermal Cooling Straps and Braids      |       |

|     | 1.2.5               | High-Power Parts.                      |       |

|     |                     | nal Performance Parameters             |       |

|     | 1.3.1               | Dual Shear Plate.                      |       |

|     |                     | ials                                   |       |

|     | 1.4.1               | Material Selection.                    |       |

|     | 1.4.2               | Surface Finishes                       |       |

|     | 1.4.3               | Flame Retardant Materials              |       |

|     | 1.4.4               | Polymerics.                            |       |

|     | 1.4.5               | Ceramics.                              |       |

|     |                     | ner Requirements                       |       |

|     | 1.5.1               | Threaded Fasteners.                    |       |

|     | 1.5.2               | Fastener Torque.                       |       |

|     | 1.5.3               | Inserts                                |       |

|     | 1.6 Therm           | nal Design Options                     |       |

|     | 1.6.1               | Baseline Options.                      |       |

|     | 1.6.2               | PWB Design Options                     |       |

|     | 1.6.3               | Part Mounting Options.                 | 3.4-5 |

|     | on 3.5              |                                        |       |

| Sur | tace Mo             | ount Technology                        |       |

| 1   |                     | Requirements                           |       |

|     | 1.1 Produc          | cibility Level                         |       |

|   | 1.2                     | Design Rule Exceptions                                                                                                                                                                                                                                                                                           |                                                             |

|---|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|   |                         | 1.2.1 General Exceptions                                                                                                                                                                                                                                                                                         | 3.5-1                                                       |

|   |                         | 1.2.2 Electronic Parts                                                                                                                                                                                                                                                                                           | 3.5-1                                                       |

|   |                         | 1.2.3 Component-to-Board Spacing.                                                                                                                                                                                                                                                                                | 3.5-2                                                       |

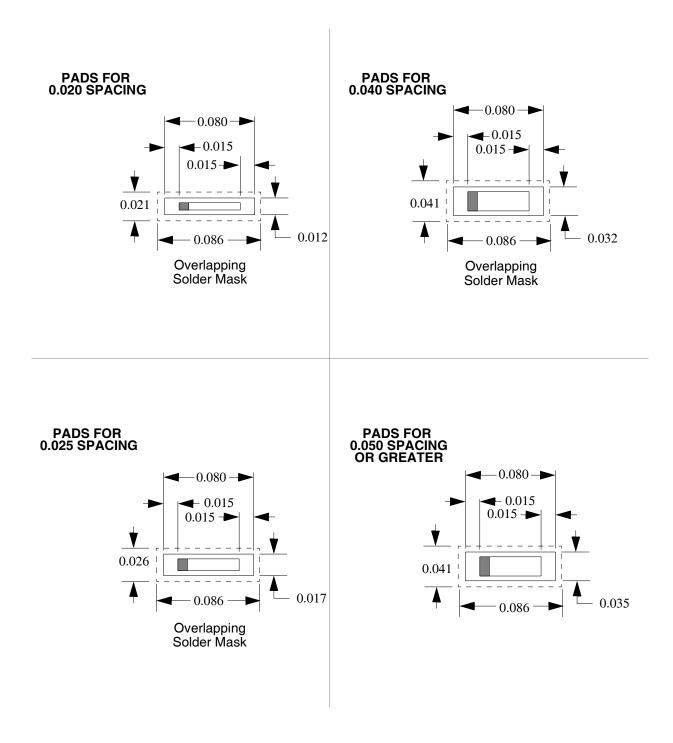

|   |                         | 1.2.4 Land Pattern Standards.                                                                                                                                                                                                                                                                                    | 3.5-3                                                       |

| 2 | As                      | sembly Requirements                                                                                                                                                                                                                                                                                              | 3.5-9                                                       |

|   |                         | Assembly Rule Exceptions                                                                                                                                                                                                                                                                                         |                                                             |

|   |                         | 2.1.1 Materials.                                                                                                                                                                                                                                                                                                 |                                                             |

|   |                         | 2.1.2 Testing Requirements                                                                                                                                                                                                                                                                                       |                                                             |

|   |                         | 2.1.3 Lead Forming.                                                                                                                                                                                                                                                                                              |                                                             |

|   |                         | 2.1.4 Terminal Mounting.                                                                                                                                                                                                                                                                                         |                                                             |

|   |                         | 2.1.5 Tinning                                                                                                                                                                                                                                                                                                    |                                                             |

|   |                         | 2.1.6 Alignment Requirements                                                                                                                                                                                                                                                                                     |                                                             |

|   |                         | 2.1.7 Reflow Requirements.                                                                                                                                                                                                                                                                                       |                                                             |

|   |                         | 2.1.8 Cleaning after Soldering.                                                                                                                                                                                                                                                                                  |                                                             |

|   |                         | 2.1.9 Solder Connections                                                                                                                                                                                                                                                                                         |                                                             |

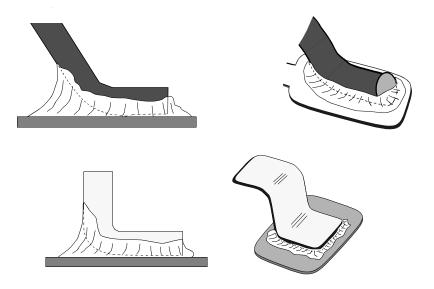

|   |                         | 2.1.10 Lap Joints (Gull-wing Leads).                                                                                                                                                                                                                                                                             |                                                             |

|   |                         | 2.1.11 Rework and Repair.                                                                                                                                                                                                                                                                                        |                                                             |

|   |                         | 2.1.12 Deliverables                                                                                                                                                                                                                                                                                              |                                                             |

| 3 | Or                      | ality Assurance                                                                                                                                                                                                                                                                                                  |                                                             |

|   | _                       | Acceptance Criteria                                                                                                                                                                                                                                                                                              |                                                             |

| 1 | Sco                     | ppe                                                                                                                                                                                                                                                                                                              | 3.6-1                                                       |

|   | 1.1                     | Purpose                                                                                                                                                                                                                                                                                                          | 3.6-1                                                       |

|   | 1.2                     | Applicability                                                                                                                                                                                                                                                                                                    | 3.6-1                                                       |

|   | 1.3                     | PWB Types                                                                                                                                                                                                                                                                                                        | 3.6-1                                                       |

|   | 1.4                     | Assembly Methods                                                                                                                                                                                                                                                                                                 |                                                             |

| 2 | Ge                      | neral Information                                                                                                                                                                                                                                                                                                | 3.6-2                                                       |

|   |                         | Role of Electronic Packaging and Fabrication                                                                                                                                                                                                                                                                     |                                                             |

|   |                         |                                                                                                                                                                                                                                                                                                                  |                                                             |

|   | 2.3                     | Waivers and Deviations                                                                                                                                                                                                                                                                                           |                                                             |

|   |                         | Waivers and Deviations  Vendor Selection and Qualification                                                                                                                                                                                                                                                       |                                                             |

|   |                         |                                                                                                                                                                                                                                                                                                                  | 3.6-2<br>3.6-2<br>3.6-3                                     |

|   |                         | Vendor Selection and Qualification                                                                                                                                                                                                                                                                               | 3.6-2<br>3.6-3<br>3.6-3                                     |

|   |                         | Vendor Selection and Qualification                                                                                                                                                                                                                                                                               | 3.6-2<br>3.6-3<br>3.6-3<br>3.6-3<br>3.6-3                   |

|   |                         | Vendor Selection and Qualification                                                                                                                                                                                                                                                                               | 3.6-2<br>3.6-2<br>3.6-3<br>3.6-3<br>3.6-3<br>3.6-3          |

|   |                         | Vendor Selection and Qualification.  2.3.1 Vendor Selection.  2.3.2 Vendor Capability                                                                                                                                                                                                                            | 3.6-2 3.6-3 3.6-3 3.6-3 3.6-4 3.6-4                         |

|   |                         | Vendor Selection and Qualification.  2.3.1 Vendor Selection.  2.3.2 Vendor Capability.  2.3.3 Survey Team.  2.3.4 Vendor Qualification.                                                                                                                                                                          | 3.6-2 3.6-3 3.6-3 3.6-3 3.6-4 3.6-4                         |

| 3 |                         | Vendor Selection and Qualification.  2.3.1 Vendor Selection.  2.3.2 Vendor Capability                                                                                                                                                                                                                            | 3.6-2 3.6-3 3.6-3 3.6-3 3.6-3 3.6-4 3.6-4 3.6-4             |

| 3 | En                      | Vendor Selection and Qualification.  2.3.1 Vendor Selection.  2.3.2 Vendor Capability.  2.3.3 Survey Team.  2.3.4 Vendor Qualification.  2.3.5 Approved Vendor List.  2.3.6 Vendor Disqualification and Requalification.                                                                                         | 3.6-2 3.6-3 3.6-3 3.6-3 3.6-4 3.6-4 3.6-5                   |

| 3 | En                      | Vendor Selection and Qualification                                                                                                                                                                                                                                                                               | 3.6-2 3.6-3 3.6-3 3.6-3 3.6-4 3.6-4 3.6-5 3.6-5             |

| 3 | <b>En</b> 3.1           | Vendor Selection and Qualification.  2.3.1 Vendor Selection.  2.3.2 Vendor Capability.  2.3.3 Survey Team.  2.3.4 Vendor Qualification.  2.3.5 Approved Vendor List.  2.3.6 Vendor Disqualification and Requalification.  gineering and Layout Considerations  Design For X.                                     | 3.6-2 3.6-3 3.6-3 3.6-3 3.6-4 3.6-4 3.6-4 3.6-5 3.6-5       |

|   | <b>En</b> 3.1 <b>De</b> | Vendor Selection and Qualification.  2.3.1 Vendor Selection.  2.3.2 Vendor Capability.  2.3.3 Survey Team.  2.3.4 Vendor Qualification.  2.3.5 Approved Vendor List.  2.3.6 Vendor Disqualification and Requalification gineering and Layout Considerations  Design For X.  3.1.1 Design For Producibility (DFP) | 3.6-2 3.6-3 3.6-3 3.6-3 3.6-3 3.6-4 3.6-4 3.6-5 3.6-5 3.6-5 |

|   | En 3.1  De 4.1          | Vendor Selection and Qualification                                                                                                                                                                                                                                                                               | 3.6- 3.6- 3.6- 3.6- 3.6- 3.6- 3.6- 3.6-                     |

| 4 | .3 | Dimens   | ioning and Tolerancing                                     | . 3.6-12 |

|---|----|----------|------------------------------------------------------------|----------|

| 4 | .4 | Electric | al Testingal                                               | 3.6-12   |

|   |    | 4.4.1    | Electrical Verification Testing at the PWB Vendor          | 3.6-12   |

|   |    | 4.4.2    | Integri-Test                                               | 3.6-12   |

|   |    | 4.4.3    | Alternative Procedure for Creating an IPC-D-356A File      | 3.6-14   |

| 4 | .5 | PWB Id   | lentification                                              | 3.6-14   |

|   |    | 4.5.1    | Serialization in the Case of PWB Rebuild                   | . 3.6-16 |

| 4 | .6 | Coupon   | S                                                          |          |

|   |    | 4.6.1    | A and B Coupons                                            | 3.6-16   |

| 4 | .7 | Materia  | l Identification and Specification                         |          |

|   |    | 4.7.1    | Abbreviations                                              |          |

|   |    | 4.7.2    | Examples of Common Material Callouts                       |          |

|   |    | 4.7.3    | Laminate/Prepreg Material Choice                           |          |

| 4 | .8 | Design   | Rules                                                      |          |

|   |    | 4.8.1    | Materials                                                  |          |

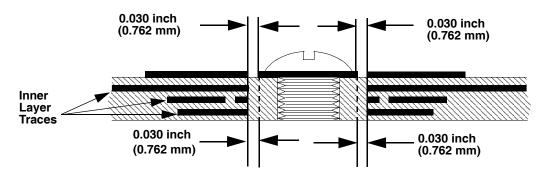

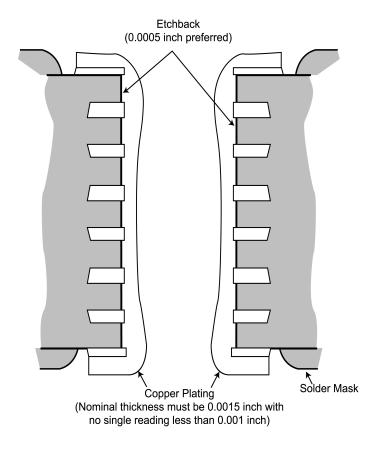

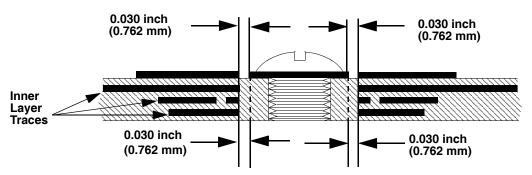

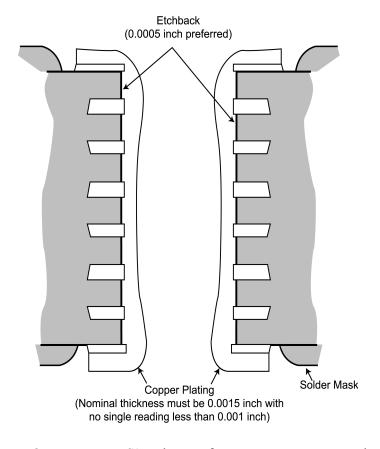

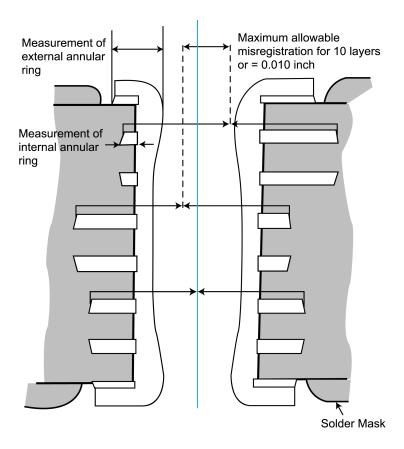

|   |    | 4.8.2    | PTHs and Vias                                              |          |

|   |    | 4.8.3    | Non-Plated Through Holes                                   |          |

|   |    | 4.8.4    | Antipads in the Plane Layers                               |          |

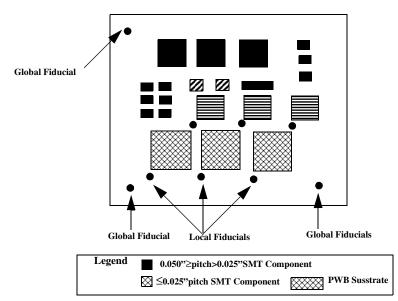

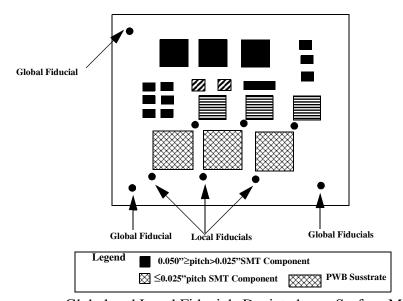

|   |    | 4.8.5    | Fiducials for SMT PWBs                                     |          |

|   |    | 4.8.6    | Footprint Patterns                                         |          |

|   |    | 4.8.7    | Distance of Features to Board Edges and to Mounting Holes. |          |

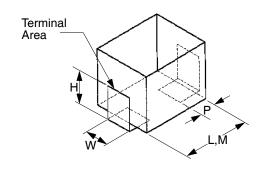

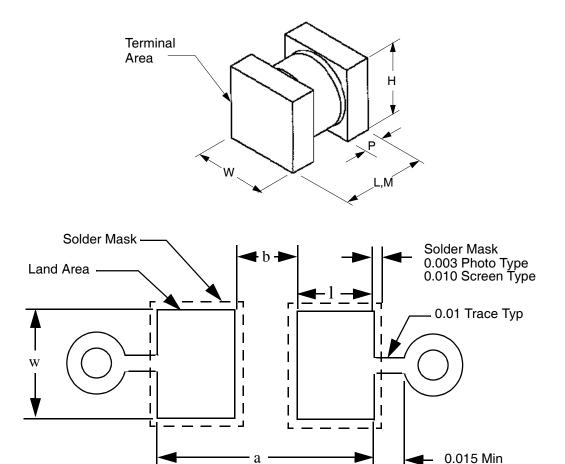

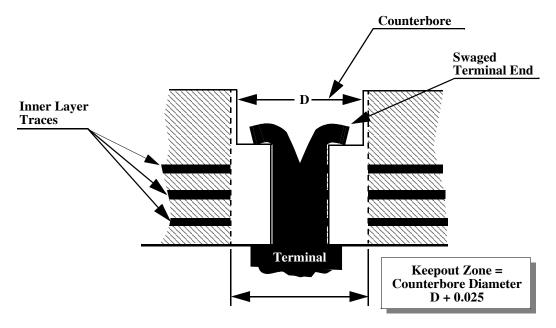

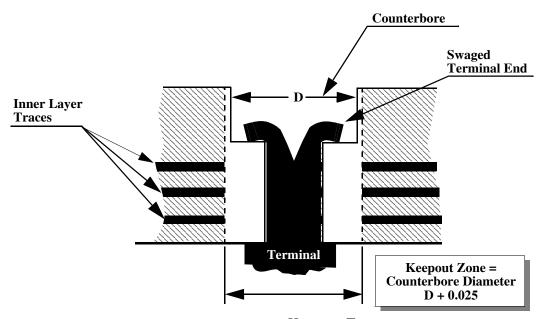

|   |    | 4.8.8    | Terminals.                                                 |          |

|   |    | 4.8.9    | Surface Finish.                                            |          |

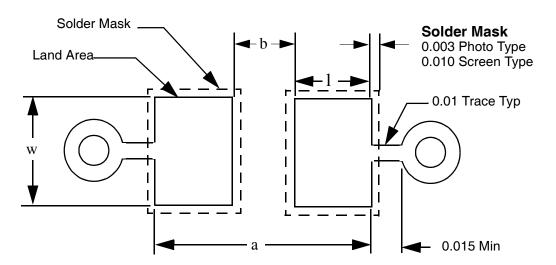

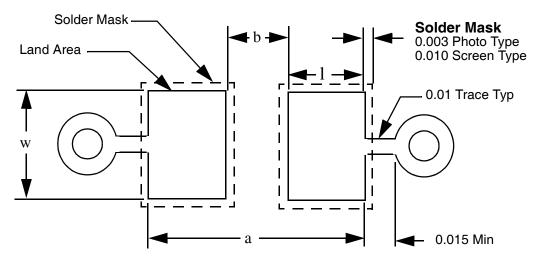

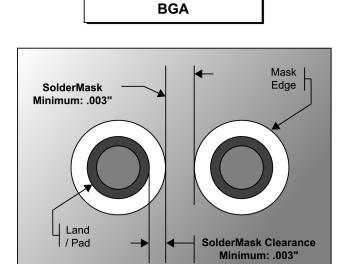

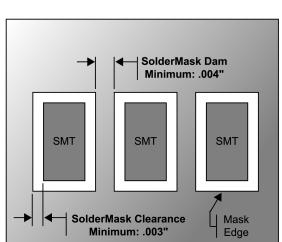

|   |    | 4.8.10   | Solder Mask.                                               |          |

|   |    | 4.8.11   | Legend Marking Materials.                                  |          |

|   |    | 4.8.12   | Dielectric Separation between Adjacent Conductive Layers   |          |

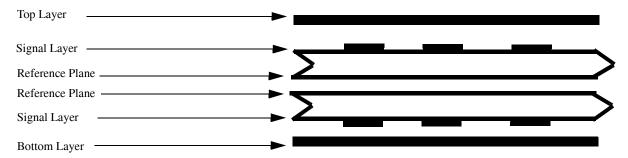

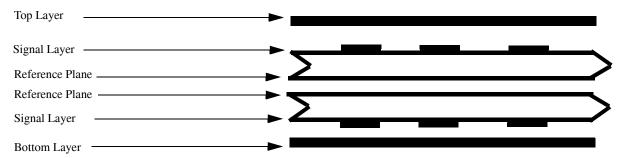

|   |    | 4.8.13   | Multilayer Board Construction                              |          |

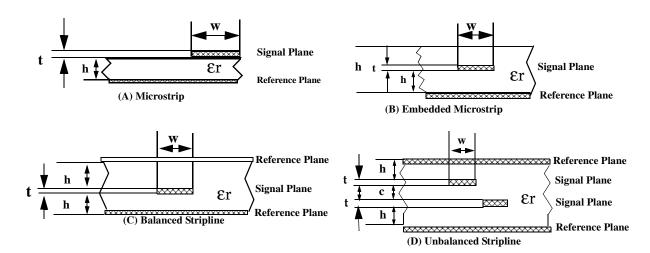

|   |    | 4.8.14   | Controlled Emissions.                                      |          |

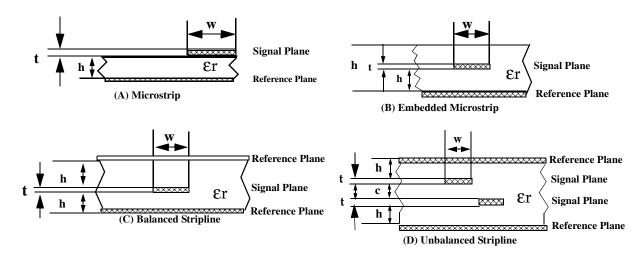

|   |    | 4.8.15   | Controlled Impedance MLB Construction                      |          |

| 4 |    |          | tion Drawing                                               |          |

|   |    | 4.9.1    | Fabrication Drawing.                                       |          |

| 4 |    |          | Output                                                     |          |

|   |    | _        | •                                                          |          |

|   |    |          | on Requirements                                            |          |

|   |    |          | f Precedence                                               |          |

| 5 |    |          | nance Class                                                |          |

|   |    | 5.2.1    | Pre-Fabrication Inspection.                                |          |

| _ |    | 5.2.2    | Board Type                                                 |          |

| 5 |    |          | tion Requirements—Flight PWBs                              |          |

|   |    | 5.3.1    | Acceptance Criteria                                        |          |

|   |    | 5.3.2    | Coupons                                                    |          |

|   |    | 5.3.3    | Artworks to be Sent to JPL                                 |          |

|   |    | 5.3.4    | Panelization.                                              |          |

|   |    | 5.3.5    | Inner Layer Inspection of MLBs.                            |          |

|   |    | 5.3.6    | MLB Lamination                                             |          |

|   |    | 5.3.7    | Drilling                                                   |          |

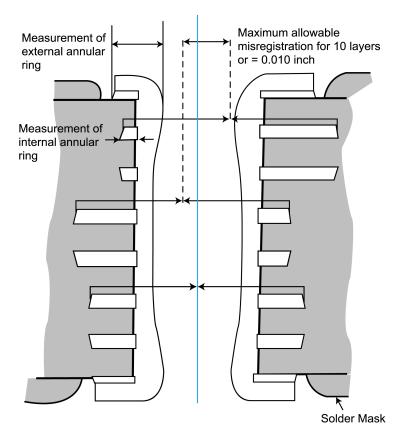

|   |    | 5.3.8    | MLB Registration                                           |          |

|   |    | 5.3.9    | PTHs and Vias                                              | . 3.6-46 |

|   |                     | 5.3.10 Cleaning Prior to Solder Mask Application  |        |

|---|---------------------|---------------------------------------------------|--------|

|   |                     | 5.3.11 Solder Mask.                               |        |

|   |                     | 5.3.12 Surface Finish.                            |        |

|   |                     | 5.3.13 Legend Ink                                 |        |

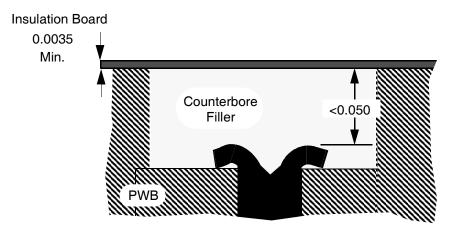

|   |                     | 5.3.14 Insulation Board.                          |        |

|   |                     | 5.3.15 Electrical Test.                           |        |

|   |                     | 5.3.16 Rework                                     |        |

|   |                     | 5.3.17 Maximum Bow and Twist                      |        |

|   |                     | 5.3.18 Serialization and Board Identification.    |        |

|   |                     | 5.3.19 Handling & Packaging/Shipping              |        |

|   |                     | 5.3.20 Chief Fabrication Requirements             |        |

|   |                     | 5.3.21 JPL QA Source Inspections.                 |        |

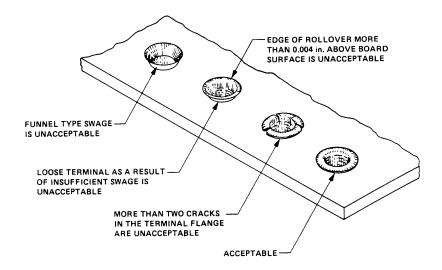

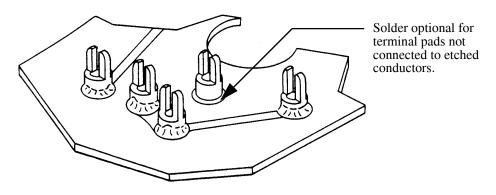

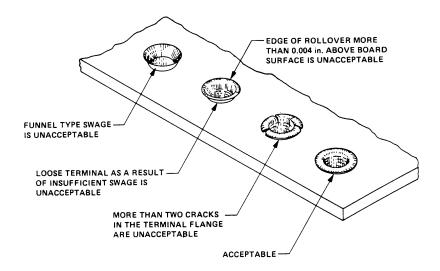

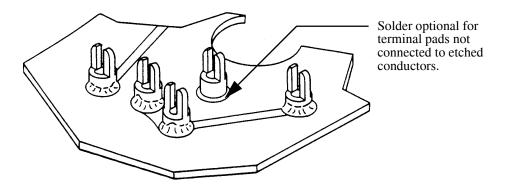

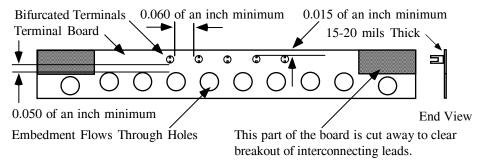

|   | 5.4                 | Fabrication Requirements-Terminal Boards          |        |

|   |                     | 5.4.1 Terminals.                                  |        |

| 6 | Qu                  | ality Assurance                                   | 3.6-53 |

|   |                     | JPL Approval and Reviews                          |        |

|   |                     | 6.1.1 QA Governing Documents                      |        |

|   |                     | 6.1.2 Survey of Vendor's Site                     |        |

|   |                     | 6.1.3 Pre-fabrication Approvals                   |        |

|   |                     | 6.1.4 Source Inspections.                         |        |

|   | 6.2                 | Data Package-Deliverables to JPL                  |        |

| 7 |                     | UDELINES AND RECOMMENDATIONS                      |        |

| - |                     | Purpose                                           |        |

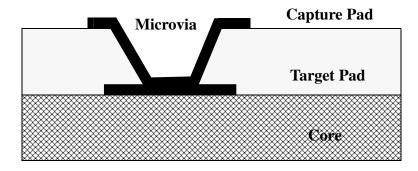

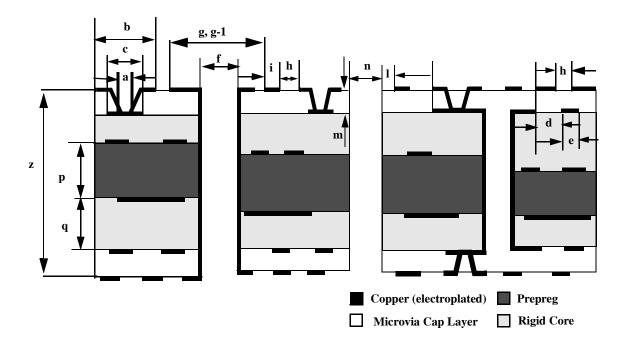

|   | ,                   | 7.1.1 Microvia PWBs.                              |        |

|   | ion 3<br><b>xib</b> | le and Rigid-Flexible Printed Wiring              |        |

| 1 | Sco                 | ope                                               |        |

|   |                     | Purpose                                           |        |

|   |                     | Applicability                                     |        |

|   |                     | PWB Types                                         |        |

|   |                     | Assembly Methods                                  |        |

| 2 |                     | neral Information                                 |        |

| _ |                     | Role of Electronic Packaging and Fabrication      |        |

|   |                     | Waivers and Deviations                            |        |

|   |                     | Vendor Selection and Qualification                |        |

|   |                     | 2.3.1 Vendor Selection                            |        |

|   |                     | 2.3.2 Vendor Capability                           |        |

|   |                     | 2.3.3 Survey Team.                                |        |

|   |                     | 2.3.4 Vendor Qualification.                       |        |

|   |                     | 2.3.5 Approved Vendor List                        |        |

|   |                     | 2.3.6 Vendor Disqualification and Requalification |        |

| 3 | En                  | gineering and Layout Considerations               |        |

| J |                     | Design For X                                      |        |

|   | ٥.1                 | 3.1.1 Design For Producibility (DFP)              |        |

|   |                     | 2006                                              |        |

| 4 | De   | sign Re | equirements                                               | 3.7-12 |

|---|------|---------|-----------------------------------------------------------|--------|

|   |      | _       | ed Units                                                  |        |

|   | 4.2  |         | nance Class                                               |        |

|   | 4.3  |         | sioning and Tolerancing                                   |        |

|   |      |         | cal Testing                                               |        |

|   |      | 4.4.1   | Electrical Verification Testing at the PWB Vendor         |        |

|   |      | 4.4.2   | Integri-Test.                                             |        |

|   |      | 4.4.3   | Alternative Procedure for Creating an IPC-D-356A File     |        |

|   | 4.5  | PWB I   | dentification                                             |        |

|   |      | 4.5.1   | Serialization in the Case of PWB Rebuild                  |        |

|   | 4.6  | Coupor  | 18                                                        |        |

|   |      | 4.6.1   | A and B Coupons                                           |        |

|   | 4.7  | Materia | al Identification and Specification                       |        |

|   |      | 4.7.1   | Abbreviations                                             |        |

|   |      | 4.7.2   | Examples of Common Material Callouts.                     |        |

|   |      | 4.7.3   | Laminate/Prepreg Material Choice                          |        |

|   | 4.8  |         | Rules                                                     |        |

|   |      | 4.8.1   | Materials.                                                |        |

|   |      | 4.8.2   | PTHs and Vias.                                            |        |

|   |      | 4.8.3   | Non-Plated Through Holes.                                 |        |

|   |      | 4.8.4   | Antipads in the Plane Layers.                             |        |

|   |      | 4.8.5   | Fiducials for SMT PWBs.                                   |        |

|   |      | 4.8.6   | Footprint Patterns.                                       |        |

|   |      | 4.8.7   | Distance of Features to Board Edges and to Mounting Holes |        |

|   |      | 4.8.8   | Terminals.                                                |        |

|   |      | 4.8.9   | Surface Finish.                                           |        |

|   |      | 4.8.10  | Solder Mask.                                              |        |

|   |      | 4.8.11  | Legend Marking Materials.                                 |        |

|   |      | 4.8.12  | Dielectric Separation between Adjacent Conductive Layers  |        |

|   |      | 4.8.13  | Multilayer Board Construction                             |        |

|   |      | 4.8.14  | Controlled Emissions.                                     |        |

|   |      | 4.8.15  | Controlled Impedance MLB Construction                     |        |

|   | 40   |         | tion Drawing                                              |        |

|   | ₹.)  | 4.9.1   | Fabrication Drawing.                                      |        |

|   | 4 10 |         | Output                                                    |        |

| _ |      | •       | •                                                         |        |

| 5 |      |         | on Requirements                                           |        |

|   |      |         | of Precedence                                             |        |

|   | 5.2  |         | nance Class                                               |        |

|   |      | 5.2.1   | Pre-Fabrication Inspection.                               |        |

|   |      | 5.2.2   | Board Type                                                |        |

|   | 5.3  |         | tion Requirements—Flight PWBs                             |        |

|   |      | 5.3.1   | Acceptance Criteria                                       | 3.7-44 |

|   |      | 5.3.2   | Coupons.                                                  |        |

|   |      | 5.3.3   | Artworks to be Sent to JPL                                | 3.7-44 |

|   |      | 5.3.4   | Panelization.                                             |        |

|   |      | 5.3.5   | Inner Layer Inspection of MLBs.                           | 3.7-45 |

|   |      | 5.3.6   | MLB Lamination.                                           | 3.7-45 |

|    |      | 5.3.7    | Drilling                                   |        |

|----|------|----------|--------------------------------------------|--------|

|    |      | 5.3.8    | MLB Registration                           | 3.7-47 |

|    |      | 5.3.9    | PTHs and Vias                              |        |

|    |      | 5.3.10   | Cleaning Prior to Solder Mask Application. |        |

|    |      | 5.3.11   | Solder Mask                                |        |

|    |      | 5.3.12   | Surface Finish.                            |        |

|    |      | 5.3.13   | Legend Ink                                 |        |

|    |      | 5.3.14   | Insulation Board                           |        |

|    |      | 5.3.15   | Electrical Test                            |        |

|    |      | 5.3.16   | Rework                                     |        |

|    |      | 5.3.17   | Maximum Bow and Twist                      |        |

|    |      | 5.3.18   | Serialization and Board Identification     |        |

|    |      | 5.3.19   | Handling & Packaging/Shipping              |        |

|    |      | 5.3.20   | Chief Fabrication Requirements             |        |

|    |      | 5.3.21   | JPL QA Source Inspections.                 |        |

|    | 5.4  | Fabrica  | ation Requirements-Terminal Boards         |        |

|    |      | 5.4.1    | Terminals.                                 |        |

| 6  | Ou   | ıality A | Assurance                                  | 3.7-55 |

| Ů  | _    | -        | pproval and Reviews                        |        |

|    | 0.1  | 6.1.1    | QA Governing Documents.                    |        |

|    |      | 6.1.2    | Survey of Vendor's Site.                   |        |

|    |      | 6.1.3    | Pre-fabrication Approvals                  |        |

|    |      | 6.1.4    | Source Inspections.                        |        |

|    | 6.2  |          | ackage-Deliverables to JPL                 |        |

| Wi | re V | Vrap     |                                            |        |

| 1  | De   | sign R   | equirements                                | 3.8-1  |

|    | 1.1  | Docum    | nentation                                  |        |

|    |      | 1.1.1    | Complete Package                           |        |

|    |      | 1.1.2    | Assembly Drawing                           |        |

|    |      | 1.1.3    | Wire List                                  |        |

|    |      | 1.1.4    | Manufacturing Data                         |        |

|    | 1.2  | Wire     | -                                          |        |

|    |      | 1.2.1    | Wire Specification                         |        |

|    |      | 1.2.2    | Conductor                                  |        |

|    |      | 1.2.3    | Conductor Finish                           |        |

|    |      | 1.2.4    | Elastic Properties of 30 AWG Wire          |        |

|    |      | 1.2.5    | Elastic Properties of 28 AWG Wire          |        |

|    |      | 1.2.6    | Wire Softness                              |        |

|    | 1.3  | Insulat  | ion                                        |        |

|    |      | 1.3.1    | Basic Properties                           |        |

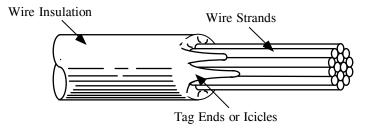

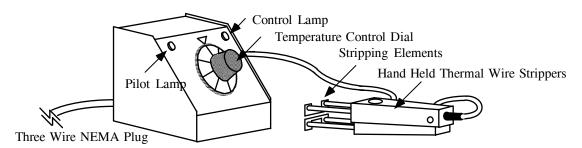

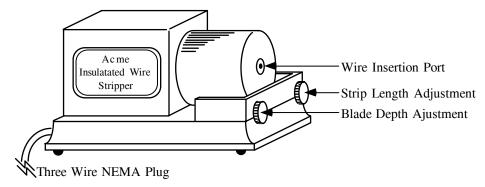

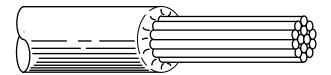

|    |      | 1.3.2    | Wire Stripping                             |        |

|    |      | 1.3.3    | Insulation Thickness                       | 3.8-3  |

|    | 1.4  | Board    | Design                                     | 3.8-3  |

|    |      | 1.4.1    | Plane Requirements                         |        |

|    |      |          | •                                          |        |

|   |     | 1.4.2   | Dielectric Materials.      | 3.8-3 |

|---|-----|---------|----------------------------|-------|

|   |     | 1.4.3   | Copper Clad and Plating.   | 3.8-3 |

|   |     | 1.4.4   | Flame Retardant Materials  | 3.8-3 |

|   |     | 1.4.5   | Installation Hole Size     | 3.8-4 |

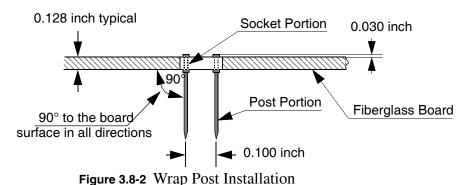

|   | 1.5 | Wrap P  | ost                        | 3.8-4 |

|   |     | 1.5.1   | Post Dimensions            |       |

|   |     | 1.5.2   | Wrap Post Materials        |       |

|   |     | 1.5.3   | Surface Plating            |       |

|   |     | 1.5.4   | Minimum Plating.           |       |

|   |     | 1.5.5   | Edge Radius                |       |

|   |     | 1.5.6   | Edge Burrs                 |       |

|   |     | 1.5.7   | Post Length                |       |

|   |     | 1.5.8   | Apex Configuration         |       |

|   |     | 1.5.9   | Parallelism                |       |

|   |     | 1.5.10  | Wrap Post Spacing          |       |

|   |     | 1.5.10  | Wrap Post Insulation.      |       |

|   |     | 1.5.11  | Minimum Torque.            |       |

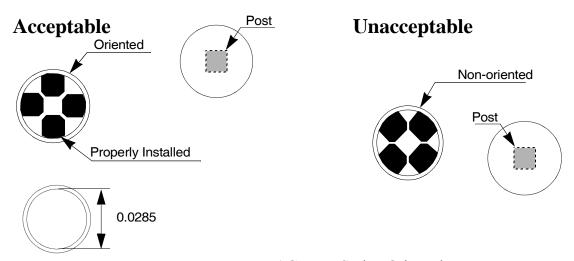

|   |     | 1.5.12  | Contact Spring Orientation |       |

|   |     | 1.5.13  | Socket/Post Orientation    |       |

|   |     | 1.5.14  | Wrap Post Installation     |       |

|   |     |         | 1                          |       |

|   | 1.6 | 1.5.16  | Socket/Post Orientation    |       |

|   | 1.0 |         | Design                     |       |

|   |     | 1.6.1   | Hole Diameter              |       |

|   |     | 1.6.2   | Socket Material            |       |

|   |     | 1.6.3   | Contact Spring             |       |

|   |     | 1.6.4   | Type of Contact            |       |

|   |     | 1.6.5   | Plating                    |       |

|   |     | 1.6.6   | Orientation                |       |

|   | 1.7 |         | Vrap Connection            |       |

|   |     | 1.7.1   | Routing                    |       |

| 2 | Fal | bricati | on Requirements            | 3.8-6 |

|   |     |         | nent                       |       |

|   |     | 2.1.1   | Certified Tooling          |       |

|   | 2.2 | Wire    |                            |       |

|   |     | 2.2.1   | Continuous Insulation      | 3.8-6 |

|   |     | 2.2.2   | Rewrapping                 |       |

|   |     | 2.2.3   | Damage Avoidance           |       |

|   |     | 2.2.4   | Excessive Wire.            |       |

|   | 2.3 | Board.  |                            |       |

|   |     | 2.3.1   | Electrical Testing         |       |

|   | 2.4 |         | ost                        |       |

|   | r   | 2.4.1   | Bent Wrap Post             |       |

|   |     | 2.4.2   | Wrap Post Plating          |       |

|   |     | 2.4.3   | Post Rewrap                |       |

|   | 25  |         | Post Newrap                |       |

|   | ۷.5 | 2.5.1   | Minimum Retention          |       |

|   |     | 2.5.1   | Retention Force of Contact |       |

|   |     | 4.5.4   | Retention Foles of Confact | 3.0-/ |

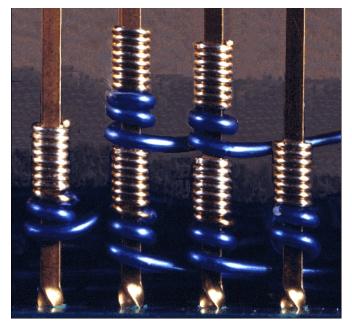

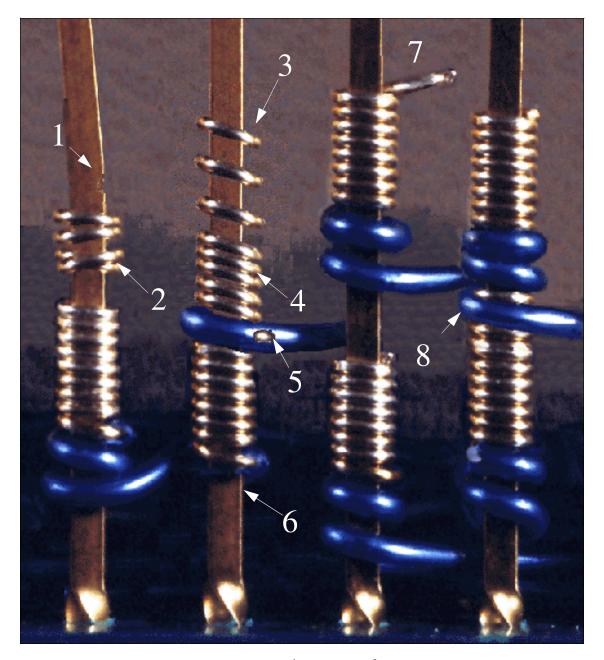

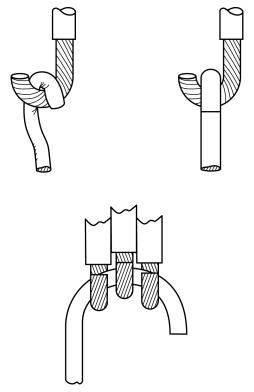

|     | 2.6  | Wrap (                                      | Connection                                                                                                             |                                           |

|-----|------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|     |      | 2.6.1                                       | Minimum Turns of Wire.                                                                                                 |                                           |

|     |      | 2.6.2                                       | Proper Wire-Wrap Construction.                                                                                         |                                           |

|     |      | 2.6.3                                       | End Tail                                                                                                               |                                           |

|     |      | 2.6.4                                       | Adjacent Turn Spacing.                                                                                                 |                                           |