MIL-STD-2117(EC) 27 FEBRUARY 1981

# MILITARY STANDARD

# COMMUNICATIONS, DIGITAL CONTROL AND STATUS INFORMATION INTERCHANGE STANDARD

NO DELIVERABLE DATA REQUIRED BY THIS DOCUMENT.

FSC TCTS

### DEPARTMENT OF DEFENSE Washington, D.C. 20301

Control and Status Information Interchange Standard

MIL-STD-2117(EC)

1. This Military Standard is approved for use by the Naval Electronic Systems Command, Department of the Navy, and is available for use by all Departments and Agencies of the Department of Defense.

2. Beneficial comments (recommendations, additions, deletions) and any pertinent data which may be of use in improving this document should be addressed to: Commander, Naval Electronic Systems Command (ELEX 5043), Mashington, D.C. 20360, by using the self-addressed Standardization Document Improvement Proposal (DD Form 1426) appearing at the end of this document or by letter.

1

· ...

### FOREWORD

This document defines the interface standards for the automatic interchange of control and status (C&S) digital information in the shipboard Naval Telecommunications System (NTS). The standard is intended to provide guidelines for the design and acquisition of equipments, systems, software and firmware related to the U.S. Navy's automated communications systems. Physical, functional, and electrical characteristics are addressed.

-----

-----

MIL-STD-2117 (EC) 27 February 1981

### CONTENTS

| Paragraph         1.         SCOPE         1           1.1         Purpose         1           1.2         Scope         1           1.3.1         Type B - Naval tactical data system NTDS         1           1.3.1         Type B - Naval tactical data system NTDS         1           1.3.2         Multiplex Serial (MIL-STD-1355)         1           1.4         Implementation         2           1.5         Specific Interface formatting requirements         2           2.1         Government documents         4           2.2         Other publications         6           3.         DEFINITIONS         7           3.2.1         Introduction         7           3.2.2         Bat erron rate (BER)         7           3.2.3         Baud         7           3.2.4         Bit         7           3.2.5         Bit, parallel         8           3.2.6         Bit, parallel         8           3.2.7         Bit(s), framing         8           3.2.8         Bit, parallel         8           3.2.9         Bit, parallel         8           3.2.10         Bit, parity         8           3.2.                                                                                                   |           |        |                                            | PAGE   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|--------------------------------------------|--------|

| 1.1         Purpose         1           1.2         Scope         1           1.3         Data interface clasification         1           1.3.1         Type B - Naval tactical data system NTDS         1           1.3.2         Multiplex Serial (ML-STD-1553)         1           1.4         Implementation         2           1.5         Specific interface formatting requirements         2           2.1         REFERENCED DOCUMENTS         4           2.1         Government documents         4           2.2         Other publications         6           3.         DEFINITIONS         7           3.1         Introduction         7           3.2.1         Asynchronous data transmission channel         7           3.2.2         Definitions         6           3.2.1         Asynchronous data transmission channel         7           3.2.2         Beintions         6           3.2.1         Asynchronous data transmission channel         7           3.2.2         Beintions         6           3.2.1         Asynchronous data transmission channel         7           3.2.2.3         Baud         7           3.2.4         Bit <td>Paragraph</td> <td>1.</td> <td>SCOPE</td> <td>1-</td> | Paragraph | 1.     | SCOPE                                      | 1-     |

| 1.3       Data interface classification       1         1.3.1       Type B - Naval tactical data system NTDS       1         1.3.2       Multiplex Serial (MiL-STD-1553)       1         1.4       Implementation       2         1.5       Specific interface formatting requirements       2         2.       REFERENCED DOCUMENTS       4         2.1       Government documents       4         2.2       Other publications       7         3.1       Introduction       7         3.2.1       Asynchronous data transmission channel       7         3.2.2       Bade       7         3.2.3       Baud       7         3.2.4       Bit       7         3.2.5       Bit, erron rate (BER)       8         3.2.6       Bit, parallel       8         3.2.7       Bit, farming       8         3.2.8       Bit, parallel       8         3.2.9       Bit, service       8         3.2.10       Bick, erroneous       8         3.2.11       Block, erroneous       8         3.2.12       Block, erroneous       8         3.2.13       Channel       8         3.2.14 <t< td=""><td></td><td>1.1</td><td>Purpose</td><td>1</td></t<>                                                                                             |           | 1.1    | Purpose                                    | 1      |

| 1.3.1       Type B - Naval tactical data system NTDS       1         rast (ML-STD-1397)       1.3.2       Multiplex Serial (ML-STD-1553)       1         1.4       Implementation       2         1.5       Specific interface formatting requirements       2         2.       REFFRENCED DOCUMENTS       4         2.1       Government documents       4         2.2       Other publications       7         3.1       Introduction       7         3.2       Definitions       7         3.2.1       Asynchronous data transmission channel       7         3.2.2       Back-to-back (loop) bit error rate (BER)       7         3.2.3       Baud       7         3.2.4       Bit       7         3.2.5       Bit, erroneous       8         3.2.6       Bit, parallel       8         3.2.7       Bit(s, erroneous       8         3.2.8       Bit, parallel       8         3.2.9       Bit, service       8         3.2.10       Bit, service       8         3.2.11       Block       9         3.2.12       Block       9         3.2.13       Charmel       9         <                                                                                                                                                   |           | 1.2    |                                            | 1      |

| fait (MIL-STD-1397)1.3.2Multiplex Serial (MIL-STD-1553)11.4Implementation21.5Specific interface formatting requirements22.REFERENCED DOCUMENTS42.1Government documents63.2Other publications63.1Intraduction73.2.2Definitions73.2.1Asynchronous data transmission channel73.2.2Back-to-back (loop) bit error rate (BER)73.2.3Baud73.2.4Bit73.2.5Bit, erroneous83.2.6Bit, service83.2.7Bit(s), framing83.2.8Bit, parallel83.2.9Bit, service83.2.10Bit, service83.2.11Block, erroneous83.2.12Block, erroneous83.2.13Channel83.2.14Code83.2.15Commat/Response data bus93.2.16Commat/Response data bus93.2.17Ontroller93.2.18Data processing system (DPS)93.2.29Inpriver (line driver)103.2.21Driver (line driver)103.2.22Duplex channel (EF) data113.2.33Isochronosus data transmission113.2.44Code113.2.15Commat/Response data bus93.2.16Commat/Response data bus9 <td></td> <td></td> <td>Data interface classification</td> <td>1</td>                                                                                                                                                                                                                                                                                               |           |        | Data interface classification              | 1      |

| 1.3.2       Multiplex Serial (ML-STD-1553)       1         1.4       Implementation       2         1.5       Specific interface formatting requirements       2         2.       REFERENCED DOCUMENTS       4         2.1       Government documents       4         2.2       Other publications       6         3.       DEFINITIONS       7         3.1       Introduction       7         3.2       Definitions       7         3.2.1       Asynchronous data transmission channel       7         3.2.2       Back-to-back (loop) bit error rate (BER)       7         3.2.3       Baud       7         3.2.4       Bit, erroneous       8         3.2.5       Bit, erroneous       8         3.2.6       Bit, parallel       8         3.2.7       Bits, erroneous       8         3.2.10       Bit, service       8         3.2.11       Block       8         3.2.12       Block, erroneous       8         3.2.13       Channel       9         3.2.14       Code       9         3.2.15       Commad/Response data bus       9         3.2.16       Compatibility </td <td></td> <td>1.3.1</td> <td></td> <td>1</td>                                                                                                      |           | 1.3.1  |                                            | 1      |

| 1.4       Implementation       2         1.5       Specific interface formatting requirements       2         2.1       Government documents       4         2.2       Other publications       6         3.       DEFINITIONS       7         3.1       Introduction       7         3.2       Definitions       7         3.2.1       Asynchronous data transmission channel       7         3.2.2       Back-to-back (loop) bit error rate (BER)       7         3.2.3       Baud       7         3.2.4       Bit       7         3.2.5       Bit, erroneous       8         3.2.6       Bit, error rate (BER)       8         3.2.7       Bit(s), framing       8         3.2.8       Bit, parallel       8         3.2.9       Bit, service       8         3.2.11       Block       8         3.2.212       Block, erroneous       8         3.2.13       Channel       9         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Command/Response data bus       9         3.2.19       Detected BER       <                                                                                                                                                            |           | 1.3.2  |                                            | 1      |

| 2.       REFERENCED DOCUMENTS       4         2.1       GOVERNENT documents       4         2.2       Other publications       6         3.       DEFINITIONS       7         3.1       Introduction       7         3.2       Definitions       7         3.2.1       Asynchronous data transmission channel       7         3.2.2       Back-to-back (loop) bit error rate (BER)       7         3.2.3       Baud       7         3.2.4       Bit       7         3.2.5       Bit, erroneous       8         3.2.6       Bit error rate (BER)       8         3.2.7       Bit(s), framing       8         3.2.8       Bit, parily       8         3.2.9       Bit, parily       8         3.2.10       Bick, erroneous       8         3.2.11       Block       8         3.2.12       Block, erroneous       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9 <td></td> <td>1.4</td> <td></td> <td></td>                                                                                                                                   |           | 1.4    |                                            |        |

| 2.       REFERENCED DOCUMENTS       4         2.1       GOVERNENT documents       4         2.2       Other publications       6         3.       DEFINITIONS       7         3.1       Introduction       7         3.2       Definitions       7         3.2.1       Asynchronous data transmission channel       7         3.2.2       Back-to-back (loop) bit error rate (BER)       7         3.2.3       Baud       7         3.2.4       Bit       7         3.2.5       Bit, erroneous       8         3.2.6       Bit error rate (BER)       8         3.2.7       Bit(s), framing       8         3.2.8       Bit, parily       8         3.2.9       Bit, parily       8         3.2.10       Bick, erroneous       8         3.2.11       Block       8         3.2.12       Block, erroneous       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9 <td></td> <td>1.5</td> <td>Specific interface formatting requirements</td> <td>2</td>                                                                                        |           | 1.5    | Specific interface formatting requirements | 2      |

| 2.2Other publications63.DEFINITIONS73.1Introduction73.2Definitions73.2.1Asynchronous data transmission channel73.2.2Back-to-back (loop) bit error rate (BER)73.2.3Baud73.2.4Bit, erroneous83.2.5Bit, erroneous83.2.6Bit, erroneous83.2.7Bit(s), framing83.2.8Bit, parallel83.2.9Bit, service83.2.11Block, erroneous83.2.12Block, erroneous83.2.13Channel83.2.14Code93.2.15Command/Response data bus93.2.16Compatibility93.2.17Controller93.2.18Data processing system (DPS)93.2.20Device (input-output (1/0)103.2.21Driver (line driver)103.2.22Duplex channel (full duplex channel)103.2.23Effective speed of transmission103.2.24Error-detecting and feedback system103.2.25External function (Ef) data113.2.26Hol2113.2.27High duplex channel113.2.20Input113.2.21Driver (line driver)103.2.22Duplex channel113.2.23Effective speed of transmission103.2.24Err                                                                                                                                                                                                                                                                                                                                                                    |           |        | REFERENCED DOCUMENTS                       | 4      |

| 3.         DEFINITIONS         7           3.1         Introduction         7           3.2         Definitions         7           3.2.1         Asynchronous data transmission channel         7           3.2.2         Back-to-back (loop) bit error rate (BER)         7           3.2.3         Baud         7           3.2.4         Bit         7           3.2.5         Bit, erroneous         8           3.2.6         Bit error rate (BER)         8           3.2.7         Bit(s), framing         8           3.2.8         Bit, parity         8           3.2.9         Bit, parity         8           3.2.10         Bit, service         8           3.2.11         Block         8           3.2.12         Block, erroneous         8           3.2.13         Channel         8           3.2.14         Code         9           3.2.15         Command/Response data bus         9           3.2.16         Compatibility         9           3.2.17         Controller         9           3.2.20         Device, input-output (I/0)         10           3.2.21         Driver (line driver)                                                                                                            |           |        |                                            |        |

| 3.1       Introduction       7         3.2       Definitions       7         3.2.1       Asynchronous data transmission channel       7         3.2.2       Back-to-back (loop) bit error rate (BER)       7         3.2.3       Baud       7         3.2.4       Bit       7         3.2.5       Bit, erroneous       8         3.2.6       Bit error rate (BER)       8         3.2.7       Bit(s), framing       8         3.2.8       Bit, parallel       8         3.2.9       Bit, parity       8         3.2.10       Bit, service       8         3.2.11       Block, erroneous       8         3.2.12       Block, erroneous       8         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Command/Response data bus       9         3.2.17       Controller       9         3.2.20       Device, input-output (I/O)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23 <td< td=""><td></td><td>2.2</td><td>Other publications</td><td>6</td></td<>                                                                                 |           | 2.2    | Other publications                         | 6      |

| 3.2         Definitions           3.2.1         Asynchronous data transmission channel         7           3.2.2         Back-to-back (loop) bit error rate (BER)         7           3.2.3         Baud         7           3.2.4         Bit         7           3.2.5         Bit, erroneous         8           3.2.6         Bit error rate (BER)         8           3.2.7         Bit(s), framing         8           3.2.8         Bit, parallel         8           3.2.9         Bit, parallel         8           3.2.10         Bit, service         8           3.2.11         Block         8           3.2.12         Block, erroneous         8           3.2.14         Code         9           3.2.15         Command/Response data bus         9           3.2.16         Demand/Response data bus         9           3.2.17         Controller         9           3.2.18         Data processing system (DPS)         9           3.2.20         Device, input-output (I/0)         10           3.2.21         Driver (line driver)         10           3.2.22         Duplex channel (full duplex channel)         11                                                                                      |           |        | DEFINITIONS                                |        |

| 3.2.1       Asynchronous data transmission channel       7         3.2.2       Back-to-back (loop) bit error rate (BER)       7         3.2.3       Baud       7         3.2.4       Bit       7         3.2.5       Bit, erron rate (BER)       8         3.2.6       Bit error rate (BER)       8         3.2.7       Bit(s), framing       8         3.2.8       Bit, parity       8         3.2.9       Bit, service       6         3.2.10       Bit, service       8         3.2.11       Block       8         3.2.12       Block, erroneous       8         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Command/Response data bus       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.20       Device, input-output (I/0)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (Full duplex channel)       10         3.2.23       Effective speed of transmission       10                                                                                                                                      |           |        | Introduction                               | 7      |

| 3.2.2       Back-to-back (loop) bit error rate (BER)       7         3.2.3       Baud       7         3.2.4       Bit       7         3.2.5       Bit, erroneous       8         3.2.6       Bit error rate (BER)       8         3.2.7       Bit(s), framing       8         3.2.8       Bit, parallel       8         3.2.9       Bit, service       6         3.2.10       Bit, service       8         3.2.11       Block       8         3.2.12       Block, erroneous       8         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.20       Device, input-output (1/0)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3                                                                                                                                              |           |        |                                            | _      |

| 3.2.3       Baud       7         3.2.4       Bit       7         3.2.5       Bit, erroneous       8         3.2.6       Bit, error rate (BER)       8         3.2.7       Bit(s), framing       8         3.2.8       Bit, parallel       8         3.2.9       Bit, parity       8         3.2.10       Bit, service       8         3.2.11       Block, erroneous       8         3.2.12       Block, erroneous       8         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.20       Device, input-output (I/O)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3                                                                                                                                              |           | 3.2.1  |                                            |        |

| 3.2.4       Bit       7         3.2.5       Bit, erroneous       8         3.2.6       Bit, erron rate (BER)       8         3.2.7       Bit(s), framing       8         3.2.8       Bit, parallel       8         3.2.9       Bit, service       8         3.2.10       Bit, service       8         3.2.11       Block       8         3.2.12       Block, erroneous       8         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.20       Device, input-output (I/0)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       H0CS       11         3.2.27 <td></td> <td></td> <td></td> <td></td>                                                                                                         |           |        |                                            |        |

| 3.2.5       Bit, erroneous       8         3.2.6       Bit error rate (BER)       8         3.2.7       Bit(s), framing       8         3.2.8       Bit, parallel       8         3.2.9       Bit, parallel       8         3.2.10       Bit, service       8         3.2.11       Block       8         3.2.12       Block, erroneous       8         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Command/Response data bus       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.19       Detected BER       9         3.2.20       Device, input-output (I/0)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       HoCS       11 <t< td=""><td></td><td></td><td></td><td></td></t<>                                                                                      |           |        |                                            |        |

| 3.2.6       Bit error rate (BER)       8         3.2.7       Bit(s), framing       8         3.2.8       Bit, parity       8         3.2.9       Bit, parity       8         3.2.10       Bit, service       8         3.2.11       Block       8         3.2.12       Block, erroneous       8         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.20       Device, input-output (I/0)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       HoCS       11         3.2.28       Hoplex channel       11                                                                                                                                                       |           |        |                                            |        |

| 3.2.8       Bit, parily       8         3.2.9       Bit, parity       8         3.2.10       Bit, service       6         3.2.11       Block       8         3.2.12       Block, erroneous       8         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.19       Detected BER       9         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.33 </td <td></td> <td></td> <td></td> <td>8</td>                                                                                                  |           |        |                                            | 8      |

| 3.2.8       Bit, parily       8         3.2.9       Bit, parity       8         3.2.10       Bit, service       6         3.2.11       Block       8         3.2.12       Block, erroneous       8         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.19       Detected BER       9         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.33 </td <td></td> <td></td> <td></td> <td>8</td>                                                                                                  |           |        |                                            | 8      |

| 3.2.11       Block       £         3.2.12       Block, erroneous       £         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.19       Detected BER       9         3.2.20       Device, input-output (I/0)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.32       Interval, unit       11                                                                                                                                               |           | 3.2.7  |                                            | C<br>B |

| 3.2.11       Block       £         3.2.12       Block, erroneous       £         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.19       Detected BER       9         3.2.20       Device, input-output (I/0)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.32       Interval, unit       11                                                                                                                                               |           |        |                                            | р<br>С |

| 3.2.11       Block       £         3.2.12       Block, erroneous       £         3.2.13       Channel       8         3.2.14       Code       9         3.2.15       Command/Response data bus       9         3.2.16       Compatibility       9         3.2.17       Controller       9         3.2.18       Data processing system (DPS)       9         3.2.19       Detected BER       9         3.2.20       Device, input-output (I/0)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.32       Interval, unit       11                                                                                                                                               |           |        |                                            | 5<br>8 |

| 3.2.19       Detected BER       9         3.2.20       Device, input-output (I/O)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.20       Interval, significant       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                             |           |        |                                            | e<br>R |

| 3.2.19       Detected BER       9         3.2.20       Device, input-output (I/O)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.20       Interval, significant       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                             |           |        |                                            | 8      |

| 3.2.19       Detected BER       9         3.2.20       Device, input-output (I/O)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.20       Interval, significant       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                             |           |        |                                            | 8      |

| 3.2.19       Detected BER       9         3.2.20       Device, input-output (I/O)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.20       Interval, significant       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                             |           |        |                                            | 9      |

| 3.2.19       Detected BER       9         3.2.20       Device, input-output (I/O)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.20       Interval, significant       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                             |           |        |                                            | 9      |

| 3.2.19       Detected BER       9         3.2.20       Device, input-output (I/O)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.20       Interval, significant       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                             |           |        |                                            | 9      |

| 3.2.19       Detected BER       9         3.2.20       Device, input-output (I/O)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.20       Interval, significant       11         3.2.30       Instants, significant       11         3.2.31       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                             |           |        |                                            | 9      |

| 3.2.19       Detected BER       9         3.2.20       Device, input-output (I/0)       10         3.2.21       Driver (line driver)       10         3.2.22       Duplex channel (full duplex channel)       10         3.2.23       Effective speed of transmission       10         3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.30       Instants, significant       11         3.2.31       Interval, significant       11         3.2.32       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                             |           | 3.2.18 | Data processing system (DPS)               | 9      |

| 3.2.21Driver (line driver)103.2.22Duplex channel (full duplex channel)103.2.23Effective speed of transmission103.2.24Error-detecting and feedback system103.2.25External function (EF) data113.2.26Half duplex channel113.2.28HOCS113.2.29Input113.2.30Instants, significant113.2.31Interval, significant113.2.32Low state123.2.34Low state123.2.35Manchester II, biphase level123.2.37Multiplex12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |        |                                            |        |

| 3.2.22Duplex channel (full duplex channel)103.2.23Effective speed of transmission103.2.24Error-detecting and feedback system103.2.25External function (EF) data113.2.26Half duplex channel113.2.27High-state113.2.28HOCS113.2.29Input113.2.30Instants, significant113.2.31Interval, significant113.2.32Interval, unit113.2.33Isochronous data transmission123.2.34Low state123.2.35Manchester II, biphase level123.2.37Multiplex12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |        |                                            |        |

| 3.2.23Effective speed of transmission103.2.24Error-detecting and feedback system103.2.25External function (EF) data113.2.26Half duplex channel113.2.27High-state113.2.28HOCS113.2.29Input113.2.30Instants, significant113.2.31Interval, significant113.2.32Interval, unit113.2.33Isochronous data transmission123.2.34Low state123.2.35Manchester II, biphase level123.2.36Message123.2.37Multiplex12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |        |                                            |        |

| 3.2.24       Error-detecting and feedback system       10         3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.30       Instants, significant       11         3.2.31       Interval, significant       11         3.2.32       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.36       Message       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |        |                                            |        |

| 3.2.25       External function (EF) data       11         3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.30       Instants, significant       11         3.2.31       Interval, significant       11         3.2.32       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.36       Message       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |        |                                            |        |

| 3.2.26       Half duplex channel       11         3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.30       Instants, significant       11         3.2.31       Interval, significant       11         3.2.32       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.36       Message       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |        |                                            |        |

| 3.2.27       High-state       11         3.2.28       HOCS       11         3.2.29       Input       11         3.2.30       Instants, significant       11         3.2.31       Interval, significant       11         3.2.32       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.36       Message       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |        |                                            |        |

| 3.2.28       HOČS       11         3.2.29       Input       11         3.2.30       Instants, significant       11         3.2.31       Interval, significant       11         3.2.32       Interval, unit       11         3.2.33       Isochronous data transmission       12         3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.36       Message       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | 3.2.26 |                                            |        |

| 3.2.29Input113.2.30Instants, significant113.2.31Interval, significant113.2.32Interval, unit113.2.33Isochronous data transmission123.2.34Low state123.2.35Manchester II, biphase level123.2.36Message123.2.37Multiplex12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |        |                                            |        |

| 3.2.30Instants, significant113.2.31Interval, significant113.2.32Interval, unit113.2.33Isochronous data transmission123.2.34Low state123.2.35Manchester II, biphase level123.2.36Message123.2.37Multiplex12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |        |                                            |        |

| 3.2.31Interval, significant113.2.32Interval, unit113.2.33Isochronous data transmission123.2.34Low state123.2.35Manchester II, biphase level123.2.36Message123.2.37Multiplex12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |        |                                            |        |

| 3.2.32Interval, unit113.2.33Isochronous data transmission123.2.34Low state123.2.35Manchester II, biphase level123.2.36Message123.2.37Multiplex12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |        |                                            |        |

| 3.2.33Isochronous data transmission123.2.34Low state123.2.35Manchester II, biphase level123.2.36Message123.2.37Multiplex12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |        |                                            |        |

| 3.2.34       Low state       12         3.2.35       Manchester II, biphase level       12         3.2.36       Message       12         3.2.37       Multiplex       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |        |                                            |        |

| 3.2.35Manchester II, biphase level123.2.36Message123.2.37Multiplex12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |        |                                            |        |

| 3.2.36 Message 12<br>3.2.37 Multiplex 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |        |                                            |        |

| 3.2.37 Multiplex 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |        |                                            |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | 3.2.37 |                                            |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |        |                                            |        |

Page

### CONTENTS - Continued

| Paragraph |

|-----------|

|-----------|

}

~\_\_\_

~---

I

~

| 3.2.39NTDS3.2.40One-Way Channel BER3.2.41One way only (unidirectional3.2.42Output                                                                                                                                                                                                                                                                                                                                                                                         | 13<br>13<br>) channels<br>13<br>14<br>14                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 3.2.42Dutput3.2.43PCM multiplex system3.2.44Pulse code modulation (PCM)3.2.45Rate, data signaling3.2.46Remote multiplexer (RM)3.2.47Remote terminal (RT)3.2.48Signal3.2.49Signal conversion equipment3.2.50Signal lelement3.2.52Signal level3.2.53Signal parameter3.2.54Signal transition3.2.55Start-stop data transmission3.2.56Synchronous data transmission3.2.58Undetected BER3.2.59Word                                                                              | 14<br>14<br>14<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15                                |

| 4.GENERAL REQUIREMENTS4.1Introduction4.2Standard bus interface system4.3C/R buses4.3.1Data bus operation4.3.2Information transfer modes4.3.3Modulation rate4.3.4RTs4.3.5.1Non-SDMS facilities4.3.5.2SDMS equipped platforms                                                                                                                                                                                                                                               | n 17<br>17<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>20<br>20<br>20                              |

| 5. DETAILED REQUIREMENTS<br>5.1 Functional requirements, star                                                                                                                                                                                                                                                                                                                                                                                                             | ndard 24                                                                                                  |

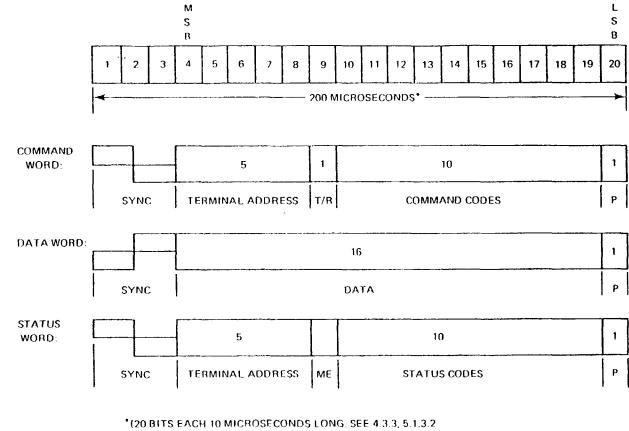

| bus system5.1.1Bus system interface for the5.1.2Bus selection5.1.3Detailed C/R buses requirement5.1.3.1Message formats5.1.3.1.1Controller to RT transfers5.1.3.1.2RT to controller transfers5.1.3.1.3Data form5.1.3.1.4Bit count5.1.3.2Word formats on the bus5.1.3.2.1Word size5.1.3.2.2Command word5.1.3.2.2.1Command sync5.1.3.2.2.2Transmit or receive or both formats5.1.3.2.2.3Transmit or receive or both formats5.1.3.2.2.4Command codes5.1.3.2.2.5Command parity | HOCS DPS 24<br>24<br>nts 24<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25 |

.

---- --- ---

MIL-STD-2117 (EC) 27 February 1981

### CONTENTS - Continued

Paragraph

|                        |                                              | Page     |

|------------------------|----------------------------------------------|----------|

| 5.1.3.2.3              | Data word                                    | 28       |

| 5.1.3.2.3.1            | Data sync                                    | 28       |

| 5.1.3.2.3.2            | Data                                         | 28       |

| 5.1.3.2.3.3            | Data parity                                  | 28       |

| 5.1.3.2.4              | Status word                                  | 28       |

| 5.1.3.2.4.1            | Status sync                                  | 28       |

| 5.1.3.2.4.2            | Status RT address                            | 28       |

| 5.1.3.2.4.3            | Message error                                | 28       |

| 5.1.3.2.4.4            | Status codes                                 | 29       |

| 5.1.3.2.4.5            | Status parity                                | 29       |

| 5.1.4                  | C/R bus to RT interface                      | 29       |

| 5.2                    | Electrical requirements, standard bus        | 29       |

| 5.2.1                  | Bus controller                               | 29       |

| 5.2.2                  | C/R bus media                                | 31       |

| 5.2.2.1                | Transmission media                           | 31       |

| 5.2.2.2                | Terminating impedance                        | 31       |

| 5.2.2.3                | Signal characteristics                       | 31       |

| 5.2.2.3.1<br>5.2.2.3.2 | System clock, distribution and utilization   | 31       |

| 5.2.2.3.3              | Receive clock                                | 32       |

| 5.2.2.3.4              | Transmit clock                               | 32       |

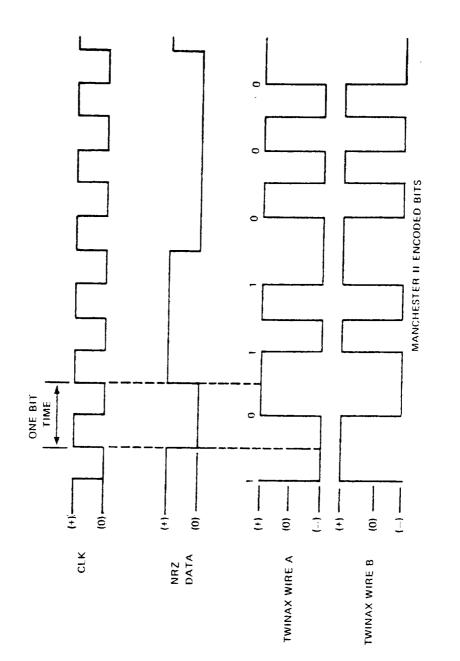

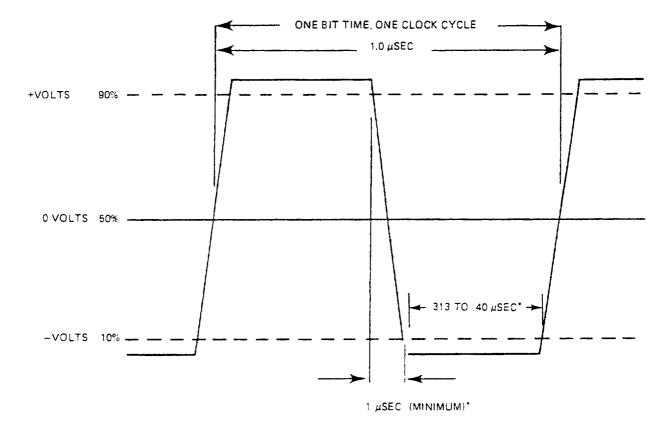

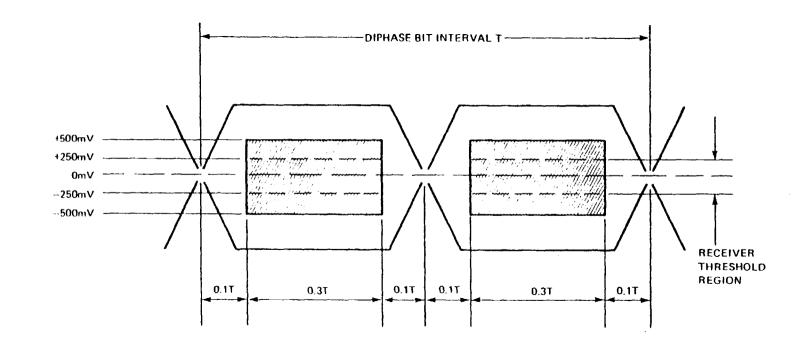

| 5.2.2.3.5              | Data coding<br>Bus signaling                 | 34       |

| 5.2.2.3.6              | Sync                                         | 34       |

| 5.2.2.3.7              | Controller output levels                     | 34<br>34 |

| 5.2.2.3.8              | RT output waveform                           | 34<br>34 |

| 5.2.2.3.9              | RT output noise                              | 34       |

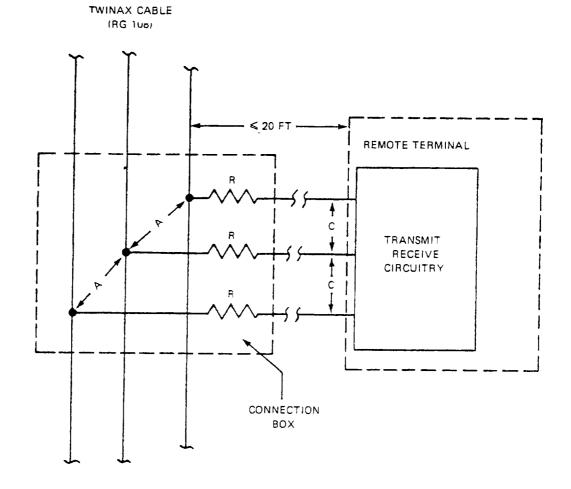

| 5.2.3                  | Interface between C/R bus and RT             | 36       |

| 5.2.3.1                | Bus AC coupling technique                    | 36       |

| 5.2.3.2                | Bus fault isolation                          | 38       |

| 5.2.3.3                | Typical signal characteristics between       | 38       |

| 0121010                | the bus and RT                               | 50       |

| 5.2.3.3.1              | Bus interface                                | 38       |

| 5.2.3.3.2              | Serial digital signal characteristics        | 38       |

| 5.2.3.4                | RT characteristics                           | 39       |

| 5.2.3.4.1              | RT input characteristics                     | 39       |

| 5.2.3.4.1.1            | Input waveform compatibility                 | 39       |

| 5.2.3.4.1.2            | Common mode rejections                       | 41       |

| 5.2.3.4.1.3            | Input impedance                              | 41       |

| 5.2.3.4.2              | Data validation                              | 41       |

| 5.2.3.4.3              | RT output characteristics                    | 42       |

| 5.2.3.5                | Terminal operation                           | 42       |

| 5.2.3.5.1              | Response time                                | 42       |

| 5.2.3.5.2              | Terminal fail-safe operation                 | 42       |

| 5.2.3.6                | Environmental considerations                 | 42       |

| 5.2.3.6.1              | Electromagnetic emissions and susceptibility | 43       |

| 5.2.3.6.2              | BER                                          | 43       |

| 5.2.3.6.3              | Incomplete message rate                      | 43       |

| 5.2.3.6.4              | Test conditions                              | 44       |

| 5.3                    | Physical requirements, standard bus          | 44       |

| 5.3.1                  | Cabling, stand-alone bus controller          | 44       |

|                        | to DPS                                       |          |

| 5.3.1.1                | Cable                                        | 44       |

| 5.3.1.2                | Cable connectors                             | 45       |

|                        |                                              |          |

- - - - - - - -

Page

### CONTENTS - Continued

| Paragraph     | 5.3.1.3 | Connector pin assignments               | 45 |

|---------------|---------|-----------------------------------------|----|

| r ur ugr upri | 5.3.1.4 | Connector keying                        | 45 |

|               | 5.3.2   | The cables and connectors of C/R bus    | 45 |

|               | 5.3.2.1 | Cable                                   | 45 |

|               |         |                                         | 45 |

|               | 5.3.2.2 | Cable coupling                          | 46 |

|               | 5.3.2.3 | Cable connectors                        | 40 |

|               |         | FIGURES                                 |    |

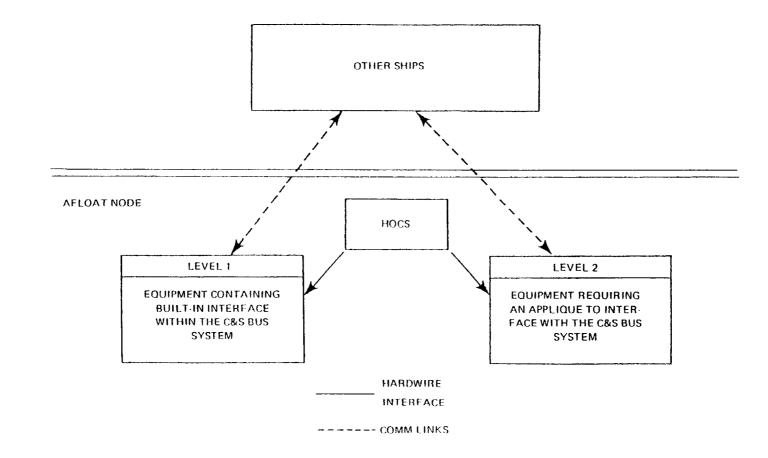

| Figure        | 1       | NTS control and status interface levels | 3  |

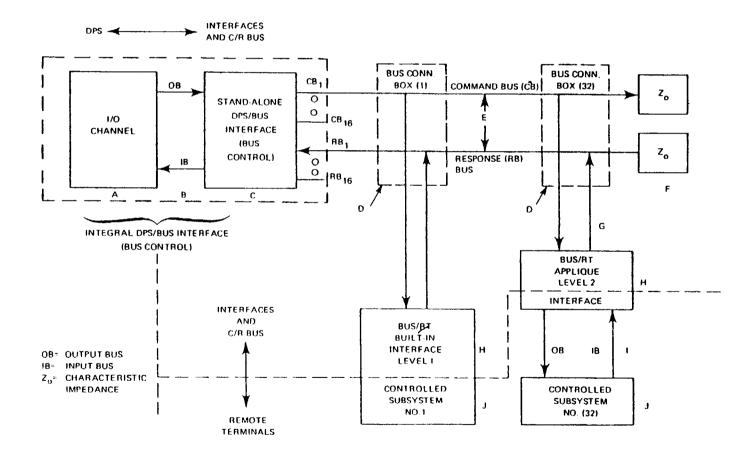

|               | 2       | Block diagram of interfaces and C/R bus | 18 |

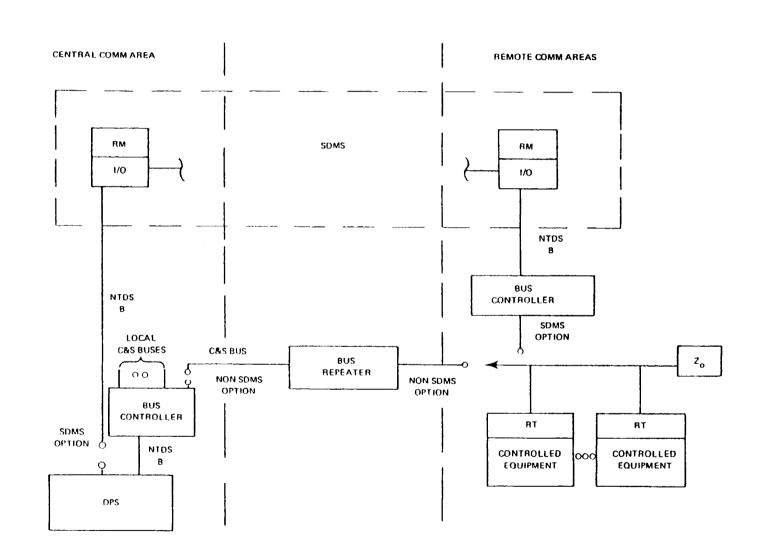

|               | 3       | Extended bus options, block diagram     | 21 |

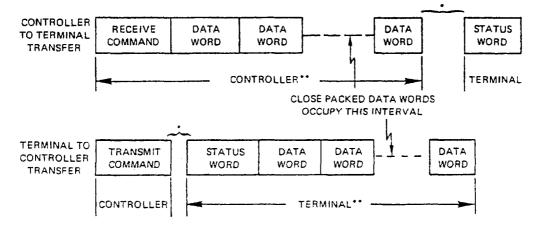

|               | 5       | NTS interface standard message formats  | 22 |

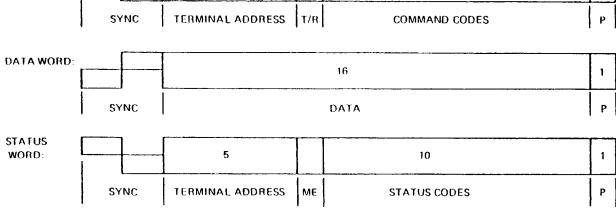

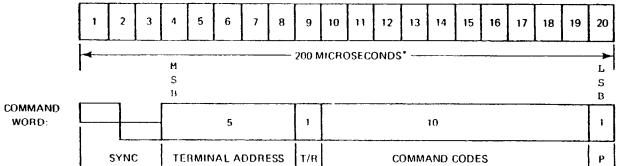

|               | 4<br>F  | Word formats on the NTS standard bus    | 26 |

|               | 5       |                                         | 27 |

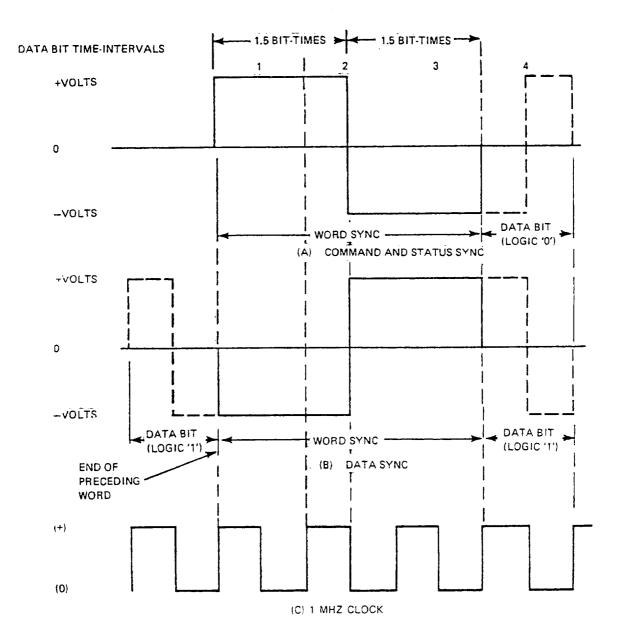

|               | 6       | Bus-signal waveforms for sychronization | 21 |

| 7    | Data encoding                            |    |

|------|------------------------------------------|----|

| 8    | Data bus interface (transmit or receive) | 35 |

| 9    | Output waveform (logic one)              | 37 |

| 10   | Input signal minimum requirements        | 41 |

| 10.1 | Word Forms on the Standard Bus           | 49 |

| 10.2 | Sample Command Word Bit Assignment       | 50 |

| 10.3 | Sample Status Word Bit Assignment        | 52 |

|      |                                          |    |

### TAELES

Table

I

)

I/O cable-nin assignment (central processor 47/48

interface with bus controller)

### APPENDIX

.

.

### 1. SCOPE

1.1 <u>Purpose</u>. The purpose of this document is to define bus interface standards for the automatic interchange of control and status information for shipboard use.

1.2 <u>Scope</u>. This standard establishes the physical, functional, electrical and optical interface requirements for the automatic interchange of control and status information for shipboard use.

- a. Where supervision or signaling or supervision and signaling (S/S) information is transferred (in-band or out of band) on a traffic circuit, the traffic standards shall govern and the S/S information shall be retrieved (and conditioned as necessary) from the control and status (C&S) word by applique items (or circuitry) not presently within the scope of this document.

- b. This document is not concerned with operational traffic signal samples utilized with communication performance assessment (CPA). However, status decisions provided by built-in test equipment (BITE) concerning the quality of these traffic signals shall be considered as C&S information, and is within the scope of this document.

- c. Semi-automatic (and remote) control schemes are currently in extensive use aboard U.S. Navy ships. Existing Naval telecommunication system (NTS) ships equipped with these semi-automatic schemes may require appliques to provide adaptation to the standard defined herein.