NOT MEASUREMENT SENSITIVE

MIL-STD-1378E <u>21 APRIL 1989</u> SUPERSEDING MIL-STD-1378D 16 MAY 1986 (SEE 6.6)

# MILITARY STANDARD

# REQUIREMENTS FOR EMPLOYING STANDARD ELECTRONIC MODULES

AMSC N/A FSC 5963 DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

#### FOREWORD

1. This military standard is approved for use by all Departments and Agencies of the Department of Defense.

2. Beneficial comments (recommendations, additions, deletions) and any pertinent data which may be of use in improving this document should be addressed to: Commander Naval Sea Systems Command, SEA 55Z3, Department of the Navy, Washington, DC 20362-5101 by using the self-addressed Standardization Document Improvement Proposal (DD Form 1426) appearing at the end of this document or by letter. ٠

## MIL-STD-1378E

## CONTENTS

| PARAGRAPH |                                      | PAGE |

|-----------|--------------------------------------|------|

| 1.        | SCOPE                                | 1    |

| 1.1       | Scope                                | 1    |

| 1.2       | Purpose                              | 1    |

| 2.        | APPLICABLE DOCUMENTS                 | 2    |

| 2.1       | Government documents                 | 2    |

| 2.1.1     | Specifications and standards         | 2    |

| 2.2       | Order of precedence                  | .3   |

| 3.        | DEFINITIONS                          | 4    |

| 3.1       | Terms and definitions                | 4    |

| 3.1.1     | SHARP                                | 4    |

| 3.1.2     | SEM                                  | 4    |

| 3.1.3     | Equipment contractor (EC)            | 4    |

| 3.1.4     | SEM quality assurance (SEM-QAA)      | 4    |

| 3.1.5     | SEM design review activity (SEM-DRA) | 4    |

| 3.1.6     | Government program manager (PM)      | 4    |

| 3.1.7     | Design approval request (DAR)        | 4    |

| 3.1.8     | Functional specification.            | 4    |

| 3.1.9     | Design disclosure to SEM-QAA         | 5    |

| 3.1.10    | SEM standard                         | 5    |

| 3.1.11    | Candidate SEM standard               | 5    |

| 3.1.12    | SEM special                          | 5    |

|           |                                      | _    |

| 4.        | GENERAL REQUIREMENTS                 | 6    |

| 4.1       | General                              | 6    |

| 4.2       | Priority of implementation           | 6    |

| 4.2.1     | Existing SEM standards               | 6    |

| 4.2.2     | In-process SEM standards             | 6    |

| 4.2.3     | Existing SEM specials                | 5    |

| 4.2.4     | New SEM designs                      | 6    |

| 4.2.4.1   | Circuit functional requirements      | 7    |

| 4.2.4.2   | System packaging constraints         | 7    |

| 4.2.4.3   | System environmental constraints     | 7    |

| 4.2.4.4   | Cost effectiveness requirements      | 7    |

| 4.3       | Design requirements for new SEM      | 7    |

## CONTENTS - Continued

| PARAGRAPH |                                                 | <u>PAGE</u> |

|-----------|-------------------------------------------------|-------------|

| 4.3.1     | Design objectives                               | 7           |

| 4.3.1.1   | Maximum flexibility                             | 7           |

| 4.3.1.2   | Proprietary parts or processes                  | 8           |

| 4.3.1.3   | Repairability                                   | 8           |

| 5.        | DETAILED REQUIREMENTS                           | 9           |

| 5.1       | Purpose                                         | 9           |

| 5.2       | SEM standard requirements                       | 9           |

| 5.2.1     | SEM standard design requirements                | 9           |

| 5.2.2     | SEM standard quality assurance requirements     | 9           |

| 5.2.3     | SEM standard documentation requirements         | 9           |

| 5.2.4     | Nonstandard parts waiver                        | 9           |

| 5.3       | Candidate SEM standard requirements             | 9           |

| 5.3.1     | Candidate SEM standard design requirements.     | 10          |

| 5.3.2     | Candidate SEM standard quality assurance        |             |

|           | requirements                                    | 10          |

| 5.3.3     | Candidate SEM standard documentation            |             |

|           | requirements                                    | 10          |

| 5.3.4     | Nonstandard parts approval                      | 10          |

| 5.4       | SEM special requirements                        | 10          |

| 5.4.1     | SEM special design requirements                 | 10          |

| 5.4.2     | SEM special quality assurance requirements      | 10          |

| 5.4.3     | SEM special documentation requirements          | 11          |

| 5.4.4     | Nonstandard parts approval                      | 11          |

| 5.5       | Implementation procedures                       | 11          |

| 5.6       | Submission of design approval requests          |             |

|           | (Block 1)                                       | 11          |

| 5.6.1     | DAR action (Block 2)                            | 11          |

| 5.6.1.1   | PM review (Block 3)                             | 12          |

| 5.6.1.2   | Status notification                             | 12          |

| 5.7       | Submission of module descriptions (Block 4)     | 12          |

| 5.8       | Preparation of detail specification draft       |             |

|           | (Block 4)                                       | 12          |

| 5.9       | Preparation of preliminary detail specification |             |

|           | (Block 7)                                       | 12          |

| 5.9.1     | SEM correlation (Block 9)                       | 13          |

| 5.10      | SEM initial qualification submission (Block 13) | 13          |

| 5.10.1    | Notification for initial qualification          | 13          |

.

٠

## MIL-STD-1378E

.

## CONTENTS - Continued

|         | PARAGRAPH |                                                    | PAGE |

|---------|-----------|----------------------------------------------------|------|

|         | 5.10.2    | Completion of initial qualification (Block 14).    | 13   |

|         | 5.10.3    | Retention of module samples                        | 13   |

|         | 5,10.4    | Repository for final detail specification          |      |

|         |           | (Block 11)                                         | 13   |

|         | 5.10.5    | Initial qualification rejection                    | 14   |

|         | 5.10.6    | Resubmission                                       | 14   |

|         | 5.11      | Contract data requirements                         | 14   |

|         | 6.        | NOTES                                              | 15   |

|         | 6.1       | Intended use                                       | 15   |

|         | 6.2       | Issue of DODISS                                    | 15   |

|         | 6.3       | Data requirements                                  | 15   |

|         | 6.4       | Timely submission and approval                     | 16   |

|         | 6.4.1     | DAR                                                | 16   |

|         | 6.4.2     | Status                                             | 16   |

|         | 6.4.3     | Module descriptions                                | 16   |

|         | 6.5       | Subject term (keyword) listing                     | 16   |

|         | 6.6       | Changes from previous issue                        | 16   |

| FIGURES | 1.        | SEM design approval procedure                      | 17   |

|         | 2.        | Logic load circuit                                 | 60   |

|         | 3.        | Example of an input test condition test table      | 61   |

|         | 4.        | Example of an input test condition test tolerance  |      |

|         |           | table <i>.</i>                                     | 62   |

|         | 5.        | Example of an output test condition test table     | 63   |

|         | 6.        | Example of an output test condition test tolerance |      |

|         |           | table <i></i>                                      | 64   |

|         | 7.        | Example of a module functional block diagram       | 65   |

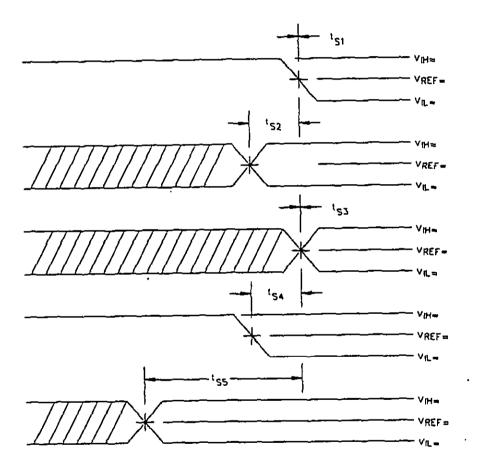

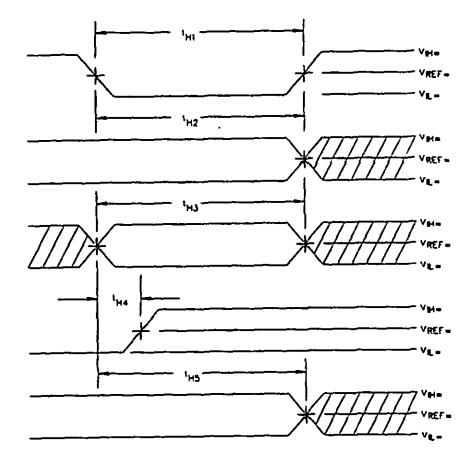

|         | 8.        | Example of input waveforms                         | 66   |

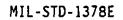

|         | 9.        | Example of output waveforms                        | 68   |

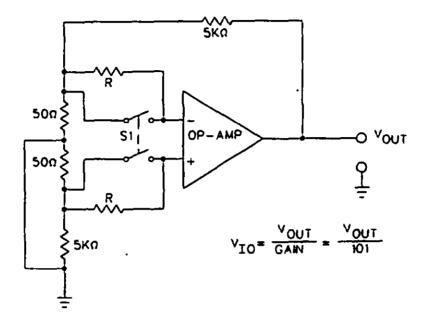

|         | 10.       | Typical operational amplifier test circuit         | 103  |

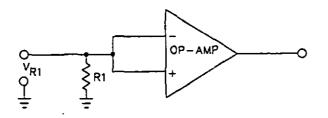

|         | 11.       | Typical I <sub>IB</sub> test circuit               | 104  |

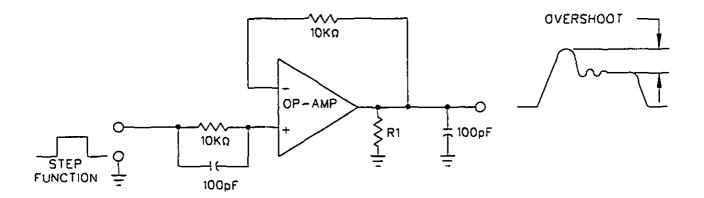

|         | 12.       | Typical phase margin test circuit                  | 104  |

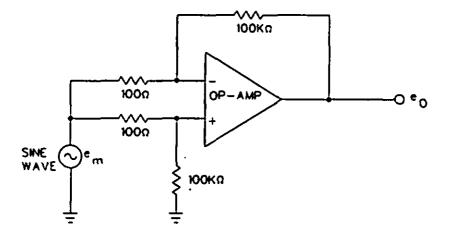

|         | 13.       | Typical CMRR test circuit                          | 105  |

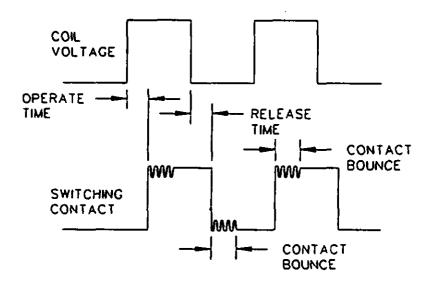

|         | 14.       | Contact switching characteristics                  | 105  |

|         | 15.       | Dynamic regulation response                        | 106  |

•

## CONTENTS - Continued

|            |    | PAGE                                                |

|------------|----|-----------------------------------------------------|

| TABLES     | I. | Functional test pattern coverage                    |

|            |    | Working voltage versus test voltage                 |

| APPENDICES | .Α | Sample standard electronic module design approval   |

|            |    | request                                             |

|            | В  | Instructions for preparing module descriptions 29   |

|            | С  | Instructions for preparing module specifications 35 |

|            | D  | Test requirements for digital modules               |

|            | Ε  | Test requirements for analog modules                |

## 1. SCOPE

1.1 <u>Scope</u>. This standard establishes the requirements for the implementation of Standard Electronic Modules (SEM) in the design and construction of selected military electronic systems. The selection of systems for which this standard will be invoked in a contract should be based upon the criteria set forth in MIL-HDBK-246.

1.2 <u>Purpose</u>. The purpose of this standard is to provide the acquisition activity with specific instructions for implementation of the Standard Electronic Modules (SEM) in order to reduce system life cycle costs. This standard also provides instructions for the preparation of a standard electronic module design approval request, instructions for preparing module descriptions, instructions for preparing module specifications, test requirements for digital modules, and test requirements for analog modules.

## 2. APPLICABLE DOCUMENTS

## 2.1 Government documents.

2.1.1 <u>Specifications and standards</u>. The following specifications and standards form a part of this standard to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DODISS) and supplement thereto, cited in the solicitation (see 6.2).

## SPECIFICATIONS

MILITARY

| MIL-E-5400  | <ul> <li>Electronic Equipment, Aerospace, General</li> <li>Specification for.</li> </ul>                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIL-E-16400 | <ul> <li>Electronic, Interior Communication and<br/>Navigation Equipment, Naval Ship and Shore,<br/>General Specification for.</li> </ul>                    |

| MIL-P-24423 | - Basic Design Requirements for Propulsion and<br>Auxiliary Control Consoles and Associated<br>Control and Instrumentation Equipment, Navy<br>Shipboard use. |

| MIL-M-28787 | <ul> <li>Modules, Standard Electronic General<br/>Specification for.</li> </ul>                                                                              |

### STANDARDS

MILITARY

| MIL-STD-965  | - | Parts Control Program.                          |

|--------------|---|-------------------------------------------------|

| MIL-STD-1331 | - | Parameters to be Controlled for the             |

|              |   | Specification of Microcircuits.                 |

| MIL-STD-1389 | - | Design Requirements for Standard Electronic     |

|              |   | Modules.                                        |

| MIL-STD-1634 | - | Module Descriptions for the Standard Electronic |

|              |   | Modules Program.                                |

(Unless otherwise indicated, copies of federal and Military specifications and standards are available from the Naval Publications and Forms Center, (ATTN: NPODS), 5801 Tabor Avenue, Philadelphia, PA 19120-5099.)

2.2 Order of precedence. In the event of a conflict between the text of this document and the references cited herein, the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. DEFINITIONS

3.1 <u>Terms and definitions</u>. The definitions of terms used in this standard shall be as specified herein and in MIL-STD-1331.

3.1.1 SHARP. Standard Hardware Acquisition and Reliability.

3.1.2 <u>SEM</u>. Standard Electronic Modules (includes all modules in the SHARP).

3.1.3 <u>Equipment contractor (EC)</u>. EC applies to both system developers and developers of electronic assemblies and subassemblies in which SEM are to be employed.

3.1.4 <u>SEM quality assurance activity (SEM-QAA)</u>. The SEM-QAA is the activity responsible for performing SEM qualification testing. (This function is performed by the Naval Weapons Support Center, Code 603, Crane, IN 47522-5060.)

3.1.5 <u>SEM design review activity (SEM-DRA)</u>. The SEM-DRA is the activity responsible for the review and approval of SEM designs. (This function is performed by the Naval Avionics Center, Code 814, 6000 E 21st Street, Indianapolis, IN 46219-2189.)

3.1.6 <u>Government program manager (PM)</u>. The PM is the Government program manager who is initiating the particular system application.

3.1.7 <u>Design approval request (DAR)</u>. DAR is data item necessary to justify a new design for a SEM. It is used to describe new SEM functions in order that they can be classified by the SEM-DRA (see 6.3).

3.1.8 <u>Functional specification</u>. A functional specification is the documentation which completely describes the form, fit, and function of a module assembly. This includes the outer module dimensions including interfaces and the precise electronic function with inputs and outputs. A functional specification also includes a complete and exhaustive series of tests to verify this function.

4

3.1.9 <u>Design disclosure to SEM-QAA</u>. A design disclosure to SEM-QAA is the documentation needed to manufacture or repair a module. This includes the component lists complete with manufacturer's part numbers, the schematic and artwork of the exact circuitry, and the necessary processes to make the assembly.

3.1.10 <u>SEM standard</u>. A SEM standard is a module for which the SEM-DRA anticipates multisystem applications (see 5.2). Attributes of SEM standard are:

- (1) The module has potential multisystem applications.

- (2) Complete documentation to SEM-QAA requirements has been prepared.

- (3) Documentation is controlled by SEM.

- (4) Complete quality assurance is held to SEM requirements.

3.1.11 <u>Candidate SEM standard</u>. A candidate SEM standard module is one for which the SEM-DRA anticipates multisystem applications but for which documentation and qualification have been deferred (see 5.3). Attributes of candidate SEM standard are:

- (1) The module has potential multisystem applications.

- (2) Complete documentation to SEM requirement unless otherwise specified by the cognizant PM.

- (3) SEM-DRA is kept updated on configuration control.

- (4) Complete quality assurance is held to SEM requirements unless otherwise specified by the cognizant PM.

3.1.12 <u>SEM special</u>. A SEM special module is one for which the SEM-DRA anticipates a limited scope of applications (intrasystem uses) (see 5.4). The attributes of SEM specials are:

- (1) Limited applications.

- (2) SEM-DRA is kept updated on configuration control unless otherwise specified by cognizant PM.

- (3) Complete documentation to SEM requirements unless otherwise specified by the cognizant PM.

- (4) Complete quality assurance is held to SEM requirements unless otherwise specified by cognizant PM.

#### 4. GENERAL REQUIREMENTS

4.1 <u>General</u>. When this standard is invoked, all electronic circuitry shall be designed in accordance with MIL-STD-1389. Any exceptions to implementation of SEM requirements must be specified in the contract. For special and candidate standard modules all documentation and hardware deliverables shall be as specified in the Contract Data Requirement List (CDRL) or line item.

4.2 <u>Priority of implementation</u>. The EC shall implement electronic circuitry requirements in accordance with the priority sequence in 4.2.1 through 4.2.4.

4.2.1 <u>Existing SEM standards</u>. The EC shall initially attempt to implement system electronic circuitry requirements with existing SEM standards as listed in MIL-STD-1634.

4.2.2 <u>In-process SEM standards</u>. The EC shall coordinate with the SEM-DRA to determine whether there are any new SEM being developed within the SEM which are not as yet included in MIL-STD-1634. In the event that there is an applicable module design whose completion schedule will not impose any scheduling incompatibility, the module shall be used in lieu of proposing the development of another new module function.

4.2.3 <u>Existing SEM specials</u>. The next order of priority in SEM implementation shall be to employ an existing SEM special module which has been fully designed to the requirements of MIL-STD-1389. Change control of SEM specials lies with the PM who originated the special module. Therefore, use of an existing SEM special will depend on whether or not the PM can arrange joint change control with the PM who originated the SEM special module. Information regarding these modules shall be obtained from the SEM-DRA. If the need and desire exists, SEM specials may be upgraded to SEM standards.

4.2.4 <u>New SEM designs</u>. New SEM designs shall be proposed by the EC only under one of the exceptions specified in 4.2.4.1 through 4.2.4.4.

4.2.4.1 <u>Circuit functional requirements</u>. New SEM designs shall be proposed when a system partitioning analysis shows that the required system function cannot be implemented and the system operating parameters cannot be achieved by utilizing existing SEM.

4.2.4.2 <u>System packaging constraints</u>. When a packaging analysis shows that the system cannot be implemented in the space available by using existing SEM, new and functionally complex SEM designs which would achieve the necessary requirements may be proposed.

4.2.4.3 <u>System environmental constraints</u>. When the environmental requirements of a system preclude the use of an otherwise functionally suitable SEM which has been developed to a less stringent SEM environmental class, a new module design shall be proposed to meet the more stringent requirement. Such a new design, however, shall be functionally . interchangeable and contact compatible with the existing module of the less stringent SEM environmental class.

4.2.4.4 <u>Cost effectiveness requirements</u>. A new module design shall be proposed in lieu of an applicable existing SEM where substantial cost savings may result. It shall be demonstrated through a detailed cost analysis that on a life cycle cost basis the use of a new SEM design is more cost effective than an existing module. This cost analysis shall directly compare the cost of implementing the required system function with an existing SEM versus the new SEM design.

4.3 <u>Design requirements for new SEM</u>. New SEM designs shall be developed in accordance with the following requirements.

4.3.1 <u>Design objectives</u>. The developer of a new SEM shall, where feasible, design the new module with the objective of its being classified as a SEM standard.

4.3.1.1 <u>Maximum flexibility</u>. Except as otherwise specified in 5.3, the design of SEM shall be such that each module can be utilized in a broad range of system applications.

7

4.3.1.2 <u>Proprietary parts or processes</u>. It is the intent of this standard to encourage competition so that those modules which are standard can be made by more than one vendor. The utilization of proprietary parts, processes, or techniques is discouraged.

4.3.1.3 <u>Repairability</u>. A cost analysis shall be made of the module design and evaluated by the PM to determine whether or not it would be cost effective to repair the module if it should fail. If the evaluation shows that it would be cost effective to repair a failed module, those classified as SEM standard shall be documented with both design disclosed and functional specifications in accordance with appendix C. A module classified as a repairable SEM special shall be documented with a design disclosed specification in accordance with appendix C, unless otherwise specified by the PM.

## 5. DETAILED REQUIREMENTS

5.1 <u>Purpose</u>. The requirements herein define and explain the documentation and quality assurance requirements which make up the different types of SEM. The steps involved in implementing a new SEM are also described.

5.2 <u>SEM standard requirements</u>. A SEM standard is a module function which has the potential for being used in many military electronic systems and shall meet the following requirements.

5.2.1 <u>SEM standard design requirements</u>. A SEM standard shall be designed in accordance with the requirements of MIL-STD-1389.

5.2.2 <u>SEM standard quality assurance requirements</u>. A SEM standard shall conform to the quality assurance requirements specified in MIL-M-28787.

5.2.3 <u>SEM standard documentation requirements</u>. A SEM standard shall be documented in accordance with appendix C, both with a functional specification (also called a "slash sheet") and a design disclosed specification unless otherwise specified by the SEM-DRA and SEM-QAA (see 5.10).

5.2.4 <u>Nonstandard parts waiver</u>. In the event a SEM standard employs parts other than those specified in MIL-E-16400, MIL-E-5400, or MIL-P-24423 (or other contractually specified documents) as standard parts, the EC shall submit to the SEM-QAA documentation in accordance with MIL-STD-965 explaining the need for such parts and the reason or reasons that the equipment performance requirements cannot be met using the nearest similar standard parts (see 5.11).

5.3 <u>Candidate SEM standard requirements</u>. A candidate SEM standard is a module which has the potential for being used in multisystem applications, however, due to program constraints during the system development phase, the documentation and qualification have been deferred. A candidate SEM standard shall be developed into a SEM standard when the initial system application evolves into a production phase or earlier if another system application enables the development of the standard.

9

5.3.1 <u>Candidate SEM standard design requirements</u>. A candidate SEM standard shall be designed in accordance with the requirements of MIL-STD-1389.

5.3.2 <u>Candidate SEM standard quality assurance requirements</u>. A candidate SEM standard shall conform to the quality assurance requirements of MIL-M-28787 unless otherwise specified by the cognizant PM.

5.3.3 <u>Candidate SEM standard documentation requirements</u>. A candidate SEM standard shall be documented in accordance with appendix C. The type of documentation to be prepared shall be as directed by the cognizant PM, but it is recommended that documentation to the level of a SEM standard be planned. Upon preparation of the rough draft documentation for a candidate SEM standard, a copy shall be forwarded to the SEM-DRA for approval. Thereafter, the EC shall identify to the SEM-DRA within 25 working days of any changes made to this documentation, design of the module, or selection of components. The changes shall be identified in writing.

5.3.4 <u>Nonstandard parts approval</u>. In the event a candidate SEM standard employs parts other than those specified in MIL-E-16400, MIL-E-5400, or MIL-P-24423 (or other contractually specified documents) as standard parts, the EC shall submit to the SEM-DRA documentation in accordance with MIL-STD-965 explaining the need for such parts and the reason or reasons that equipment performance requirements cannot be met using the nearest similar standard parts (see 5.11).

5.4 <u>SEM special requirements</u>. A SEM special is a module function which does not have the potential for broad applicability. These modules shall be designed to meet the following requirements.

5.4.1 <u>SEM special design requirements</u>. SEM special modules shall meet the mechanical and electrical design requirements of MIL-STD-1389.

5.4.2 <u>SEM special quality assurance requirements</u>. SEM special modules shall be in accordance with the quality assurance requirements of MIL-M-28787 unless otherwise specified by the cognizant PM.

5.4.3 <u>SEM special documentation requirements</u>. SEM special modules shall be documented in accordance with appendix C. The level of documentation shall be directed by the cognizant PM. However, if the module is repairable, it is recommended that both functional and design disclosed specifications be prepared, and if non-repairable, it is recommended that a functional specification only be prepared.

5.4.4 <u>Nonstandard parts approval</u>. In the event that a SEM special module employs parts other than those specified in MIL-E-16400 (or other contractually specified documents) as standard parts, the contractor shall submit documentation in accordance with MIL-STD-965 explaining the need for such parts and the reason or reasons that equipment performance requirements cannot be met using the nearest similar standard parts (see 5.11). Existing SEM special modules using nonstandard parts which have been fully designed, documented, and qualified to the requirements of MIL-STD-1389 and MIL-M-28787 do not require reapproval of nonstandard parts.

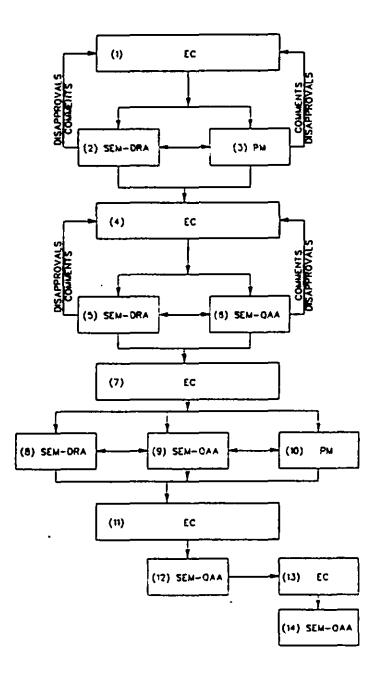

5.5 <u>Implementation procedures</u>. The procedure for obtaining approval of new associated detail specifications is illustrated on figure 1. The function of the elements depicted on figure 1 are as defined in 5.6 through 5.10.4.

5.6 <u>Submission of design approval requests (Block 1)</u>. The EC shall complete and forward the DAR (in accordance with appendix A) concurrently to the SEM-DRA and the PM for each new module design proposed (see 5.11 and 6.4.1).

5.6.1 <u>DAR action (Block 2)</u>. Following receipt of each DAR, the SEM-DRA will forward the DAR action notification to the EC and the PM. If the DAR is approved, the following will be indicated on the action notification:

(a) Module classification (SEM standard or SEM special).

(b) Module key code.

11

- (c) Module name.

- (d) MIL-M-28787 detail specification number for SEM standards.

- (e) SEM special module document numbers are assigned by the PM (or his agent). If the module is classified as a special, the procedure is concluded at this point. If the DAR is disapproved, the action notification will give a complete explanation for the disapproving action. If the PM elects to treat the special as a standard in documentation and quality assurance, the procedure continues as for a standard.

5.6.1.1 <u>PM review (Block 3)</u>. The PM shall review the DAR, comment, and approve or disapprove for a particular system application.

5.6.1.2 <u>Status notification</u>. The EC shall notify the SEM-DRA and the PM at periodic intervals of the current design status of modules with approved DARs (see 5.11 and 6.4.2).

5.7 <u>Submission of module descriptions (Block 4)</u>. The EC shall prepare a module description in accordance with appendix B for each module classified as standard by the SEM-DRA and shall forward the completed description concurrently to the SEM-DRA and the SEM-QAA (see 5.11 and 6.4.3).

5.8 <u>Preparation of detail specification draft (Block 4)</u>. The EC proposing a new SEM design shall develop the appropriate associated detail specification for the module in accordance with appendix C. The EC shall submit a rough draft detail specification to the PM, the SEM-DRA, and the SEM-QAA for review and comment (Blocks 5 and 6) prior to the preparation of the preliminary associated detail specification (see 5.11).

5.9 <u>Preparation of preliminary associated detail specification (Block</u> <u>7</u>). Upon approval of the associated detail specification draft by the PM, the SEM-DRA, and the SEM-QAA, the EC shall prepare the preliminary associated detail specification in accordance with appendix C. The EC obtains proof and correlation modules and submits them to SEM-QAA.

5.9.1 <u>SEM correlation (Block 9)</u>. The SEM-QAA performs correlation testing on the submitted modules and verifies the contents of the preliminary associated detail specification. The SEM-QAA then submits the results to the EC, the SEM-QAA, and the PM.

5.10 <u>SEM initial qualification submission (Block 13)</u>. Upon completion of the preliminary associated detail specification, the EC shall submit the appropriate number of module samples and the preliminary detail specification to the SEM-QAA for initial qualification in accordance with MIL-M-28787. At the same time, a copy of the associated detail specification shall be submitted to the SEM-DRA and the PM for review. (Blocks 8 and 10). The SEM-DRA and the PM review the preliminary associated detail specification and submit comments to the EC and the SEM-QAA.

5.10.1 <u>Notification for initial qualification</u>. The EC shall notify the SEM-QAA not later than 90 days prior to submission of the module samples and associated detail specification for initial qualification testing.

5.10.2 <u>Completion of initial qualification (Block 14)</u>. The time required to complete qualification procedures for SEM will not exceed 120 days after receipt of the module samples at the SEM-QAA. The SEM-QAA submits the results to the EC, the SEM-DRA, and the PM.

5.10.3 <u>Retention of module samples</u>. All modules supplied for initial qualification to the SEM-QAA will be retained by the SEM-QAA unless otherwise agreed to by the PM and the SEM-QAA.

5.10.4 <u>Repository for final detail specification (Block 11)</u>. Upon completion of correlation data and approval of the preliminary detail specification by the SEM-QAA and the SEM-DRA, the EC shall prepare the final detail specification. The final detail specification shall include recommendations made as a result of design review and correlation data. The EC shall submit copies of the final detail specification to the PM, the SEM-DRA, and the SEM-QAA for approval. After approval, the detail specification masters for SEM standards will be forwarded to the SEM-QAA (Block 12). The SEM-QAA will forward the detail specification to the MIL-M-28787 preparing activity. The SEM-QAA is responsible for maintaining

configuration management for all SEM standard modules. They review all proposed revisions and coordinate with common module users to determine whether module interchangeability would be adversely affected. SEM special module configuration management remains the responsibility of the developer (for example, the sponsoring program office or acquisition office). SEM candidate standard module configuration remains the responsibility of the developer until the time the module is fully developed as a SEM standard. However, prior to that time, any changes to the documentation, design of the module, or selection of components must be identified to the SEM-DRA.

5.10.5 <u>Initial qualification rejection</u>. In the event of module failure during initial qualification tests, the SEM-QAA will forward a detailed report of test results and recommendations to the PM and the EC for corrective action.

5.10.6 <u>Resubmission</u>. The EC shall make all necessary corrections to the module design and documentation or module construction, or both, and resubmit new module samples for qualification or revised detail specification, or both, to the SEM-QAA.

5.11 <u>Contract data requirements</u>. Data required by this standard are not deliverable unless specified on the Contract Data Requirements List (DD Form 1423) or the contract schedule (see 6.3).

#### 6. NOTES

(This section contains information of a general or explanatory nature that may be helpful, but is not mandatory.)

6.1 <u>Intended use</u>. This standard contains requirements for employing standard electronic modules.

6.2 <u>Issue of DODISS</u>. When this standard is used in acquisition, the issue of the DODISS to be applicable to this solicitation must be cited in this solicitation (see 2.1.1).

6.3 <u>Data requirements</u>. The following Data Item Descriptions (DID's) must be listed, as applicable, on the Contract Data Requirements List (DD Form 1423) when this standard is applied on a contract, in order to obtain the data, except where DOD FAR Supplement 27.475-1 exempts the requirement for a DD Form 1423. The deliverable data includes the following:

| Reference<br><u>Paragraph</u>         | <u>DIO Number</u> | <u>OID Title</u>                                                     |

|---------------------------------------|-------------------|----------------------------------------------------------------------|

| 5.3.4, 5.4.4                          | DI-MISC-80071     | Parts Approval Request.                                              |

| 3.1.7, 5.6,<br>5.6.1, 5.6.1.1,<br>5.7 | DI-E-7042         | Request, Design Approval for Standard<br>Electronic Modules Program. |

| 5.8                                   | DI-E-7043         | Specifications, Standard Electronic<br>Modules Program (SEMP).       |

| 5.3.4, 5.4.4                          | DI-E-7044         | Request, Exception, Standard Elec-<br>tronic Modules Program (SEMP). |

The above DID's were those cleared as of the date of this standard. The current issue of DOD 5010.12-L, Acquisition Management Systems and Data Requirements Control List (AMSDL), must be researched to ensure that only current, cleared DID's are cited on the DD Form 1423.

6.4 Timely submission and approval.

6.4.1 <u>DAR</u>. Submission of the DAR should be made within 120 calendar days after award of contract, but no later than 30 days prior to the Critical Design Review (CDR). In addition, updated DARs should be submitted within 14 days after additional requirements are realized. DAR action notification should be forwarded to the PM within 25 working days of DAR receipt.

6.4.2 <u>Status</u>. EC notification of the PM as to module design status occurs at intervals not exceeding 90 days.

6.4.3 <u>Module descriptions</u>. Submission of the module description should be made no later than 25 working days after receipt of the SEM-DRA letter approving and classifying the module DAR as a standard.

6.5 <u>Subject\_term (keyword) listing</u>.

Modules, Standard Electronic SEM Standard Electronic Modules

6.6 <u>Changes from previous issue</u>. Marginal notations are not used in this revision to identify changes with respect to the previous issue due to the extensiveness of the changes.

| Custodians         |     |    |

|--------------------|-----|----|

| Army - ER          |     |    |

| Navy - SH          |     |    |

| Air Force - 85     |     |    |

| Review activities: |     |    |

| Army - AT, AV      |     |    |

| Navy - AS, MC      |     |    |

| Air Force - 13,    | 17, | 19 |

| DLA - ES           |     |    |

Preparing activity: Navy - SH-

Agent: NWSC Crane

(Project 5963-0038)

## NOTES:

- 1. See 3.1 for definition of activities.

- 2. See 5.6 through 5.10.4 for function of each block.

FIGURE 1. SEM design approval procedure.

## APPENDIX A

## SAMPLE STANDARD ELECTRONIC MODULE DESIGN APPROVAL REQUEST

10. SCOPE

10.1 <u>Scope</u>. This appendix is not a mandatory part of the standard. The information contained herein is intended for guidance only. This appendix provides a sample blank design approval request form. It may be reproduced as necessary.

20. APPLICABLE DOCUMENTS. This section is not applicable to this appendix.

## APPENDIX A

|                                                                                                                      | DAR NUMBER                            | FOR                              |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------|

|                                                                                                                      | DATE RECEIVED                         | DRA                              |

| STANDARD ELECTRONIC MODULE                                                                                           | CLASSIFICATION                        | USE                              |

| DESIGN APPROVAL REQUEST                                                                                              |                                       | ONLY                             |

|                                                                                                                      |                                       |                                  |

|                                                                                                                      |                                       |                                  |

|                                                                                                                      |                                       |                                  |

|                                                                                                                      |                                       |                                  |

| INITIATOR INFORMATION:                                                                                               |                                       |                                  |

| ACTIVITY NAME                                                                                                        |                                       |                                  |

| ADDRESS                                                                                                              |                                       | <u> </u>                         |

| <u> </u>                                                                                                             |                                       | <u> </u>                         |

| INITIAL SYSTEM APPLICATION                                                                                           | <u> </u>                              |                                  |

| NAME OF COGNIZANT INDIVIDUAL                                                                                         |                                       |                                  |

| Will this module be designed in ac<br>If not, give exceptions.<br><u>MODULE INFORMATION</u> : Identificat<br>module7 | ion number (reference DAR, asse       | mbly, and so forth) for this     |

| NAME                                                                                                                 |                                       |                                  |

| TYPE: DIGITAL ANAL                                                                                                   |                                       |                                  |

| DRAWING ASSY NO                                                                                                      |                                       |                                  |

| NUMBER OF COMPLETE CIRCUITS PER MODUL                                                                                |                                       |                                  |

| NUMBER OF CONNECTOR CONTACTS                                                                                         |                                       |                                  |

| DOES MODULE CONTAIN PROGRAMMABLE ELEM                                                                                |                                       | FF PROGRAMMARIE FLEMENTS SECTION |

| (EX: PROM, CONFIGURABLE GATE ARRAY,                                                                                  |                                       |                                  |

| COMPONENT INFORMATION:                                                                                               |                                       |                                  |

| FUNCTION TECHNOLOGY                                                                                                  | VENDOR AND PART NUMBER                | ALTERNATE PART NUMBER            |

|                                                                                                                      |                                       |                                  |

|                                                                                                                      |                                       |                                  |

|                                                                                                                      | · · ·                                 |                                  |

|                                                                                                                      | ·                                     |                                  |

|                                                                                                                      | · · · · · · · · · · · · · · · · · · · |                                  |

20

## APPENDIX A

٦

٢

•

|                                 |                       | · · · · ·                                                    |                        |             |

|---------------------------------|-----------------------|--------------------------------------------------------------|------------------------|-------------|

|                                 |                       |                                                              |                        |             |

| HOOULE QUANTIT                  | Y PER SYSTEH APPLICAT | 10M                                                          |                        |             |

| NUMBER OF SYST                  | EHS CONTRACTED        |                                                              |                        |             |

|                                 |                       |                                                              |                        |             |

| MICH EXISTING                   | SEM HAVE BEEN CONSID  | WERED FOR THE IMPLEMENTATION                                 | OF THIS FUNCTION?      |             |

| ESTIMATED COMP                  | LETION DATE:          |                                                              |                        |             |

| DESIGN                          |                       |                                                              |                        |             |

| PROTOTYPE                       |                       |                                                              |                        |             |

| HOOULE SPECE                    | ICATION               |                                                              |                        | <u></u>     |

|                                 |                       | <u></u>                                                      |                        |             |

|                                 |                       | CLUDE. AS APPLICABLE. INPUT                                  | OUTPUT REDUIREMENTS AN | D RELATION- |

|                                 | DESCRIPTION SHALL IN  | CLUDE, AS APPLICABLE, INPUT,<br>. BOOLEAN EQUATIONS, CONTROL |                        |             |

| TYPICALLY THE<br>SHIPS, TRUTH T | DESCRIPTION SHALL IN  |                                                              |                        |             |

| TYPICALLY THE<br>HIPS, TRUTH TA | DESCRIPTION SHALL IN  |                                                              |                        |             |

| TYPICALLY THE<br>HIPS, TRUTH TA | DESCRIPTION SHALL IN  |                                                              |                        |             |

| TYPICALLY THE<br>HIPS, TRUTH TA | DESCRIPTION SHALL IN  |                                                              |                        |             |

| TYPICALLY THE<br>HIPS, TRUTH TA | DESCRIPTION SHALL IN  |                                                              |                        |             |

| TYPICALLY THE<br>SHIPS, TRUTH T | DESCRIPTION SHALL IN  |                                                              |                        |             |

| TYPICALLY THE<br>HIPS, TRUTH TA | DESCRIPTION SHALL IN  |                                                              |                        |             |

| TYPICALLY THE<br>SHIPS, TRUTH T | DESCRIPTION SHALL IN  |                                                              |                        |             |

## APPENDIX A

#### LOGIC/SCHEMATIC DIAGRAM

٠

(A LOGIC/SCHEMATIC DIAGRAM SHALL BE INCLUDED, DENOTING CONTACT ASSIGNMENTS (IF KNOWN), PART NUMBERS, AND COMPONENT VALUES). IF PROGRAMMABLE GATE FUNCTIONS ARE USED, THE GATE EQUIVALENT DIAGRAMS, TRANSFER FUNCTIONS, OR TRUTH TABLES SHALL BE PROVIDED.

## APPENDIX A

| INPUT CHARACTERISTICS         | MENEHUH      | TYPICAL  | HAXIMUN   | CONDITIONS  |

|-------------------------------|--------------|----------|-----------|-------------|

| v <sub>IL</sub>               | <u> </u>     |          |           | -           |

| A <sup>IH</sup>               |              |          |           | <u> </u>    |

| IIL                           |              | <u> </u> |           |             |

| <sup>T</sup> IL               | <u> </u>     |          |           |             |

| IIL                           |              |          |           | <b></b> _   |

| IIH                           | <u> </u>     |          |           | <b></b>     |

| IIH                           |              | <u> </u> |           | <del></del> |

| IIH                           |              |          |           |             |

| CAPACITANCE                   |              |          |           |             |

| OUTPUT CHARACTERISTICS        |              |          |           |             |

| VOL                           |              |          |           |             |

| v <sub>он</sub>               |              |          |           | <del></del> |

| IOL                           |              |          |           |             |

| тон                           |              |          | · <u></u> |             |

| PROPAGATION DELAY TIMES       |              |          |           |             |

|                               | <u> </u>     |          |           |             |

|                               |              |          |           |             |

|                               |              |          |           |             |

|                               |              |          |           |             |

| MAXEMUM LOAD CAPACETANCE      |              |          |           |             |

| POWER SUPPLY VOLTAGES AND TOL | ERANCES      |          |           |             |

| ABSOLUTE MAXIMUN              |              |          |           |             |

| NORHAL VOLTAGE(S)             |              |          |           |             |

| HOOLE POVER DISSIPATION       |              |          |           |             |

| LIST ANY ADDITIONAL PARAMETER | RECUIREMENTS |          |           |             |

| CLAR OUT DOWNLEDING FACADELES |              |          |           |             |

\*

.

## APPENDIX A

| INPUT AMPLITUDE           |              | TOLERANCE                                                          |  |

|---------------------------|--------------|--------------------------------------------------------------------|--|

|                           |              | CONDITIONS                                                         |  |

|                           |              |                                                                    |  |

|                           |              |                                                                    |  |

| INPUT OFFSET VOLTAGE      |              |                                                                    |  |

|                           |              |                                                                    |  |

|                           |              |                                                                    |  |

| ALOG OUTPUTS              |              |                                                                    |  |

| AMPLITUDE RANGE           | 07           | TOLERANCE                                                          |  |

|                           |              | <u> </u>                                                           |  |

|                           |              |                                                                    |  |

|                           |              | ·····                                                              |  |

|                           |              | TOLERANCE                                                          |  |

| ACCURACY OF FUNCTION      |              |                                                                    |  |

|                           |              |                                                                    |  |

|                           |              |                                                                    |  |

|                           |              |                                                                    |  |

| POWER GAIN                |              |                                                                    |  |

| UPPER 3 dB POINT (Hz)     |              |                                                                    |  |

|                           |              |                                                                    |  |

|                           |              | <u> </u>                                                           |  |

|                           |              | <u></u>                                                            |  |

| SETTLING TIME             |              |                                                                    |  |

|                           |              |                                                                    |  |

|                           |              |                                                                    |  |

| POWER SUPPLY VOLTAGES AND | TOLEDANCES   |                                                                    |  |

| MODULE POWER DISSIPATION: | TYPICAL      | MAXIMUM                                                            |  |

| LIST ADDITIONAL PARAMETER | REQUIREMENTS |                                                                    |  |

|                           |              |                                                                    |  |

| OTHER CHARACTERISTICS:    |              | MATION OR FOR FUNCTIONS THAT AR<br>ICALLY CONVERTERS. POWER SUPPLI |  |

24

## APPENOIX A

|          | SYSTEM INFORMATION SECTION                                                                    |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| Name of  | this system/equipment. (Please define acronyms)                                               |  |  |  |  |

|          |                                                                                               |  |  |  |  |

| List oth | er names which also identify this system/equipment.                                           |  |  |  |  |

|          | ive a brief description of this system/equipment.                                             |  |  |  |  |

|          |                                                                                               |  |  |  |  |

| ls this  | equipment a part of another equipment, or made up of several different subequipment units     |  |  |  |  |

|          | s, and so forth) or is it an update of an existing equipment? If so, please explain the ship. |  |  |  |  |

|          |                                                                                               |  |  |  |  |

| What is  | the cognizant Government activity?                                                            |  |  |  |  |

| Ac       | tivity name                                                                                   |  |  |  |  |

| Ac       | tivity address                                                                                |  |  |  |  |

| Who is t | he cognizant Government individual?                                                           |  |  |  |  |

| Na       | me and Code                                                                                   |  |  |  |  |

| Ad       | dress                                                                                         |  |  |  |  |

| ī        | lephone                                                                                       |  |  |  |  |

|          | nt contract number                                                                            |  |  |  |  |

|          | the schedule for this system/equipment?                                                       |  |  |  |  |

|          | ototype request for bids (RFB) date.                                                          |  |  |  |  |

| -        |                                                                                               |  |  |  |  |

|          | GLOCYDW OWIIVERY GALE.                                                                        |  |  |  |  |

| P -      | ctotype delivery date                                                                         |  |  |  |  |

•

.

.

## MIL-STD-1378E

## APPENDIX A

|       | Company name                                                                                  |

|-------|-----------------------------------------------------------------------------------------------|

|       | Division                                                                                      |

|       | Address                                                                                       |

|       |                                                                                               |

|       | Cognizant individual                                                                          |

|       | Te lephone                                                                                    |

| Name  | of the subcontractor(s) for major subassemblies (involving new module designs).               |

|       | Company name                                                                                  |

|       | Division                                                                                      |

|       | Address                                                                                       |

|       |                                                                                               |

|       | Cognizant individual                                                                          |

|       | Te lephone                                                                                    |

| How m | ay equipment units will be produced?                                                          |

|       | During prototype phase                                                                        |

|       | During production phase                                                                       |

| What  | environmental class are these modules designed to meet?                                       |

| Are s | pecial modules in this system designed to be repairable?                                      |

|       | will this equipment be installed? Describe each different installation.                       |

|       |                                                                                               |

| How m | any systems will be installed at each different type of installation?                         |

| wi11  | each installation of this system contain the same complement of modules, or will each instal- |

| latio | n be entirely different? (Please explain).                                                    |

|       |                                                                                               |

|       |                                                                                               |

|       |                                                                                               |

|       |                                                                                               |

|       |                                                                                               |

|       |                                                                                               |

|       |                                                                                               |

## APPENDIX A

#### PROGRAMMABLE ELEMENTS

What type of programmable element is used?

How many program versions of this module will exist in the system/equipment at a given time?

Describe the type of information programmed on these module(s). \_\_\_\_\_\_

How many ROH key codes are anticipated? \_\_\_\_\_

(A drawing number is required for each key code assigned). Should these modules all be keyed the

same or keyed differently? (Explain) \_\_\_\_

If you need assistance in completing this form, please contact:

Naval Avionics Center (8/814) 5000 E 21st Street Indianapolis, IN 46219-2189

Telephone: (317) 353-3735

## APPENDIX A

| Key code and military<br>part number or<br>reference number | Description | Modules per<br>equipment | Comments |

|-------------------------------------------------------------|-------------|--------------------------|----------|

|                                                             |             |                          | ·        |

|                                                             |             |                          |          |

|                                                             |             | · ·                      |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

|                                                             |             |                          |          |

Use additional sheets, if required.

.

#### APPENDIX 8

#### INSTRUCTIONS FOR PREPARING MODULE DESCRIPTIONS

10. SCOPE

10.1 <u>Scope</u>. This appendix is a mandatory part of the standard and shall be used in the preparation of module descriptions for the Standard Electronic Modules (SEM) Program. The information contained herein is intended for compliance. This appendix does not attempt to specify how a module shall be designed, tested, or used, but describes the information that shall be included in the module description and the format for presenting the information.

20. APPLICABLE DOCUMENTS

20.1 <u>Non-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents which are DOD adopted are those listed in the issue of the DODISS cited in the solicitation. Unless otherwise specified, the issues of documents not listed in the DODISS are the issues of the documents cited in the solicitation.

AMERICAN NATIONAL STANDARDS INSTITUTE (ANSI)

| Y 14.15 | • | Electrical and Electronics Diagrams.           |

|---------|---|------------------------------------------------|

| STD 91  | • | Standard Graphic Symbols for Logic Functions   |

| Y 32.2  | - | Graphic Symbols for Electrical and Electronics |

|         |   | Diagrams.                                      |

(Application for copies should be addressed to the American National Standards Institute, Inc., 1430 Broadway, New York, NY 10018.)

(Non-Government standards and other publications are normally available from the organizations that prepare or distribute the documents. These documents also may be available in or through libraries or other informational services.)

#### APPENDIX B

**30. GENERAL REQUIREMENTS**

30.1 <u>General requirements</u>. Module descriptions prepared in accordance with this appendix will be included in MIL-STD-1634 and used for selection and application of SEM modules. Information, in addition to that required by this appendix, may be added to the module description as required so that selection and application of a particular module to a system will be more easily accomplished.

30.1.1 <u>Style, format, and identification</u>. An example of the style, format, and identification of module descriptions is available from the SEM-DRA.

30.1.2 <u>Warnings, cautions, and notes</u>. Warnings and cautions shall precede the text to which they apply. Notes may either precede or follow, or both, the text to which they apply depending on the material to be highlighted. Inserts in the text shall be short and concise and be used to emphasize important and critical instructions.

30.1.2.1 <u>Warnings</u>. Warnings shall be used when an operating procedure or practice if not followed correctly, could result in personal injury or loss of life.

30.1.2.2 <u>Cautions</u>. Cautions shall be used when an operating procedure or practice if not strictly observed, could result in damage to, or destruction of, equipment.

30.1.2.3 <u>Notes</u>. Notes shall be used when it is necessary to highlight an operating procedure, practice or condition.

30.1.3 <u>Diagrams and graphic symbols</u>. Diagrams and graphic symbols shall be in accordance with ANSI Y 14.15, ANSI Y 32.2, and ANSI STD 91.

## APPENDIX B

#### 40. DETAILED REQUIREMENTS

40.1 <u>Module descriptions</u>. The module descriptions shall have the content and pages in the order specified herein. The parameters and other . information shall be complete and compatible with that which is in or will be in the detail specification.

40.1.1 <u>Page numbers</u>. Each page of the module description shall be marked at the bottom center with a module key code and a page number.

40.1.2 <u>Parameters and information</u>. The following is a list of the parameters and information which shall be included in the module description and the contents of each item.

- (a) KEY CODE: (Each page of the module description shall be marked in the upper right corner with the module key code).

- (b) NAME: (Insert the official module name assigned by the SEM-DRA).

- (c) SPEC NUMBER: MIL-M-28787/ (Insert detail specification number).

- (d) DESCRIPTION: (Insert a brief functional description).

- (e) DESIGN DISCLOSED: /FUNCTIONALLY SPECIFIED: (Place an "X" in the appropriate box).

- (f) FAMILY: (Insert appropriate family type, in other words, digital, analog, and so forth).

- (g) ORIGINAL TECHNOLOGY: (Insert name of technology used in the original module design, in other words, Schottky TTL, MOS, bipolar, and so forth)...

- (h) CIRCUITS PER MODULE: (Insert the number of circuits, components, and so forth, per module).

31

#### APPENDIX 8

- MECHANICAL SIZE: (Insert mechanical size and a note if the module extends below the interface plane and a note if holddown screws are used).

- (j) MECHANICAL FORMAT: (Insert the applicable module format).

- (k) PITCH: (Insert the pitch for the module, if applicable).

- (1) CONNECTOR CONTACTS: (Insert the number of connector contacts).

- (m) ENVIRONMENT: (Insert appropriate environment class).

- (n) POWER DISSIPATION (MAX): (Insert worst case power dissipation as ensured by the detail specification and the applicable power supply voltages).

- (o) POWER SUPPLY REQUIREMENTS: (Insert the power supply voltages necessary for module operation and the allowable tolerances of each).

- (p) INITIAL DESIGN COG: (Insert the name of the company or activity which is responsible for the initial module design).

- (q) APPLICATION INFORMATION: (Insert applications information which is necessary and useful for module users. The information should be concise and for functionally specified modules should be limited to those parameters which will be directly or indirectly ensured by the detail specification or other SEM requirements document. As a minimum the following areas shall be addressed:

- (1) Paralleling of outputs, if applicable.

- (2) Designation of inputs and outputs exactly as they will appear in the detail specification.

- (3) Generic component types.

\_\_\_\_

32

#### APPENDIX B

- (4) User application rules: A space of not less than 20 lines shall be left for each user to insert or reference application rules unique to each user application. This should be the last item under APPLICATION INFORMATION).

- (r) INPUT OUTPUT RELATIONSHIP: (Module descriptions for digital modules shall contain truth tables and instruction sets if applicable defining the logical input-output relationship).

- (s) CONTACT PROGRAMMING: (If applicable, analog module descriptions shall have contact programming tables or other useful tabulated information.)

- (t) SCHEMATIC: (Insert module function diagram figure. This figure shall be a functional block diagram of the module and shall be prepared in accordance with ANSI Y 14.15, using symbols in accordance with ANSI Y 32.14 and ANSI STD 91. The module function diagram figure shall be as it will appear in the detail specification. The designation of inputs and outputs shall be exactly as they will appear in the detail specification. In addition, a figure shall be included showing the module contacts in their relative physical locations as viewed from the bottom of the module and the designation of each including unused contacts. Power supply filter capacitance shall be shown as a single bulk capacitance for each power supply. The value and tolerance as ensured by the detail specification shall be shown for each).

- (u) STATIC CHARACTERISTICS: (Insert applicable operating temperature range (NOTE: Values are approximate and will not be finalized until after qualification testing). The static characteristics table shall list all static parameters of interest to module users during selection and design, minimum and maximum end-of-life limits over the operating temperature range, and the units for the limits. Static characteristics should also show significant absolute maximum ratings, such as input breakdown limits. The parameter column shall also show significant conditions under which the limits apply. All limits shall be exactly as they will appear in the detail specification or derived directly from those limits. The limits shall, in general, reflect worst case conditions.)

### APPENDIX B

- (v) DYNAMIC CHARACTERISTICS: (Insert applicable operating temperature range (NOTE: Values are approximate and will not be finalized until after qualification testing). The dynamic characteristics table shall list all dynamic parameters of interest to module users during selection and design, minimum and maximum end-of-life limits over the operating temperature range, and the units for the limits. The limits and parameters columns should indicate any significant conditions under which the limits apply. All limits shall be exactly as they will appear in the detail specification or derived directly from those limits. The limits shall reflect worst case conditions.)

- (w) WAVEFORMS: (Additional pages may be included for more complex functions. This page shall consist of useful or clarifying graphic representation such as waveforms showing timing relationships and parameter definitions or frequency response curves, and so forth. The title shall be changed to reflect the nature of the information given.)

#### APPENDIX C

#### INSTRUCTIONS FOR PREPARING MODULE SPECIFICATIONS

10. SCOPE

10.1 <u>Scope</u>. This appendix is a mandatory part of the standard in the preparation of detail specifications for the SEM program. The information contained herein is intended for compliance. This appendix does not attempt to specify how a module shall be designed or tested, but describes the information that shall be included in the detail specification in conjunction with the requirements specified in the standard and the format for presenting the information.

10.2 <u>Classification</u>. The specifications covered by this appendix shall be of the following types:

Design disclosed specifications. Functional specifications.

20. APPLICABLE DOCUMENTS.

20.1 Government documents.

20.1.1 <u>Specifications and standards</u>. The following specifications and standards form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DODISS) and supplement thereto, cited in the solicitation.

SPECIFICATIONS

MILITARY

| MIL-M-28787/269 | - | Modules, Standard Electronic, Amplifier,  |

|-----------------|---|-------------------------------------------|

|                 |   | Differential, Analog, Key Code FGH.       |

| MIL-M-28787/305 | • | Modules, Standard Electronic, Controller, |

|                 |   | Interrupt, Digital, Key Code ZJX.         |

| MIL-M-28787/308 | • | Modules, Standard Electronic, Program     |

|                 |   | Control Unit, Key Code MJC.               |

#### APPENDIX C

| - | Modules, Standard Electronic, Converter, |

|---|------------------------------------------|

|   | D/A, Key Code DBK.                       |

| - | Modules, Standard Electronic, Micro-     |

|   | processor Control and Maintenance, Key   |

|   | Code ADP.                                |

| - | Modules, Standard Electronic,            |

|   | Microprocessor, Key Code NAH.            |

|   | -                                        |

STANDARDS

MILITARY

| DOD-STD-100 |   | Engineering Drawing Practices.         |

|-------------|---|----------------------------------------|

| MIL-STD-961 | - | Military Specifications and Associated |

|             |   | Documents, Preparation of.             |

(Unless otherwise indicated, copies of federal and Military specifications and standards are available from the Naval Publications and Forms Center, (ATTN: NPODS), 5801 Tabor Avenue, Philadelphia, PA 19120-5099).

**30. GENERAL REQUIREMENTS**

30.1 <u>General requirements</u>. Specifications prepared in accordance with this appendix shall be the documents used for the acquisition and testing of modules. Information, in addition to that required by this appendix, may be added to the detail specification as required for the acquisition and testing of a particular module.

30.1.1 <u>Types of specifications</u>. All military specifications prepared for SEM in accordance with this appendix shall be in accordance with MIL-STD-961. Military specifications required to be design disclosed shall also be in accordance with requirements of this appendix (see 40.). Examples of functional specifications for SEM standard modules (also known as "slash sheets") are MIL-M-28787/269, MIL-M-28787/305, MIL-M-28787/308, MIL-M-28787/352, MIL-M-28787/353, and MIL-M-28787/322. An example of a design disclosed specification is available from the SEM-QAA. Specifications for SEM special modules shall be prepared as bookform drawings on "A" size drawing forms in accordance with DOD-STD-100.

#### APPENDIX C

30.1.2 <u>Style, format, and identification</u>. The style, format, and identification of the detail specification shall be as specified in MIL-STD-961 and this appendix.

30.1.3 <u>Assembly data sheets</u>. Design disclosed specifications shall include following the numbered sections, the assembly, note, and parts list sheets which depict the complete module assembly instructions (see 40.1.1, 40.1.2, and 40.1.3).

40. DETAILED REQUIREMENTS

40.1 <u>Detailed requirements</u>. The requirements and test procedures shall be in accordance with MIL-M-28787 and appendices D and E of this standard.

40.1.1 <u>Assembly sheets</u>. The module assembly sheets shall depict the final assembly, specifying component location and identification, printed wiring boards and module structure.

40.1.2 <u>Note sheets</u>. The note sheets shall contain the notes referenced on the assembly sheets.

40.1.3 <u>Parts list sheets</u>. The parts list sheets shall define the items applicable to the manufacturer of the module. Items are identified by quantity, identification number, and nomenclature. Where applicable, the unit measure, code identification number, reference designation, and mounting hardware item number shall also be specified.

40.1.4 <u>Artwork and schematic</u>. Figures included with the documentation shall include a schematic of the electrical circuit and a pictorial view covering the artwork.

#### APPENDIX D

#### TEST REQUIREMENTS FOR DIGITAL MODULES

10. SCOPE

10.1 <u>Scope</u>. This appendix is a mandatory part of the standard in the preparation of detail specifications for digital modules for the SEM. The information contained herein is intended for compliance. This appendix provides a baseline against which new digital module detail specifications are written and reviewed.

20. APPLICABLE DOCUMENT

20.1 Government documents.