#### **METHOD 5010.4**

# TEST PROCEDURES FOR COMPLEX MONOLITHIC MICROCIRCUITS

1. <u>PURPOSE</u>. This method establishes screening, qualification, and quality conformance requirements for the testing of complex monolithic microcircuits to assist in achieving the following levels of quality (class level B and S) and reliability commensurate with the intended application. Complex monolithic microcircuits are defined as monolithic devices that contain a minimum of 4,500 transistors. It shall be used in conjunction with other documentation such as appendix A of MIL-PRF-38535 and an applicable device specification or drawing to establish the design, material, performance, control, and documentation requirements which are needed to achieve prescribed levels of device quality and reliability.

2. <u>APPARATUS</u>. Suitable measurement equipments necessary to determine compliance with applicable acquisition documents and other apparatus as required in the referenced test methods.

3. <u>PROCEDURE</u>. The procedures defined herein, including appendix I and II, outline the requirements and testing necessary to certify and qualify a complex microcircuit design, fabrication, assembly and testing facility. It illustrates the concept of generic qualification through the use of standard evaluation circuits and process monitors.

3.1 <u>Test procedures for complex monolithic microcircuits</u>. Complex monolithic microcircuits shall be tested as described herein, and in the device specification or drawing.

3.1.1 <u>Precedence</u>. Unless otherwise specified in the device specification or drawing, the test requirements and conditions shall be given herein.

3.1.2 <u>Electrostatic discharge sensitivity</u>. Electrostatic discharge sensitivity testing, marking, and handling shall be in accordance with appendix A of MIL-PRF-38535.

3.1.3 <u>Failure analysis</u>. When required by the applicable device specification failure analysis of devices rejected during any test in the screening sequence shall be accomplished in accordance with method 5003, test condition A.

3.1.4 <u>Failure analysis class level S</u>. Class level S devices shall be analyzed in accordance with method 5003, test condition B to identify the cause for failed lots and burn-in failures in accordance with appendix A of MIL-PRF-38535, A.4.3.3.1, and A.4.6.1.2.1. The documented results shall only be reported to the qualifying or acquiring activity when specifically requested.

3.1.5 <u>Class requirements</u>. Within tables having a class column, only those test and inspections or subgroups identified with "B" are applicable to class level B. All apply to class level S.

3.1.6 <u>Radiation</u>. When required by the applicable device specification or drawing, qualification, and quality conformance inspection requirements for radiation hardness assured devices are in addition to the normal class level S and B requirements. These requirements for each specified radiation levels (M, D, P, L, R, F, G and H) are detailed in table VIII herein.

#### 3.2 Element evaluation.

#### 3.2.1 General.

3.2.1.1 <u>Element</u>. Herein "element" refers to materials for device assembly. Before device assembly, element characteristics shall be evaluated and verified to assure their compatibility with element specifications, device requirements, and manufacturing procedures (see table I). Also, characteristics which cannot be verified after manufacturing but could cause function failure shall be evaluated and verified before assembly.

### TABLE I. Element evaluation summary.

| Element            | Paragraph | Requirement          |  |  |

|--------------------|-----------|----------------------|--|--|

| Microcircuit wafer | 3.2.2     | Appendix II (herein) |  |  |

| Package            | 3.2.3     | Table II (herein)    |  |  |

3.2.1.2 <u>Element evaluation requirements</u>. Element evaluation may be performed at either the element supplier or device manufacturing facility up to the point where the element must undergo processing or assembly prior to testing. If element evaluation is performed by the supplier, then the device manufacturer must obtain a summary of the results for verification, and record retention.

#### 3.2.2 Microcircuit wafer evaluation.

3.2.2.1 <u>Definition</u>. Diffused wafers used and evaluated shall, as a minimum, be complete with interconnect layers and glassivation from material that was homogeneously processed through wafer fabrication.

3.2.2.2 <u>General</u>. For the purpose of microcircuit wafer evaluation and wafer lot acceptance, measurement of the process monitor (PM), verifying that the identified parameters are within process limits, will be required from each wafer lot in accordance with appendix II wafer lot acceptance herein. Each die from each diffused wafer lot shall be electrically tested prior to assembly in accordance with the manufacturer's in-house documentation.

3.2.3 <u>Package evaluation</u>. Each package type shall be evaluated and characterized in accordance with table II herein prior to use. Finite element analyses techniques may be used. Packages used for complex monolithic microcircuits and fabricated to this test method shall be tested as follows:

3.2.3.1 <u>Definition</u>. Package used and evaluated shall consist of the same element specifications, materials, and finish; and homogeneously processed through device assembly.

# 3.2.3.2 Incoming inspection.

- a. From the initial package inspection lot, a randomly selected sample shall be subjected to package evaluation (see table II). Additionally, subgroup 3 testing shall be accomplished using sealed packages. A die may be attached. Subgroups 2, 3, and 4 apply to cases only.

- b. Additionally, subgroups 1, 2, and 3 of table II shall be accomplished for each subsequent acquisition.

- c. For solderability (subgroup 2), lead integrity (subgroup 3), and metal package isolation (subgroup 4) defined within table II, a quantity (accept number) of 15 (0) shall apply to the number of terminals or leads tested. The leads shall be randomly selected from the three packages.

| Subgroup | Class | levels | Test                       | Test MIL-STD-883                 |                                                                                                                                                        | Quantity<br>(accept<br>number) | Reference<br>paragraph |

|----------|-------|--------|----------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------|

|          | S     | В      |                            | Method                           | Condition                                                                                                                                              |                                |                        |

| 1        | х     | Х      | Physical dimensions        | 2016                             |                                                                                                                                                        | 15 (0)                         | 3.2.3.3                |

| 2        | Х     | Х      | Solderability              | 2003                             | Solderability<br>temperature<br>245 ±5°C                                                                                                               | 3 (0)<br><u>1</u> /            |                        |

| 3        | Х     | х      | Thermal shock<br>or        | 1011                             | С                                                                                                                                                      | 3 (0)                          |                        |

|          |       |        | Temperature cycle          | 1010                             | C (20 cycles)                                                                                                                                          |                                |                        |

|          | Х     | х      | High temperature bake      | 1008                             | 2 hours at<br>150°C                                                                                                                                    | 3 (0)                          |                        |

|          | ×     | x      | Lead integrity             | 2004<br>2028                     | B2<br>(lead fatigue)<br>D<br>(leadless chip<br>carriers)<br>B1<br>(leaded chip<br>carrier<br>packages)<br>(Pin grid array<br>leads and<br>rigid leads) | 3 (0)<br><u>1</u> /            |                        |

|          | Х     | х      | Seal                       | 1014                             | D<br>Sealed cases                                                                                                                                      | 3 (0)                          |                        |

| 4        | Х     | Х      | Metal package<br>isolation | 1003                             | 600 V dc,<br>100 nA<br>maximum                                                                                                                         | 3 (0)<br><u>1</u> /            | 3.2.3.4                |

| 5        | х     | Х      | Insulation                 | 1003                             | <u>2</u> /                                                                                                                                             | 3 (0)                          |                        |

| 6        | Х     | Х      | Conductor                  | MIL-STD-<br>202<br>method<br>307 | <u>2</u> /                                                                                                                                             | 3 (0)                          |                        |

| 7        | Х     | Х      | Thermal characterization   | 1012                             |                                                                                                                                                        | <u>3</u> /                     |                        |

# TABLE II. Package evaluation requirements.

1/ A quantity (accept number) of 15 (0) shall apply to the number of terminals or leads to be tested. The leads shall be randomly selected from three packages minimum.

2/ Selected from three packages minimum. Conditions as specified by acquisition document and Appendix A of MIL-PRF-38535.

<u>3</u>/ Required on all package types prior to initial use.

3.2.3.3 <u>Subgroup 1</u>. Separately verify case and cover dimensional compliance with the device specification or drawing.

3.2.3.4 <u>Subgroup 4</u>. For metal cases with leads separated by an insulator, measure insulation resistance between the metal body of the case and the leads that are isolated from the case. This test does not apply to nonmetallic cases.

3.3 Manufacturing control.

3.3.1 Process control requirements. Line control as detailed below is required.

3.3.1.1 <u>Wafer fabrication controls</u>. Wafer fabrication shall be controlled in accordance with the manufacturer's fabrication baseline and documented procedures of the fabrication process.

3.3.1.2 <u>Assembly controls</u>. Assembly controls shall be in accordance with the manufacturer's assembly baseline and documented assembly procedures and additions herein

3.3.2 Design/layout system control. Design/layout controls shall be implemented using appendix I as a guide.

3.3.3 Testing controls. Documentation of testing controls shall meet the requirements of MIL-PRF-38535, appendix A.

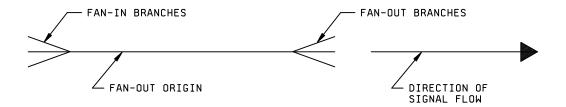

3.3.3.1 <u>Test vectors</u>. The manufacturing-level logic test vectors shall be graded for fault coverage using a fault simulator. The resulting fault coverage shall be reported in the device specification or drawing. Fault coverage shall be based on the detectable equivalence classes of single, permanent, stuck at zero, and stuck at one faults on all logic lines of a structural logic model. The logic model shall be expressed in terms of gate-level primitives or simple atomic functions (such as flip-flops). Large, regular structures such as RAMs and ROMs shall not be modeled at the gate level; rather, documentation shall be provided to show that these structures are tested using appropriate procedures (such as, galloping patterns for a RAM).

3.3.3.2 Built-in-test/build-in-redundancy. When specified in the device specification or drawing, the following shall apply.

3.3.3.2.1 <u>Probe/bond sites</u>. The device shall contain probe/bond sites to allow testing using the full set of test vectors specified in the device specification or drawing.

3.3.3.2.2 <u>Built-in redundancy for yield enhancement</u>. Where built-in redundancy is used to provide yield enhancement, testing shall be included to provide a statistic which represents the amount of alternate element selection utilized.

3.3.3.2.3 <u>Built-in redundancy using self test and fix</u>. Where built-in redundancy is provided in the form of self test and fix, the circuitry will be capable of interrogation to determine the level of redundancy remaining on the device.

3.3.4 Quality controls. The product assurance program plan shall be in accordance with MIL-PRF-38535, appendix A.

3.3.4.1 <u>Process monitor</u>. Process control and stability of dc parameters must be demonstrated through the use of the manufacturer's process monitor (PM). The PM is to be designed so that the dc process parameters may be measured in wafer form. The PM may also be packaged so as to permit biasing of those circuits for measurement. The PM design must be submitted to the qualifying activity for approval prior to qualification and must contain as a minimum the structures outlined in table I of appendix II herein.

3.3.4.1.1 <u>Process monitors for other technology devices</u>. An adequate set of PM's applicable for other technology devices shall be generated to assure that applicable failure mechanisms are detected and submitted for approval by the qualifying activity.

3.3.4.2 <u>Qualification device</u>. A qualification device shall be used to demonstrate process stability and reliability. The qualification device, either a standard evaluation circuit (SEC) or an actual device (worst case design) shall be submitted to the qualifying activity for approval and as such contain the basic information as detailed herein. The qualification device shall be fabricated with the same process and designed to the same design rules that will produce any device in the technology to be qualified. The qualification device design shall be configured in such a manner so as to evaluate the reliability of the underlayer designs (e.g., diffusion) and evaluate the worst case design rule conditions on the personalization layers. The design should utilize cell libraries as well as test structures which will detect metal to metal shorting or opening, high via resistance and dielectric pinholes during reliability life testing, where applicable. The following structures are suggested:

| Parameter                           | Structure                                     |

|-------------------------------------|-----------------------------------------------|

| Functionality and performance       | Large functional block (ALU), ring oscillator |

| Contact resistance/electromigration | Contact strings                               |

| Hot electrons/holes                 | Short channel devices                         |

| Oxide breakdown voltage             | Capacitors                                    |

| Resistance (electromigration test)  | Metal stripes                                 |

3.4 <u>Screening procedures for microcircuits</u>. Screening of microcircuits shall be conducted as described in 3.4 through 3.4.13 and table III herein. This provision does not preclude the performance of additional tests or inspection which may be required for specific devices or which may be desirable to optimize results of screening; however, any such special test inspection shall be subjected to the requirements of appendix A of MIL-PRF-38535, A.4.3.4 and A.4.3.7. Sampling inspections shall not be an acceptable substitute for any specified screening test. Any burn-in, in addition to that specified, is only permitted when documented in the lot records, and any failures shall be counted in applicable PDA calculations. Where end point or post test measurements are required as part of any given test method used in the screening procedure and where such post-test measurements are duplicated in the interim (post burn-in) or final electrical tests that follow, such measurements need not be duplicated and need to be performed only as part of the interim (post burn-in) or final electrical tests. Devices which pass screening requirements of a higher reliability level shall be considered to meet the screening requirements of a light reliability level shall be considered to meet the screening requirements of all lower levels. In no case shall screening to a lower level than that specified be permitted.

#### 3.4.1 General.

- a. Devices that fail any test or inspection criteria in the screening sequence shall be removed from the lot at the time of observation or immediately at the conclusion of the test in which the failure was observed. Once rejected and verified as a device failure, no device may be retested for acceptance. Unless otherwise specified in the device specification or drawings, electrical rejects may be used to satisfy sample selection requirements for qualification and quality conformance inspection in accordance with 3.5.

- b. Device screening shall be performed in the sequence shown in table III except where variations in sequence are specifically allowed herein.

# TABLE III. Device screening.

| Screen                                                       | Class level                                                     | S           | Class leve                                                   | Reference<br>paragraph |         |

|--------------------------------------------------------------|-----------------------------------------------------------------|-------------|--------------------------------------------------------------|------------------------|---------|

|                                                              | Method                                                          | Reqmt       | Method                                                       | Reqmt                  |         |

| Wafer lot acceptance                                         | 5010 appendix II<br>and 5007                                    | All<br>lots | 5010 appendix II                                             | All<br>lots            |         |

| Nondestructive bond pull                                     | 2023                                                            | 100%        |                                                              |                        |         |

| Internal visual                                              | 2010, test condition A                                          | 100%        | 2010, test<br>condition B                                    | 100%                   | 3.4.2   |

| Stabilization bake. No<br>end point measurements<br>required |                                                                 |             |                                                              |                        | 3.4.3   |

| Temperature cycling or thermal shock                         | 1010, test<br>condition C                                       | 100%        | 1010, test<br>condition C                                    | 100%                   | 3.4.5   |

|                                                              |                                                                 |             | 1011, test<br>condition A                                    | 100%                   |         |

| Constant acceleration                                        | 2001, test<br>condition E<br>(min) Y1<br>orientation<br>only    | 100%        | 2001, test<br>condition E<br>(min) Y1<br>orientation<br>only | 100%                   | 3.4.6   |

| Visual inspection                                            |                                                                 | 100%        |                                                              | 100%                   |         |

| Particle impact noise detection (PIND)                       | 2020, test condition A                                          | 100%        |                                                              |                        | 3.4.7   |

| Serialization                                                |                                                                 | 100%        |                                                              |                        |         |

| Interim (pre-burn-in)<br>electrical parameters               | In accordance<br>with applicable<br>device<br>specification     | 100%        | In accordance<br>with applicable<br>device<br>specification  | 100%                   | 3.4.9.1 |

| Burn-in test                                                 | 1015<br>240 hours at<br>125°C minimum                           | 100%        | 1015<br>160 hours at<br>125°C minimum                        | 100%                   | 3.4.10  |

| Interim (post-burn-in)<br>electrical parameters              | In accordance<br>with applicable<br>device<br>specification     | 100%        |                                                              | Optional               | 3.4.9.1 |

| Reverse bias burn-in                                         | 1015; test<br>condition A or<br>C, 72 hours at<br>150° minimum. | 100%        |                                                              |                        |         |

# TABLE III. Device screening -Continued.

| Screen                                                                                                                                                                                             | Class level S                                                                                                          |                      | Class level B                                               | Reference paragraph  |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------|----------------------|---------|

|                                                                                                                                                                                                    | Method                                                                                                                 | Reqmt.               | Method                                                      | Reqmt.               |         |

| Interim (post-burn-in)<br>electrical parameters                                                                                                                                                    | In accordance<br>with applicable<br>device<br>specification                                                            | 100%                 | In accordance<br>with applicable<br>device<br>specification | 100%                 | 3.4.9.1 |

| Percent defective<br>allowable (PDA)<br>calculation                                                                                                                                                | 5 percent<br>(subgroup 1,<br>table IV)<br>3 percent<br>functional<br>parameters at<br>25°C<br>(subgroup 7<br>table IV) | All<br>lots          | 5 percent<br>(subgroup 1,<br>table IV)                      | All<br>lots          | 3.4.9.1 |

| Final electrical test<br>a. Static tests<br>(1) 25°C (subgroup 1,<br>table IV)<br>(2) Maximum and<br>minimum rated<br>operating temp.<br>(subgroup 2, 3,<br>(table IV)<br>b. Dynamic or functional | In accordance<br>with applicable<br>device<br>specification                                                            | 100%<br>100%<br>100% | In accordance<br>with applicable<br>device<br>specification | 100%<br>100%<br>100% | 3.4.11  |

| tests<br>(1) 25°C (subgroup 4,<br>or 7, table IV)<br>(2) Minimum and<br>maximum rated<br>operating temp.<br>(subgroup 5 and<br>6, or 8, table<br>IV)<br>c. Switching tests at                      |                                                                                                                        | 100%                 |                                                             | 100%                 |         |

| 6, or 8, table<br>IV)                                                                                                                                                                              |                                                                                                                        | 100%                 |                                                             | 100%                 |         |

#### TABLE III. <u>Device screening</u> - Continued.

| Screen                                                                      | Class level S  |        | Class level B | Reference<br>paragraph |        |

|-----------------------------------------------------------------------------|----------------|--------|---------------|------------------------|--------|

|                                                                             | Method         | Reqmt. | Method        | Reqmt.                 |        |

| Seal<br>Fine<br>Gross                                                       | 1014           | 100%   | 1014          | 100%                   | 3.4.8  |

| Radiographic                                                                | 2012 two views | 100%   |               |                        | 3.4.12 |

| Qualification or quality<br>conformance inspection<br>test sample selection | See 3.5        |        | See 3.5       |                        |        |

| External visual                                                             | 2009           | 100%   | 2009          | 100%                   | 3.4.13 |

3.4.2 <u>Internal visual inspection</u>. Internal visual inspection shall be performed to the requirements of method 2010, condition A for class level S devices and condition B for class level B devices. Devices awaiting preseal inspection, or other accepted, unsealed devices awaiting further processing shall be stored in a dry, inert, controlled environment until sealed.

Unless otherwise specified, at the manufacturer's option, test samples for group B, bond strength may be randomly selected prior to or following internal visual, prior to sealing provided all other specification requirements are satisfied (e.g., bond strength requirements shall apply to each inspection lot, bond failures shall be counted even if the bond would have failed internal visual exam).

The alternate procedure of 3.4.2.1 shall be used when any of the following criteria are met:

- a. Minimum horizontal geometry is less than three microns.

- b. Metallization consists of two or more levels.

- c. Opaque materials mask design features.

3.4.2.1 <u>Alternate procedures for class level B microcircuits</u>. Alternate procedures may be used on an optional basis on any microcircuit, provided that the conditions and limits of the alternate procedures are submitted to, and approved by the preparing activity, or the acquiring activity.

3.4.2.1.1 <u>Alternate procedures</u>. The deletions and the changes stated herein are allowable only if the requirements of alternate 1 or alternate 2 are met.

- Alternate 1: The deletions and the changes stated in 3.4.2.1.1a. are allowable for complex monolithic microcircuits for class level B product only if the requirements of 3.4.2.1.1.b and 3.4.2.1.1.c are imposed and any of the following conditions exists.

- 1. Minimum horizontal geometry is less than 3 micrometers (µm).

- 2. Interconnects consisting of two or more levels.

- 3. Opaque materials mask design features.

- a. For inspection of each microcircuit die, delete the inspection criteria of 3.1.1, 3.1.2, 3.1.3, 3.1.4, 3.1.5, 3.1.6, 3.1.7, and 3.2.5 of condition B of method 2010 and for use in conjunction with alternate procedures, add 3.1.1.1, 3.1.1.2, 3.1.1.6, 3.1.3, 3.1.4, and 3.2.5 to the low magnification inspection of method 2010.

- b. Temperature cycling (3.4.5). The minimum total number of temperature cycles shall be 50. The manufacturer may reduce the number of temperature cycles from 50 to the 10 required as part of normal screening based upon data justifying the reduction in temperature cycles approved by the preparing activity and an approved plan which shall include the following criteria:

- (1) Reduction of test must be considered separately for each wafer fabrication line and each die family.

- (2) The manufacturer shall demonstrate that the wafer fabrication line that produces product which will involve reduction of temperature cycles is capable and in process control.

- (3) The manufacturer shall perform a high magnification visual inspection on a small sample of devices (e.g., 5(0)) to monitor the process. This inspection may be performed at wafer level.

- c. Special electrical screening tests shall be applied to each microcircuit die at the wafer, individual die (chip) and packaged, or both, microcircuit level in accordance with the requirements of MIL-STD-883, method 5004, 3.3.2. The conditions and limits of the electrical tests (in table III format) shall be submitted to the preparing activity for approval and subsequently maintained on file with the qualifying activity. These special screens are in addition to the required electrical parametric tests which the device must pass and shall be designed to screen out devices with defects that were not inspected to the full criteria of 3.4.3 (internal visual). Due to the nature of these tests, they are not to be repeated as part of the qualification and quality conformance procedures.

- Alternate 2: The requirements and conditions for use of this alternate are contained in appendix A of method 5004. This option applies to both class level B and class level S microcircuits.

3.4.3 <u>Stabilization bake</u>. Stabilization bake is not required for class level S or class level B product unless specified in the device specification or drawing.

3.4.4 <u>Visual inspection for damage</u>. The manufacturer may inspect for damage after each screening step. Damaged devices shall be removed from the lot.

3.4.5 <u>Temperature cycling or thermal shock</u>. All devices shall be subjected to the requirements of temperature cycling or thermal shock. The device specifications or drawing shall specify which screen shall be employed. Temperature cycling shall be in accordance with MIL-STD-883, method 1010, condition C minimum. For class level B, this test may be replaced with thermal shock in accordance with MIL-STD- 883, method 1011, condition A minimum.

3.4.6 <u>Constant acceleration</u>. All devices shall be subjected to constant acceleration, in the Y<sub>1</sub> axis only, in accordance with MIL-STD-883, method 2001, condition E (minimum). Microcircuits which are contained in packages which have an inner seal or cavity perimeter of two inches or more in total length or have a package mass of five grams or more may be treated in accordance with provisions below as an alternate to this procedure. Delete test condition E and replace with test condition D. Unless otherwise specified, the stress level for large, monolithic microcircuit packages shall not be reduced below condition D. If the stress level specified is below condition D, the manufacture shall have data to justify this reduction and this data must be maintained and available for review by the preparing or acquiring activity. The minimum stress level allowed is condition A.

3.4.7 <u>Particle impact noise detection test (PIND)</u>. Testing to be performed in accordance with appendix A of MIL-PRF-38535, A.4.6.3. The PIND test may be performed in any sequence after temperature cycling and prior to final electrical test.

3.4.8 Seal (fine and gross leak) testing. For class level S devices seal testing may be performed in any sequence between the final electrical test and external visual, but it shall be performed after all shearing and forming operations on the terminals. For class level B devices, fine and gross seal test shall be performed separate or together in any sequence and order between 3.4.7 and 3.4.13 and they shall be performed after all shearing and forming operations on the terminals. When the 100 percent seal screen cannot be performed following all shearing or forming operations (i.e., flat packs, brazed lead packages, and chip carriers) the seal screen shall be done 100 percent prior to those shearing and forming operations and a sample test using sample size number of 45 (C = 0) shall be performed on each inspection lot following these operations to verify integrity. For devices with leads that are not glass-sealed and that have a lead pitch less than or equal to 1.27 mm (0.050 inch), the sample seal test shall be performed using an acceptance criteria of a quantity (accept number) of 15 (0). If sample fails the sample acceptance criteria, all devices in the inspection lot represented by the sample tested shall be subjected to and pass 100 percent fine and gross leak seal screens.

#### 3.4.9 Electrical measurements.

3.4.9.1 Interim (pre- and post-burn-in) electrical parameters. Interim (pre- and post-burn-in) electrical testing shall be performed when specified, to remove defective devices prior to further testing or to provide a basis for application of percent defective allowable (PDA) criteria when a PDA is specified. The PDA shall be 5 percent or one device, whichever is greater. This PDA shall be based, as a minimum, on failures from group A, subgroup 1 plus deltas (in cases where delta parameters are specified) with the parameters, deltas, and any additional subgroups (or subgroups tested in lieu of A-1) subject to the PDA as specified in the applicable device specification or drawing. If no device specification or drawing exists, subgroups tested shall at least meet those of the most similar device specification or Standard Microcircuit Drawing. In addition, for class level S the PDA shall be 3 percent (or one device, whichever is greater) based on failures from functional parameters measured at room temperature. For class level S screening, where an additional reverse bias burn-in is required, the PDA shall be based on the results of both burn-in tests combined. The verified failures after burn-in divided by the total number of devices submitted in the lot or sublot for burn-in shall be used to determine the percent defective for that lot, or sublot and the lot or sublot shall be accepted or rejected based on the PDA for the applicable device class. Lots and sublots may be resultive of pDA, or 20 percent, whichever is greater.

3.4.9.2 Pattern failures. Pattern failure criteria may be used as an option for class level B, provided that:

- a. Inspection lot size is less than 500 devices.

- b. Pre burn-in electrical testing is done.

3.4.9.2.1 <u>Pattern failures criteria</u>. A maximum number of pattern failures (failures of the same part type when the failures are caused by the same basic failure mechanism) shall apply as specified in the acquisition document. If not otherwise specified, the maximum allowable pattern failures shall be five. Accountability shall include burn-in through final electrical test.

3.4.9.2.2 <u>Pattern failure resubmission</u>. When the number of pattern failures exceeds the specified limits, the inspection lot shall be rejected. At the manufacturer's option, the rejected lot may be resubmitted to burn-in one time provided:

- a. The cause of the failure has been evaluated and determined.

- b. Appropriate and effective corrective action has been completed to reject all devices affected by the failure cause.

- c. Appropriate preventive action has been initiated.

3.4.10 <u>Burn-in</u>. Device burn-in shall be performed in accordance with the requirements of method 1015 conditions A, B, C, D, or E. Regardless of power level, devices shall be able to be burned-in at their maximum rated operating temperature. For devices whose maximum operating temperature is stated in terms of ambient temperature,  $T_A$ , table I of method 1015 applies. For devices whose maximum operating temperature is stated in terms of case temperature,  $T_C$ , and where the ambient temperature would cause  $T_J$  to exceed 200°C for class level B or 175°C for class level S, the ambient operating temperature may be reduced during burn-in from 125°C to a value that will demonstrate a  $T_J$  between 175°C and 200°C (for both class levels S and B) and  $T_C$  equal to or greater than 125°C without changing the test duration. Data supporting this reduction shall be available to the acquiring and qualifying activities upon request.

3.4.11 <u>Final electrical measurements</u>. Final electrical testing of microcircuits shall assure that the microcircuits tested meet the electrical requirements of the applicable device specification or drawing and shall include, as a minimum, the tests of group A, subgroups 1, 2, 3, 4 or 7, 5 and 6, or 8, and 9.

3.4.12 <u>Radiographic</u>. The radiographic screen may be performed in any sequence after PIND test and before external visual inspection. Only one view is required for flat packages and leadless chip carriers having lead (terminal) metal on four sides.

3.4.13 External visual inspection. All devices shall be inspected in accordance with MIL-STD-883, method 2009, prior to acceptance for shipment

3.5 <u>Qualification and quality conformance procedures</u>. Qualification and quality conformance shall be performed in accordance with A.4.4 qualification procedures and A.4.5 quality conformance inspection of appendix A of MIL-PRF-38535 except as modified herein. The qualification device shall be used for QCI testing in accordance with 3.5.3 herein, as well as for qualifying the process line. Life testing requirements shall follow the same criteria as burn-in (3.4.10 herein) for reduced temperature.

3.5.1 <u>Qualification testing</u>. Initial product process qualification shall be in accordance with MIL-STD-883 method 5005. Change to qualified product shall be addressed in accordance with MIL-STD-883, method 5005 and appendix A of MIL-PRF-38535, A.3.4.2. The SEC shall be used for group D inspection whenever practical; where the SEC cannot be used, another die may be used (for gate arrays, 60 percent or greater utilization required). Utilizing the qualification device the process monitor, the manufacturer shall demonstrate:

- a. Process control and stability.

- b. Process/device reliability.

- c. Design and simulation control.

3.5.1.1 <u>Detailed qualification test plan</u>. The manufacturer shall submit to the qualifying activity for approval a detailed qualification test plan to assure conformance to 3.5.1 herein. The test plan shall, as a minimum, define test groups, subgroups, conditions, and sampling plans in accordance with method 5005, as well as the tests to carry out 3.5.1.2, 3.5.1.3, and 3.5.1.4.

3.5.1.2 <u>Database test</u>. For qualification, at least five PM's per wafer (located in accordance with appendix II) shall be measured to ensure the establishment of a statistically valid database on which a decision can be made as to whether the manufacturer's process is stable and under control.

3.5.1.3 <u>Qualification device design and test plan</u>. Qualification device design and test plan to be used to qualify the manufacturing line shall be submitted to the qualifying activity for approval. The design must meet the minimum requirements of 3.3.4.2 herein. The test plan must include life test requirements. If a SEC is used as the qualification device, data demonstrating process reliability from lots processed within 12 months of qualification and that an on-going SEC program is in effect shall be submitted for qualifying activity review.

3.5.1.4 Design and simulation verification. Design and simulation verification shall be accomplished as follows:

- a. Design rule check (DRC) verification. DRC software shall be run on a design which contains known design rule violations.

- b. Electrical rule check (ERC) verification. ERC software shall be run on a design which contains known electrical rule violations (e.g., fan-out violations).

- c. Layout versus schematic (LVS) check.

- d. Correct by construction. If the manufacturers' design methodology is based on a "correct by construction" approach, distinct DRC, ERC, and LVS software is unnecessary and a, b, and c above do not apply. However, the manufacturer shall provide suitable data to demonstrate the correct performance of "correct by construction" software.

- e. Computer aided design (CAD) system control shall be in accordance with appendix I herein.

3.5.2 <u>Quality conformance inspection</u>. This procedure, as applicable to the microcircuit type and class, shall apply for all quality conformance inspection requirements. Subgroups within a group of tests may be performed in any sequence but individual tests within a subgroup (except group B, subgroup 2) shall be performed in the sequence indicated for groups B, C, D, and E tests herein. Where end-point electrical measurements are required for subgroups in groups B, C, D, and E testing herein, they shall be as specified in the applicable device specification or drawing. Where end-point measurements are required but no parameters have been identified in the acquisition document for this purpose, the final electrical parameters specified for 100 percent screening shall be used as end-point measurements. Electrical reject devices from the same inspection lot may be used for all subgroups when end-point measurements are not required.

3.5.2.1 <u>Radiation hardness</u>. Quality conformance inspection requirements for radiation hardness assured devices are in addition to the normal class level S and B requirements. Those requirements are detailed in table VIII (group E) herein. The radiation levels (M, D, P, L, R, F, G and H) are defined in appendix A of MIL-PRF-38535.

3.5.2.2 Quality conformance inspection. For class level B quality conformance inspection, each inspection lot (sublot) shall pass groups A, B, and E (when applicable) tests or be accepted in accordance with 3.5.3 herein and the periodic group C and D tests shall be in accordance with appendix A of MIL-PRF-38535. End point electrical parameters shall be as specified in 3.5.2.3 herein. For class level S, each QCI inspection lot shall be assembled in accordance with the class level S requirements of appendix A of MIL-PRF-38535. Quality conformance testing for class level S shall be in accordance with tables IV, V, VI, and VII herein.

3.5.2.3 <u>End point electrical parameters</u>. Where intermediate and end point electrical measurements are required for subgroups B, C, D, and E testing, they shall be as specified in the applicable device specification or drawing where required and when end point parameters have not been identified, group A, subgroup 1, 2, 3, 4 or 7, and 9 shall be used for end point measurements.

3.5.2.4 <u>Constant acceleration</u>. Constant acceleration shall be performed in accordance with method 2001, test condition E for all applicable subgroups except as allowed in accordance with 3.4.6, herein.

3.5.3 <u>Quality conformance testing</u>. Conformance testing shall be performed through the use of the identified quality conformance vehicles.

| Table IVGroup AActual deviceEach inspection lotTable VGroup BActual deviceEach inspection lotTable VIGroup CSEC or actual device3 monthsTable VIIGroup DSEC or actual device6 months | Quality conformance test |         | Quality conformance vehicle | Frequency           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------|-----------------------------|---------------------|

| Table VIII     Group E     Actual device     See MIL-PRF-38535. appendix A                                                                                                           | Table V                  | Group B | Actual device               | Each inspection lot |

|                                                                                                                                                                                      | Table VI                 | Group C | SEC or actual device        | 3 months            |

|                                                                                                                                                                                      | Table VII                | Group D | SEC or actual device        | 6 months            |

3.5.3.1 <u>Alternate group A method</u>. The alternate group A method below may be used provided that:

- a. Inspection lot size is less than 500 devices.

- b. Final electrical test shall assure that the electrical requirements of the device specification or drawing are met and shall include the tests of group A, subgroups 1, 2, 3, 4 or 7, 5 and 6 or 8, 9, as a minimum.

- c. All test software and procedures are under document control.

3.5.3.1.1 In-line verification testing.

- a. For each test set up (and operator for manual testing), production runs correlation unit to assure that the accuracy requirements of MIL-STD-883 4.5.2 are being met.

- b. Testing is performed using the verified set up.

- c. At the completion of testing utilizing the verified set up (not to exceed 8 hours and at the change of operators) a separate party (QA or QA designate) then verifies the production testing by:

- (1) Checking visually to verify that the correct fixture, equipment, software, and procedure(s) were used.

- (2) Actual testing of controlled known good device utilizing the fixtures, set ups, software and procedures that were used by production. Variables data for all required group A tests shall be read and recorded for the controlled unit. This data shall be maintained with the lot.

#### TABLE IV. Group A electrical test. 1/

| Subgroup | Parameters <u>2/3/4/5/</u>                                           | Quantity/<br>acceptance number |

|----------|----------------------------------------------------------------------|--------------------------------|

| 1        | Static test at +25°C                                                 | 116/0                          |

| 2        | Static tests at maximum rated operating temperature                  | 116/0                          |

| 3        | Static tests at minimum rated operating temperature                  | 116/0                          |

| 4        | Dynamic test at +25°C                                                | 116/0                          |

| 5        | Dynamic tests at maximum rated operating temperature                 | 116/0                          |

| 6        | Dynamic tests at minimum rated operating temperature                 | 116/0                          |

| 7        | Functional test at +25°C                                             | 116/0                          |

| 8        | Functional tests at maximum and minimum rated operating temperatures | 116/0                          |

| 9        | Switching tests at +25°C                                             | 116/0                          |

| 10       | Switching tests at maximum rated operating temperature               | 116/0                          |

| 11       | Switching tests at minimum rated operating temperature               | 116/0                          |

1/ The specific parameters to be included for tests in each subgroup shall be as specified in the applicable acquisition document. Where no parameters have been identified in a particular subgroup or test within a subgroup, no group A testing is required for that subgroup or test to satisfy group A requirements.

2/ At the manufacturer's option, the applicable tests required for group A testing (see 1/) may be conducted individually or combined into sets of tests, subgroups (as defined in table I), or sets of subgroups. However, the manufacturer shall predesignate these groupings prior to group A testing. Unless otherwise specified, the individual tests, subgroups, or sets of tests/subgroups may be performed in any sequence.

- 3/ The sample plan (quantity and accept number) for each test, subgroup, or set of tests/subgroups as predesignated in 2/ above, shall be 116/0.

- 4/ A greater sample size may be used at the manufacturer's option; however, the accept number shall remain at zero. When the (sub)lot size is less than the required sample size, each and every device in the (sub)lot shall be inspected and all failed devices removed from the (sub)lot for final acceptance of that test, subgroup, or set of tests/subgroups, as applicable.

- 5/ If any device in the sample fails any parameter in the test, subgroup, or set of tests/subgroups being sampled, each and every additional device in the (sub)lot represented by the sample shall be tested on the same test set-up for all parameters in that test, subgroup, or set of tests/subgroups for which the sample was selected, and all failed devices shall be removed from the (sub)lot for final acceptance of that test, subgroup, or set of tests/subgroups, as applicable. For class level S only, if this testing results in a percent defective greater than 5 percent, the (sub)lot shall be rejected, except that for (sub)lots previously unscreened to the tests that caused failure of this percent defective, the (sub)lot may be accepted by resubmission and passing the failed individual tests, subgroups, or set of tests/subgroups, as applicable, using a 116/0 sample.

| Subgroup | Cla<br>lev |   | Test                                                                                               | MIL                | STD-883                             | quantity/(accept<br>number)<br>or sample<br>size number,<br>accept number | Referenced paragraph |

|----------|------------|---|----------------------------------------------------------------------------------------------------|--------------------|-------------------------------------|---------------------------------------------------------------------------|----------------------|

|          | S          | В |                                                                                                    | Method             | Condition                           |                                                                           |                      |

| 1        | Х          | х | Physical dimensions                                                                                | 2016               |                                     | 2 (0)                                                                     |                      |

| 2        | Х          |   | Particle impact noise detection test                                                               | 2020               | A or B                              | 15 (0)                                                                    | 3.4.7                |

| 3        | Х          | Х | Resistance to solvents                                                                             | 2015               |                                     | 3 (0)                                                                     |                      |

| 4        | Х          | х | Internal visual and mechanical                                                                     | 2014               |                                     | 1 (0)                                                                     | 3.4.2                |

| 5        | Х          | x | Bond strength<br>a. Thermocompression<br>b. Ultrasonic or<br>wedge<br>c. Flip-chip<br>d. Beam lead | 2011               | C or D<br>C or D<br>F<br>H          | 2 (0)                                                                     |                      |

| 6        | х          | х | Die shear strength or<br>substrate attach<br>strength                                              | 2019<br>or<br>2027 |                                     | 2 (0)                                                                     |                      |

| 7        | х          | х | Solderability                                                                                      | 2003               | Solder<br>temperature<br>245°C ±5°C | 1 (0)                                                                     |                      |

| 8        | х          | х | Seal<br>a. Fine<br>b. Gross                                                                        | 1014               |                                     | Sample size<br>number = 15<br>C = 0                                       | 3.4.8                |

# TABLE V. Group B testing.

| Subgroup | Cla<br>lev |   | Test                                         | MI           | STD-883                                                       | Sample size<br>number,<br>accept number | Referenced paragraph |

|----------|------------|---|----------------------------------------------|--------------|---------------------------------------------------------------|-----------------------------------------|----------------------|

|          | S          | В |                                              | Method       | Condition                                                     |                                         |                      |

| 1        | Х          | Х | External                                     | 2009         |                                                               | Sample size<br>number = 15              | 3.4.13               |

|          | х          | х | Temperature cycling                          | 1010         | C<br>100 cycles<br>minimum                                    | C = 0                                   | 3.4.5                |

|          | х          | х | Mechanical shock or<br>constant acceleration | 2002<br>2001 | B, Y1 axis<br>E, Y1 axis                                      |                                         | 3.4.6                |

|          | х          | х | Seal (fine and gross)                        | 1014         |                                                               |                                         | 3.4.8                |

|          | х          |   | Radiographic                                 | 2012         | Y axis                                                        |                                         | 3.4.12               |

|          | х          | х | Visual examination                           |              | In accordance<br>with visual<br>criteria of<br>method 1010.   |                                         |                      |

|          | х          | х | End point electrical                         |              | As specified<br>in accordance<br>with device<br>specification |                                         | 3.5.2.3              |

| 2        | х          | Х | Steady-state life test                       | 1005         | 1,000 hours<br>at +125°C<br>minimum                           | Sample size<br>number = 22<br>C = 0     | 3.5.2.3              |

|          |            |   | End point electrical                         |              | As specified<br>in accordance<br>with device<br>specification |                                         |                      |

# TABLE VI. Group C testing.

# TABLE VII. Group D testing.

| Subgroup | Class | 5 | Test                                                                           | MIL-STD-883 |           | Quantity/<br>accept<br>number                               | Referenced paragraph |

|----------|-------|---|--------------------------------------------------------------------------------|-------------|-----------|-------------------------------------------------------------|----------------------|

|          | S     | В |                                                                                | Method      | Condition |                                                             |                      |

| 1        | х     | x | Internal water vapor<br>content<br>5000 PPM maximum water<br>content at +100°C | 1018        |           | 3 devices<br>(0 failures)<br>or<br>5 devices<br>(1 failure) |                      |

| 2        | Х     | Х | Moisture resistance                                                            | 1004        |           | 5 (0)                                                       |                      |

| 3        | Х     | Х | Salt atmosphere                                                                | 1009        |           | 5 (0)                                                       |                      |

| Test                                              | Ν      | MIL-STD-883                                                   |                               | Class level S                     |                               | vel B                    |

|---------------------------------------------------|--------|---------------------------------------------------------------|-------------------------------|-----------------------------------|-------------------------------|--------------------------|

|                                                   | Method | Condition                                                     | Quantity/<br>accept<br>number | Notes                             | Quantity/<br>accept<br>number | Notes                    |

| Subgroup 1 2/                                     |        |                                                               |                               |                                   |                               |                          |

| Neutron irradiation<br>a. Qualification<br>b. QCI | 1017   | +25°C                                                         | a. 11 (0)<br>b. 11 (0)        | <u>3</u> /<br><u>3</u> /          | a. 11 (0)<br>b. 11 (0)        | <u>4</u> /<br><u>4</u> / |

| Endpoint electrical<br>parameters                 |        | As specified in<br>accordance with<br>device<br>specification |                               |                                   |                               |                          |

| Subgroup 2 5/                                     |        |                                                               |                               |                                   |                               |                          |

| Steady-state total dose irradiation               | 1019   | +25°C<br>Maximum supply<br>voltage                            |                               |                                   |                               |                          |

| a. Qualification                                  |        |                                                               | a. 4 (0)<br>2 (0)             | a. <u>6</u> /<br>8/               | a. 22 (0)                     | <u>7</u> /               |

| b. QCI                                            |        |                                                               | b. 4 (0)<br>2 (0)             | <u>8</u> /<br>b. <u>6</u> /<br>8/ | b. 22 (0)                     | <u>7</u> /               |

| Endpoint electrical<br>parameters                 |        | As specified in<br>accordance with<br>device<br>specification | 2 (0)                         | <u> </u>                          |                               |                          |

# TABLE VIII. Group E (radiation hardness assurance tests). 1/

- 1/ Parts used for one subgroup test may not be used for other subgroups but may be used for higher levels in the same subgroup. Total exposure shall not be considered cumulative unless testing is performed within the time limits of the test method.

- 2/ Waive neutron test for MOS IC devices except where neutron susceptibility is less than 10<sup>13</sup> neutrons/cm<sup>2</sup> (e.g., charge coupled devices, BICMOS, ect.). Where testing is required, the limit for neutron fluence shall be 2x10<sup>12</sup> neutrons/cm<sup>2</sup>.

- 3/ Per wafer lot. If one part fails, seven additional parts may be added to the test sample with no additional failures allowed, 18(1).

- 4/ Per inspection lot. If one part fails, seven additional parts may be added to the test sample with no additional failures allowed, 18(1).

- 5/ Class level B devices shall be inspected using either the class level B quantity/accept number criteria as specified, or by using the class level S criteria on each wafer.

- 6/ Per wafer for device types with less than or equal to 4,000 equivalent transistors/chip selected from the wafer at a radius approximately equal to two-thirds of the wafer radius, and spaced uniformly around this radius.

- <u>7</u>/ Per inspection lot. If one part fails, 16 additional parts may be added to the test sample with no additional failures allowed, 38(1).

- 8/ Per wafer for device types with greater than 4,000 equivalent transistor/chip selected from the wafer at a radius approximately equal to two-thirds of the wafer radius and spaced uniformly around this radius.

- (3) The verifying party shall stamp or sign the lot traveler to attest that the above data meets the test requirements and that all of the above items were performed and were found to be acceptable.

- (4) Failure of the verification test shall require, as a minimum, engineering to perform a detailed review of hardware/software/set up and parts. If engineering locates the problem, a one time only 100 percent retest to all group A requirements for all devices that were under consideration for acceptance shall be required. If the engineering review does not locate the problem, the verification unit shall undergo failure analysis before retesting the lot.

- (a) If failure analysis locates the problem, the entire group of devices being considered for acceptance at the time of the failure may be retested for appropriate subgroup(s) acceptance one time only by repeating this group A method.

- (b) If the failure analysis does not specifically locate the problem, the lot may be considered for acceptance one time only by 100 percent retesting of all the devices of the group A requirements and by repeating this group A method.

3.6 <u>Disposition of samples</u>. Disposition of sample devices in groups A, B, C, D, and E testing shall be in accordance with the applicable device specification.

3.7 Substitution of test methods and sequence.

3.7.1 Accelerated qualification or quality conformance testing for class level B. When the accelerated temperature/time test conditions of condition F of method 1005 are used for any operating life or steady-state reverse bias subgroups on a given sample for purposes of qualification or quality conformance inspection, the accelerated temperature/time test conditions shall be used for all those named subgroups. When these accelerated test conditions are used for burn-in screening test (test condition F of method 1015) or stabilization bake for devices with aluminum/gold metallurgical systems (any test temperature above the specified maximum rated junction temperature) for any inspection lot, it shall be mandatory that they also be used for the operating life, and steady-state reverse bias tests of method 5005, or herein as applicable, or qualification or quality conformance inspection. Qualification and quality conformance inspection may be performed using accelerated conditions on inspection lots that have been screened using normal test conditions.

3.8 <u>Test results</u>. Unless otherwise specified, test results that are required by the applicable acquisition document shall be reported in accordance with the general requirements of appendix A of MIL-PRF-38535 (see A.4.7).

- 4. <u>SUMMARY</u>. The following details shall be specified in the applicable device specification:

- a. Procedure paragraph if other than 3.1, and device class.

- b. Sequence of test, sample size, test method, and test condition where not specified, or if other than specified.

- c. Test condition, limit, cycles, temperatures, axis, etc., where not specified, or if other than specified (see 3).

- d. Acceptance procedure or sample size and acceptance number, if other than specified.

- e. Initial and interim (pre and post burn-in) electrical parameters for group A.

- f. Electrical parameters for groups B, C, D, and E end point measurements, where applicable.

- g. Burn-in test conditions (see table III) and burn-in test circuit.

- h. Delta parameter measurements or provisions for PDA including procedures for traceability or provisions for pattern failure limits including accountable parameters, test conditions, and procedures for traceability, where applicable.

- i. Final electrical measurements.

- j. Constant acceleration level.

- k. Requirements for failure analysis.

- I. Requirements for data recording and reporting if other than specified in 3.8.

- m. Restriction or resubmission of failed lots where applicable.

- n. Steady-state life test circuits, where not specified or if other than specified.

- o. Parameters on which delta measurements are required.

- p. Wafer travelers shall be used to record completion of each requirement of 3.4.2.1.1.

#### APPENDIX I

#### COMPUTER AIDED DESIGN (CAD) CERTIFICATION REQUIREMENTS

#### 10. SCOPE.

10.1 <u>Scope</u>. Additional line certification requirements. This appendix defines additional line certification requirements. The answers to the questions in this appendix shall be provided to the qualifying activity for approval. The manufacturer shall have the following additional information on file and available for review.

- a. Design/layout rules as a manufacturer's controlled document.

- b. A list of the cells in the manufacturer's cell library, cell performance data, and simulation verification data, if applicable.

- c. Process monitor design used by the manufacturer.

- d. Standard evaluation circuit implementation used by the manufacturer for qualification and qualification conformance inspection (QCI).

- e. JEDEC benchmark macro set (see JEDEC standards 12, 12-1, 12-2, and 12-3), delay simulation data, if applicable.

- f. A list of the software packages (including names and current version) used by the manufacturer in the circuit design process.

- g. Design rule check (DRC) verification. DRC software shall be run on a design which contains known design rule violations.

- h. Electrical rule check (ERC) verification. ERC software shall be run on a design which contains known electrical rule violations.

- i. Layout versus schematic (LVS) checker.

- j. If the manufacturer's design methodology is based on the "correct by construction" approach, distinct DRC, ERC, and LVS software is unnecessary and may not exist. In this case, the provisions of g., h., and i. do not apply. Instead, the manufacturer will provide suitable example data to demonstrate the correct performance of "correct by construction" software.

10.2 <u>Functional delay simulation</u>. To be retained by manufacturer; simulation to be derived from each final application specific electrical design and layout (i.e., post-routed design). Simulation will be done using actual delays and parasitics computed from the placement and layout of the device as it will be fabricated. Actual delays shall include the contribution associated with the delay through the gate, as well as the contribution due to actual metal capacitance and device loading on the output(s). Using these actual delays, the application specific integrated circuit (ASIC) designer shall insure that there are no timing violations remaining in the circuit. Such timing violations shall include, but not be limited to, setup, hold, critical delay path, and circuit race conditions due to variations in process, temperature and supply voltage. Simulation at the two worst case extremes (temperature, process, radiation (if applicable) and supply voltage) shall be identical with respect to circuit operation (final state of each signal in each clock cycle must be identical).

#### APPENDIX I

10.3 Layout verification. The manufacturer shall retain the results of full mask level design rule checks, electrical rule checks, and connectivity checks (see 10.1) for each application specific design. Rule checking will encompass the rules set provided under 10.1 herein. The manufacturer will explain any rules not checked and all error reports produced by the checker. The LVS checker will ensure that the layout matches exactly the schematic simulated by the ASIC designer. Final layout verification results will not be required if the manufacturer's design methodology is "correct by construction." In this case, the manufacturer will explain the methodology and rules used, as well as any rules not checked and all error reports which were not corrected during construction of design.

10.4 <u>Power routing simulation</u>. To be retained by manufacturer; derived from each final application specific electrical design and layout. The worst case simulation of power buses shall show that at no time shall the localized bus current density exceed specification for allowable current density of the power bus material. In addition, at no point in the power bus shall voltage levels exceed design goals for IR drop values from the respective supply. Power routing simulation must be based upon actual placement of cells within the array. Such a simulation may be driven by Monte Carlo methods, or in conjunction with a digital simulator using the selected set of test vectors.

10.5 <u>Cell design and simulation qualification</u>. Cell design and simulation qualification shall be accomplished in a two step procedure consisting of:

- a. Parameter verification/simulation verification, and

- b. Functional verification.

A chip or set of chips, called the cell test chip set, shall be designed to provide access to a set of cells to test performance characteristics. The cell test chip set design must be submitted to the qualifying activity for approval prior to use. The cell test chip shall include as a minimum:

#### Description

Inverter

#### 4-input NAND

2-input AND into 3-input NOR

D latch with active low reset

JK flip-flop with active low reset

TTL input buffer

CMOS input buffer

Output buffer

Three-state I/O buffer with pull-up

#### APPENDIX I

The intent is to get a representative cross section of cell types (i.e., combinational, sequential, input, output). Chains shall be formed (when necessary to avoid rise and fall time measurement problems) and actual performance data over the full operating range shall be taken (a provision to extract for multiplexing and I/O buffer delay shall be included). Delay versus metal wire length and fanout for the above cells shall be determined. The actual performance data shall be submitted to the qualifying activity along with computer program simulation results. The actual performance data must be within the limits predicted by the simulation. If multipliers are used to extrapolate performance at the temperature extremes, such multipliers shall be verified as well.

In addition, for the above cells, a set of pins shall be provided on the test chip for observability. This will enable verification of functionality of the cells. (Note: Inputs and outputs may be multiplexed).

10.6 <u>CAD routing and post routing simulation</u>. A chip or set of chips shall be submitted for approval and used to qualify the manufacturer's ability to perform routing and to accurately predict post routing performance. The manufacturer must submit to the qualifying activity:

- a. The actual measured performance data for each function over temperature and voltage.

- b. The computer simulation performance prediction.

The two results will remain on file and the actual measured performances must fall between the simulation extremes.

20. APPLICABLE DOCUMENTS. (This section is not applicable to this document.)

#### 30. CERTIFICATION QUESTIONS.

- 30.1 Cell libraries.

- a. Who is the source for your cell libraries?

Own organization?

Work station vendors?

Outside commercial vendors?

Universities?

- b. What verification or certification is done for cell libraries, including those obtained from outside organizations? Are macrocells implemented in silicon and verified for functionality and performance limits via actual hardware test? Is only software simulation performed?

- c. How are cell libraries controlled (e.g., level of documentation, maintenance and revisions, specifications, additions)?

- d. Provide company-approved cell library.

- e. Identify those implemented and tested in silicon.

- f. Is a designer allowed to tailor a macrocell or "roll his own" for a certain application? If so, how is the resulting macro tested to insure there are no problems?

## APPENDIX I

#### 30.2 Design process.

a. Who does and who approves the various levels of design?

Requirements definition? Detail function definition? Detail design (e.g., gate level design)? Layout and mask generation?

- b. What automatic aids are used for refinement from each design level to the next?

- c. What automatic aids are used for verifying the refinement at each level (e.g., automatic checking of layout versus schematic)?

- d. How is automatic placement and routing software verified and certified for use?

#### 30.3 Simulation.

a. What simulators are used for:

Process simulation (e.g., SUPREME-II)?

Circuit simulation (e.g., SPICE, SCEPTRE)?

Gate level simulation (e.g., LASAR HITS)?

Switch level simulation?

Behavior/function simulation?

Dynamic timing analysis (to include actual delays due to placement and routing?

- b. How are the above simulators verified? Are benchmarks used, and if so, what are these benchmarks?

- c. Are the simulation results periodically checked against actual silicon test data (to complete the loop)?

# 30.4 Test.

a. What test tools are used for:

Automatic test vector generation?

Fault simulation?

Insertion of design-for-testability/built-in-test features? (And are they integrated with the design process?)

b. Who is responsible for test generation:

Foundry?

Customer?

Designer?

c. If test vectors are not generated by the foundry, are the submitted vectors evaluated by the foundry to determine the percentage of faults detected?

#### APPENDIX I

#### 30.5 Design rule checking.

a. Are design constraints enforced by the customers or management, such as:

Synchronous designs only?

Use of an approved set of cells/macrocells only?

Conservative use of electrical and switching limits?

Is the designer able to obtain waivers?

b. What design rule checkers (DRCs) are used for:

Physical rule checks (e.g., minimum spacing)?

Electrical rule checks (e.g., max current density, fanout restrictions)? Timing rule checks (e.g., worst-case timing paths)? Logical rule checks (e.g., unclocked feedback paths)?

- c. Is each design subjected to the above DRCs?

- d. How can the DRC software be shown to "work as advertised?"

- e. If "correct by construction" techniques are used, what procedure is used, how is "correctness" assured?

#### 30.6 Software control.

a. What are the sources of design and test software?

Own organization?

Workstation vendors?

Outside commercial vendors?

Universities?

b. How is design and test software approved and controlled:

Frequency of major/minor revision?

Trouble reports?

**Regression testing?**

c. What commercial CAD/CAE work stations or packages are used (e.g., MENTOR, Daisy, Silvar-Lisco)? Are modifications to any of the software packages permitted?

#### APPENDIX I

30.7 How is interface with foundries and customers, or both done?

Data formats?

Media (e.g., magtapes, modems, DDN/Arpanet)?

Qualification of foundry via test chips?

Are evaluation chips available for customers to assess performance?

30.8 Who tests the chips?

At wafer level?

After packaging?

Burn-in?

Life testing?

What automatic test equipment types are used?

30.9 Masks.

- a. What are the procedures for mask making, inspection, verification, and repair?

- b. Is the design transferred to the fab house via an actual mask set or via software?

- c. If design transfer is via software, what are the procedures used to verify the mask design?

#### 30.10 Wafer acceptance.

- a. What wafer inspection/accept-reject criteria are currently used (i.e., how is process control/stability demonstrated)?