Notice of Change

This document and process conversion measures necessary to comply with this revision shall be completed by 30 September 2003

# INCH-POUND

MIL-STD-883E NOTICE 5 7 March 2003

# DEPARTMENT OF DEFENSE

### TEST METHOD STANDARD MICROCIRCUITS

### TO ALL HOLDERS OF MIL-STD-883E:

1. THE FOLLOWING TEST METHODS OF MIL-STD-883E HAVE BEEN REVISED AND SUPERSEDE THE TEST METHODS LISTED:

| NEW METHOD | DATE          | SUPERSEDED METHOD | DATE             |   |

|------------|---------------|-------------------|------------------|---|

| 1019.6     | 07 March 2003 | 1019.5            | 1 December 1997  | - |

| 2019.7     | 07 March 2003 | 2019.6            | 18 December 2000 |   |

# 2. THE FOLLOWING PAGES OF MIL-STD-883E HAVE BEEN REVISED AND SUPERSEDE THE PAGES LISTED:

| METHOD  | NEW PAGE | DATE             | SUPERSEDED PAGE | DATE                     |

|---------|----------|------------------|-----------------|--------------------------|

|         | iii      | 31 December 1996 | iii             | REPRINTED WITHOUT CHANGE |

|         | iv       | 07 March 2003    | iv              | 18 December 2000         |

|         | V        | 05 November 1999 | V               | REPRINTED WITHOUT CHANGE |

|         | vi       | 18 December 2000 | vi              | REPRINTED WITHOUT CHANGE |

| 1014.10 | 5        | 14 March 1995    | 5               | REPRINTED WITHOUT CHANGE |

|         | 6        | 07 March 2003    | 6               | 14 March 1995            |

| 1018.3  | 1        | 07 March 2003    | 1               | 18 December 2000         |

|         | 2        | 18 December 2000 | 2               | REPRINTED WITHOUT CHANGE |

| 2010.10 | 3        | 07 March 2003    | 3               | 27 July 1990             |

|         | 4        | 07 March 2003    | 4               | 27 July 1990             |

|         | 5        | 07 March 2003    | 5               | 27 July 1990             |

|         | 6        | 07 March 2003    | 6               | 27 July 1990             |

|         | 39       | 07 March 2003    | 39              | 27 July 1990             |

|         | 39a      | 07 March 2003    | 39a             | new page                 |

|         | 39b      | 07 March 2003    | 39b             | new page                 |

|         | 40       | 18 December 2000 | 40              | REPRINTED WITHOUT CHANGE |

|         | 49       | 07 March 2003    | 49              | 27 July 1990             |

|         | 50       | 27 July 1990     | 50              | REPRINTED WITHOUT CHANGE |

AMSC N/A <u>DISTRIBUTION STATEMENT A</u>. Approved for public release; distribution is unlimited. FSC 5962

# 3. RETAIN THIS NOTICE AND INSERT BEFORE TABLE OF CONTENTS.

4. Holders of MIL-STD-883E will verify that page changes, additions, and corrections indicated above have been entered. This notice page will be retained as a check sheet. This issuance, together with appended pages, is a separate publication. Each notice is to be retained by stocking points until the military standard is completely revised or canceled.

NOTE: The margins of this notice are marked with asterisks to indicate where changes (additions, modifications, corrections, deletions) from the previous notice were made. This was done as a convenience only and the Government assumes no liability whatsoever for any inaccuracies in these notations. Bidders and contractors are cautioned to evaluate the requirements of this document based on the entire content irrespective of the marginal notations and relationship to the last previous notice.

### CONCLUDING MATERIAL

Custodians:

Army - CR Navy - EC Air Force - 11 NASA-NA DLA - CC

Review activities Army - AR, MI, SM Navy - OS, SH, TD, AS, CG, MC Air Force - 19, 99 Preparing activity: DLA - CC

(Project 5962-1943)

# CONTENTS

# PARAGRAPH

# Page

| 1.<br>1.1<br>1.2                             | SCOPE<br>Purpose<br>Intended use of or reference to MIL-STD-883                                                                              | 1                      |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 2.<br>2.1<br>2.2<br>2.3<br>2.4               | APPLICABLE DOCUMENTS<br>General<br>Government documents<br>Non-Government publications<br>Order of precedence                                | 3<br>3<br>4            |

| 3.<br>3.1                                    | ABBREVIATIONS, SYMBOLS, AND DEFINITIONS<br>Abbreviations, symbols, and definitions                                                           |                        |

| 4.<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | GENERAL REQUIREMENTS<br>Numbering system<br>Test results<br>Test sample disposition<br>Orientation<br>Test conditions<br>General precautions | 8<br>9<br>9<br>9<br>12 |

| 5.                                           | DETAIL REQUIREMENTS                                                                                                                          | 15                     |

| 6.                                           | NOTES                                                                                                                                        | 16                     |

# FIGURES

### FIGURE

| 1. | Orientation of noncylindrical microelectronic devices to |    |

|----|----------------------------------------------------------|----|

|    | direction of applied force                               | 10 |

| 2. | Orientation of cylindrical microelectronic device to     |    |

|    | direction of applied force                               | 11 |

# TEST METHODS

| METHOD NO. | ENVIRONMENTAL TESTS                                                |

|------------|--------------------------------------------------------------------|

| 1001       | Barometric pressure, reduced (altitude operation)                  |

| 1002       | Immersion                                                          |

| 1003       | Insulation resistance                                              |

| 1004.7     | Moisture resistance                                                |

| 1005.8     | Steady state life                                                  |

| 1006       | Intermittent life                                                  |

| 1007       | Agree life                                                         |

| 1008.2     | Stabilization bake                                                 |

| 1009.8     | Salt atmosphere (corrosion)                                        |

| 1010.7     | Temperature Cycling                                                |

| 1011.9     | Thermal shock                                                      |

| 1012.1     | Thermal characteristics                                            |

| 1013       | Dew point                                                          |

| 1014.10    | Seal                                                               |

| 1015.9     | Burn-in test                                                       |

| 1016       | Life/reliability characterization tests                            |

| 1017.2     | Neutron irradiation                                                |

| 1018.3     | Internal water-vapor content                                       |

| 1019.6     | Ionizing radiation (total dose) test procedure                     |

| 1020.1     | Dose rate induced latchup test procedure                           |

| 1021.2     | Dose rate upset testing of digital microcircuits                   |

| 1022       | Mosfet threshold voltage                                           |

| 1023.2     | Dose rate response of linear microcircuits                         |

| 1030.1     | Preseal burn-in                                                    |

| 1031       | Thin film corrosion test                                           |

| 1032.1     | Package induced soft error test procedure (due to alpha particles) |

| 1033       | Endurance life test                                                |

| 1034       | Die penetrant test (for plastic devices)                           |

MECHANICAL TESTS

| 2001.2                      | Constant acceleration                                          |

|-----------------------------|----------------------------------------------------------------|

| 2002.4                      | Mechanical shock                                               |

| 2003.7                      | Solderability                                                  |

| 2004.5                      | Lead integrity                                                 |

| 2005.2                      | Vibration fatigue                                              |

| 2006.1                      | Vibration noise                                                |

| 2007.3                      | Vibration, variable frequency                                  |

| 2008.1                      | Visual and mechanical                                          |

| 2009.9                      | External visual                                                |

| 2010.10                     | Internal visual (monolithic)                                   |

| 2010.10<br>2011.7<br>2012.7 | Bond strength (destructive bond pull test)<br>Radiography      |

| 2013.1                      | Internal visual inspection for DPA                             |

| 2014                        | Internal visual and mechanical                                 |

| 2015.13                     | Resistance to solvents                                         |

| 2016                        | Physical dimensions                                            |

| 2017.7                      | Internal visual (hybrid)                                       |

| 2018.3                      | Scanning electron microscope (SEM) inspection of metallization |

| 2019.7                      | Die shear strength                                             |

| 2020.7                      | Particle impact noise detection test                           |

Supersedes page iv of Notice 4 of MIL-STD-883E

### TEST METHODS

| METHOD NO. | MECHANICAL TESTS |

|------------|------------------|

|            |                  |

- 2021.3 Glassivation layer integrity Wetting balance solderability 2022.2

- 2023.5 Nondestructive bond pull

- Lid torque for glass-frit-sealed packages 2024.2

- Adhesion of lead finish 2025.4

- Random vibration 2026

- 2027.2 Substrate attach strength

- Pin grid package destructive lead pull test 2028.4

- Ceramic chip carrier bond strength 2029

- 2030 Ultrasonic inspection of die attach

- Flip chip pull-off test 2031.1

- 2032.1 Visual inspection of passive elements

- 2035 Ultrasonic inspection of TAB bonds

# ELECTRICAL TESTS (DIGITAL)

| 3001.1 | Drive source, dynamic                                                |

|--------|----------------------------------------------------------------------|

| 3002.1 | Load conditions                                                      |

| 3003.1 | Delay measurements                                                   |

| 3004.1 | Transition time measurements                                         |

| 3005.1 | Power supply current                                                 |

| 3006.1 | High level output voltage                                            |

| 3007.1 | Low level output voltage                                             |

| 3008.1 | Breakdown voltage, input or output                                   |

| 3009.1 | Input current, low level                                             |

| 3010.1 | Input current, high level                                            |

| 3011.1 | Output short circuit current                                         |

| 3012.1 | Terminal capacitance                                                 |

| 3013.1 | Noise margin measurements for digital microelectronic devices        |

| 3014   | Functional testing                                                   |

| 3015.7 | Electrostatic discharge sensitivity classification                   |

| 3016   | Activation time verification                                         |

| 3017   | Microelectronics package digital signal transmission                 |

| 3018   | Crosstalk measurements for digital microelectronic device packages   |

| 3019.1 | Ground and power supply impedance measurements for digital micro     |

| 3020   | High impedance (off-state) low-level output leakage current          |

| 3021   | High impedance (off-state) high-level output leakage current         |

| 3022   | Input clamp voltage                                                  |

| 3023.1 | Static latch-up measurements for digital CMOS microelectronic device |

| 3024   | Simultaneous switching noise measurements for digital microelectron  |

|        | ELECTRICAL TESTS (LINEAR)                                            |

| 4001.1 | Input offset voltage and current and bias current                    |

| 4002.1 | Phase margin and slew rate measurements                              |

| 4003.1 | Common mode input voltage range                                      |

|        | Common mode rejection ratio                                          |

|        | Supply voltage rejection ratio                                       |

- or digital microelectronics device packages rrent

- urrent

- ectronic devices

- microelectronic devices

- Supply voltage rejection ratio

- 4004.1 Open loop performance

- 4005.1 Output performance

- Power gain and noise figure 4006.1

- Automatic gain control range 4007

# TEST METHODS

| METHOD NO. | TEST PROCEDURES                                                                      |

|------------|--------------------------------------------------------------------------------------|

| 5001       | Parameter mean value control                                                         |

| 5002.1     | Parameter distribution control                                                       |

| 5003       | Failure analysis procedures for microcircuits                                        |

| 5004.10    | Screening procedures                                                                 |

| 5005.13    | Qualification and quality conformance procedures                                     |

| 5006       | Limit testing                                                                        |

| 5007.6     | Wafer lot acceptance                                                                 |

| 5008.9     | Test procedures for hybrid and multichip microcircuits                               |

| 5009.1     | Destructive physical analysis                                                        |

| 5010.3     | Test procedures for custom monolithic microcircuits                                  |

| 5011.4     | Evaluation and acceptance procedures for polymeric adhesives.                        |

| 5012.1     | Fault coverage measurement for digital microcircuits.                                |

| 5013       | Wafer fabrication control and wafer acceptance procedures for processed GaAs wafers. |

| Volume of<br>package (V)<br>in cm <sup>3</sup>                                                                     | Bomb condition             |                                                     | R <sub>1</sub><br>Reject limit<br>(atm cc/s He) |                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                                                                                                    | Psia<br>±2                 | Minimum<br>exposure time<br>hours (t <sub>1</sub> ) | Maximum dwell hours (t <sub>2</sub> )           |                                                                                                                      |

| $ \begin{array}{c} <0.05\\ \geq 0.05 - <0.5\\ \geq 0.5 - <1.0\\ \geq 1.0 - <10.0\\ \geq 10.0 - <20.0 \end{array} $ | 75<br>75<br>45<br>45<br>45 | 2<br>4<br>2<br>5<br>10                              | 1<br>1<br>1<br>1<br>1                           | 5 x 10 <sup>-8</sup><br>5 x 10 <sup>-8</sup><br>1 x 10 <sup>-7</sup><br>5 x 10 <sup>-8</sup><br>5 x 10 <sup>-8</sup> |

#### TABLE II. Fixed conditions for test condition A<sub>1</sub>.

3.1.1.2 Test condition  $A_2$ , flexible method. Values for bomb pressure exposure time, and dwell time shall be chosen such that actual measured tracer gas leak rate (R<sub>1</sub>) readings obtained for the devices under test (if defective) will be greater than the minimum detection sensitivity capability of the mass spectrometer. The devices shall be subjected to a minimum of 2 atmospheres absolute of helium atmosphere. If the chosen dwell time (t<sub>2</sub>) is greater than 60 minutes, graphs shall be plotted to determine an R<sub>1</sub> value which will assure overlap with the selected gross leak test condition. The chosen values, in conjunction with the value of the internal volume of the device package to be tested and the maximum equivalent standard leak rate (L) limit (as shown below or as specified in the applicable acquisition document), shall be used to calculate the measured leak rate (R<sub>1</sub>) limit using the following formula:

$$R_{1} = \frac{LP_{E}}{P_{O}} \left(\frac{M_{A}}{M}\right)^{\frac{1}{2}} \qquad \left\{ 1 - e^{\left[\frac{LT_{1}}{VP_{0}}\left(\frac{M_{A}}{M}\right)^{\frac{1}{2}}\right]} \right\} \qquad e^{\left[\frac{LT_{2}}{VP_{0}}\left(\frac{M_{A}}{M}\right)^{\frac{1}{2}}\right]}$$

Where:

- $R_1$  = The measured leak rate of tracer gas (He) through the leak in atm cc/s He.

- L = The equivalent standard leak rate in atm cc/s air.

- $P_E$  = The pressure of exposure in atmospheres absolute.

- $P_0$  = The atmospheric pressure in atmospheres absolute. (1)

- $M_A$  = The molecular weight of air in grams. (28.7)

- M = The molecular weight of the tracer gas (Helium) in grams. (4)

- $t_1$  = The time of exposure to  $P_E$  in seconds.

- $t_2$  = The dwell time between release of pressure and leak detection, in seconds.

- V = The internal volume of the device package cavity in cubic centimeters.

3.1.1.2.1 <u>Failure criteria</u>. Unless otherwise specified, devices with an internal cavity volume of 0.01 cc or less shall be rejected if the equivalent standard leak rate (L) exceeds  $5 \times 10^{-8}$  atm cc/s air. Devices with an internal cavity volume greater than 0.01 cc and equal to or less than 0.4 cc shall be rejected if the equivalent standard leak rate (L) exceeds  $1 \times 10^{-7}$  atm cc/s air. Devices with an internal cavity volume greater than 0.4 cc shall be rejected if the equivalent standard leak rate (L) exceeds  $1 \times 10^{-7}$  atm cc/s air. Devices with an internal cavity volume greater than 0.4 cc shall be rejected if the equivalent standard leak rate (L) exceeds  $1 \times 10^{-6}$  atm cc/s air.

3.1.2 Test condition A<sub>4</sub>, procedure applicable to the unsealed package method. The fixture and fittings of 2.1a. shall be mounted to the evacuation port of the leak detector. Proof of fixturing integrity shall be verified by sealing a flat surfaced metal plate utilizing the gasket of 2.1 (and grease or fluid of 2.1 if required to obtain seal) and measuring the response of the leak test system. Testing shall be performed by sealing the package(s) to the evacuation port and the package cavity evacuated to 0.1 torr or less. Care shall be taken to prevent contact of grease with package (seal ring not included) to avoid masking leaks. The external portion of the package shall be flooded with Helium gas either by the use of an envelope or a spray gun, at a pressure of 10 psig.

3.1.2.1 <u>Failure criteria</u>. Unless otherwise specified, devices shall be rejected if the measured leak rate ( $R_1$ ) exceeds 1 x 10<sup>-8</sup> atm cc/s He.

#### 3.2 Test condition B, radioisotope fine leak test.

\*

3.2.1 <u>Activation parameters</u>. The activation pressure and soak time shall be determined in accordance with the following equation:

$$Q_s = \frac{R}{skT P t}$$

(1)

The parameters of equation (1) are defined as follows:

- Q<sub>S</sub> = The maximum leak rate allowable, in atm cc/s Kr, for the devices to be tested.

- R = Counts per minute above the ambient background after activation if the device leak rate were exactly equal to Q<sub>s</sub>. This is the reject count above the background of both the counting equipment and the component, if it has been through prior radioactive leak tests.

- s = The specific activity, in microcuries per atmosphere cubic centimeter, of the krypton-85 tracer gas in the activation system.

- k = The overall counting efficiency of the scintillation crystal in counts per minute per microcurie of krypton-85 in the internal void of the specific component being evaluated. This factor depends upon component configuration and dimensions of the scintillation crystal. The counting efficiency shall be determined in accordance with 3.2.2.

- T = Soak time, in hours, that the devices are to be activated.

- $P = P_e^2 P_i^2$ , where  $P_e$  is the activation pressure in atmospheres absolute and  $P_i$  is the original internal pressure of the devices in atmospheres absolute. The activation pressure ( $P_e$ ) may be established by specification or if a convenient soak time (T) has been established, the activation pressure ( $P_e$ ) can be adjusted to satisfy equation (1).

- t = Conversion of hours to seconds and is equal to 3,600 seconds per hour.

- NOTE: The complete version of equation (1) contains a factor ( $P_0^2 (\Delta P)^2$ ) in the numerator which is a correction factor for elevation above sea level.  $P_0$  is sea level pressure in atmospheres absolute and  $\Delta P$  is the difference in pressure, in atmospheres between the actual pressure at the test station and sea level pressure. For the purpose of this test method, this factor has been dropped.

Supersedes Page 6 of MIL-STD-883E

#### **METHOD 1018.3**

#### INTERNAL WATER-VAPOR CONTENT

1. <u>PURPOSE</u>. The purpose of this test is to measure the water-vapor content of the atmosphere inside a metal or ceramic hermetically-sealed device. It can be destructive (procedures 1 and 2) or nondestructive (procedure 3).

2. <u>APPARATUS</u>. The apparatus for the internal water-vapor content test shall be as follows for the chosen procedure:

2.1 <u>Procedure 1</u>. (Procedure 1 measures the water-vapor content of the device atmosphere by mass spectrometry.) The apparatus for procedure 1 shall consist of:

- a. A mass spectrometer meeting the following equipments:

- (1) <u>Spectra range</u>. The mass spectrometer shall be capable of reading a minimum spectra range of 1 to 100 atomic mass units (AMUs).

- (2) Detection limit. The mass spectrometer shall be capable of reproducibly detecting the specified moisture content for a given volume package with signal to noise ratio of 20 to 1 (i.e., for a specified limit of 5,000 ppmv, .01 cc, the mass spectrometer shall demonstrate a 250 ppmv minimum detection limit to moisture for a package volume of .01 cc). The smallest volume shall be considered the worst case.

- (3) <u>Calibration</u>. The calibration of the mass spectrometer shall be accomplished at the specified moisture limit (±20 percent) using a package simulator which has the capability of generating at least three known volumes of gas ±10 percent on a repetitive basis by means of a continuous sample volume purge of known moisture content ±10 percent. Moisture content shall be established by the standard generation techniques (i.e., 2 pressure, divided flow, or cryogenic method). The dew point analyzer shall be recalibrated a minimum of once per year using equipment traceable to NIST or by a suitable commercial calibration services laboratory using equipment traceable to NIST standards. Calibration records shall be kept on a daily basis. Gas analysis results obtained by this method shall be considered valid only in the moisture range or limit bracketed by at least two (volume or concentration) calibration points (i.e., 5,000 ppmv between .01 .1 cc) or 1,000 5,000 ppmv between .01 .1 cc). A best fit curve shall be used between volume calibration points. Systems not capable of bracketing may use an equivalent procedure as approved by the qualifying activity. Corrections of sensitivity factors deviation greater than 10 percent from the mean between calibration points shall be required.

NOTE: It is recommended that the percentage of water vapor contained in a gas flowing through the gas humidifier be compared to the dewpoint sensor reading for accuracy of the sensor. The following equation may be used to calculate the percent of water vapor contained in a gas flowing through the gas humidifier.

$\% H_2 O = \frac{100(Pvmb)}{68.95 \ mb/psi \ Pg + 1.33 \ mb/mmPa}$ , where

Pv = vapor pressure of water in the GPH based on water temperature in degrees centigrade,

- $P_q$  = gauge pressure in psi, and

- $P_a$  = atmospheric pressure in mm Hg.

- (4) <u>Calibration for other gases</u>. Calibration shall be required for all gases found in concentrations greater than .01 percent by volume. As a minimum, this shall include all gases listed in 3.1c. The applicable gases shall be calibrated at approximately 1 percent concentrations as part of the yearly calibration requirements, with the exception of fluorocarbons, which may use a concentration of approximately 200 ppmv; nitrogen, which may use a concentration of approximately 80 percent or more; helium, which may use a concentration of approximately 10 percent; and oxygen, which may use a concentration of approximately 20 percent.

Supersedes Page 1 of Notice 4 of MIL-STD-883E

- (5) <u>Calibration check</u>. The system calibration shall be checked on the day of test prior to any testing. This shall include checking the calibration by in-letting a 5000 ppmv ±20% moisture calibration sample of the required volumes and comparing the result with the calibration sample. The resulting moisture reading shall be within 250 ppmv of the moisture level in the calibration sample. Calibration performed on the day of test prior to any testing may be substituted for the calibration check.

- b. A vacuum opening chamber which can contain the device and a vacuum transfer passage connecting the device to the mass spectrometer of 2.1a. The system shall be maintained at a stable temperature equal to or above the device temperature. The fixturing in the vacuum opening chamber shall position the specimen as required by the piercing arrangement of 2.1c, and maintain the device at 100°C ±5°C for a minimum of 10 minutes prior to piercing.

Note: A maximum 5-minute transfer time from prebake to hot insertion into apparatus shall be allowed. If 5 minutes is exceeded, device shall be returned to the prebake oven and the prebake continued until device reaches 100 °C  $\pm$  5 °C.

For initial certification of systems or extension of suitability, device temperature on systems using an external fixture shall be characterized by placing a thermocouple into the cavity of a blank device of similar mass, internal volume, construction and size. This shall be a means for proving the device temperature has been maintained at 100 °C  $\pm$  5 °C for the minimum ten minutes. This also applies to devices prebaked in an external oven but tested with the external fixture to adjust for any temperature drop during the transfer. These records shall be maintained by the test laboratory.

- c. A piercing arrangement functioning within the opening chamber or transfer passage of 2.1b, which can pierce the specimen housing (without breaking the mass spectrometer chamber vacuum and without disturbing the package sealing medium), thus allowing the specimen's internal gases to escape into the chamber and mass spectrometer.

- NOTE: A sharp-pointed piercing tool, actuated from outside the chamber wall via a bellows to permit movement, should be used to pierce both metal and ceramic packages. For ceramic packages, the package lid or cover should be locally thinned by abrasion to facilitate localized piercing.

2.2 <u>Procedure 2</u>. (Procedure 2 measures the water-vapor content of the device atmosphere by integrating moisture picked up by a dry carrier gas at 50°C.) The apparatus for procedure 2 shall consist of:

- a. An integrating electronic detector and moisture sensor capable of reproducibly detecting a water-vapor content of 300 ±50 ppmv moisture for the package volume being tested. This shall be determined by dividing the absolute sensitivity in micrograms H<sub>2</sub>0 by the computed weight of the gas in the device under test, and then correcting to ppmv.

- b. A piercing chamber or enclosure, connected to the integrating detector of 2.2a, which will contain the device specimen and maintain its temperature at 100°C ±5°C during measurements. The chamber shall position the specimen as required by the piercing arrangement. The piercing mechanism shall open the package in a manner which will allow the contained gas to be purged out by the carrier gas or removed by evacuation. The sensor and connection to the piercing chamber will be maintained at a temperature of 50°C ±2°C.

2.3 <u>Procedure 3</u>. (Procedure 3 measures the water-vapor content of the device atmosphere by measuring the response of a calibrated moisture sensor or an IC chip which is sealed within the device housing, with its electrical terminals available at the package exterior.) The apparatus for procedure 3 shall consist of one of the following:

a. A moisture sensor element and readout instrument capable of detecting a water-vapor content of 300 ±50 ppmv while sensor is mounted inside a sealed device.

#### **METHOD 1019.6**

### IONIZING RADIATION (TOTAL DOSE) TEST PROCEDURE

1. <u>PURPOSE</u>. This test procedure defines the requirements for testing packaged semiconductor integrated circuits for ionizing radiation (total dose) effects from a cobalt-60 (<sup>60</sup>Co) gamma ray source. The testing includes both standard room temperature irradiation as well as irradiation at elevated temperature. In addition this procedure provides an accelerated annealing test for estimating low dose rate ionizing radiation effects on devices. This annealing test is important for low dose-rate or certain other applications in which devices may exhibit significant time-dependent effects. This procedure addresses only steady state irradiations, and is not applicable to pulse type irradiations. This test may produce severe degradation of the electrical properties of irradiated devices and thus should be considered a destructive test.

1.1 <u>Definitions</u>. Definitions of terms used in this procedure are given below:

\*

\*

\*

\*

- a. <u>Ionizing radiation effects</u>. The changes in the electrical parameters of a device or integrated circuit resulting from radiation-induced charge. These are also referred to as total dose effects.

- b. In-flux test. Electrical measurements made on devices during irradiation exposure.

- c. Not in-flux test. Electrical measurements made on devices at any time other than during irradiation.

- d. <u>Remote tests</u>. Electrical measurements made on devices which are physically removed from the radiation location.

- e. <u>Time dependent effects</u>. Significant degradation in electrical parameters caused by the growth or annealing or both of radiation-induced trapped charge after irradiation. Similar effects also take place during irradiation.

- f. Accelerated annealing test. A procedure utilizing elevated temperature to accelerate time-dependent effects.

- g. <u>Enhanced Low Dose Rate Sensitivity (ELDRS)</u>. Used to refer to a part that shows enhanced radiation induced damage at dose rates below 50 rad(Si)/s.

- h. <u>Overtest</u>. A factor that is applied to the specification dose to determine the test dose level that the samples must pass to be acceptable at the specification level. An overtest factor of 1.5 means that the parts must be tested at 1.5 times the specification dose.

i. <u>Parameter Delta Design Margin (PDDM)</u>. A design margin that is applied to the radiation induced change in an electrical parameter. For a PDDM of 2 the change in a parameter at a specified dose from the pre-irradiation value is multiplied by two and added to the post-irradiation value to see if the sample exceeds the post-irradiation parameter limit. For example, if the pre-irradiation value of Ib is 30 nA and the post-irradiation value at 20 krad(Si) is 70 nA (change in Ib is 40 nA), then for a PDDM of 2 the post-irradiation value would be 110 nA (30 nA + 2 X 40 nA). If the allowable post-irradiation limit is 100 nA the part would fail.

2. <u>APPARATUS</u>. The apparatus shall consist of the radiation source, electrical test instrumentation, test circuit board(s), cabling, interconnect board or switching system, an appropriate dosimetry measurement system, and an environmental chamber (if required for time-dependent effects measurements or elevated temperature irradiation). Adequate precautions shall be observed to obtain an electrical measurement system with sufficient insulation, ample shielding, satisfactory grounding, and suitable low noise characteristics.

2.1 <u>Radiation source</u>. The radiation source used in the test shall be the uniform field of a <sup>60</sup>Co gamma ray source. Uniformity of the radiation field in the volume where devices are irradiated shall be within  $\pm 10$  percent as measured by the dosimetry system, unless otherwise specified. The intensity of the gamma ray field of the <sup>60</sup>Co source shall be known with an uncertainty of no more than  $\pm 5$  percent. Field uniformity and intensity can be affected by changes in the location of the device with respect to the radiation source and the presence of radiation absorption and scattering materials.

2.2 <u>Dosimetry system</u>. An appropriate dosimetry system shall be provided which is capable of carrying out the measurements called for in 3.2. The following American Society for Testing and Materials (ASTM) standards and guidelines or other appropriate standards and guidelines shall be used:

ASTM E 666 - Standard Method for Calculation of Absorbed Dose from Gamma or X Radiation.

1

| ASTM E 668 -  | Standard Practice for the Application of Thermoluminescence Dosimetry (TLD) Systems for Determining Absorbed Dose in Radiation-Hardness Testing of Electronic Devices.                     |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASTM E 1249 - | Minimizing Dosimetry Errors in Radiation Hardness Testing of Silicon Electronic Devices.                                                                                                   |

| ASTM E 1250 - | Standard Method for Application of Ionization Chambers to Assess the Low Energy Gamma Component of Cobalt 60 Irradiators Used in Radiation Hardness Testing of Silicon Electronic Devices. |

| ASTM E 1275 - | Standard Practice for Use of a Radiochromic Film Dosimetry System.                                                                                                                         |

| ASTM F 1892 - | Standard Guide for Ionizing Radiation (Total Dose) Effects Testing of Semiconductor Devices.                                                                                               |

These industry standards address the conversion of absorbed dose from one material to another, and the proper use of various dosimetry systems.  $\underline{1}$ /

2.3 <u>Electrical test instruments</u>. All instrumentation used for electrical measurements shall have the stability, accuracy, and resolution required for accurate measurement of the electrical parameters. Any instrumentation required to operate in a radiation environment shall be appropriately shielded.

2.4 Test circuit board(s). Devices to be irradiated shall either be mounted on or connected to circuit boards together with any associated circuitry necessary for device biasing during irradiation or for in-situ measurements. Unless otherwise specified, all device input terminals and any others which may affect the radiation response shall be electrically connected during irradiation, i.e., not left floating. The geometry and materials of the completed board shall allow uniform irradiation of the devices under test. Good design and construction practices shall be used to prevent oscillations, minimize leakage currents, prevent electrical damage, and obtain accurate measurements. Only sockets which are radiation resistant and do not exhibit significant leakages (relative to the devices under test) shall be used to mount devices and associated circuitry to the test board(s). All apparatus used repeatedly in radiation fields shall be checked periodically for physical or electrical degradation. Components which are placed on the test circuit board, other than devices under test, shall be insensitive to the accumulated radiation or they shall be shielded from the radiation. Test fixtures shall be made such that materials will not perturb the uniformity of the radiation field intensity at the devices under test. Leakage current shall be measured out of the radiation field. With no devices installed in the sockets, the test circuit board shall be connected to the test system such that all expected sources of noise and interference are operative. With the maximum specified bias for the test device applied, the leakage current between any two terminals shall not exceed ten percent of the lowest current limit value in the pre-irradiation device specification. Test circuit boards used to bias devices during accelerated annealing must be capable of withstanding the temperature requirements of the accelerated annealing test and shall be checked before and after testing for physical and electrical degradation.

2.5 <u>Cabling</u>. Cables connecting the test circuit boards in the radiation field to the test instrumentation shall be as short as possible. If long cables are necessary, line drivers may be required. The cables shall have low capacitance and low leakage to ground, and low leakage between wires.

2.6 <u>Interconnect or switching system</u>. This system shall be located external to the radiation environment location, and provides the interface between the test instrumentation and the devices under test. It is part of the entire test system and subject to the limitation specified in 2.4 for leakage between terminals.

2.7 <u>The environmental chamber</u>. The environmental chamber for time-dependent effects testing, if required, shall be capable of maintaining the selected accelerated annealing temperature within  $\pm 5^{\circ}$ C.

2.8 <u>The irradiation temperature chamber</u>. The irradiation temperature chamber, if required for elevated temperature irradiation, should be capable of maintaining a circuit under test at 100°C ±5°C while it is being irradiated. The chamber should be capable of raising the temperature of the circuit under test from room temperature to the irradiation temperature within a reasonable time prior to irradiation and cooling the circuit under test from the irradiation. The irradiation bias shall be maintained during the heating and cooling. The method for raising, maintaining and lowering the temperature of the circuit under test may be by conduction through a heat sink using heating and cooling fluids, by convection using forced hot and cool air, or other means that will achieve the proper results.

1/ Copies may be obtained from the American Society for Testing and Materials, 1916 Race Street, Philadelphia, PA 19103.

\*

3. <u>PROCEDURE</u>. The test devices shall be irradiated and subjected to accelerated annealing testing (if required for time-dependent effects testing) as specified by a test plan. This plan shall specify the device description, irradiation conditions, device bias conditions, dosimetry system, operating conditions, measurement parameters and conditions, and accelerated annealing test conditions (if required).

3.1 <u>Sample selection and handling</u>. Only devices which have passed the electrical specifications as defined in the test plan shall be submitted to radiation testing. Unless otherwise specified, the test samples shall be randomly selected from the parent population and identically packaged. Each part shall be individually identifiable to enable pre- and post-irradiation comparison. For device types which are ESD-sensitive, proper handling techniques shall be used to prevent damage to the devices.

3.2 <u>Burn-in</u>. For some devices, there are differences in the total dose radiation response before and after burnin. Unless it has been shown by prior characterization or by design that burn-in has negligible effect (parameters remain within post-irradiation specified electrical limits) on the total dose radiation response, then one of the following must be done:

3.2.1 The manufacturer shall subject the radiation samples to the specified burn-in conditions prior to conducting total dose radiation testing or

3.2.2 The manufacturer shall develop a correction factor, (which is acceptable to the parties to the test) taking into account the changes in total dose response resulting from subjecting product to burn-in. The correction factor shall then be used to accept product for total dose response without subjecting the test samples to burn-in.

3.3 <u>Dosimetry measurements</u>. The radiation field intensity at the location of the device under test shall be determined prior to testing by dosimetry or by source decay correction calculations, as appropriate, to assure conformance to test level and uniformity requirements. The dose to the device under test shall be determined one of two ways: (1) by measurement during the irradiation with an appropriate dosimeter, or (2) by correcting a previous dosimetry value for the decay of the <sup>60</sup>Co source intensity in the intervening time. Appropriate correction shall be made to convert from the measured or calculated dose in the dosimeter material to the dose in the device under test.

3.4 Lead/Aluminum (Pb/Al) container. Test specimens shall be enclosed in a Pb/Al container to minimize dose enhancement effects caused by low-energy, scattered radiation. A minimum of 1.5 mm Pb, surrounding an inner shield of at least 0.7 mm Al, is required. This Pb/Al container produces an approximate charged particle equilibrium for Si and for TLDs such as CaF<sub>2</sub>. The radiation field intensity shall be measured inside the Pb/Al container (1) initially, (2) when the source is changed, or (3) when the orientation or configuration of the source, container, or test-fixture is changed. This measurement shall be performed by placing a dosimeter (e.g., a TLD) in the device-irradiation container at the approximate test-device position. If it can be demonstrated that low energy scattered radiation is small enough that it will not cause dosimetry errors due to dose enhancement, the Pb/Al container may be omitted.

3.5 <u>Radiation level(s)</u>. The test devices shall be irradiated to the dose level(s) specified in the test plan within ±10 percent. If multiple irradiations are required for a set of test devices, then the post-irradiation electrical parameter measurements shall be performed after each irradiation.

3.6 <u>Radiation dose rate</u>. The radiation dose rate for bipolar and BiCMOS linear or mixed-signal parts used in applications where the maximum dose rate is below 50 rad(Si)/s shall be determined as described in paragraph 3.13 below. Parts used in low dose rate applications, unless they have been demonstrated to not exhibit an ELDRS response shall use Condition C, Condition D, or Condition E.

Note: Devices that contain both MOS and bipolar devices may require qualification to multiple subconditions to ensure that both ELDRS and traditional MOS effects are evaluated.

3.6.1 <u>Condition A.</u> For condition A (standard condition) the dose rate shall be between 50 and 300 rad(Si)/s [0.5 and 3 Gy(Si)/s] <sup>60</sup>Co  $\underline{2}$ / The dose rates may be different for each radiation dose level in a series; however, the dose rate shall not vary by more than ±10 percent during each irradiation.

2/ The SI unit for the quantity absorbed dose is the gray, symbol GY. 100 rad = 1 Gy.

3.6.2 <u>Condition B.</u> For condition B, for MOS devices only, if the maximum dose rate is < 50 rad(Si)/s in the intended application, the parties to the test may agree to perform the test at a dose rate  $\geq$  the maximum dose rate of the intended application. Unless the exclusions in 3.12.1b are met, the accelerated annealing test of 3.12.2 shall be performed.

3.6.3 <u>Condition C</u>. For condition C, (as an alternative) the test may be performed at the dose rate agreed to by the parties to the test.

3.6.4 <u>Condition D</u>. For condition D, for bipolar or BiCMOS linear or mixed-signal circuits only, the parts shall be irradiated at  $\leq 10 \text{ mrad}(\text{Si})$ /s unless the specification dose is greater than 25 krad(Si). For radiation levels greater than 25 krad(Si) the total irradiation time shall be  $\geq 1000$  hours and the dose rate shall be determined from the total dose (including any overtest factors) and the irradiation time.

\*

\*

\*

\*

\*

- 3.6.5 <u>Condition E</u>. For condition E, for bipolar or BiCMOS linear or mixed-signal circuits only, the parts shall be irradiated at between 0.5 and 5 rad(Si)/s if the specification dose is  $\leq$  50 krad(Si). Condition E applies to elevated temperature irradiation at 100°C ±5°C and does not apply for devices with specification doses >50 krad(Si) unless it can be demonstrated that the elevated temperature irradiation test provides a conservative bound for low dose rate response at a radiation specification level that is above 50 krad(Si).

- 3.7 <u>Temperature requirements</u>. The following requirements shall apply for room temperature and elevated temperature irradiation.

- 3.7.1 Room temperature irradiation. Since radiation effects are temperature dependent, devices under test shall be irradiated in an ambient temperature of 24°C ±6°C as measured at a point in the test chamber in close proximity to the test fixture. The electrical measurements shall be performed in an ambient temperature of 24°C ±6°C. If devices are transported to and from a remote electrical measurement site, the temperature of the test devices shall not be allowed to increase by more than 10°C from the irradiation environment. If any other temperature range is required, it shall be specified.

- \* <u>3.7.2</u> <u>Elevated temperature irradiation</u>. For bipolar or BiCMOS linear or mixed-signal circuits irradiated using Condition E dose rate, devices under test shall be irradiated in an ambient temperature of 100°C ±5°C as measured at a point in the test chamber in close proximity to the test fixture.

3.8 <u>Electrical performance measurements</u>. The electrical parameters to be measured and functional tests to be performed shall be specified in the test plan. As a check on the validity of the measurement system and pre- and post-irradiation data, at least one control sample shall be measured using the operating conditions provided in the governing device specifications. For automatic test equipment, there is no restriction on the test sequence provided that the rise in the device junction temperature is minimized. For manual measurements, the sequence of parameter measurements shall be chosen to allow the shortest possible measurement period. When a series of measurements is made, the tests shall be arranged so that the lowest power dissipation in the device occurs in the earliest measurements and the power dissipation increases with subsequent measurements in the sequence.

The pre- and post-irradiation electrical measurements shall be done on the same measurement system and the same sequence of measurements shall be maintained for each series of electrical measurements of devices in a test sample. Pulse-type measurements of electrical parameters should be used as appropriate to minimize heating and subsequent annealing effects. Devices which will be subjected to the accelerated annealing testing (see 3.12) may be given a pre-irradiation burn-in to eliminate burn-in related failures.

3.9 <u>Test conditions</u>. The use of in-flux or not in-flux testing shall be specified in the test plan. (This may depend on the intended application for which the data are being obtained.) The use of in-flux testing may help to avoid variations introduced by post-irradiation time dependent effects. However, errors may be incurred for the situation where a device is irradiated in-flux with static bias, but where the electrical testing conditions require the use of dynamic bias for a significant fraction of the total irradiation period. Not-in-flux testing generally allows for more comprehensive electrical testing, but can be misleading if significant post-irradiation time dependent effects occur.

3.9.1 <u>In-flux testing</u>. Each test device shall be checked for operation within specifications prior to being irradiated. After the entire system is in place for the in-flux radiation test, it shall be checked for proper interconnections, leakage (see 2.4), and noise level. To assure the proper operation and stability of the test setup, a control device with known parameter values shall be measured at all operational conditions called for in the test plan. This measurement shall be done either before the insertion of test devices or upon completion of the irradiation after removal of the test devices or both.

3.9.2 <u>Remote testing</u>. Unless otherwise specified, the bias shall be removed and the device leads placed in conductive foam (or similarly shorted) during transfer from the irradiation source to a remote tester and back again for further irradiation. This minimizes post-irradiation time dependent effects.

3.9.3 <u>Bias and loading conditions.</u> Bias conditions for test devices during irradiation or accelerated annealing shall be within ±10 percent of those specified by the test plan. The bias applied to the test devices shall be selected to produce the greatest radiation induced damage or the worst-case damage for the intended application, if known. While maximum voltage is often worst case some bipolar linear device parameters (e.g. input bias current or maximum output load current) exhibit more degradation with 0 V bias. The specified bias shall be maintained on each device in accordance with the test plan. Bias shall be checked immediately before and after irradiation. Care shall be taken in selecting the loading such that the rise in the junction temperature is minimized.

3.10 Post-irradiation procedure. Unless otherwise specified, the following time intervals shall be observed:

- a. The time from the end of an irradiation to the start of electrical measurements shall be a maximum of 1 hour unless Condition D is used, in which case the maximum time shall be 72 hours.

- b. The time to perform the electrical measurements and to return the device for a subsequent irradiation, if any, shall be within two hours of the end of the prior irradiation unless Condition D is used, in which case the maximum time shall be 120 hours.

To minimize time dependent effects, these intervals shall be as short as possible. The sequence of parameter measurements shall be maintained constant throughout the tests series.

3.11 Extended room temperature anneal test. The tests of 3.1 through 3.10 are known to be overly conservative for some devices in a very low dose rate environment (e.g. dose rates characteristic of space missions). The extended room temperature anneal test provides an estimate of the performance of a device in a very low dose rate environment even though the testing is performed at a relatively high dose rate (e.g. 50-300 rad(Si)/s). The procedure involves irradiating the device per steps 3.1 through 3.10 and post-irradiation subjecting the device under test to a room temperature anneal for an appropriate period of time (see 3.11.2c) to allow leakage-related parameters that may have exceeded their pre-irradiation specification to return to within specification. The procedure is known to lead to a higher rate of device acceptance in cases:

- a. where device failure when subjected to the tests in 3.1 through 3.10 has been caused by the buildup of trapped positive charge in relatively soft oxides, and

- b. where this trapped positive charge anneals at a relatively high rate.

\*

\*

\*

3.11.1 <u>Need to perform an extended room temperature anneal test</u>. The following criteria shall be used to determine whether an extended room temperature anneal test is appropriate:

- a. The procedure is appropriate for either MOS or bipolar technology devices.

- b. The procedure is appropriate where only parametric failures (as opposed to functional failure) occurs. The parties to the test shall take appropriate steps to determine that the device under test is subject to only parametric failure over the total ionizing dose testing range.

- c. The procedure is appropriate where the natural annealing response of the device under test will serve to correct the out-of-specification of any parametric response. Further, the procedure is known to lead to a higher rate of device acceptance in cases where the expected application irradiation dose rate is sufficiently low that ambient temperature annealing of the radiation induced trapped positive charge can lead to a significant improvement of device behavior. Cases where the expected application dose rate is lower than the test dose rate and lower than 0.1 rad(Si)/s should be considered candidates for the application of this procedure. The parties to the test shall take appropriate steps to determine that the technology under test can provide the required annealing response over the total ionizing dose testing range.

3.11.2 <u>Extended room temperature anneal test procedure</u>. If the device fails the irradiation and testing specified in 3.1 through 3.10, an additional room temperature annealing test may be performed as follows:

- a. Following the irradiation and testing of 3.1 through 3.10, subject the device under test to a room temperature anneal under worst-case static bias conditions. For information on worst case bias see 3.9.3,

- b. The test will be carried out in such a fashion that the case of the device under test will have a temperature within the range 24°C ± 6°C.

c. Where possible, the room temperature anneal should continue for a length of time great enough to allow device parameters that have exceeded their pre-irradiation specification to return to within specification or post-irradiation- parametric limit (PIPL) as established by the manufacturer. However, the time of the room temperature anneal shall not exceed t<sub>max</sub>, where

$$t_{max} = \frac{D_{spec}}{R_{max}}$$

$D_{\text{spec}}$  is the total ionizing dose specification for the part and  $R_{\text{max}}$  is the maximum dose rate for the intended use.

d. Test the device under test for electrical performance as specified in 3.7 and 3.8. If the device under test passes electrical performance tests following the extended room temperature anneal, this shall be considered acceptable performance for a very low dose rate environment in spite of having previously failed the post-irradiation and electrical tests of 3.1 through 3.10.

3.12 <u>MOS accelerated annealing test</u>. The accelerated annealing test provides an estimate of worst-case degradation of MOS microcircuits in low dose rate environments. The procedure involves heating the device following irradiation at specified temperature, time and bias conditions. An accelerated annealing test (see 3.12.2) shall be performed for cases where time dependent effects (TDE) can cause a device to degrade significantly or fail. Only standard testing shall be performed as specified in 3.1 through 3.10 for cases where TDE are known not to cause significant device degradation or failure (see 3.12.1) or where they do not need to be considered, as specified in 3.12.1.

3.12.1 <u>Need to perform accelerated annealing test</u>. The parties to the test shall take appropriate steps to determine whether accelerated annealing testing is required. The following criteria shall be used:

- a. The tests called out in 3.12.2 shall be performed for any device or circuit type that contains MOS circuit elements (i.e., transistors or capacitors).

- b. TDE tests may be omitted if:

- 1. circuits are known not to contain MOS elements by design, or

- 2. the ionizing dose in the application, if known, is below 5 krad(Si), or

- the lifetime of the device from the onset of the irradiation in the intended application, if known, is short compared with TDE times, or

- 4. the test is carried out at the dose rate of the intended application, or

- 5. the device type or IC technology has been demonstrated via characterization testing not to exhibit TDE changes in device parameters greater than experimental error (or greater than an otherwise specified upper limit) and the variables that affect TDE response are demonstrated to be under control for the specific vendor processes.

At a minimum, the characterization testing in (5) shall include an assessment of TDE on propagation delay, output drive, and minimum operating voltage parameters. Continuing process control of variables affecting TDE may be demonstrated through lot sample tests of the radiation hardness of MOS test structures.

c. This document provides no guidance on the need to perform accelerated annealing tests on technologies that do not include MOS circuit elements.

3.12.2 <u>Accelerated annealing test procedure</u>. If the device passes the tests in 3.1 through 3.10 or if it passes 3.11 (if that procedure is used) to the total ionizing dose level specified in the test plan or device specification or drawing and the exclusions of 3.12.1 do not apply, the accelerated annealing test shall be conducted as follows:

# a. <u>Overtest</u>.

- 1. Irradiate each test device to an additional 0.5-times the specified dose using the standard test conditions (3.1 through 3.10). Note that no electrical testing is required at this time.

- 2. The additional 0.5-times irradiation in 3.12.2.a.1may be omitted if it has been demonstrated via characterization testing that:

- a. none of the circuit propagation delay, output drive, and minimum operating voltage parameters recover toward their pre-irradiation value greater than experimental accelerated annealing test of 3.12.2.b, and

- b. the irradiation biases chosen for irradiation and accelerated annealing tests are worst-case for the response of these parameters during accelerated annealing.

The characterization testing to establish worst-case irradiation and annealing biases shall be performed at the specified level. The testing shall at a minimum include separate exposures under static and dynamic irradiation bias, each followed by worst-case static bias during accelerated annealing according to 3.12.2.b.

- b. <u>Accelerated annealing</u>. Heat each device under worst-case static bias conditions in an environmental chamber according to one of the following conditions:

- 1. At 100°C ±5°C for 168 ±12 hours, or

- 2. At an alternate temperature and time that has been demonstrated via characterization testing to cause equal or greater change in the parameter(s) of interest, e.g., propagation delay, output drive, and minimum operating voltage, in each test device as that caused by 3.12.2.b.1, or

- 3. At an alternate temperature and time which will cause trapped hole annealing of >60% and interface state annealing of <10% as determined via characterization testing of NMOS test transistors from the same process. It shall be demonstrated that the radiation response of test transistors represent that of the device under test.</p>

- c. Electrical testing. Following the accelerated annealing, the electrical test measurements shall be performed as specified in 3.8 and 3.9.

- \* 3.13 <u>Test procedure for Bipolar and BiCMOS linear or mixed signal circuits with agreed to dose rates of less than</u> 50 rad(Si)/s. Many bipolar linear parts exhibit ELDRS, which cannot be simulated with a room temperature 50-300 rad(Si)/s irradiation plus elevated temperature anneal, such as that used for MOS parts (see ASTM-F1892 for more technical details). Parts that exhibit ELDRS shall be tested either at the agreed to dose rate, at a prescribed low dose rate to an overtest radiation level, or with an elevated temperature irradiation test that includes a parameter delta design margin.

- \* Need to perform low dose rate testing.

- a. The low dose rate tests described in 3.13 may be omitted if:

- \*

\*

\*

\*

1. circuits are known not to contain bipolar transistors by design, or

- 2. circuits are known not to contain any linear circuit functions by design.

- the device type and IC technology have been demonstrated via characterization testing not to exhibit ELDRS in device parameters greater than experimental error (or greater than an otherwise specified upper limit) and the variables that affect ELDRS response are demonstrated to be under control for the specific vendor processes.

3.13.1 Low dose rate or elevated temperature irradiation test for bipolar or BiCMOS linear or mixed-signal \* circuits. All circuits that do not meet the exception of 3.13.a shall be tested using one of the following test conditions. Note: The test procedures described in paragraphs b. and c. below represent a compromise between the desire for a conservative, worst-case test and the constraints of test cost, schedule and facilities. For this reason, the test procedures may result in a non-conservative test for some kinds of circuits. Test at the agreed to dose rate. Irradiate each test device at the dose rate described in 3.6.3 Condition C \* a. using the standard test conditions (3.1 through 3.10). \* Test at a prescribed low dose rate. Irradiate each test device at the dose rate described in 3.6.4 b. Condition D using the standard test conditions (3.1 through 3.10) with the following additional requirements: If the dose rate is < 10 mrad(Si)/s, an overtest factor of 1.5 shall be applied to the radiation test 1. \* level, i.e. the part must pass at a radiation level of 1.5 times the specification dose to be acceptable. If the dose rate is greater than 10 mrad(Si)/s, an overtest factor of 2.0 shall be applied to the \* 2. radiation test level, i.e. the part must pass at a radiation level of 2.0 times the specification dose to be acceptable. \* Test at an elevated temperature. Irradiate each test device at the dose rate described in 3.6.5 Condition С E using the standard test conditions (3.1 through 3.10) with the following additional requirements: The irradiation temperature shall be  $100^{\circ}C \pm 5^{\circ}C$  using an irradiation test chamber as 1. \* described in paragraph 2.8. Every effort shall be made to minimize the time at temperature. The elevated temperature irradiation test shall only be used for parts with a specification dose 2. \* of 50 krad(Si) or less. All pre and post irradiation electrical measurements shall be made at a temperature of 24°C \* 3. ±6°C. \* A parameter delta design margin of 3 shall be applied at the specification dose to all critical 4. electrical parameters in the following manner. The change in each electrical parameter shall be calculated for each sample at the specification dose. This change in the parameter shall be multiplied by 3 and added (or subtracted) to the post irradiation parameter value for each sample. This value shall be compared to the allowable degraded value of the parameter to determine whether the sample passes or fails the test. 3.14 Test report. As a minimum, the report shall include the device type number, serial number, the \* manufacturer, package type, controlling specification, date code, and any other identifying numbers given by the manufacturer. The bias circuit, parameter measurement circuits, the layout of the test apparatus with details of distances and materials used, and electrical noise and current leakage of the electrical measurement system for in-flux testing shall be reported using drawings or diagrams as appropriate. Each data sheet shall include the test date, the radiation source used, the bias conditions during irradiation, the ambient temperature around the devices

date, the radiation source used, the bias conditions during irradiation, the ambient temperature around the devices during irradiation and electrical testing, the duration of each irradiation, the time between irradiation and the start of the electrical measurements, the duration of the electrical measurements and the time to the next irradiation when step irradiations are used, the irradiation dose rate, electrical test conditions, dosimetry system and procedures and the radiation test levels. The pre- and post-irradiation data shall be recorded for each part and retained with the parent population data in accordance with the requirements of MIL-PRF-38535 or MIL-PRF-38534. Any anomalous incidents during the test shall be fully documented and reported. The accelerated aging annealing procedure, if used, shall be described. Any other radiation test procedures or test data required for the delivery shall be specified in the device specification, drawing or purchase order.

- 4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document as required:

- a. Device-type number(s), quantity, and governing specifications (see 3.1).

- b. Radiation dosimetry requirements (see 3.3).

- c. Radiation test levels including dose and dose rate (see 3.5 and 3.6).

- d. Irradiation, electrical test and transport temperatures if other than as specified in 3.7.

- e. Electrical parameters to be measured and device operating conditions during measurement (see 3.8).

- f. Test conditions, i.e., in-flux or not-in-flux type tests (see 3.9).

- g. Bias conditions for devices during irradiation (see 3.9.3).

- h. Time intervals of the post-irradiation measurements (see 3.10).

- i. Requirement for extended room temperature anneal test, if required (see 3.11).

- j. Requirement for accelerated annealing test, if required (see 3.12).

- k. Documentation required to be delivered with devices (see 3.14).

\*

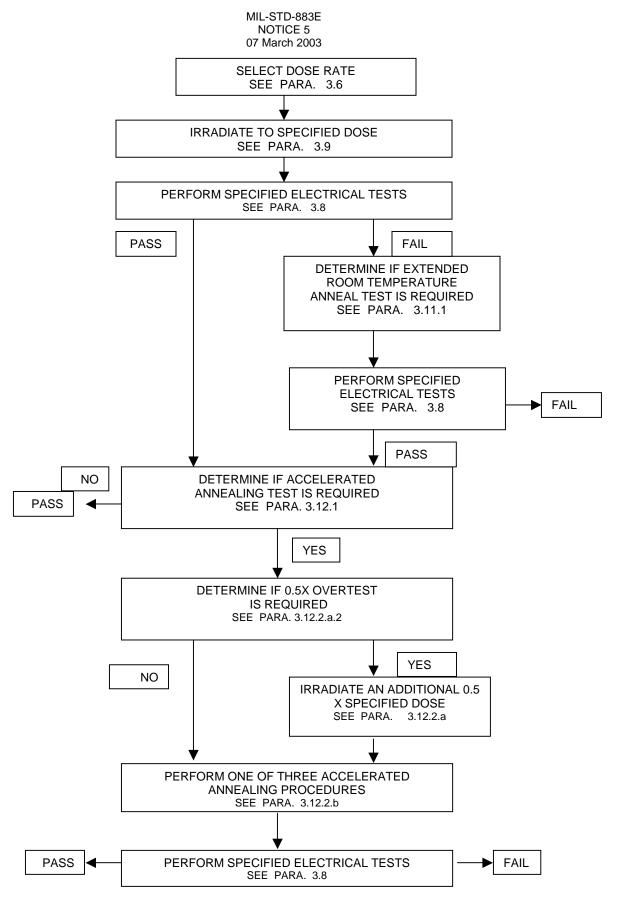

Figure 1019-1. Flow diagram for ionizing radiation test procedure for MOS and digital bipolar circuits

\*

\*

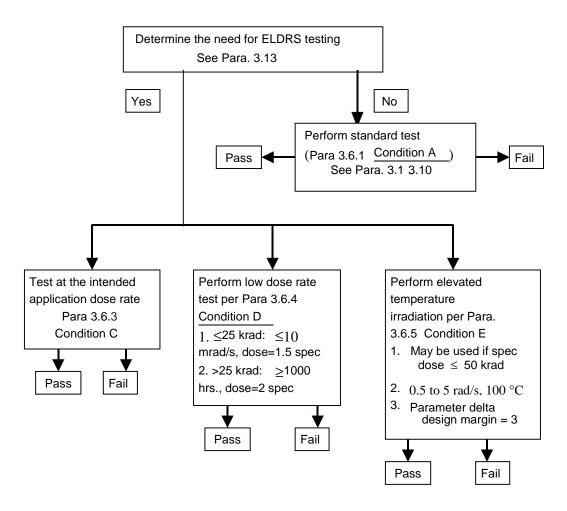

Figure 1019-2. Flow diagram for Ionizing radiation test procedure for bipolar (or BiCMOS) linear or mixedsignal circuits Downloaded from http://www.everyspec.com

MIL-STD-883E NOTICE 5 07 March 2003

This page intentionally left blank

### f. Definitions:

\*

\*

\*

\*

\*

\*

\*

- Active circuit area. All areas enclosed by the perimeter of functional circuit elements, operating metallization or any connected combinations thereof excluding beam leads.

- (2) Coupling (air) bridge. A raised layer of metallization used for interconnection that is isolated from the surface of the element.

- (3) Block resistor. A thin film resistor which for purposes of trimming is designed to be much wider than would be dictated by power density requirements and shall be identified in the approved manufacturer's precap visual implementation document.

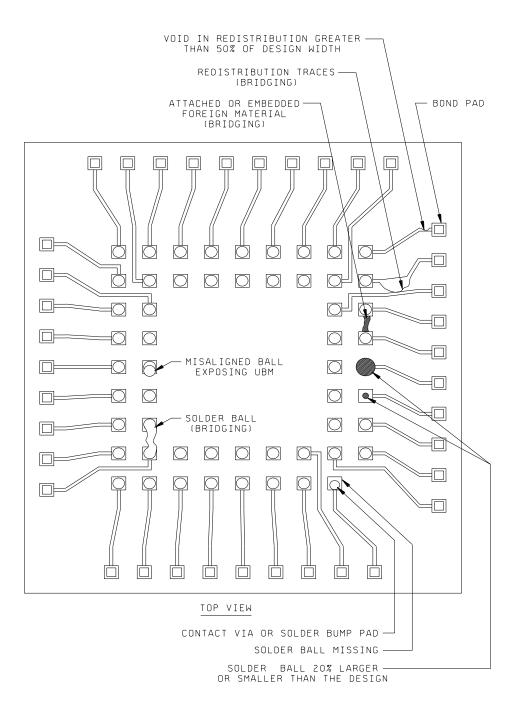

- (4) Contact Via. The Via where dielectric material is etched away in order to expose the Under Bump Metalization (UBM) on the bond pads or solder bump attach pads.

- (5) Channel. An area lying between the drain and the source of FET structures.

- (6) Controlled environment. Shall be class 1,000, (see 40.8.1.1.7 of appendix A of MIL-PRF-38535), except that the maximum allowable relative humidity shall not exceed 65 percent.

- (7) Crazing. The presence of numerous minute cracks in the referenced material, (e.g., glassivation crazing).

- (8) Detritus. Fragments of original or laser modified resistor material remaining in the kerf.

- (9) Die coat. A thin layer of soft polyimide coating applied to the surface of a semiconductor element that is intended to produce stress relief resulting from encapsulation and to protect the circuit from surface scratches.

- (10) Dielectric isolation. Electrical isolation of one or more elements of a monolithic semiconductor integrated circuit by surrounding the elements with an isolating barrier such as semiconductor oxide.

- (11) Dielectric layer or layers. Dielectric layer or layers deposited on the die surface to protect the redistribution metalization, and to create the contact via for solder bump pad.

- (12) Diffusion tub. A volume (or region) formed in a semiconductor material by a diffusion process (nor p- type) and isolated from the surrounding semiconductor material by a n-p or p-n junction or by a dielectric material (dielectric isolation, coplanar process, SOS, SOI).

- \* (13) Foreign material. Any material that is foreign to the microcircuit or package, or any nonforeign material that is displaced from its original or intended position within the microcircuit package.

- (14) Functional circuit elements. Diodes, transistors, crossunders, capacitors, and resistors.

Supersedes Page 3 of MIL-STD-883E

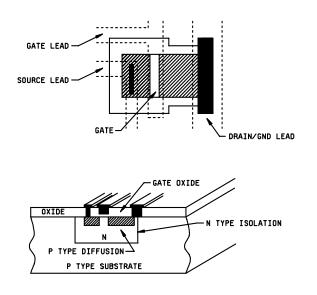

| ~ | (15) | Gate oxide. The oxide or other dielectric that separates gate metallization (or other material used for the gate electrode) from the channel of MOS structures (see figure 2010-1).                                                                                                                                                                                                                |

|---|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * | (16) | Glassivation. The top layer(s) of transparent insulating material that covers the active circuit area, with the exception of bonding pad areas and beam leads.                                                                                                                                                                                                                                     |

| * | (17) | Glassivation cracks. Fissures in the glassivation layer.                                                                                                                                                                                                                                                                                                                                           |

| * | (18) | Junction line. The outer edge of a passivation step that delineates the boundary between "P" and "N" type semiconductor material. An active junction is any P/N junction intended to conduct current during normal operation of the circuit element, (e.g., collector to base).                                                                                                                    |

| * | (19) | Kerf. That portion of the component area from which material has been removed or modified by trimming or cutting.                                                                                                                                                                                                                                                                                  |

| * | (20) | Line of separation. Visible distance or space between two features that are observed not to touch at the magnification in use.                                                                                                                                                                                                                                                                     |

| * | (21) | MESFET. (Metal semiconductor field-effect transistor). A field-effect transistor in which a metal semiconductor rectifying contact is used for the gate electrode. Typically the structure is fabricated in gallium arsenide and the term GaAs MESFET may be used. Both depletion-type and enhancement type devices have been manufactured. The acronyms are D-MESFET, and E-MESFET, respectively. |

| * | (22) | Metallization nonadherence. Unintentional separation of material from an underlying substrate excluding air bridges and undercutting by design.                                                                                                                                                                                                                                                    |

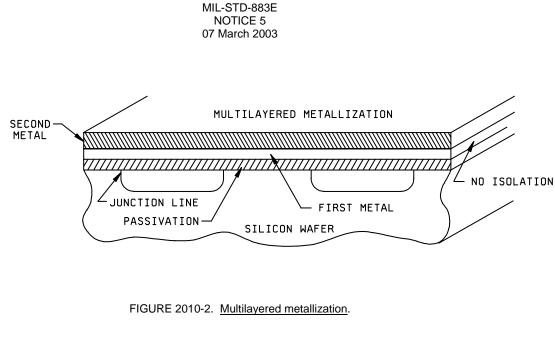

| * | (23) | Multilayered metallization (conductors). Two or more layers of metal or any other material used for interconnections that are not isolated from each other by insulating material. The term "underlying metal" shall refer to any layer below the top layer of metal (see figure 2010-2).                                                                                                          |

Supersedes Page 4 of MIL-STD-883E

4

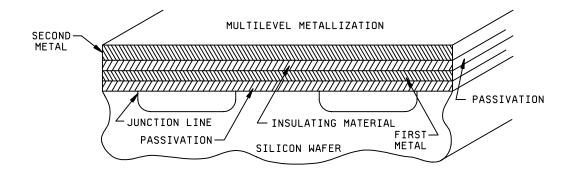

(24) Multilevel metallization (conductors). Two or more levels of metal or any other material used for interconnections that are isolated from each other by insulating material (also referred to as interlevel dielectric) (see figure 2010-3).

FIGURE 2010-3. Multilevel metallization.

- \* (25) Narrowest resistor width. The narrowest portion of a given resistor prior to trimming.

\* (26) Operating metallization (conductors). Metal or any other material used for interconnection except metallized scribe lines, test patterns, unconnected functional circuit elements, unused bonding pads, and identification markings.

\* (27) Original width. The width dimension or distance that would have been present, in the absence of the observed abnormality (e.g., original metal width, original diffusion width, original beam width, etc.).

\* (28) Package post. A generic term used to describe the bonding location on the package.

\* (29) Passivation. The silicon oxide, nitride or other insulating material that is grown or deposited

- (29) Passivation. The silicon oxide, nitride or other insulating material that is grown or deposited directly on the die prior to the deposition of metal or between metal levels on multilevel devices.

Supersedes Page 5 of MIL-STD-883E

| * | (3                         | 30) Passivation step. An abrupt change of elevation (level) of the passivation such as a contact<br>window, or operating metallization crossover.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

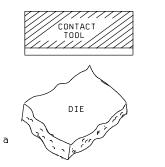

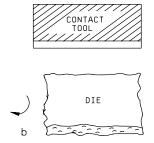

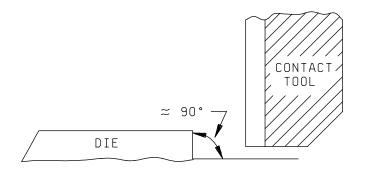

| * | (                          | 31) Peripheral metal. All metal that lies immediately adjacent to or over the scribe grid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |