This document and process conversion measures necessary to comply with this change shall be completed by 16 March 2020. **INCH - POUND**

MIL-STD-883-3 <u>16 September 2019</u> SUPERSEDING MIL-STD-883K w/CHANGE 3 3 May 2018

# DEPARTMENT OF DEFENSE TEST METHOD STANDARD ELECTRICAL TESTS (DIGITAL) FOR MICROCIRCUITS PART 3: TEST METHODS 3000-3999

AMSC N/A

FSC 5962

DISTRIBUTION STATEMENT A. Approved for public release. Distribution is unlimited.

## FOREWORD

1. This standard is approved for use by all Departments and Agencies of the Department of Defense.

2. This entire standard has been revised. This revision has resulted in many changes to the format, but the most significant one is the splitting the document into parts. See MIL–STD–883 for the change summary.

3. Comment, suggestions, or questions on this document should be addressed to: Commander, Defense Logistics Agency, ATTN: DLA Land and Maritime - VA, P.O. Box 3990, Columbus, OH 43218-3990, or by email to <u>STD883@dla.mil</u>. Since contact information can change, you may want to verify the currency of this address information using the ASSIST Online database at: <u>https://assist.dla.mil/</u>.

## CONTENTS

## PARAGRAPH

## Page

| Purpose                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General<br>Government documents<br>Non-Government publications                             | 1<br>1<br>3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| General<br>Test circuits<br>Destructive tests<br>Laboratory suitability                    | 8<br>8<br>8<br>8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DETAIL REQUIREMENTS                                                                        | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Intended use<br>International standardization agreement<br>Subject term (key word) listing | 8<br>8<br>8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                            | SCOPE       Purpose         Numbering system       APPLICABLE DOCUMENTS         General.       Government documents         Non-Government publications       Order of precedence         DEFINITIONS       Abbreviations, symbols, and definitions.         General.       General.         Test circuits       Destructive tests         Laboratory suitability       Method of reference         DETAIL REQUIREMENTS       DETAIL REQUIREMENTS         NOTES       Intended use.         International standardization agreement       Subject term (key word) listing         Supersession data       Supersession data. |

# ELECTRICAL TESTS (DIGITAL)

| 3001.1 | Drive source, dynamic                                                                       |

|--------|---------------------------------------------------------------------------------------------|

| 3002.1 | Load conditions                                                                             |

| 3003.1 | Delay measurements                                                                          |

| 3004.1 | Transition time measurements                                                                |

| 3005.1 | Power supply current                                                                        |

| 3006.1 | High level output voltage                                                                   |

| 3007.1 | Low level output voltage                                                                    |

| 3008.1 | Breakdown voltage, input or output                                                          |

| 3009.1 | Input current, low level                                                                    |

| 3010.1 | Input current, high level                                                                   |

| 3011.1 | Output short circuit current                                                                |

| 3012.1 | Terminal capacitance                                                                        |

| 3013.2 | Noise margin measurements for digital microelectronic devices                               |

| 3014   | Functional testing                                                                          |

| 3015.9 | Electrostatic discharge sensitivity classification                                          |

| 3016.1 | Activation time verification                                                                |

| 3017   | Microelectronics package digital signal transmission                                        |

| 3018   | Crosstalk measurements for digital microelectronic device packages                          |

| 3019.2 | Ground and power supply impedance measurements for digital microelectronics device packages |

| 3020   | High impedance (off-state) low-level output leakage current                                 |

| 3021   | High impedance (off-state) high-level output leakage current                                |

| 3022   | Input clamp voltage                                                                         |

| 3023.2 | Static latch-up measurements for digital CMOS microelectronic devices                       |

| 3024   | Simultaneous switching noise measurements for digital microelectronic devices               |

|        |                                                                                             |

#### 1. SCOPE

1.1 <u>Purpose</u>. Part 3 of this test method standard establishes uniform test methods for the electrical testing (digital) to determine resistance to deleterious effects of natural elements and conditions surrounding military operations. For the purpose of this standard, the term "devices" includes such items as monolithic, multichip, film and hybrid microcircuits, microcircuit arrays, and the elements from which the circuits and arrays are formed. This standard is intended to apply only to microelectronic devices.

1.2 <u>Numbering system</u>. The test methods are designated by numbers assigned in accordance with the following system:

1.2.1 <u>Classification of tests</u>. The electrical test methods included in this part of a multipart test method standard are numbered 3001 to 3024 inclusive.

1.2.2 <u>Test method revisions</u>. Revisions are numbered consecutively using a period to separate the test method number and the revision number. For example, 3001.2 designates the second revision of test method 3001.

#### 2. APPLICABLE DOCUMENTS

2.1 <u>General</u>. The documents listed in this section are specified in sections 3, 4, and 5 of this standard. This section does not include documents cited in other sections of this standard or recommended for additional information or as examples. While every effort has been made to ensure the completeness of this list, document users are cautioned that they must meet all specified requirements documents cited in sections 3, 4, and 5 of this standard, whether or not they are listed.

#### 2.2 Government documents.

2.2.1 <u>Specifications, standards, and handbooks</u>. The following specifications, standards, and handbooks form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### DEPARTMENT OF DEFENSE SPECIFICATIONS

| MIL-PRF-680   | - | Degreasing Solvent, Performance Specification For.                            |

|---------------|---|-------------------------------------------------------------------------------|

| MIL-PRF-19500 | - | Semiconductor Devices, General Specification For.                             |

| MIL-PRF-38534 | - | Hybrid Microcircuits, General Specification For.                              |

| MIL-PRF-38535 | - | Integrated Circuits (Microcircuits) Manufacturing, General Specification For. |

|               |   |                                                                               |

### DEPARTMENT OF DEFENSE STANDARDS

| MIL-STD-202<br>MIL-STD-750 | - | Electronic and Electrical Component Parts.<br>Test Methods for Semiconductor Devices.    |

|----------------------------|---|------------------------------------------------------------------------------------------|

| MIL-STD-1686               | - | Electrostatic Discharge Control Program for Protection of Electrical and Electronic      |

|                            |   | Parts, Assemblies and Equipment (Excluding Electrically Initiated Explosive<br>Devices). |

|                            | - | Electronic Component Case Outlines.                                                      |

| MIL-STD-1916               | - | DOD Preferred Methods for Acceptance of Product.                                         |

#### DEPARTMENT OF DEFENSE HANDBOOKS

| MIL-HDBK-217  | - | Reliability Prediction of Electronic Equipment.                                |

|---------------|---|--------------------------------------------------------------------------------|

| MIL-HDBK-505  | - | Definitions of Item Levels, Item Exchangeability, Models, and Related Terms.   |

| MIL-HDBK-781  | - | Reliability Test Methods, Plans, and Environments for Engineering, Development |

|               |   | Qualification, and Production .                                                |

| MIL-HDBK-1331 | - | Parameters to be Controlled for the Specification of Microcircuits.            |

#### FEDERAL STANDARDS

| SAE AMS-STD-595       | - | Colors Used in Government Procurement |

|-----------------------|---|---------------------------------------|

| SAE AMS-STD-595/15102 | - | Blue, Gloss                           |

| SAE AMS-STD-595/25102 | - | Blue, Semi-gloss                      |

## OTHER GOVERNMENT DOCUMENTS, DRAWINGS, AND PUBLICATIONS

| QML-38534 | - | Hybrid Microcircuits, General Specification For.                             |

|-----------|---|------------------------------------------------------------------------------|

| QML-38535 | - | Integrated Circuits (Microcircuits) Manufacturing, General Specification For |

#### COMMERCIAL ITEM DESCRIPTIONS

A-A-58092 - Tape, Antiseize, Polytetrafluorethylene.

(Copies of these documents are available online at https://quicksearch.dla.mil.)

2.3 <u>Non-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

INTERNATIONAL ORGANIZATION FOR STANDARDIZATION (ISO) STANDARDS

| ISO 14644-1 | <ul> <li>Cleanrooms and Associated Controlled Environments – Part 1: Classification of Air<br/>Cleanliness.</li> </ul>                                                        |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISO 14644-2 | <ul> <li>Cleanrooms and Associated Controlled Environments – Part 2: Specifications for<br/>Testing and Monitoring to Prove Continued Compliance with ISO 14644-1.</li> </ul> |

ISO /ASTM 51275 - Standard Practice for Use of a Radiochromic Film Dosimetry System.

(Copies of these documents are available online at https://www.iso.org)

AMERICAN NATIONAL STANDARDS INSTITUTE (ANSI)

ANSI/NCSL Z540.3 - Requirements for the Calibration of Measuring and Test Equipment, General Requirements.

(Copies of these documents are available online at https://ansi.org)

IPC - ASSOCIATION CONNECTING ELECTRONICS INDUSTRIES (IPC)

| IPC J-STD-004 | <ul> <li>Requirements for Soldering Fluxes.</li> </ul>                            |

|---------------|-----------------------------------------------------------------------------------|

| IPC J-STD-005 | - Requirements for Soldering Pastes.                                              |

| IPC J-STD-006 | - Requirements for Electronic Grade Solder Alloys and Fluxed and Non-fluxed Solid |

|               | Solders for Electronic Soldering Applications.                                    |

| IPC J-STD-033 | - Handling, Packing, Shipping and Use of Moisture/Reflow Sensitive Surface Mount  |

|               | Devices.                                                                          |

| IPC-T-50      | - Terms and Definitions for Interconnecting and Packaging Electronic Circuits.    |

(Copies of these documents are available online at https://www.ipc.org)

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC).

| JEDEC JESD22-B116   | - Wire Bond Shear Test                                                |

|---------------------|-----------------------------------------------------------------------|

| JEDEC JESD78        | - IC Latch-up Test.                                                   |

| JEDEC JESD213       | - Common Test Method for Detection Component Surface Finish Material. |

| JEDEC Standard 12   | - Standard for Gate Array Benchmark Set                               |

| JEDEC Standard 12-1 | - Terms and Definitions for Gate Array Benchmark Set.                 |

| JEDEC Standard 12-2 | - Standard for Cell-Based Integrated Circuit Benchmark Set.           |

| JEDEC Standard 12-3 | - CMOS Gate Array Macrocell Standard.                                 |

|                     |                                                                       |

(Copies of these documents are available online at https://www.jedec.org)

#### NATIONAL COUNCIL ON RADIAATION PROTECTION AND MEASUREMENT

| Report Number 40  | - | Protection Against Radiation from Brachytherapy Sources |

|-------------------|---|---------------------------------------------------------|

| Report Number 102 | - | Medical X-ray, Electron Beam and Gamma Ray Protection   |

(Copies of these documents are available online at <u>http://www.NCRPPublications.org</u>) TECHSTREET THOMPSON REUTERS

| TechAmerica EIA-557 | - | Statistical Process Control Systems |

|---------------------|---|-------------------------------------|

|---------------------|---|-------------------------------------|

(Copies of these documents are available online at https://www.techstreet.com)

## AMERICAN SOCIETY FOR TESTING AND MATERIALS (ASTM)

| ASTM C 1 | 77 -  | Standard Test Method for Steady-State Heat Flux Measurements and Thermal<br>Transmission Properties by Means of the Guarded Hot-Plate Apparatus.                                 |

|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASTM C 5 | 18 -  | Standard Test Method for Steady-State Heat Flux Measurements and Thermal Transmission Properties by Means of the Heat Flow Meter Apparatus.                                      |

| ASTM D 1 | 50 -  | Standard Test Methods for A-C Loss Characteristics and Permittivity (Dielectric Constant) of Solid Electrical Insulating Materials.                                              |

| ASTM D 2 | 57 -  | Standard Test Methods for D-C Resistance or Conductance of Insulating Materials.                                                                                                 |

| ASTM D 8 | -77 - | Standard Test Methods for Dielectric Breakdown Voltage of Insulating Liquids Using Disk Electrodes.                                                                              |

| ASTM D 9 | 71 -  | Interfacial Tension of Oil Against Water by the Ring Method.                                                                                                                     |

| ASTM D 1 |       | Standard Test Method for Strength Properties of Adhesives in Shear by Tension                                                                                                    |

|          |       | Loading (Metal-to-Metal).                                                                                                                                                        |

| ASTM D 1 | 120 - | Engine Coolant, Boiling Point of.                                                                                                                                                |

| ASTM D 1 | 331 - | Standard Test Methods for Surface and Interfacial Tension of Solutions of Surface-                                                                                               |

|          |       | Active Agents.                                                                                                                                                                   |

| ASTM D 2 | - 109 | Standard Test Methods for Nonvolatile Matter in Halogenated Organic Solvents and their Admixtures.                                                                               |

| ASTM D 3 | 574 - | Materials, Flexible Cellular-Slab, Bonded, and Molded Uretane Foam.                                                                                                              |

| ASTM D 3 | 850 - | Rapid Thermal Degradation of Solid Electrical Insulating Materials by                                                                                                            |

|          |       | Thermogravimetric Method, Test Method for.                                                                                                                                       |

| ASTM E 2 | 63 -  | Standard Test Method for Measuring Fast-Neutron Reaction Rates by                                                                                                                |

|          |       | Radioactivation of Iron.                                                                                                                                                         |

| ASTM E 2 | 64 -  | Standard Test Method for Measuring Fast-Neutron Reaction Rates by Radioactivation of Nickel.                                                                                     |

| ASTM E 2 | 65 -  | Standard Test Method for Measuring Reaction Rates and Fast-Neutron Fluences by Radioactivation of Sulfur-32.                                                                     |

| ASTM E 6 | 66 -  | Standard Practice for Calculating Absorbed Dose from Gamma or X-Radiation.                                                                                                       |

| ASTM E 6 | 68 -  | Standard Practice for Application of Thermoluminescence-Dosimetry (TLD) Systems                                                                                                  |

|          |       | for Determining Absorbed Dose on Radiation Hardness Testing of Electronic Devices.                                                                                               |

| ASTM E 7 | 20 -  | Standard Guide for Selection and Use of Neutron Sensors for Determining Neutron<br>Spectra Employed in Radiation-Hardness Testing of Electronics.                                |

| ASTM E 7 | 21 -  | Standard Method for Determining Neutron Energy Spectra with Neutron-Activation                                                                                                   |

|          | 21 -  | Foils for Radiation-Hardness Testing of Electronics.                                                                                                                             |

| ASTM E 7 | 22 -  | Standard Practice for Characterizing Neutron Energy Fluence Spectra in Terms of<br>an equivalent Monoenergetic Neutron Fluence for Radiation-Hardness Testing of<br>Electronics. |

AMERICAN SOCIETY FOR TESTING AND MATERIALS (ASTM) (CONTINUED)

| ASTM E 801                 | <ul> <li>Standard Practice for Controlling Quality of Radiological Examination of Electronic<br/>Devices.</li> </ul>                                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASTM E 831                 | <ul> <li>Standard Test Method for Linear Thermal Expansion of Solid Materials by<br/>Thermomechanical Analysis</li> </ul>                                                                                              |

| ASTM E 1249                | <ul> <li>Minimizing Dosimetry Errors in Radiation Hardness Testing of Silicon Electronic<br/>Devices.</li> </ul>                                                                                                       |

| ASTM E 1250                | <ul> <li>Standard Method for Application of Ionization Chambers to Assess the Low Energy<br/>Gamma Component of Cobalt 60 Irradiators Used in Radiation Hardness Testing of<br/>Silicon Electronic Devices.</li> </ul> |

| ASTM E 2450                | <ul> <li>Standard Practice for Application of CaF<sub>2</sub>(Mn) Thermoluminescence Dosimeters in<br/>Mixed Neutron-Photon Environments.</li> </ul>                                                                   |

| ASTM F 458                 | <ul> <li>Standard Practice for Nondestructive Pull Testing of Wire Bonds.</li> </ul>                                                                                                                                   |

| ASTM F 459                 | - Standard Test Methods for Measuring Pull Strength of Microelectronic Wire Bonds.                                                                                                                                     |

| ASTM F 526                 | <ul> <li>Standard Test Method for Measuring Dose for Use in Linear Accelerator Pulsed<br/>Radiation Effects Tests.</li> </ul>                                                                                          |

| ASTM F 1192<br>ASTM F 1892 | <ul> <li>Standard Guide for the Measurement of Single Event Phenomena (SEP).</li> <li>Standard Guide for Ionizing Radiation (Total Dose) Effects Testing of Semiconductor Devices.</li> </ul>                          |

(Copies of these documents are available online at https://www.astm.org/)

2.4 <u>Order of precedence</u>. Unless otherwise noted herein or in the contract, in the event of a conflict between the text of this document and the references cited herein, the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. DEFINITIONS

3.1 <u>Abbreviations, symbols, and definitions</u>. For the purpose of this standard, the abbreviations, symbols, and definitions specified in MIL-PRF-19500, MIL-PRF-38535, or MIL-HDBK-505 apply. The following definitions also apply:

3.1.1 <u>Microelectronic device</u>. A microcircuit, microcircuit module, or an element of a microcircuit as defined in appendix A of MIL-PRF-38535. For the purposes of this document, each type of microelectronic device will be identified by a unique type, or drawing number.

3.1.2 <u>Mode of failure</u>. The cause for rejection of any failed device or microcircuit as defined in terms of the specific electrical or physical requirement which it failed to meet (i.e., no failure analysis is required to identify the mode of failure, which should be obvious from the rejection criteria of the test method).

3.1.3 <u>Mechanism of failure</u>. The original defect which initiated the microcircuit or device failure or the physical process by which the degradation proceeded to the point of failure, identifying quality defects, internal, structural, or electrical weakness and, where applicable, the nature of externally applied stresses which led to failure.

3.1.4 <u>Absolute maximum ratings</u>. The values specified for ratings, maximum ratings, or absolute maximum ratings are based on the "absolute system" and are not to be exceeded under any measurable or known service or conditions. In testing microelectronic devices, limits may be exceeded in determining device performance or lot quality, provided the test has been determined to be nondestructive and precautions are taken to limit device breakdown and avoid conditions that could cause permanent degradation. These ratings are limiting values beyond which the serviceability of any individual microelectronic integrated circuit may be impaired. It follows that a combination of all the absolute maximum ratings cannot normally be attained simultaneously. Combinations of certain ratings are permissible only if no single maximum rating is exceeded under any service conditions. Unless otherwise specified, the voltage, current, and power ratings are based on continuous dc power conditions at free air ambient temperature of 25°C ±3°C. For pulsed or other conditions of operation of a similar nature, the current, voltage, and power dissipation ratings are a function of time and duty cycle. In order not to exceed absolute ratings, the equipment designer has the responsibility of determining an average design value, for each rating, below the absolute value of that rating by a safety factor, so that the absolute values will never be exceeded under any usual conditions of supply-voltage variations, load variations, or manufacturing variations in the equipment itself.

3.1.5 <u>Worst case condition</u>. Worst case condition(s) consists of the simultaneous application of the most adverse (in terms of required function of the device) values (within the stated operating ranges) of bias(es), signal input(s), loading and environment to the device under test. Worst cases for different parameters may be different. If all the applied test conditions are not established at the most adverse values, the term "partial worst case condition" should be used to differentiate and should be accompanied by identification of the departure from worst case. For example, the lowest values of supply voltages, signal input levels, and ambient temperature and the highest value of loading may constitute "worst case conditions" for measurement of the output voltage of a gate. Use of the most adverse values of applied electrical conditions, at room temperature, would then constitute "partial worst case conditions" and should be so identified using a postscript "at room temperature."

3.1.5.1 <u>Accelerated test condition</u>. Accelerated test conditions are defined as test conditions using one or more applied stress levels which exceed the maximum rated operating or storage stress levels but are less than or equal to the "Testing Rating" values.

3.1.6 <u>Static parameters</u>. Static parameters are defined as dc voltages, dc currents, or ratios of dc voltages or dc currents, or both.

3.1.7 <u>Dynamic parameters</u>. Dynamic parameters are defined as those which are rms or time-varying values of voltages or currents, or ratios of rms or time-varying values of voltages or currents, or both.

3.1.8 <u>Switching parameters</u>. Switching parameters are defined as those which are associated with the transition of the output from one level to another or the response to a step input.

3.1.9 <u>Functional tests</u>. Functional tests are defined as those go, no-go tests which sequentially exercise a function (truth) table or in which the device is operated as part of an external circuit and total circuit operation is tested.

3.1.10 <u>Acquiring activity</u>. The acquiring activity is the organizational element of the Government which contracts for articles, supplies, or services; or it may be a contractor or subcontractor when the organizational element of the Government has given specific written authorization to such contractor or subcontractor to serve as agent of the acquiring activity. A contractor or subcontractor serving as agent of the acquiring activity does not have the authority to grant waivers, deviations, or exceptions unless specific written authorization to do so has also been given by the Government organization.

3.1.11 <u>Accuracy</u>. The quality of freedom from error. Accuracy is determined or assured by calibration, or reliance upon calibrated items.

3.1.12 <u>Calibration</u>. Comparison of measurement standard or instrument of known accuracy with another standard, instrument or device to detect, correlate, report or eliminate by adjustment, any variation in the accuracy of the item being compared. Use of calibrated items provide the basis for value traceability of product technical specifications to national standard values. Calibration is an activity related to measurement and test equipment performed in accordance with ANSI/NCSL Z540.3 or equivalent.

3.1.13 <u>Precision</u>. The degree to which an instrument, device, assemblage, test, measurement or process exhibits repeatability. Expressed statistically or through various techniques of Statistical Process Control (SPC). Term is used interchangeably with "repeatability".

3.1.14 <u>Resolution</u>. The smallest unit of readability or indication of known value in an instrument, device or assemblage thereof.

3.1.15 <u>Standard reference material (SRM)</u>. A device or artifact recognized and listed by the National Institute of Standards and Technology (NIST) as having known stability and characterization. SRM's used in product testing provide traceability for technical specifications. SRM's do not require calibration when used and stored in accordance with NIST accompanying instructions. They are used as "certified materials".

3.1.16 <u>Tolerance</u>. A documented range over which a specified value may vary.

3.1.17 <u>Test accuracy ratio (TAR)</u>. A ratio of the tolerance of the device under test to the accuracy of the related measuring or test instrument or to the accuracy of the correlation device/SRM.

3.1.18 <u>Uncertainty</u>. An expression of the combined errors in a test measurement process. Stated as a range within which the subject quantity is expected to lie. Comprised of many components including: estimates of statistical distribution and results of measurement or engineering analysis. Uncertainty established with a suitable degree of confidence, may be used in assuring or determining product conformance and technical specifications.

3.1.19 <u>Susceptibility</u>. The point at which a device fails to meet the postirradiation end-point electrical parameter limits or fails functionally during radiation exposure (e.g., neutron irradiation).

3.1.20 <u>Class M</u>. Class M is defined as 1.2.1 of MIL-STD-883 basic compliant product or product built in compliance to Appendix A of MIL-PRF-38535 documented on a Standard Microcircuit Drawing where configuration control is provided by the Government preparing activity. Class M devices are required to use the conditions specified in the test methods herein for class level B product.

3.1.21 <u>Class level B and class level S</u>. 2 class levels are used in this document to define requirements for high reliability military applications (Class level B) and space applications (Class level S). Class level B requirements contained in this document are intended for use for Class Q, Class H, and Class M products, as well as Class B M38510 JAN slash sheet product. Class level B requirements are also intended for use for product claimed as 883 compliant or 1.2.1 compliant for high reliability military applications. Class level S requirements contained in this document are intended for use for Class V, Class K, as well as M38510 Class S JAN slash sheet product. Class level S requirements are also intended for use for Class V, Class K, as well as M38510 Class S JAN slash sheet product. Class level S requirements are also intended for use for product claimed as 883 compliant or 1.2.1 of MIL-STD-883 basic compliant for space level applications.

3.1.22 <u>Acquisition documents</u>. Acquisition documents consist of the acquisition order or contract, device specification (e.g. SMD's, SCD's) or specifications as applicable.

#### 4. GENERAL REQUIREMENTS

4.1 <u>General</u>. Unless otherwise specified in the individual test method, the general requirements of MIL-STD-883 shall apply.

4.2 <u>Test circuits</u>. The test circuits shown in the test methods of this test method standard are given as examples which may be used for the measurements. They are not necessarily the only test circuits which can be used; however the manufacturer shall demonstrate to the Government that other test circuits which they may desire to use will give results within the desired accuracy of measurement.

4.3 <u>Destructive tests</u>. Unless otherwise demonstrated, the test methods listed in table I shall be classified as destructive. <u>MIL-STD-883</u> covers the necessary actions needed to reclassify a test method as non-destructive.

| Test method number | Test                                                  |

|--------------------|-------------------------------------------------------|

| 3015               | Electrostatic discharge sensitivity<br>classification |

TABLE I. Destructive tests.

4.4 <u>Laboratory suitability</u>. Prior to processing any microcircuit intended for use in any military system or subsystem, the facility performing the test(s) shall be audited by the DLA Land and Maritime, Sourcing and Qualification Division and be granted written laboratory suitability status for each test method to be employed. Processing of any devices by any facility without laboratory suitability status for the test methods used shall render the processed devices nonconforming.

4.5 <u>Method of reference</u>. When applicable, test methods contained herein shall be referenced in the individual specification or specification sheet by specifying the test method number and, the details required in the summary of the applicable test method shall be listed. To avoid the necessity for changing documents that refer to test methods of this standard, the revision number should not be used when referencing test methods. (For example: Use 1001 versus 1001.2.)

## 5. DETAILED REQUIREMENTS

This section is not applicable to this standard.

#### 6. NOTES

(This section contains information of a general or explanatory nature that may be helpful, but is not mandatory.)

6.1 <u>Intended use</u>. The intended use of this test method standard is to establish appropriate conditions for testing semiconductor devices to give test results that simulate the actual service conditions existing in the field. This test method standard has been prepared to provide uniform test methods, controls, and procedures for determining with predictability the suitability of such devices within military, aerospace and special application equipment.

6.2 <u>International standardization agreement</u>. Certain provisions of this test method standard are the subject of international standardization agreement. When amendment, revision, or cancellation of this test method standard is proposed which will affect or violate the international agreement concerned, the preparing activity will take appropriate reconciliation action through international standardization channels, including departmental standardization offices, if required.

6.3 Subject term (key word) listing

Destructive tests Environmental tests Laboratory suitability Non–destructive tests

6.4 <u>Supersession data</u> The main body and five parts (-1 through -5) of this revision of MIL-STD-883 replace superseded MIL-STD-883K

MIL-STD-883-3

This page intentionally left blank

#### METHOD 3001.1

#### DRIVE SOURCE, DYNAMIC

1. <u>PURPOSE</u>. This method establishes a drive source to be used in measuring dynamic performance of digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The drive source shall supply a smooth transition between specified voltage levels. The signal characteristics shall not vary outside of their prescribed tolerances when interfaced with the device under test (device in the test socket).

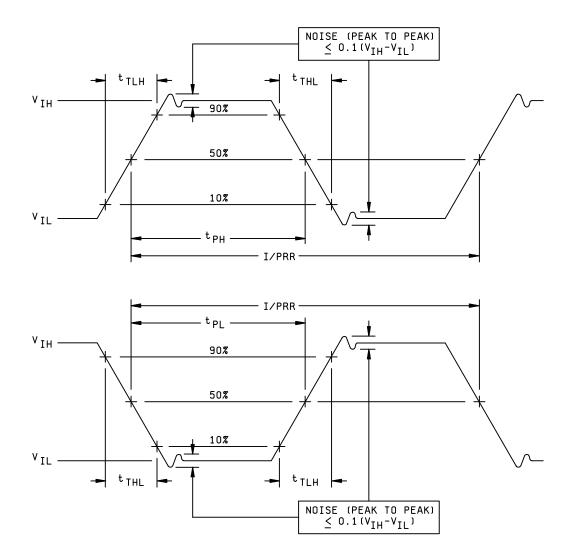

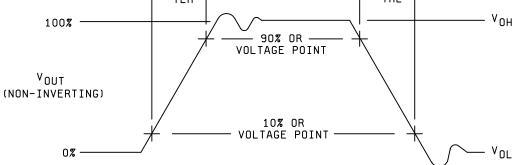

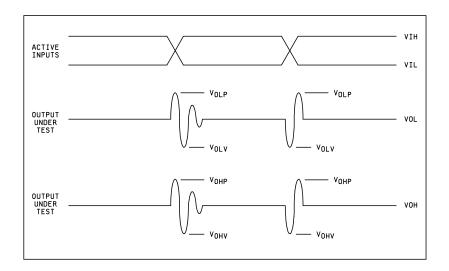

3. <u>PROCEDURE</u>. The drive source shall be measured at the input terminal of the test socket (no device in the test socket). Figure 3001-1 shows typical driving source waveforms and should be used specifying the parameters shown, unless otherwise stated in the applicable acquisition document.

3.1 <u>Pulse amplitude</u>. The specified HIGH level of the driving source shall be greater than the  $V_{OH}$  of the device. The specified LOW level of the driving source shall be less than  $V_{OL}$  of the device.

3.2 <u>Transition times</u>. The transition times of the driving source  $(t_{THL} \text{ and } t_{TLH})$  shall be faster than the transition time of the device being tested, unless otherwise stated in the acquisition document. The transition times shall normally be measured between the 10 percent and 90 percent levels of the specified pulse.

3.3 <u>Pulse repetition rate (PRR)</u>. Unless the pulse repetition rate is the parameter being tested, it shall be chosen so that doubling the rate or reducing by a half will not affect the measurement results.

3.4 <u>Duty factors (duty cycles)</u>. The duty cycles of the driving source shall be chosen so that a 10 percent variation in the duty cycle will not affect the measurement results. The duty cycle shall be defined with respect to either a positive or negative pulse. The pulse width  $(t_p)$  of the input pulses shall be measured between the specified input measurement levels. When more than one pulse input is needed to test a device, the duty cycle of the prime input (i.e., clock, etc.) shall be specified. The phase relationship of all other input pulses shall be referenced to the prime input pulse.

4. <u>SUMMARY</u>. The following details, when applicable, shall be specified in the applicable acquisition document:

- a. Levels VIL and VIH.

- b. Driving signal transition times.

- c. Pulse repetition rate.

- d. Duty factors.

- e. Recommended pulse generator, if required.

- f. Input measurement levels, if other than those shown in figure 3001-1.

FIGURE 3001-1. Drive sources.

#### METHOD 3002.1

#### LOAD CONDITIONS

1. <u>PURPOSE</u>. This method establishes the load conditions to be used in measuring the static and dynamic performance of digital microelectronic devices such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The load for static tests shall simulate the worst case conditions for the circuit parameters being tested. The load for dynamic tests shall simulate a specified use condition for the parameters being tested. The loads shall be specified in the applicable acquisition document.

2.1 <u>Discrete component load</u>. The load will consist of any combination of capacitive, inductive, resistive, or diode components.

2.1.1 <u>Capacitive load (CL)</u>. The total load capacitance of the circuit under test shall include probe and test fixture capacitance and a compensating capacitor as required. The value of the capacitance, measured at 1 MHz  $\pm$ 10 percent, shall be specified in the applicable acquisition document.

2.1.2 Inductive load ( $L_L$ ). The total load inductance of the circuit under test shall include probe and test fixture inductance and a compensating inductor as required. The value of the inductance, measured at 1 MHz ±10 percent, shall be specified in the applicable acquisition document.

2.1.3 <u>Resistive load (R</u><sub>L</sub>). The resistive load shall represent the worst case fan out conditions of the device under test for static tests and a specified fan out condition for dynamic tests. For sink loads, the resistor shall be connected between the power supply (V<sub>CC</sub> or V<sub>DD</sub>) and the circuit output for TTL, DTL, RTL, C-MOS, and MOS (N-Channel) and between circuit output and ground for MOS (P-Channel). For source loads, the resistor shall be connected between circuit output and ground for TTL, DTL, RTL, C-MOS, and MOS (N-Channel) and between V<sub>DD</sub> and the circuit output for MOS (P-Channel). For source loads, the resistor shall be connected between circuit output and ground for TTL, DTL, RTL, C-MOS, and MOS (N-Channel) and between V<sub>DD</sub> and the circuit output for MOS (P-Channel). For ECL devices, the load resistors are connected from the output to a specified negative voltage.

2.1.4 <u>Diode load (DL)</u>. The diode load shall represent the input diode(s) of the circuit under test. The equivalent diode, as specified in the applicable acquisition document, will also represent the base-emitter or base-collector diode of any transistor in the circuit path of the normal load.

2.2 <u>Dynamic load change</u>. The load shall automatically change its electrical parameters as the device under test changes logic state if this is the normal situation for the particular family of circuits being tested. One method of accomplishing this dynamic change is to simulate devices or use actual devices from the same logic family equal to the specified load.

3. <u>PROCEDURE</u>. The load will normally be paralleled by a high impedance voltage detection indicator. The indicator may be either visual or memory storage.

4. <u>SUMMARY</u>. The following shall be defined in the applicable acquisition document:

- a. Capacitive load (see 2.1.1).

- b. Inductive load (see 2.1.2).

- c. Resistive load (see 2.1.3).

- d. Diode load, the 1NXXX number and any associated critical parameters shall be specified (see 2.1.4).

- e. Negative voltage, when using a resistive load for ECL (see 2.1.3).

MIL-STD-883-3

This page intentionally left blank

#### METHOD 3003.1

#### DELAY MEASUREMENTS

1. <u>PURPOSE</u>. This method established the means for measuring propagation delay of digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

1.1 <u>Definitions</u>. The following definitions for the purpose of this test method shall apply.

1.1.1 <u>Propagation delay time (tPHL</u>). The time measured with the specified output changing from the defined HIGH level to the defined LOW level with respect to the corresponding input transition.

1.1.2 <u>Propagation delay time ( $t_{PLH}$ )</u>. The time measured with the specified output changing from the defined LOW level to the defined HIGH level with respect to the corresponding input transition.

2. <u>APPARATUS</u>. Equipment capable of measuring elapsed time between the input signal and output signal at any percentage point or voltage point between the maximum LOW level and minimum HIGH level shall be provided. The input shall be supplied by a driving source as described in method 3001 of this standard. It is desirable for this equipment to have data logging capability so that circuit dynamic performance can be monitored. The test chamber shall be capable of maintaining the device under test at any specified temperature.

3. <u>PROCEDURE</u>. The test circuit shall be loaded according to method 3002 of this standard. The driving signal to the test circuit shall be provided according to method 3001 of this standard. The device shall be stabilized at the specified test temperature.

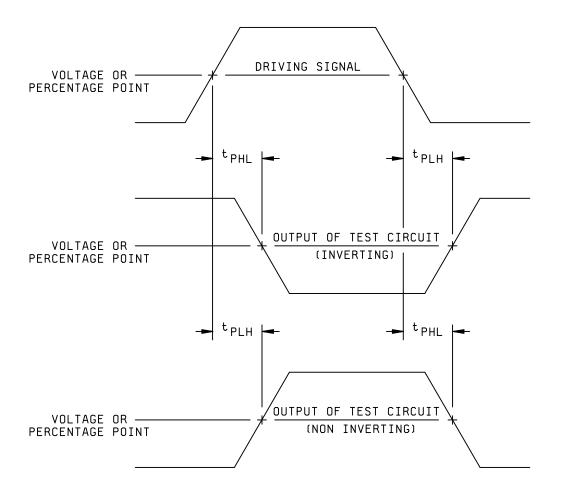

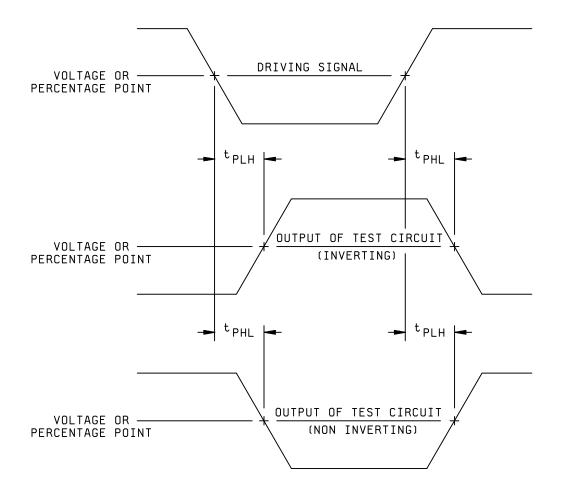

3.1 <u>Measurements at a voltage point</u>.  $t_{PLH}$  and  $t_{PHL}$  shall be measured from the threshold voltage point on the driving signal to the threshold voltage point on the test circuit output signal for both inverting and noninverting logic. These delays shall be measured at the input and output terminals of the device under test. The device under test shall be conditioned according to the applicable acquisition document with nominal bias voltages applied. Figures 3003-1 and 3003-2 show typical delay measurements.

3.2 <u>Measurements at percentage points</u>. t<sub>PLH</sub> and t<sub>PHL</sub> shall be measured from a specified percentage point on the driving signal to a specified percentage point on the test circuit output signal for both inverting and noninverting logic. These delays shall be measured at the input and output terminals of the device under test. The device under test shall be conditioned according to the applicable acquisition document with nominal bias voltages applied. Figures 3003-1 and 3003-2 show typical delay measurements.

4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. tPLH and tPHL limits.

- b. Parameters of the driving signal: t<sub>THL</sub>, t<sub>TLH</sub>, high Level, low Level, pulse width, repetition rate.

- c. Load conditions.

- d. Conditioning voltages (static or dynamic).

- e. Measurement points (see 3.1 and 3.2).

- f. Power supply voltages.

- g. Test temperature.

MIL-STD-883-3

FIGURE 3003-1. Propagation delay-positive input pulse.

MIL-STD-883-3

FIGURE 3003-2. Propagation delay - negative input pulse.

MIL-STD-883-3

This page intentionally left blank

#### METHOD 3004.1

#### TRANSITION TIME MEASUREMENTS

1. <u>PURPOSE</u>. This method establishes the means for measuring the output transition times of digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

1.1 <u>Definitions</u>. The following definitions shall apply for the purpose of this method.

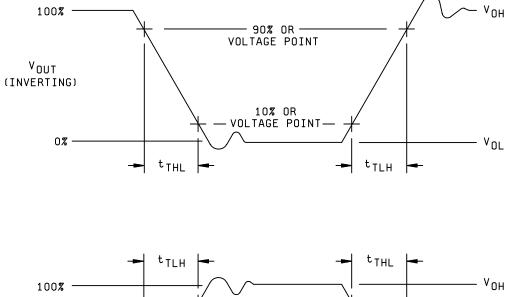

1.1.1 <u>Rise time ( $t_{TLH}$ )</u>. The transition time of the output from 10 percent to 90 percent or voltage levels of output voltage with the specified output changing from the defined LOW level to the defined HIGH level.

1.1.2 Fall time ( $t_{THL}$ ). The transition time of the output from 90 percent to 10 percent or voltage levels of output voltage with the specified output changing from the defined HIGH level to the defined LOW level.

2 <u>APPARATUS</u>. Equipment capable of measuring the elapsed time between specified percentage points (normally 10 percent to 90 percent on the positive transition and 90 percent to 10 percent on the negative transition) or voltage levels. The test chamber shall be capable of maintaining the device under test at any specified temperature.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. The device under test shall be loaded as specified in the applicable acquisition document. The load shall meet the requirements specified in method 3002 of this document. The driving signal shall be applied as specified in method 3001 or the applicable acquisition document.

3.1 <u>Measurement of t<sub>TLH</sub> and t<sub>THL</sub></u>. Unless otherwise stated, the rise transition time (t<sub>TLH</sub>) shall be measured between the 10 percent and 90 percent points on the positive transition of the output pulse and the fall transition time (t<sub>THL</sub>) shall be measured between the 90 percent and 10 percent points on the negative transition of the output pulse. The device under test shall be conditioned according to the applicable acquisition document with nominal bias voltages applied. Figure 3004-1 shows typical transition time measurement.

- 4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. t<sub>TLH</sub> limits.

- b. t<sub>THL</sub> limits.

- c. Transition time measurement points if other than 10 percent or 90 percent.

- d. Parameters of the driving signal.

- e. Conditioning voltages (static or dynamic).

- f. Load condition.

- g. Power supply voltages.

- h. Test temperature.

FIGURE 3004-1. Transition time measurements.

#### METHOD 3005.1

#### POWER SUPPLY CURRENT

1. <u>PURPOSE</u>. This method establishes the means for measuring power supply currents of digital microelectronic devices such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. Equipment capable of applying prescribed voltage to the test circuit power supply terminals and measuring the resultant currents flowing in these terminals shall be provided. The test chamber shall be capable of maintaining the device under test at any specified temperature.

3. PROCEDURE. The device shall be stabilized at the specified test temperature.

3.1 <u>I<sub>CCH</sub> (logic gate</u>). Inputs of the device under test shall be conditioned in such a way as to provide a HIGH level at the output, the worst case supply voltage(s) shall be applied and the resultant current flow in the supply terminals measured.

3.2 <u>IccL</u> (logic gate). Inputs of the device under test shall be conditioned in such a way as to provide a LOW level at the output, the worst case supply voltages(s) shall be applied and the resultant current flow in the supply terminals measured.

3.3 <u>Icc or IEE of combinatorial digital circu</u>its. The inputs of the device under test shall be conditioned to put the device into its worst case power dissipating state. The current flowing into the  $V_{CC}$ , (positive supply) terminal, or out of the  $V_{EE}$  (negative supply) terminal shall be measured with the  $V_{CC}$  and  $V_{EE}$  voltages at their maximum specified operating levels.

3.4 <u>Icc or IEE of sequential digital circuits</u>. The inputs of the device under test shall be exercised to put the device in a known output state (either HIGH or LOW) that causes worst case power dissipation. The current flowing into the  $V_{CC}$  (positive supply) terminal, or out of the  $V_{EE}$  (negative supply) terminal shall be measured with the  $V_{CC}$  and  $V_{EE}$  voltages at their maximum specified operating levels.

3.5 <u>IDD (MOS logic gate)</u>. Inputs of the device under test shall be conditioned in such a way as to provide a HIGH level at the output of MOS (P-Channel and C-MOS) or a LOW level at the output of MOS (N-Channel and C-MOS); worst case voltage(s) shall be applied and the resultant current in the supply terminals measured.

3.6  $I_{GG}$  (MOS P-Channel and N-Channel logic gates). Inputs of the device under test shall be conditioned in such a way as to provide a HIGH level at the output of MOS (P-Channel) or a LOW level at the output of MOS (N-Channel); worst case voltage(s) shall be applied and the resultant current flow in the supply terminals measured.

3.7 IDD of MOS combinatorial circuits. See 3.3 above.

3.8 IDD of MOS sequential circuits. See 3.4 above.

3.9 I<sub>GG</sub> of MOS combinatorial circuits. See 3.3 above.

3.10 IGG of MOS sequential circuits. See 3.4 above.

3.11 IDD dynamic (MOS logic gating and flip flop circuits). The driving signal to the test circuit shall be provided according to method 3001 of this standard; the worst case voltage(s) shall be applied and the resultant average current in the supply terminals measured.

- 4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Power supply voltages.

- c. ICCH, ICCL, IDD, IGG, and IEE limits.

- d. Conditioning voltages.

- e. Dynamic input parameters (see 3.11).

#### METHOD 3006.1

#### HIGH LEVEL OUTPUT VOLTAGE

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document in regard to HIGH level output drive, which may be specified as a minimum value  $V_{OH}$  min. or as a maximum  $V_{OH}$  max. This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The test instrument shall be capable of loading the output of the circuit under test with the specified positive or negative currents ( $I_{OH}$ ). Resistors may be used to simulate the applicable current levels. The test instrument shall also be capable of supplying the worst case power supply and input voltages. The test chamber shall be capable of maintaining the device under test at any specified test temperature.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Worst case power supply voltages and worst case input levels including guaranteed noise margins shall be applied to the test circuit to provide a HIGH level output. Forcing current, equal to the circuit worst case high level fan out, shall then be applied to the test circuit output terminal and the resultant output voltage measured. The output measurement shall be made after each input is conditioned.

- 4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Current to be forced from or into output terminal.

- c. Power supply voltage(s).

- d. Input levels.

- e. VOH min. or VOH max. limits.

MIL-STD-883-3

This page intentionally left blank

#### METHOD 3007.1

#### LOW LEVEL OUTPUT VOLTAGE

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document with regard to LOW level output drive which is specified as a maximum value ( $V_{OL}$  max) or a minimum value ( $V_{OL}$  min). This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The test instrument shall be capable of loading the output of the circuit under test with the specified positive or negative currents ( $I_{OL}$ ). Resistors may be used to simulate the applicable current levels. The test instrument shall be capable of supplying the worst case power supply and input voltages. The test chamber shall be capable of maintaining the device under test at any specified temperature.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Worst case power supply voltages and worst case input levels including guaranteed noise margins shall be applied to the test circuit to provide a LOW level output. Forcing current, equal to the circuit worst case LOW level fan out, shall be applied to the test circuit output and the resultant output voltage measured. The output measurement shall be made after each input is conditioned.

- 4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Current to be forced into or from the output terminal.

- c. Power supply voltage(s).

- d. Input levels.

- e. VoL max or VoL min limits.

MIL-STD-883-3

This page intentionally left blank

#### METHOD 3008.1

#### BREAKDOWN VOLTAGE, INPUT OR OUTPUT

1. <u>PURPOSE</u>. This method establishes the means for assuring device performance to the limits specified in the applicable acquisition document in regard to input and output breakdown voltage symbolized as  $V_{IH}$  (max),  $V_{OH}$  (max),  $V_{IL}$  (min), and  $V_{OL}$  (min) as applicable. This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The test chamber shall be capable of maintaining the device under test at any specified temperature.

2.1 <u>Method A</u>. This test is generally performed to assure that breakdown does not occur on a device. An instrument shall be provided that has the capability of forcing a specified voltage at the input or output terminal of the test circuit and measuring the resultant current flowing in that terminal. The test instrument shall also have the capability of applying voltage levels to all other terminals. Care should be taken to assure that the test equipment does not inadvertently apply voltage to the device under test that will exceed the maximum rating of each terminal and that the current from the test equipment is sufficiently limited so that the device is not destroyed. This method can also be used to test the ability of power supply terminals to withstand a voltage overload.

2.2 <u>Method B</u>. This test is generally performed to assure that breakdown does occur on a device as specified in the applicable acquisition document. An instrument shall be provided that has the capability of forcing a specified current at the input or output terminal of the test circuit and measuring the resultant voltage at that terminal. The test instrument shall also have the capability of applying voltage levels to all other terminals. Care should be taken to assure that the test equipment does not inadvertently apply voltage to the device under test that will exceed the maximum rating of each terminal so that the device is not destroyed. The minimum compliance voltage of the current source shall be specified when applicable.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature.

3.1 <u>Method A</u>. All terminals, with the exception of the test terminal, shall be conditioned according to the applicable acquisition document. A prescribed voltage shall be applied to the designated input or output terminal and the resultant current measured. When testing for breakdown, all input and output terminals shall be tested individually. At the conclusion of the test, the device shall be functional.

3.2 <u>Method B</u>. All terminals, with the exception of the test terminal, shall be conditioned according to the applicable acquisition document. The specified current shall be forced at the designated input or output terminal, and the voltage at the terminal measured. At the conclusion of the test, the device shall be functional.

- 4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Forced voltages (method A).

- c. Conditioning voltages for all other terminals.

- d. Forced current (method B).

- e. Maximum breakdown current limits (method A).

- f. Minimum breakdown terminal voltage (method B).

MIL-STD-883-3

This page intentionally left blank

#### METHOD 3009.1

#### INPUT CURRENT, LOW LEVEL

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document in regard to LOW level input load which may be specified as a minimum value ( $I_{L}$  min) or as a maximum value ( $I_{L}$  max). This method applied to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The test chamber shall be capable of maintaining the device under test at any specified test temperature. An instrument shall be provided that has the capability of applying the worst case LOW voltage to the input terminal of the test circuit, (and worst case levels on the other inputs), and measuring the resultant current at the input terminal.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Worst case power supply voltages and worst case input voltages shall be applied to the test circuit and the resultant current at the input terminal shall be measured. Inputs shall be tested individually.

4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Power supply voltages.

- c. Input voltage.

- d. Voltages at other input terminals which cause worst case current at the input under test.

- e.  $I_{IL}$  max or  $I_{IL}$  min.

MIL-STD-883-3

This page intentionally left blank

#### METHOD 3010.1

#### INPUT CURRENT, HIGH LEVEL

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document in regard to HIGH level input load which may be specified as a maximum value ( $I_{IH}$  max) or a minimum value ( $I_{IH}$  min). This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The test chamber shall be capable of maintaining the device under test at any specified temperature. An instrument shall be provided that has the capability of applying the worst case HIGH voltage to the input terminal of the test circuit, and worst case levels at the other inputs, and measuring the resultant current at the input terminal.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Worst case power supply voltages and worst case input voltages shall be applied to the test circuit and the resultant current at the input terminal shall be measured. Inputs shall be tested individually.

4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Power supply voltages.

- c. Input voltage.

- d. Input voltages at other input terminals which cause worst case current at the input under text.

- e. I<sub>IH</sub> max.

MIL-STD-883-3

This page intentionally left blank

## METHOD 3011.1

## OUTPUT SHORT CIRCUIT CURRENT

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document in regard to output short circuit current (I<sub>OS</sub>). This method applied to digital microelectronic devices, such as TTL, DTL, RTL, and MOS.

2. <u>APPARATUS</u>. A test chamber capable of maintaining the device under test at any specified temperature. An instrument will be provided that has the capability of forcing a voltage specified in the applicable acquisition document at the output terminal of the device under test and measuring the resultant current flowing in that terminal. The test instrument shall also have the capability of applying specified voltage levels to all other inputs.

3. <u>PROCEDURE</u>. The device shall be stabilized at the specified test temperature. Each output per package shall be tested individually.

3.1 <u>TTL, DTL, RTL, MOS (P-Channel and N-Channel)</u>. Inputs of the device under test shall be conditioned in such a way as to provide a HIGH level at the output for TTL, DTL, RTL, and MOS (N-Channel) and a LOW level at the output for MOS (P-Channel). The output terminal shall be forced to 0 volt potential and the resultant current flow measured.

3.2 <u>C-MOS IOSH</u>. Inputs of the device under test shall be conditioned in such a way as to provide a HIGH level at the output. The output terminal shall be forced to 0 volt potential and the resultant current flow measured.

3.3 <u>C-MOS lost</u>. Inputs of the device under test shall be conditioned in such a way as to provide a LOW level at the output. The output terminal shall be forced to a voltage potential specified in the acquisition document and the resultant current flow measured.

4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Test temperature.

- b. Input conditioning voltages.

- c. Power supply voltages.

- d. los max and los min limits.

Downloaded from http://www.everyspec.com

MIL-STD-883-3

This page intentionally left blank

METHOD 3011.1 15 November 1974

## METHOD 3012.1

## TERMINAL CAPACITANCE

1. <u>PURPOSE</u>. This method establishes the means for assuring circuit performance to the limits specified in the applicable acquisition document in regard to terminal capacitance. This method applies to digital microelectronic devices, such as TTL, DTL, RTL, ECL, and MOS.

2. <u>APPARATUS</u>. The instrument shall be capable of applying a 1 MHz controllable amplitude signal superimposed on a variable plus or minus dc voltage. The instrument will also have the capability of measuring the capacitance of this terminal to within the limits and tolerance specified in the applicable acquisition document.

3. <u>PROCEDURE</u>. This test may be performed at  $25^{\circ}C \pm 3^{\circ}C$ . The capacitance measuring bridge shall be connected between the input or output terminal and the ground terminal of the test circuit. The bridge shall be adjusted for a signal of 1 MHz, riding a bias level specified in the applicable acquisition document; the signal amplitude shall not exceed 50 mV rms. With no device in the test socket the bridge shall then be zeroed. For capacitance values below 20 pF, the device shall be connected directly to the bridge with leads as short as possible to avoid the effects of lead inductance. After inserting the device under test and applying the specified bias conditions, the terminal capacitance shall be measured and compared to the limits listed in the applicable acquisition document.

4. <u>SUMMARY</u>. The following details shall be specified in the applicable acquisition document:

- a. Circuit bias conditions.

- b. Bias level at which measurements are to be made.

- c. Maximum capacitance limits.

Downloaded from http://www.everyspec.com

MIL-STD-883-3

This page intentionally left blank

METHOD 3012.1 15 November 1974

## METHOD 3013.2

## NOISE MARGIN MEASUREMENTS FOR DIGITAL MICROELECTRONIC DEVICES

1. <u>PURPOSE</u>. This method establishes the means of measuring the dc (steady- state) and ac (transient) noise margin of digital microelectronic devices or to determine compliance with specified noise margin requirements in the applicable acquisition document. It is also intended to provide assurance of interchangeability of devices and to eliminate misunderstanding between manufacturers and users on noise margin test procedures and results. The standardization of particular combinations of test parameters (e.g., pulse width, pulse amplitude, etc.) does not preclude the characterization of devices under test with other variations in these parameters. However, such variations shall, where applicable, be provided as additional conditions of test and shall not serve as a substitute for the requirements established herein.

- 1.1 Definitions. The following definitions shall apply for the purposes of this test method:

- a. Noise margin. Noise margin is defined as the voltage amplitude of extraneous signal which can be algebraically added to the noise-free worst case "input" level before the output voltage deviates from the allowable logic voltage levels. The term "input" (in quotation marks) is used here to refer to logic input terminals or ground reference terminals.

- b. DC noise margin. DC noise margin is defined as the dc voltage amplitude which can be algebraically added to the noise-free worst case "input" level before the output exceeds the allowable logic voltage levels.

- c. AC noise margin. AC noise margin is defined as the transient or pulse voltage amplitude which can be algebraically added to the noise-free worst case "input" level before the output voltage exceeds the allowable logic voltage levels.

- d. Maximum and minimum. Maximum and minimum refer to an algebraic system where "max" represents the most positive value of the range and "min" represents the least positive value of the range.

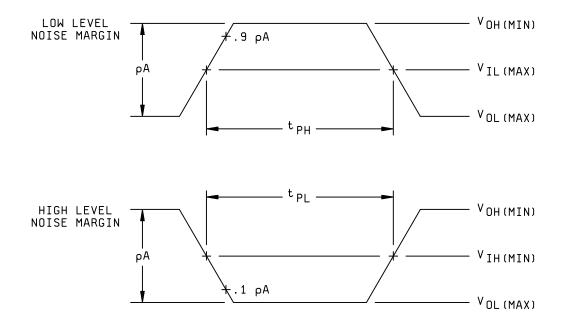

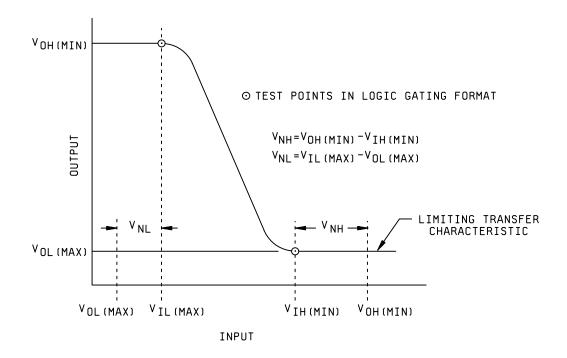

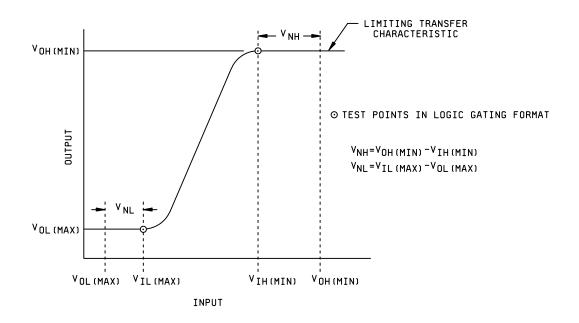

1.2 <u>Symbols</u>. The following symbols shall apply for the purposes of this test method and shall be used in accordance with the definitions provided (see 1.2.1, 1.2.2, and 1.2.3) and depicted on figures 3013-1, 3013-2, and 3013-3.

#### 1.2.1 Logic levels.

VIL max: The maximum allowed input LOW level in a logic system.

- V<sub>IL</sub> min: The minimum allowed input LOW level in a logic system.

- VIH max: The maximum allowed input HIGH level in a logic system.

- VIH min: The minimum allowed input HIGH level in a logic system.

- $V_{OL}$  max: The maximum output LOW level specified for a digital microelectronic device.  $V_{OL}$  max is also the noise-free worst case input LOW level,  $V_{OL}$  (max)  $\leq V_{IL}$  (max)

- $V_{OH}$  min: The minimum output HIGH level specified for a digital microelectronic device.  $V_{OH}$  min is also the noise-free worst case input HIGH level,  $V_{OH}$  (min)  $\geq V_{IH}$  (min)

#### 1.2.2 Noise margin levels.

- V<sub>NL</sub>: The LOW level noise margin or input voltage amplitude which can be algebraically added to V<sub>OL</sub> (max) before the output level exceeds the allowed logic level.

- V<sub>NH</sub>: The HIGH level noise margin or input voltage amplitude which can be algebraically added to V<sub>OH</sub> (min) before the output level exceeds the allowed logic level.

- V<sub>NG+</sub>: The positive voltage which can be algebraically added to the ground level before the output exceeds the allowed logic level determined by worst case logic input levels.

- V<sub>NG</sub>.: The negative voltage which can be algebraically added to the ground level before the output exceeds the allowed logic level determined by worst case logic input levels.

- V<sub>NP+</sub>: The positive voltage which can be algebraically added to the noise-free worst case most positive power supply voltage before the output exceeds the allowed logic level determined by worst case logic input levels.

- V<sub>NP-</sub>: The negative voltage which can be algebraically added to the noise-free worst case most negative (least positive) power supply voltage before the output exceeds the allowed logic level determined by worst case logic input levels.

1.2.3 Noise pulse widths.

- $t_{PL}$ : The LOW level noise pulse width, measured at the V<sub>IL</sub> (max) level.

- t<sub>PH</sub>: The HIGH level noise pulse width, measured at the V<sub>IH</sub> (min) level.

2. <u>APPARATUS</u>. The apparatus used for noise margin measurements shall include a suitable source generator (see 2.1), load (see 2.2), and voltage detection devices for determining logic state.

2.1 <u>Source generator</u>. The source generator for this test shall be capable of supplying the required ac and dc noise inputs. In the case of pulsed inputs the transition times of the injected noise pulse shall each be maintained to less than 20 percent of the pulse width measured at the 50 percent amplitude level. For the purpose of this criteria, the transition times shall be between the 10 percent and 90 percent amplitude levels. The pulse repetition rate shall be sufficiently low that the element under test is at steady-state conditions prior to application of the noise pulse. For the purpose of this criteria, doubling the repetition rate or duty cycle shall not affect the outcome of the measurement.

2.2 Load. The load for this test shall simulate the circuit parameters of the normal load which would be applied in application of the device under worst-case conditions. The load shall automatically change its electrical parameters as the device under test changes logic state if this is the normal situation for the particular device load. The load shall be paralleled by a high impedance voltage detection device.

3. <u>PROCEDURE</u>. The device shall be connected for operation using a source generator and load as specified (see 2), and measurements shall be made of  $V_{NL}$ ,  $V_{NH}$ ,  $V_{NG}$ ,  $V_{NP}$ ,  $t_{PL}$ , and  $t_{PH}$  following the procedures for both ac noise margin and dc noise margin (see 3.2 through 3.3.3).

#### 3.1 General considerations.

3.1.1 <u>Nonpropagation of injected noise</u>. As defined in 1.1, noise margin is the amplitude of extraneous signal which may be added to a noise-free worst case "input" level before the output breaks the allowable logic levels. This definition of noise margin allows the measurement of both dc and ac noise immunity on logic inputs or power supply lines or ground reference lines by detection of either a maximum LOW level or a minimum HIGH level at the output terminal. Since the output level never exceeds the allowable logic level under conditions of injected noise, the noise is not considered to propagate through the element under test.

3.1.2 <u>Superposition of simultaneously injected noise</u>. Because the logic levels are restored after one stage, and because the noise margin measurement is performed with all "inactive" inputs at the worst case logic levels, the proper system logic levels are guaranteed in the presence of simultaneous disturbances separated by at least one stage.

3.1.3 <u>Characterization of ac noise margin</u>. Although the purpose of this standard test procedure is to insure interchangeability of elements by a single- point measurement of ac noise margin, the test procedure is well suited to the measurement of ac noise margin as a function of noise pulse width. In particular, for very wide pulse widths, the ac noise margin asymptotes to a value identically equal to the dc noise margin.

## 3.2 Test procedure for dc noise margin.

3.2.1 <u>Worse case configuration</u>. The measurement of dc noise margin using a particular logic input terminal should correspond to the worst case test configuration in the applicable acquisition document. For example, the measurement of LOW level noise margin for a positive-logic inverting NAND gate should be performed under the same worst case test conditions as the dc measurement of V<sub>OH</sub> (min). If the worst case dc test conditions for V<sub>OH</sub> (min) are high power supply voltage, all unused logic inputs connected to V<sub>OH</sub> (min) and output current equal to zero, these conditions should be applied to the corresponding dc noise margin measurement.

3.2.2 LOW level noise margin,  $V_{NL}$ . The LOW level noise margin test is normally performed during the  $V_{OH}$  test for inverting logic and during the  $V_{OL}$  test for noninverting logic. The noise margin is calculated from the following expression:

$$V_{NL} = V_{IL} (max) - V_{OL} (max)$$

3.2.3 <u>HIGH level noise margin</u>,  $V_{\text{NH}}$ . The HIGH level noise margin test is performed during the V<sub>OL</sub> test for inverting logic and during the V<sub>OH</sub> test for noninverting logic. The noise margin is calculated from the following expression:

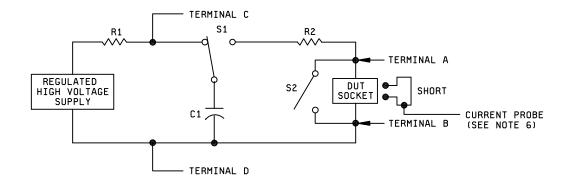

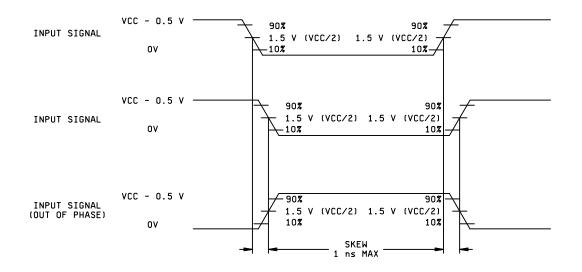

$$V_{NH} = V_{OH} (min) - V_{IH} (min)$$