NOTICE OF CHANGE

MIL-STD-750D NOTICE 3 29 February 2000

FSC 5961

The documentation and process conversion measures necessary to comply with this Notice shall be completed by 29 August 2000.

# DEPARTMENT OF DEFENSE

#### TEST METHOD STANDARD FOR SEMICONDUCTOR DEVICES

TO ALL HOLDERS OF MIL-STD-750D:

1. THE FOLLOWING PAGES OF MIL-STD-750D HAVE BEEN REVISED AND SUPERSEDE THE PAGES LISTED:

| METHOD | NEW PAGE | DATE             | SUPERSEDED PAGE | DATE                     |

|--------|----------|------------------|-----------------|--------------------------|

|        | 5        | 28 February 2000 | 5               | Reprinted Without Change |

|        | 6        | 29 February 2000 | 6               | 28 February 1995         |

|        | 15       | 29 February 2000 | 15              | 23 February 1996         |

|        | 16       | 29 February 2000 | 16              | 23 February 1996         |

|        | 17       | 29 February 2000 | 17              | Reprinted Without Change |

|        | 18       | 29 February 2000 | 18              | 23 February 1996         |

|        | 19/20    | 29 February 2000 | 19/20           | 23 February 1996         |

2. THE FOLLOWING TEST METHODS OF MIL-STD-750D HAVE BEEN REVISED AND SUPERSEDE THE TEST METHOD LISTED:

| METHOD  | DATE             | SUPERSEDED METHOD | DATE             |

|---------|------------------|-------------------|------------------|

| 2037.1  | 29 February 2000 | 2037              | 28 February 1995 |

| 2052.3  | 29 February 2000 | 2052.2            | 28 February 1995 |

| 2070.2  | 29 February 2000 | 2070.1            | 28 February 1995 |

| 2075. 1 | 29 February 2000 | 2075              | 28 February 1995 |

| 3101.3  | 29 February 2000 | 3101.2            | 28 February 1995 |

| 4016.4  | 29 February 2000 | 4016.3            | 28 February 1995 |

| 5001.2  | 29 February 2000 | 5001.1            | 28 February 1995 |

|         |                  |                   |                  |

3. THE FOLLOWING NEW METHODS HAVE BEEN ADDED:

| METHOD | TITLE                                            | DATE             |

|--------|--------------------------------------------------|------------------|

| 1080   | Single Event Gate Rupture and Drain Burnout Test | 29 February 2000 |

| 2102   | DPA for Wire Bonded Devices                      | 29 February 2000 |

4. RETAIN THIS NOTICE AND INSERT BEFORE TABLE OF CONTENTS.

5. Holders of MIL-STD-750D will verify that page changes and additions indicated above have been entered. This notice page will be retained as a check sheet. This issuance, together with appended pages, is a separate publication. Each notice is to be retained by stocking points until the military standard is completely revised or canceled.

Custodians:

Army - CR Navy - EC Air Force - 11 NASA – NA DLA-CC

Review activities:

Army - AR, MI Navy - AS, CG, MC, SH Air Force – 19, 99 Preparing activity: DLA - CC

(Project 5961-1881)

# 4. GENERAL REQUIREMENTS

- 4.1 <u>Test conditions</u>. Unless otherwise specified herein or in the individual specification, all measurements and tests shall be made at thermal equilibrium at an ambient temperature of  $25^{\circ}\text{C} \pm 3^{\circ}\text{C}$ , and at ambient atmospheric pressure and relative humidity and the specified test condition C (at environmentally elevated and reduced temperatures) shall have a tolerance of  $\pm 3$  percent or  $3^{\circ}\text{C}$ , whichever is greater. Whenever these conditions must be closely controlled in order to obtain reproducible results, the referee conditions shall be as follows: temperature  $25^{\circ}\text{C}\pm 1^{\circ}\text{C}$ , relative humidity  $50\pm 5$  percent, and atmospheric pressure from 650 to 800 millimeters of mercury. For mechanical test methods, 2000 series, the ambient temperature may be  $25^{\circ}\text{C}\pm 10^{\circ}\text{C}$ , unless otherwise specified in the detail test method.

- 4.1.1 <u>Permissible temperature variation in environmental chambers</u>. When chambers are used, specimens under test shall be located only within the working area defined as follows:

- a. Temperature variation within working area: The controls for the chamber shall be capable of maintaining the temperature of any single reference point within the working area within ±2°C or ±4 percent, whichever is greater.

- b. Space variation within working area: Chambers shall be so constructed that, at any given time, the temperature of any point within the working area shall not deviate more than  $\pm 3^{\circ}$ C or  $\pm 3$  percent, whichever is greater, from the reference point, except for the immediate vicinity of specimens generating heat.

- c. Chambers with specified minimum temperatures (such as those used in burn-in and life tests): When test requirements involve a specified minimum test temperature, the controls and chamber construction shall be such that the temperature of any point within the working area shall not deviate more than +8°C, -0°C; or +8 percent, -0 percent, whichever is greater, from the specified minimum temperature, except for the immediate vicinity of the specimens generating heat.

- 4.1.2 Electrical test frequency. Unless otherwise specified, the electrical test frequency shall be 1,000 ±25 Hertz (Hz).

- 4.1.3 Accuracy. The specified limits are for absolute (true) values, obtained with the specified (nominal) test conditions. Proper allowance shall be made for measurement errors (including those due to deviations from nominal test conditions) in establishing the working limits to be used for the measured values, so that the true values of the device parameters (as they would be under nominal test conditions) are within the specified limits.

The following electrical test tolerances and precautions, unless otherwise specified in the applicable acquisition document, shall be maintained for all device measurements to which they apply (3000, 4000 series and other specified electrical measurements). Wherever test conditions are specified in the applicable acquisition document to a precision tighter than the tolerances indicated below, the specified conditions shall apply and take precedence over these general requirements.

- a. Bias conditions shall be held to within 3 percent of the specified value.

- b. Such properties as input pulse characteristics, repetition rates, and frequencies shall be held to within 10 percent. Nominal values should be chosen so that ±10 percent variation (or the actual test equipment variation, if less than 10 percent) does not affect the accuracy or validity of the measurement of the specified value.

- c. Voltages applied in breakdown testing shall be held within 1 percent of specified value.

- d. Resistive loads shall be ±5 percent tolerance.

- e. Capacitive loads shall be \$10 percent or \$1 picofarad (pF) tolerance, whichever is greater.

- f. Inductive loads shall be \$10 percent or \$5 microhenries (mH) tolerance, whichever is greater.

- g. Static parameters shall be measured to within 1 percent.

- h. Switching parameters shall be measured to within 5 percent or 1 nanosecond (ns), whichever is greater.

- 4.1.3.1 <u>Test methods and circuits</u>. Unless otherwise stated in the specific test method, the methods and circuits shown are given as the basic measurement method. They are not necessarily the only method or circuit which can be used, but the manufacturer shall demonstrate to the acquiring activity that alternate methods or circuits which he may desire to use are equivalent and give results within the desired accuracy of measurement (see 4.1.3).

- \* 4.1.4 <u>Calibration requirements</u>. Calibration and certification procedures shall be provided in accordance with ANSI/NCSL-Z540-1-1994 for plant standards and instruments used to measure or control production processes and semiconductor devices under test. For those measurements that are not traceable to the National Institute of Standards and Technology (NIST), correlation samples shall be maintained and used as the basis of proving acceptability when such proof is required. In addition, the following requirements shall apply:

- a. The accuracy of a calibrating instrument shall be at least four times greater than that of the item being calibrated, unless the item being calibrated is state of the art equipment, which may be near or equal in accuracy to the state of the art calibrating equipment, in which case the four time requirement does not apply. However, the instrument shall be calibrated to correlate with standards established by the NIST.

- b. Except in those cases where the NIST recommends a longer period and concurrence is obtained from the qualifying activity, calibration intervals for plant electrical standards shall not exceed one year, and for plant mechanical standards shall not exceed two years.

#### 4.2 Orientations:

X is the orientation of a device with the main axis of the device normal to the direction of the accelerating force, and the major cross section parallel to the direction of the accelerating force.

Y is the orientation of a device with the main axis of the device parallel to the direction of the accelerating force, and the principal base toward (Y<sub>1</sub>), or away from (Y<sub>2</sub>), the point of application of the accelerating force.

Z is the orientation of a device with the main axis and the major cross section of the device normal to the direction of the accelerating force. Z is 90° of X.

NOTE: For case configurations, other than those shown on figures 1 and 2, the orientation of the device shall be as specified in the individual specification.

# Numerical index of test methods

Method no. Title

# Environmental tests (1000 series).

| 1001.2         | Barometric pressure (reduced).                                                                  |

|----------------|-------------------------------------------------------------------------------------------------|

| 1011.1         | Immersion.                                                                                      |

| 1015.1         | Steady-state primary photocurrent irradiation procedure (electron beam).                        |

| 1016           | Insulation resistance.                                                                          |

| 1017.1         | Neutron irradiation.                                                                            |

| 1018           | Internal water-vapor content.                                                                   |

| 1019.4         | Steady-state total dose irradiation procedure.                                                  |

| 1020.2         | Electrostatic discharge sensitivity (ESDS) classification.                                      |

| 1021.3         | Moisture resistance.                                                                            |

| 1022.5         | Resistance to solvents.                                                                         |

| 1026.5         | Steady-state operation life.                                                                    |

| 1027.3         | Steady-state operation life (sample plan).                                                      |

| 1031.5         | High-temperature life (nonoperating).                                                           |

| 1032.2         | High-temperature (nonoperating) life (sample plan).                                             |

| 1036.3         | Intermittent operation life.                                                                    |

| 1037.2         | Intermittent operation life (sample plan).                                                      |

| 1038.4         | Burn-in (for diodes, rectifiers, and zeners).                                                   |

| 1039.4         | Burn-in (for transistors).                                                                      |

| 1040           | Burn-in (for thyristors (controlled rectifiers)).                                               |

| 1041.3         | Salt atmosphere (corrosion).                                                                    |

| 1042.3         | Burn-in and life test for power MOSFET's or insulated gate bipolar transistors (IGBT).          |

| 1046.3         | Salt spray (corrosion).                                                                         |

| 1048           | Blocking life.                                                                                  |

| 1049           | Blocking life (sample plan).                                                                    |

| 1051.5         | Temperature cycling (air to air).                                                               |

| 1054.1         | Potted environment stress test.                                                                 |

| 1055.1         | Monitored mission temperature cycle.                                                            |

| 1056.7         | Thermal shock (liquid to liquid).                                                               |

| 1061.1         | Temperature measurement, case and stud.                                                         |

| 1066.1         | Dew point.                                                                                      |

| 1071.6         | Hermetic seal                                                                                   |

| * 1080         | Single Event Gate Rupture and Drain Burnout Test                                                |

|                |                                                                                                 |

|                | Mechanical characteristics tests (2000 series).                                                 |

| 2005.2         | Axial lead tensile test.                                                                        |

| 2006           | Constant acceleration.                                                                          |

| 2016.2         | Shock.                                                                                          |

| 2017.2         | Die attach integrity.                                                                           |

| 2026.10        | Solderability.                                                                                  |

| 2031.2         | Soldering heat.                                                                                 |

| 2036.4         | Terminal strength.                                                                              |

| * 2037.1       | Bond strength.                                                                                  |

| 2046.1         | Vibration fatigue.                                                                              |

| 2051.1         | Vibration noise.                                                                                |

| * 2052.3       | Particle impact noise detection (PIND) test.                                                    |

| 2056           | Vibration, variable frequency.                                                                  |

| 2057.1         | Vibration, variable frequency (monitored).                                                      |

| 2066           | Physical dimensions.                                                                            |

| 2068           | External visual for nontransparent, glass-encased, double plug, noncavity, axial leaded diodes. |

| 2069.1         | Pre-cap visual, power MOSFET's.                                                                 |

| * 2070.2       | Pre-cap visual microwave discrete and multichip transistors.                                    |

| 2071.3         | Visual and mechanical examination.                                                              |

| 2072.6         | Internal visual transistor (pre-cap) inspection.                                                |

| 2073<br>2074.4 | Visual inspection for die (semiconductor diode).                                                |

| 2074.4         | Internal visual inspection (discrete semiconductor diodes).                                     |

|                |                                                                                                 |

Supersedes page 15 of MIL-STD-750, Notice 2, dated 23 February, 1996

# Numerical index of test methods

|                | numerical index of test methods                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------|

| Method no.     | Title                                                                                                        |

|                |                                                                                                              |

|                | Mechanical characteristics tests (2000 series) - Continued.                                                  |

| * 2075.1       | Decap internal visual design verification.                                                                   |

| 2076.3         | Radiography.                                                                                                 |

| 2077.3         | Scanning electron microscope (SEM) inspection of metallization.                                              |

| 2081           | Forward instability, shock (FIST).                                                                           |

| 2082           | Backward instability, vibration (BIST).                                                                      |

| 2101.1         | DPA procedures for diodes.                                                                                   |

| * 2102         | DPA for wire bonded devices                                                                                  |

|                | Electrical characteristics tests for bipolar transistors (3000 series).                                      |

| 3001.1         | Breakdown voltage, collector to base.                                                                        |

| 3005.1         | Burnout by pulsing.                                                                                          |

| 3011.2         | Breakdown voltage, collector to emitter.                                                                     |

| 3015           | Drift.                                                                                                       |

| 3020           | Floating potential.                                                                                          |

| 3026.1         | Breakdown voltage, emitter to base.                                                                          |

| 3030           | Collector to emitter voltage.                                                                                |

| 3036.1         | Collector to base cutoff current.                                                                            |

| 3041.1<br>3051 | Collector to emitter cutoff current.                                                                         |

| 3052           | Safe operating area (continuous dc). Safe operating area (pulsed).                                           |

| 3053           | Safe operating area (pulsed). Safe operating area (switching).                                               |

| 3061.1         | Emitter to base cutoff current.                                                                              |

| 3066.1         | Base emitter voltage (saturated or nonsaturated).                                                            |

| 3071           | Saturation voltage and resistance.                                                                           |

| 3076.1         | Forward-current transfer ratio.                                                                              |

| 3086.1         | Static input resistance.                                                                                     |

| 3092.1         | Static transconductance.                                                                                     |

|                | Circuit-performance and thermal resistance measurements (3100 series).                                       |

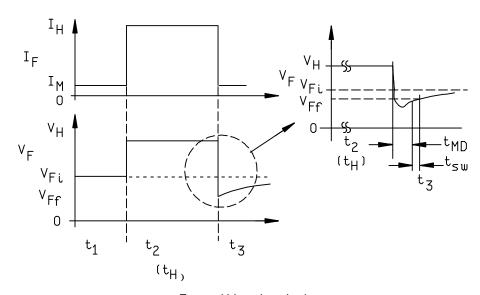

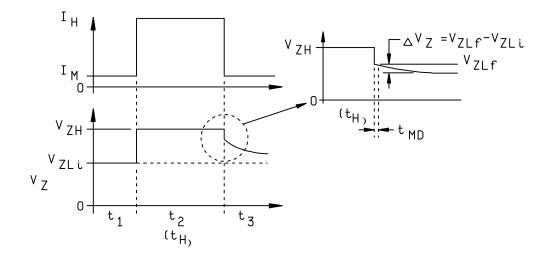

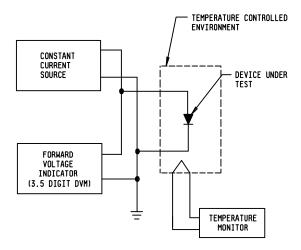

| * 3101.3       | Thermal impedance testing of diodes.                                                                         |

| 3103           | Thermal impedance measurements for insulated gate bipolar transistor (delta gate-emitter on voltage method). |

| 3104           | Thermal impedance measurements of GaAs MOSFET's (constant current forward-biased gate voltage method).       |

| 3105.1         | Measurement method for thermal resistance of a bridge rectifier assembly.                                    |

| 3126           | Thermal resistance (collector-cutoff-current method).                                                        |

| 3131.2         | Thermal impedance measurements for bipolar transistors (delta base-emitter voltage method).                  |

| 3132           | Thermal resistance (dc forward voltage drop, emitter base, continuous method).                               |

| 3136           | Thermal resistance (forward voltage drop, collector to base, diode method).                                  |

| 3141<br>3146.1 | Thermal response time. Thermal time constant.                                                                |

| 3151           | Thermal resistance, general.                                                                                 |

| 3161           | Thermal impedance measurements for vertical power MOSFET's (delta source-drain voltage method).              |

| 3181           | Thermal resistance for thyristors.                                                                           |

|                | Low frequency tests (3200 series).                                                                           |

| 3201.1         | Small-signal short-circuit input impedance.                                                                  |

| 3206.1         | Small-signal short-circuit forward-current transfer ratio.                                                   |

| 3211           | Small-signal open-circuit reverse-voltage transfer ratio.                                                    |

| 3216           | Small-signal open-circuit output admittance.                                                                 |

| 3221           | Small-signal short-circuit input admittance.                                                                 |

| 3231           | Small-signal short-circuit output admittance.                                                                |

| 3236           | Open circuit output capacitance.                                                                             |

Supersedes page 16 of MIL-STD-750, Notice 2, dated 23 February, 1996.

# Numerical index of test methods - Continued.

| Method no.                         | Title                                                                                                                                                                   |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3240.1<br>3241<br>3246.1<br>3251.1 | Input capacitance (output open-circuited or short-circuited). Direct interterminal capacitance. Noise figure. Pulse response.                                           |

| 3255                               | Large signal power gain.                                                                                                                                                |

| 3256<br>3261.1                     | Small signal power gain. Extrapolated unity gain frequency.                                                                                                             |

| 3266                               | Real part of small-signal short circuit input impedance.                                                                                                                |

|                                    | High frequency tests (3300 series)                                                                                                                                      |

| 3301                               | Small-signal short-circuit forward-current transfer-ratio cutoff frequency.                                                                                             |

| 3306.3<br>3311                     | Small-signal short-circuit forward-current transfer ratio.  Maximum frequency of oscillation.                                                                           |

| 3320                               | RF power output, RF power gain, and collector efficiency.                                                                                                               |

|                                    |                                                                                                                                                                         |

|                                    | Electrical characteristics tests for MOS field-effect transistors (3400 series)                                                                                         |

| 3401.1                             | Breakdown voltage, gate to source.                                                                                                                                      |

| 3403.1                             | Gate to source voltage or current.                                                                                                                                      |

| 3404<br>3405.1                     | MOSFET threshold voltage.  Drain to source on-state voltage.                                                                                                            |

| 3407.1                             | Breakdown voltage, drain to source.                                                                                                                                     |

| 3411.1                             | Gate reverse current.                                                                                                                                                   |

| 3413.1                             | Drain current.                                                                                                                                                          |

| 3415.1                             | Drain reverse current.                                                                                                                                                  |

| 3421.1                             | Static drain to source on-state resistance.                                                                                                                             |

| 3423                               | Small-signal, drain to source on state resistance.                                                                                                                      |

| 3431                               | Small-signal, common-source, short-circuit, input capacitance.                                                                                                          |

| 3433                               | Small-signal, common-source, short-circuit, reverse-transfer capacitance.                                                                                               |

| 3453<br>3455                       | Small-signal, common-source, short-circuit, output admittance.  Small-signal, common-source, short-circuit, forward transadmittance.                                    |

| 3457                               | Small-signal, common-source, short-circuit, forward transactification.  Small-signal, common-source, short-circuit, reverse transfer admittance.                        |

| 3459                               | Pulse response (FET).                                                                                                                                                   |

| 3461                               | Small-signal, common-source, short-circuit, input admittance.                                                                                                           |

| 3469                               | Repetitive unclamped inductive switching.                                                                                                                               |

| 3470.2                             | Single pulse unclamped inductive switching.                                                                                                                             |

| 3471.1                             | Gate charge.                                                                                                                                                            |

| 3472.2                             | Switching time test.                                                                                                                                                    |

| 3473.1                             | Reverse recovery time (t <sub>ff</sub> ) and recovered charge (Q <sub>ff</sub> ) for power MOSFET (drain-to-source) and                                                 |

|                                    | power rectifiers with t <sub>rr</sub> & 100 ns.                                                                                                                         |

| 3474.1                             | Safe operating area for power MOSFET's or insulated gate bipolar transistors.                                                                                           |

| 3475.1                             | Forward transconductance (pulsed dc method) of power MOSFET's or insulated gate bipolar transistors.                                                                    |

| 3476                               | Commutating diode for safe operating area test procedure for measuring dv/dt during reverse recovery of power MOSFET transistors or insulated gate bipolar transistors. |

| 3477.1                             | Measurement of insulated gate bipolar transistor total switching losses and switching times.                                                                            |

| 3478.1                             | Power transistor electrical dose rate test method.                                                                                                                      |

| 3479                               | Short circuit withstand time.                                                                                                                                           |

| 3490                               | Clamped inductive switching safe operating area for MOS gated power transistors.                                                                                        |

# Numerical index of test methods - Continued.

| Electrical characteristics tests for Gallium Arsenide transistors (3500 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Breakdown voltage, drain to source.  Maximum available gain of a GaAs FET.  1 dB compression point of a GaAs FET.  GaAs FET forward gain (Mag S21).  Forward transconductance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Electrical characteristics tests for diodes (4000 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Condition for measurement of diode static parameters. Capacitance. Forward voltage. Reverse current leakage. Breakdown voltage (diodes). Breakdown voltage (voltage regulators and voltage-reference diodes). Scope display. Forward recovery voltage and time. Reverse recovery characteristics. "Q" for voltage variable capacitance diodes. Rectification efficiency. Reverse current, average. Small-signal reverse breakdown impedance. Small-signal forward impedance. Stored charge. Surge current. Temperature coefficient of breakdown voltage. Saturation current. Thermal resistance of lead mounted diodes (forward voltage, switching method). |

| Electrical characteristics tests for microwave diodes (4100 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Conversion loss.  Microwave diode capacitance.  Detector power efficiency.  Figure of merit (current sensitivity).  IF impedance.  Output noise ratio.  Overall noise figure and noise figure of the IF amplifier.  Video resistance.  Standing wave ratio (SWR).  Burnout by repetitive pulsing.  Burnout by single pulse.  Rectified microwave diode current.                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Supersedes page 18 of MIL-STD-750, Notice 2, dated 23 February, 1996.

# Numerical index of test methods - Continued.

| Method no.                                     | Title                                                                                                                                                                   |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | Electrical characteristics tests for tunnel diodes (4300 series)                                                                                                        |

| 4301<br>4306.1<br>4316<br>4321<br>4326<br>4331 | Junction capacitance. Static characteristics of tunnel diodes. Series inductance. Negative resistance. Series resistance. Switching time.                               |

|                                                | High reliability space application tests (5000 series)                                                                                                                  |

| 5001.2<br>5002<br>5010                         | Wafer lot acceptance testing. Capacitance-voltage measurements to determine oxide quality. Clean room and workstation airborne particle classification and measurement. |

#### METHOD 1080

# SINGLE-EVENT BURNOUT AND SINGLE-EVENT GATE RUPTURE TEST METHOD

- 1. <u>Purpose</u>. The purpose of this test method is to describe the procedure for conducting heavy ion irradiation of power MOSFETs. This test method establishes a procedure for characterization and for verification (acceptance or qualification) of discrete power MOSFETs for single-event burnout (SEB) and single-event gate rupture (SEGR). In principle, this test method may be applicable to testing where neutrons, protons, or other light particles are used.

- 1.1 <u>Definitions</u>. The following symbols and terms shall apply for the purpose of this test method:

- a. Cross-sectional area: Calculated as the number of events per unit fluence.

- b. **DUT**: Device under test.

- c. Fluence: The ion flux integrated over the time required for the run, expressed as ions/cm<sup>2</sup>.

- d. Flux: The number of ions passing through a one cm<sup>2</sup> area perpendicular to the ion beam per unit of time, expressed as ions/cm<sup>2</sup>•s.

- e. <u>los</u>: The measured drain-to-source current (amps).

- f. <u>lss</u>: The measured gate-to-source current (amps).

- g. <u>Linear energy transfer (LET)</u>: The amount of energy transferred per unit length as the ion travels through a material, expressed as MeV/(mg/cm²) in this test method.

- h. <u>Single-event burnout (SEB)</u>: A single-ion-induced condition that causes a localized high-current state resulting in a catastrophic device failure characterized by an increase in drain current that exceeds the manufacturer's rated leakage current at the drain electrode.

- i. <u>Single-event gate rupture (SEGR)</u>: A single-ion-induced condition that causes a localized defect in the gate dielectric resulting in a catastrophic device failure, characterized by an increase in gate current that exceeds the manufacturer's rated leakage current at the gate electrode.

- j. SEB circumvention: A technique used to prevent the device from catastrophically failing during an SEB event.

- k. SEB cross-sectional area: Calculated as the number of SEB events per unit fluence.

- I. <u>SEGR cross-sectional area</u>: Calculated as the reciprocal of the fluence required to induce the SEGR event.

- m. <u>SEGR post gate-stress test</u>: After the heavy ion irradiation, a test is conducted to verify the gate integrity by applying the maximum specified V<sub>GS</sub>.

- n. Threshold LET: The minimum LET required to cause a single-ion-induced failure under the specified bias conditions.

- o.  $V_{DS}$ : The applied drain-to-source voltage (volts).

- p.  $V_{GS}$ : The applied gate-to-source voltage (volts).

- g.  $V_{\text{TH}}$ : The value of  $V_{\text{GS}}$  where the inversion layer is formed and the device turns on.

- 1.2 <u>Applicable documents</u>. The following documents form part of this test method. The most current revision of these documents shall take precedence over those cited.

- EIA/JESD57 Test Procedures for the Measurement of Single-Event Effects in Semiconductor Devices from Heavy Ion

1

ASTM F-1192 - Standard Guide for the Measurement of Single-Event Phenomena from Heavy Ion Irradiation of Semiconductor Devices.

1.3 <u>Device handling.</u> Special care shall be taken to ensure that the devices are not damaged before testing. Since the lids are removed before irradiation, extra precautions shall be taken to protect the exposed die. Otherwise, devices shall be handled in accordance with standard operating procedures to protect against damage and electrostatic discharge. Use of anti-static foams, grounding straps, and other precautions is recommended.

NOTE: Some power MOSFETs may require voltages that exceed 500 volts and voltages in excess of 32 volts can present a safety hazard. Safety precautions shall be taken to ensure safe operation of all equipment and personnel. Note that conformal coatings may interfere with the test, changing the penetration depth of the ion as well as degrading the ion energy. The effect of conformal coatings shall be evaluated. Conformal coatings, such as polyamide, should be chemically removed before testing.

- 2. <u>Apparatus</u>. The apparatus required for SEB/SEGR testing consists of a heavy ion source, a vacuum chamber system, DUT test instrumentation, test circuit board(s), cabling, switching system (if required), an x-y-z stage system (if required), and dosimetry measurement instrumentation. Precautions shall be taken to obtain an electrical measurement system with sufficient insulation, shielding, and grounding to measure a gate current, I<sub>SS</sub>, of 10 nA or less (measurement resolution).

- 2.1 <u>Heavy ion source</u>. The heavy ion source shall be a cyclotron, Van de Graaff accelerator, or other suitable source. The heavy ion source shall be capable of providing an average ion flux up to 100,000 ions/cm²•s. The average beam uniformity should be maintained within ±15 percent over the die area unless otherwise specified. The ion beam energy shall provide sufficient ion penetration depth to induce the SEGR response or as agreed to by both parties to the test. Note that the accelerator design determines the maximum ion beam energy; and, therefore, some accelerators may be inadequate to perform a worst-case test condition. Also, note that some accelerators are rf-type machines (e.g. cyclotrons) and may have higher instantaneous fluxes.

- 2.2 <u>Vacuum chamber system</u>. The chamber shall have a test circuit board mounting frame and cable feed-through. The vacuum chamber system should be capable of accepting an x-y-z stage mechanism. The pumping system shall be capable of evacuating the vacuum chamber below1.3 x 10<sup>-1</sup> Pa (10<sup>-3</sup> torr). Precautions shall be taken to ensure that any component placed in the vacuum chamber does not interfere with the vacuum system. Note that certain materials can out-gas, affecting the vacuum quality. Also note that some capacitors (e.g., electrolytic capacitors) can explode, fail, or out-gas when placed in a vacuum.

- 2.3 <u>Test instrumentation</u>. Standard electrical test instruments capable of establishing the required test conditions and measuring the required electrical parameters shall be used. Note that many power MOSFETs may require operating voltages in excess of 32 volts and safety precautions shall be followed to ensure safe operation of all equipment and personnel."

- 2.3.1 <u>SEB instrumentation.</u> Test instrumentation to bias and monitor the DUT may consist of one or more of the following types of instruments:

| inonio.          |  |  |

|------------------|--|--|

| a. Power supply. |  |  |

- b. Ammeter.

- c. Voltmeter.

- d. Counter.

- e. Oscilloscope.

- 2.3.2 <u>SEGR instrumentation</u>. Test instrumentation to bias and monitor the DUT may consist of one or more of the following types of instruments:

- a. Power supply.

- b. Ammeter.

- c. Voltmeter.

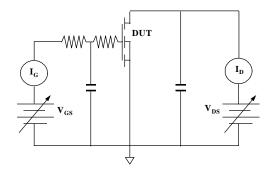

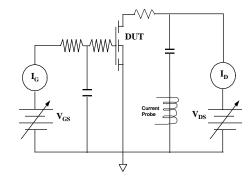

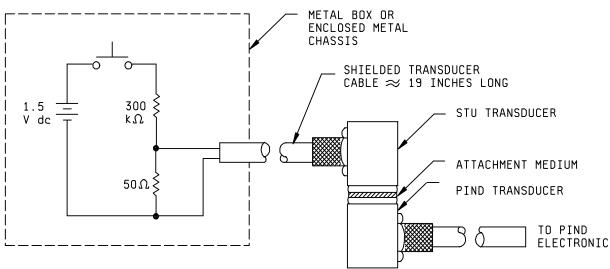

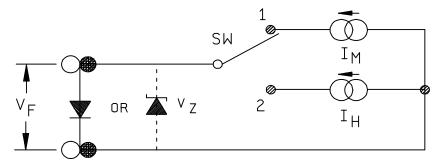

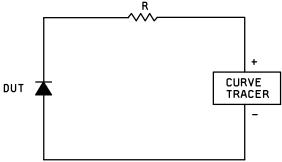

- 2.4 <u>Test circuit board</u>. The test circuit board contains the test socket, delidded DUT, any additional wiring, and any auxiliary components. The test board provides a mounting surface and interface between the test instrumentation and the DUT, applying  $V_{GS}$  and  $V_{DS}$ , while monitoring  $I_{GS}$  and  $I_{DS}$ . Figure 1 shows a representative test circuit and figure 2 shows a typical SEB circumvention and monitoring technique. Any auxiliary components, such as the resistors, capacitors, or current probes, shall be included in the final test circuit. Any accepted SEB circumvention and monitoring technique is acceptable. The test board can have multiple test sockets to minimize the time required to vent and evacuate the vacuum chamber. The test socket, in which the DUT is inserted, is mounted in such a way that the DUT surface shall be perpendicular (nominally within  $\pm 5^{\circ}$ C) to the heavy ion beam. The DUT is delidded prior to testing, and the entire die shall be irradiated.

FIGURE 1080-1. Basic SEB/SEGR test circuit.

FIGURE 1080-2. SEB circumvention and monitoring circuit.

- 2.5 <u>Cabling</u>. Cables are typically used to connect the test circuit board, located in the vacuum chamber, to the test instrumentation, normally placed outside the vacuum chamber. The cable length shall be minimized to prevent interference with the desired measurement. However, the actual cable length is dictated by the size of the vacuum chamber, the spatial location of the test board with respect to the cabling feed-throughs, and the minimum distance from the cabling feed-throughs to the DUT test instrumentation. Observation of SEB pulses shall be performed using properly terminated shielded cables to minimize reflections and other signal/noise interference.

- 2.6 <u>Switching system</u>. A switching system can be used when multiple devices are placed on the test board. The switching system shall provide electrical isolation between the gate and drain electrodes of the various test devices on the test board. Inclusion of a switching system shall not interfere with the electrical measurement system, as specified in 2.

- 2.7 <u>X-Y-Z stage system</u>. If multiple devices are placed on the test board, an x-y-z stage system can be used to provide a mechanical mechanism to move the device into and out of the heavy ion beam.

- 2.8 <u>Dosimetry system</u>. The dosimetry system shall be used to determine the ion beam energy, LET, average ion beam flux, fluence, and average ion beam uniformity. Note that many facilities provide this dosimetry system.

- 3. <u>SEB/SEGR prediction</u>. To assist in the preparation of the test plan and the selection of initial bias conditions, an appropriate SEB/SEGR prediction method may be utilized to predict the SEB/SEGR failure thresholds. The preferred prediction method is to use previous measurements on similar device types. Test personnel should use these predicted failure thresholds to help verify that the SEGR and SEB test measurements are valid. If a significant difference (nominally greater than a ±30 percent deviation from the predicted response) is observed, the test personnel should verify the test setup including the ion specie, ion energy, bias conditions, and device type. These predictions can help to develop the overall test plan.

- 3.1 <u>SEB prediction</u>. Currently, there are not any accurate prediction models available for SEB. Predictions based upon previously obtained SEB data are helpful, but, due to the nature of the failure mechanism, cannot be used to accurately predict SEB.

- 3.2 <u>SEGR prediction</u>. Predictions of SEGR can be made from previous SEGR data or calculated using currently accepted models. If previous test results are unavailable or the device layout, design, or process has been modified, then SEGR failure thresholds can be predicted using an empirical prediction method or an analytical prediction method.

3

3.2.1 <u>SEGR empirical prediction</u>. The empirical prediction method uses an empirically derived equation to predict the SEGR failure threshold of the oxide capacitor when  $V_{DS} = 0$  volts, as expressed by Equation (1).

$$V_{GS} = \frac{(E_{OX\_BR})(T_{OX})}{\left(1 + \frac{LET}{53}\right)}$$

Where: E<sub>OX\_BR</sub> is the breakdown field strength of the oxide (V/cm), T<sub>OX</sub> is the thickness of the gate oxide dielectric (cm), and

LET\_PEAK is the maximum LET value of the given ion species in MeV/mg/cm2.

An approximation of the substrate response for the case when  $V_{DS}$  is biased can be obtained by using an expanded form of equation 1. This expanded equation is expressed by equation (2).

$$V_{GS} = (0.84)(1 - e^{\frac{-LET}{17}})(V_{DS}) - \frac{(E_{OX\_BR})(T_{OX})}{\left(1 + \frac{LET}{53}\right)}$$

Where: E<sub>OX\_BR</sub> is the breakdown field strength of the oxide (V/cm),

T<sub>OX</sub> is the thickness of the gate oxide dielectric (cm), and

LET is the linear energy transfer in (MeV/mg/cm2).

LET PEAK is the maximum LET value of the given ion species in MeV/mg/cm2

- 3.2.2 <u>SEGR analytical prediction</u>. Analytical predictions can be obtained using sophisticated numerical simulations to predict the SEGR failure threshold response. Additional information concerning these predictions can be found in the literature.

- 4. Characterization tests. Characterization testing is that testing required to obtain an SEB cross-sectional area curve, an SEGR cross-sectional area curve, or an SEGR failure threshold curve. Data points are taken to describe the response of the discrete MOSFET as a function of  $V_{GS}$  and/or  $V_{DS}$  over the operating range of the device and/or over a range of LET values. Characterization testing should be conducted initially to define the worst-case operating conditions of the device or to identify the sensitive die area. Additional characterization testing may be required after process and/or design changes have been made to the device. Characterization tests are useful for establishing the conditions for subsequent verification tests. Characterization testing does not have to be performed as a part of the verification testing unless fabrication changes have been made that might invalidate the initial technology characterization. Note that angling the die surface away from the plane where the ion beam is perpendicular to the die surface to produce an effective LET is invalid and shall not be used. It has been reported that the ion energy can influence the measured SEGR failure thresholds, suggesting that the ion energy shall be considered when a worst-case test condition is specified. The maximum allowable  $V_{DS}$  bias increment for a DUT shall be no more than 10 percent of the device's rated drain voltage. The maximum allowable  $V_{GS}$  bias increment for a DUT shall be no more demonstrated to increase the LET threshold for SEB but not for SEGR, indicating that lower operating temperatures are a worst-case test condition.

- 4.1 <u>SEB characterization</u>. Characterization requires that an SEB circumvention method be utilized. SEB characterization produces a cross-sectional area curve as a function of LET for a fixed  $V_{DS}$  and  $V_{GS}$ . SEB is not sensitive to changes in the gate bias,  $V_{GS}$ . The  $V_{GS}$  bias shall be sufficient to bias the DUT in an "off" state (a few volts below  $V_{TH}$ ), allowing for total dose effects that may reduce the  $V_{TH}$ . Multiple SEB cross-sectional area curves may be required, expressing different operating conditions for  $V_{DS}$ . Note that p-channel devices have not been demonstrated to be sensitive to SEB.

4

METHOD 1080

- 4.1.1 <u>SEB cross-sectional area</u> If specified as a test requirement and if SEB is observed, one of the many reported techniques can be used to circumvent catastrophic SEB failure, such as a current-limiting resistor placed between the drain stiffening capacitor and the drain electrode. Then, to obtain an SEB error count, a current probe (Tektronix CT-2, sense resistor, or other suitable current probe) shall be inserted between the source electrode and ground. Using this setup, an SEB event will produce current pulses. SEB occurrence can be monitored using an electronic oscilloscope to record the shape of the SEB pulse(s), if required, and a pulse counter to record the number of SEB occurrences. A point on the SEB cross-sectional area curve is then obtained by dividing the number of SEB events by the fluence for that given test condition. The SEB cross sectional curve is subsequently found by finding points at several different LET values. After the DUTs have been delidded and the chamber evacuated, apply the specified V<sub>GS</sub> and V<sub>DS</sub> bias condition; and irradiate the DUT to the specified fluence level (typical ranges are between 10<sup>5</sup> and 10<sup>7</sup> ions/cm<sup>2</sup>). If SEB occurs, record the event by incrementing the counter. The flux shall be adjusted so that the number of SEB events is no more than 100 events per second. When the desired fluence is achieved, the beam is shuttered; and the total number of SEB events are recorded. This process is continued, selecting different ions to obtain the required LET values. Repeat this process for the specified samples and conditions.

- 4.2 <u>SEGR characterization</u>. SEGR characterization may produce three unique curves: an SEGR cross-sectional area curve as a function of LET for a fixed  $V_{GS}$  and  $V_{DS}$  bias condition, an SEGR threshold curve of  $V_{GS}$  as a function of  $V_{DS}$  for a fixed LET value, or an SEGR threshold curve of  $V_{DS}$  as a function of LET at a fixed  $V_{GS}$ . Multiple SEGR cross sectional area curves may be required to express different  $V_{DS}$  and  $V_{GS}$  conditions. Multiple SEGR threshold curves may be required to express different  $V_{GS}$ ,  $V_{DS}$ , or LET conditions. SEGR characterization may be performed in conjunction with SEGR verification.

- 4.2.1 <u>SEGR cross-sectional area</u>. If specified in the test requirements and if SEGR occurs, an SEGR cross-sectional area curve can be obtained. However, SEGR cannot be circumvented. Hence, to obtain an SEGR cross-sectional area curve requires the destruction of numerous devices. For a given device, the ion irradiation would be terminated upon detection of SEGR. One point on the SEGR cross-sectional area curve can be obtained by dividing one SEGR event by the measured fluence to induce that event. After the DUTs have been delidded and the chamber evacuated, apply the specified V<sub>GS</sub> and V<sub>DS</sub> bias condition; and irradiate the DUT to the specified fluence level. If SEGR occurs, immediately terminate the exposure; and record the accumulated fluence. Note that the ion flux can be lowered to obtain a more accurate fluence. If the maximum fluence is achieved and the DUT passes the post gate-stress test, a new test condition or a new DUT is selected. If SEGR occurs, a new DUT is selected. Apply the new test condition (incrementing V<sub>GS</sub>, V<sub>DS</sub>, or changing the ion specie). This process is repeated until the desired curve is obtained. Repeat this process to obtain the required curves. Note that characterization results in device failure and only represents a single data point for that device. For the special case where the applied dc field across the gate dielectric is less than 1 MV/cm, the procedure to obtain a cross-sectional area curve should be modified as follows:

- a. An incremental fluence should be set at one-third of the die area or less;

- b. After each irradiation step, a post gate-stress test shall be performed to verify device functionality;

- c. If SEGR is not detected, continue irradiation steps until SEGR occurs or until the maximum accumulated fluence is obtained; and

- d. Select new device and bias condition and repeat test procedure until the desired curve is obtained.

- 4.2.2 <u>SEGR post gate-stress test</u>. If the gate bias is small (typically  $V_{GS}$  < 10 volts) during irradiation, SEGR may or may not produce a catastrophic failure until sufficient gate bias is applied. If an insufficient gate bias is applied, SEGR may only produce a latent defect site. Therefore, after the irradiation, a post gate-stress test shall be performed on each test device. The post gate-stress test shall apply a gate bias equal to the maximum operating gate voltage (nominally  $\pm 10$  percent) or as specified.

- 5. <u>Verification tests</u>. Verification testing requires the irradiation of the DUT to specified test conditions (e.g. gate bias, drain bias, ion species, ion energy, ion LET, ion range, ion flux, and ion fluence). Verification testing is useful for hardness assurance and qualification testing of discrete power MOSFETs to determine their suitability at the specified test conditions. These tests use a "pass"/"no pass" criterion and can be destructive. Note that angling the die surface away from the plane where the ion beam is perpendicular to that surface to produce an effective LET is invalid and shall not be used to conduct these tests. It has been reported that the ion energy can influence the measured SEGR failure thresholds, suggesting that the ion energy should be considered to achieve a worst-case test condition. Also, note that increasing the DUT's operating temperature has been demonstrated to increase the LET threshold for SEB but not for SEGR, indicating that lower operating temperatures are a worst-case test condition.

- $5.1 \ \underline{\text{SEB verification tests}}$ . For SEB verification, a sufficiently large capacitance is placed at the drain electrode to produce catastrophic failure. Note that no circumvention techniques are used in this test. After the DUTs have been delidded and the chamber evacuated, apply the specified  $V_{GS}$  and  $V_{DS}$  bias condition and irradiate the DUT to the specified fluence level. If failure occurs, the exposure can be terminated. Record SEB results. Repeat for the specified samples and conditions.

- 5.2 <u>SEGR verification tests</u>. For SEGR verification, this test is a two-step process. After DUTs have been delidded and the chamber evacuated, apply the specified VGS and VDS bias condition and irradiate the DUT to the specified fluence. If failure occurs, the exposure can be terminated. The second step requires a post gate-stress test to be performed after irradiation, if the gate bias during irradiation was less that the maximum operating gate voltage. Record SEGR result. Repeat for the specified samples and conditions.

- 6. <u>SEB/SEGR test procedure</u>. The test plan should document the proper steps to be followed before, during, and after heavy ion irradiation. Sufficient samples shall be obtained to conduct the test. Samples with conformal coatings, such as polyamide, should be chemically removed before testing. SEB and SEGR both can result in catastrophic failure that produces large leakage currents, destroying the device. In SEB testing, a capacitance sufficient to hold the bias voltage within ±10 percent may be required to induce damage during an SEB event. For characterization testing, SEB can be circumvented and recorded producing an SEB event count, which then can be used to produce a point on the cross-sectional area curve. To help select the proper biases, an SEB/SEGR prediction shall be made. The required ion specie is selected and the ion beam energy shall be tuned and verified using the dosimetry system. The test circuit board, cabling, and instrumentation shall be connected and its operation verified. Before irradiation, test devices shall be delidded and inserted into the test board. The drain and gate currents, I<sub>GS</sub> and I<sub>DS</sub>, shall be monitored before, during, and after the irradiation(s), as well as during the post gate-stress test, to verify the condition of the DUT. After completion of the test run, the results of the test shall be recorded and documented.

- 6.1 <u>Test plan</u>. A test plan shall be devised that supports each test. The test plan shall be used as a guide for the procedures and decisions during irradiation. The test plan shall be developed, and the following conditions shall be outlined.

- 6.1.1 <u>Ion specie and energy</u>. The test plan shall identify the ion specie and an appropriate energy to perform the test. Selection of a specific ion specie and its energy determines the LET value. Obtaining a range of LET values requires using different ion species at different energies. Note that using angles to modulate the LET value is unacceptable. Selection of a different ion specie and energy by test personnel requires verification that the ion LET and its range meet the test requirements. Verification can be made using the TRIM code or other suitable simulation codes for the given device material. Also, note that the energy of the ion beam has been shown to influence the SEGR failure thresholds. Therefore, determination of the worst-case test condition can require multiple irradiations with the same ion at different energies.

- 6.1.2 <u>Device information</u>. The test plan shall provide a description of the devices to be tested and the number of test samples required for each test. The test plan shall identify the device type, acceptance lot, and other critical information. Devices shall be marked for traceability so that lids can be removed. Identification markers should be placed on the flange and not on the lid. Only devices that have passed the pre-electrical tests shall undergo heavy ion testing. Test samples shall be randomly selected from the parent population. The number of samples shall be specified to meet the test requirements. For the purposes of verification testing, a representative sample should be selected from the lot.

- 6.1.3 Electrical parameters. The test plan shall specify the electrical parameters to be measured before and after irradiation.

- 6.1.4 <u>Test configuration</u>. The test plan shall specify the bias and exposure conditions for each test sample. The test plan shall specify the case temperature of the DUT if it is required to be set at other than the room ambient temperature.

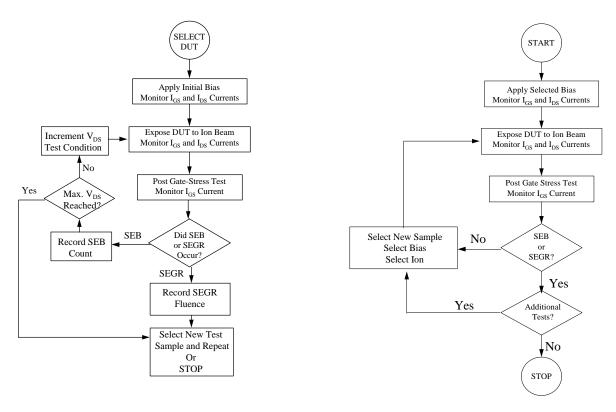

- 6.1.5 <u>Test sequence</u>. The test plan should specify a test sequence similar to figure 1080-3. For characterization testing, the test plan shall define an initial bias condition and the bias increment. The  $V_{DS}$  bias increment shall not exceed 10 percent of the device's rated drain breakdown voltage. For verification testing, the test plan shall define the specified biases, the minimum number of samples that shall be tested at each bias, and the handling of the devices after testing. Any additional electrical tests shall be specified and any special handling requirements shall be specified.

- 6.1.6 <u>SEB/SEGR detection</u>. The test plan shall specify the procedure to monitor the drain and gate currents, I<sub>GS</sub> and I<sub>DS</sub>, before, during, and after the irradiation(s). In addition, the gate and drain currents shall be monitored during the post gate-stress test to verify that the DUT was not damaged during the previous irradiation.

Characterization flowchart sample.

Verification flowchart sample.

FIGURE 1080-3. Test plan flowcharts.

- 6.1.7 Data recording. The test plan shall specify the necessary parameters that shall be recorded during the test.

- 6.1.8 Reporting requirements. The test plan shall specify the test documentation as required by 7 herein.

- 6.2 <u>Radiation test procedure</u>. The test plan shall be used as a guide to perform the radiation test. A typical SEB/SEGR test procedure is given here as an example.

- Test personnel shall specify the selected ion specie and energy to the facility operators as defined in the SEGR/SEB test plan specifying the desired flux, fluence, LET, range, and beam uniformity. Dosimetry shall be performed to verify that the ion beam characteristics are as specified.

- b. The SEGR/SEB test board shall be mounted in the test fixture mounting frame. All necessary test cables shall be connected to the test board and vacuum feed-through inside the vacuum chamber.

- c. The test instrumentation shall be set up as close as possible to the vacuum chamber. All necessary test cables shall be connected to the test hardware and vacuum feed-through outside the vacuum chamber.

- d. When the test system is set up, the operation of the test system shall be verified for continuity and operation. Note that a quick check can be performed by applying a  $V_{GS}$  and  $V_{DS}$  and verifying the presence of these voltages with a voltmeter.

- e. After test system verification is completed, ground all electrodes; and insert the devices for test. Handling of devices shall be in accordance with normal ESD practices. If lids were not removed before placement on the test board, remove the device lids. To verify that the devices were not damaged during the delidding process or insertion into the test board, a simple electrical check of los and los should be performed.

- f. After device verification is completed, the device to be tested shall be aligned to the ion beam. With the beam shuttered and the DUT biases set at 0 volts, perform an alignment of the DUT to the ion beam. Note that some facilities provide a laser alignment system for this task.

- g. When positional alignment is complete, turn off any lighting systems and laser systems in the vacuum chamber. Apply the selected bias conditions to the DUT; and begin monitoring the gate and drain leakage currents, I<sub>GS</sub> and I<sub>DS</sub>. Note that excitation by lights or laser may produce photocurrents which may interfere with the measurements.

- h. When ready, open the ion beam shutter, exposing the DUT to the heavy ion beam. Note that most facilities include instrumentation to monitor the ion beam characteristics monitoring the average flux, fluence, and beam uniformity which should be recorded. When the desired fluence level is achieved, shutter the ion beam, terminating the irradiation.

- (1) If performing an SEB characterization test, the test circuit shall include an appropriate circumvention technique and a current-sensing circuit. The number of current pulses for each irradiation shall be recorded (see 4.1).

- (2) If performing an SEGR characterization test, the ion beam shall be shuttered immediately following the detection of SEGR-any significant gate current change. The ion fluence at failure shall be recorded. Note that detection of SEGR may require the test personnel to make a judgment concerning the SEGR status of the device.

- (3) If performing an SEGR or SEB verification test, the gate and drain leakage currents, I<sub>GS</sub> and I<sub>DS</sub>, shall be monitored. If a current change is recorded (typically, a flag can be set, e.g. an I<sub>GS</sub> > 10<sup>-7</sup> amps), document the observed conditions.

- After the ion beam is shuttered, a post gate-stress test shall be performed. During the post gate-stress test (the rated gate voltage is applied), the gate current shall be monitored. If a current change is detected (typically, a flag can be set, e.g. an I<sub>GS</sub> > 10<sup>-7</sup> amps), document any observed conditions.

- j. Upon completion of the post gate-stress test, record all pertinent test data. Record run number, ion specie, ion energy, range, LET, average flux, fluence, and test conditions (V<sub>GS</sub>, V<sub>DS</sub>). Record any changes in the drain or gate currents (I<sub>GS</sub> and I<sub>DS</sub>) before, during, and after the ion irradiation. Record any changes in the drain and gate currents, I<sub>GS</sub> and I<sub>DS</sub>, during the post gate-stress test. Determine the status of the test run. If the test is a characterization test, increment the test condition or select new device as required. Repeat test procedure. If the test is a verification, select next device and test conditions. Repeat test procedure.

METHOD 1080 8

- 7. <u>Data formatting reporting</u>. Test data/test reports shall be maintained and shall include the following information:

- a. Device type, identification marker, lot identification, and date code.

- b. Test date and test personnel names.

- c. Facility, accelerator type, identification of ion, energy, average flux, LET, range in device material, and fluence.

- d. Schematic of test circuit or test board.

- e. Dosimetry output of each ion beam used.

- f. Bias condition of each exposure run.

- g. Record of observed SEGR or SEB (current changes).

- h. Device case temperature (only if required at other than room ambient)

#### METHOD 2037.1

#### BOND STRENGTH (DESTRUCTIVE BOND PULL TEST)

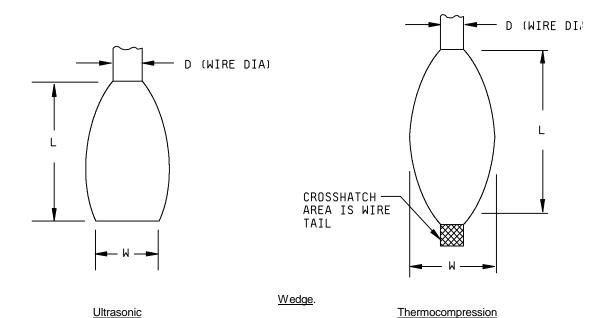

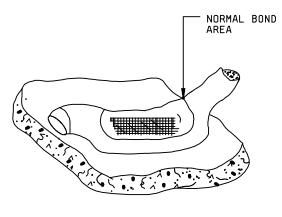

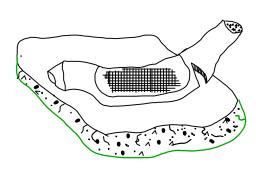

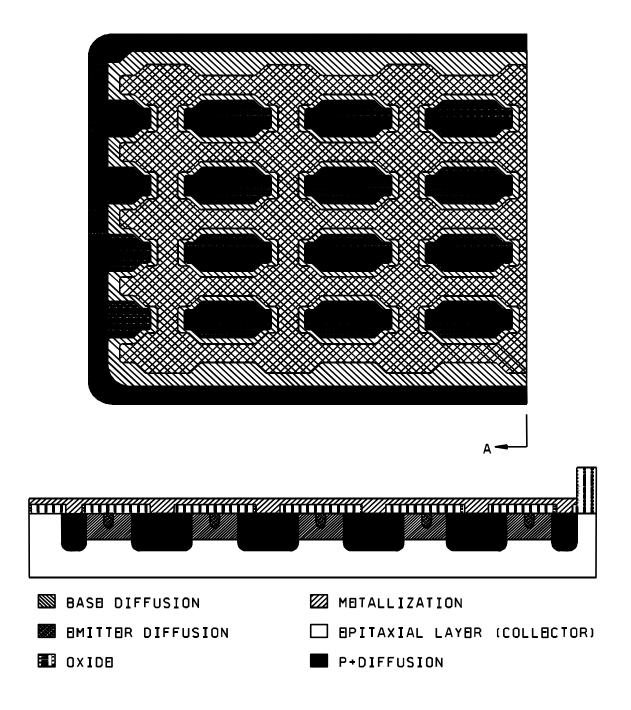

- 1. <u>PURPOSE</u>. The purpose of this test is to measure bond strengths, evaluate bond strength distributions, or determine compliance with specified bond strength requirements of the applicable acquisition document. This test may be applied to the wire-to-die bond, wire-to-substrate bond, or the wire-to-package lead bond inside the package of wire-connected microelectronic devices bonded by soldering, thermocompression, ultrasonic, or related techniques. It may also be applied to bonds external to the device such as those from device terminals-to-substrate or wiring board or to internal bonds between die and substrate in non-wire-bonded device configurations such as beam lead or flip chip devices.

- 2. <u>APPARATUS</u>. The apparatus for this test shall consist of suitable equipment for applying the specified stress to the bond, lead wire or terminal as required in the specified test condition. A calibrated measurement and indication of the applied stress in grams force (gf) shall be provided by equipment capable of measuring stresses up to twice the specified minimum limit value, with an accuracy of ±5 percent or ±0.25 gf, whichever is the greater tolerance.

- 3. <u>PROCEDURE</u>. The test shall be conducted using the test condition specified in the applicable acquisition document consistent with the particular device construction. All bond pulls shall be counted and the specified sampling, acceptance, and added sample provisions shall be observed, as applicable. Unless otherwise specified, for conditions A, C, and D, the sample size number specified for the bond strength test shall determine the minimum sample size in terms of the minimum number of bond pulls to be accomplished rather than the number of complete devices in the sample, except that the required number of bond pulls shall be randomly selected from a minimum of 4 devices. Bond pulls in accordance with test conditions D, F, G, and H, while involving two or more bonds shall count as a single pull for bond strength and sample size number purposes. Unless otherwise specified, for conditions F, G, and H the sample size number specified shall determine the number of die to be tested (not bonds). For multichip devices (all conditions), a minimum of 4 die or use all die if four are not available on a minimum of 2 completed devices shall be used. Where there is any adhesive, encapsulant or other material under, on or surrounding the die such as to increase the apparent bond strength, the bond strength test shall be performed prior to application.

When flip chip or beam-lead chips are bonded to substrates other than those in completed devices, the following conditions shall apply:

- a. The sample of chips for this test shall be taken at random from the same chip population as that used in the completed devices that they are intended to represent.

- b. The chips for this test shall be bonded on the same bonding apparatus as the completed devices, during the time period within which the completed devices are bonded.

- c. The test chip substrates shall be processed, metallized, and handled identically with the completed device substrates, during the same time period within which the completed device substrates are processed.

## 3.1 Test conditions:

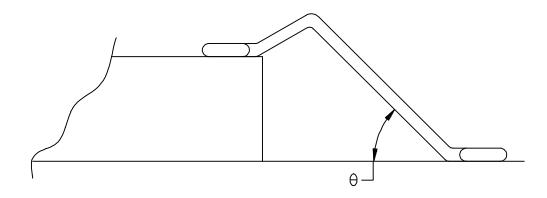

- 3.1.1 <u>Test condition A Bond peel</u>. This test is normally employed for bonds external to the device package. The lead or terminal and the device package shall be gripped or clamped in such a manner that a peeling stress is exerted with the specified angle between the lead or terminal and the board or substrate. Unless otherwise specified, an angle of 90 degrees shall be used. When a failure occurs, the force causing the failure and the failure category shall be recorded.

- 3.1.2 Test condition C Wire pull (single bond). This test is normally employed for internal bonds at the die or substrate and the lead frame of microelectronic devices. The wire connecting the die or substrate shall be cut so as to provide two ends accessible for pull test. In the case of short wire runs, it may be necessary to cut the wire close to one termination in order to allow pull test at the opposite termination. The wire shall be gripped in a suitable device and simple pulling action applied to the wire or to the device (with the wire clamped) in such a manner that the force is applied approximately normal to the surface of the die or substrate. When a failure occurs, the force causing the failure and the failure category shall be recorded.

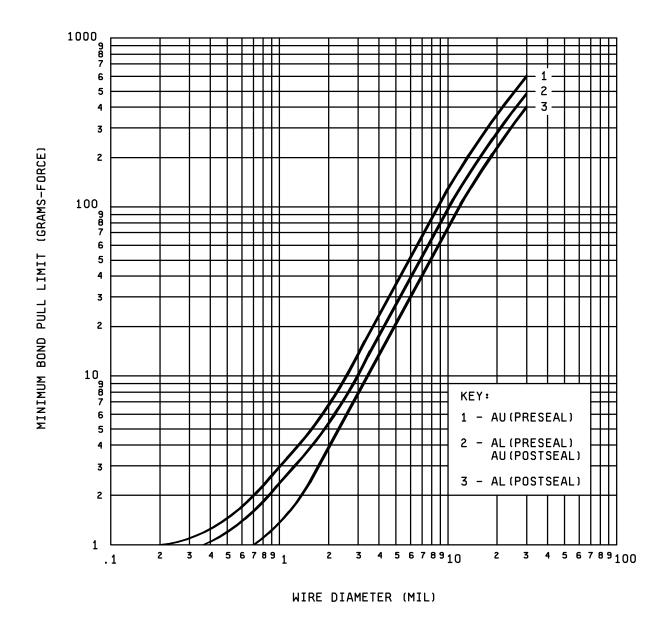

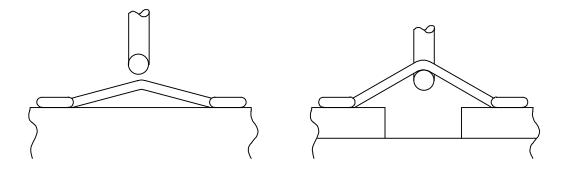

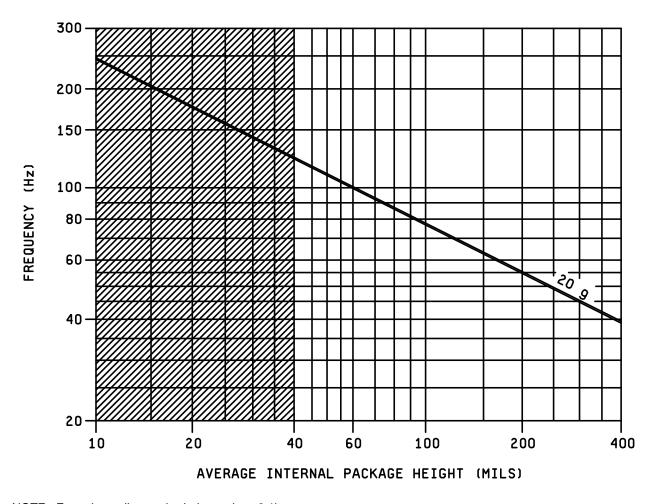

- 3.1.3 <u>Test condition D Wire pull (double bond)</u>. This procedure is identical to that of test condition C, except that the pull is applied by inserting a hook under the lead wire (attached to die, substrate or header or both ends) with the device clamped and the pulling force applied approximately in the center of the wire in a direction approximately normal to the die or substrate surface or approximately normal to a straight line between the bonds. When a failure occurs, the force causing the failure and the failure category shall be recorded. The minimum bond strength shall be taken from table I. Figure 2037.1-1 may be used for wire diameters not specified in table I. For wire diameter or equivalent cross section >0.005 inch, where a hook will not fit under the wire, a suitable clamp can be used in lieu of a hook.

- 3.1.4 <u>Test condition F Bond shear (flip chip)</u>. This test is normally employed for internal bonds between a semiconductor die and a substrate to which it is attached in a face-bonded configuration. It may also be used to test the bonds between a substrate and an intermediate carrier or secondary substrate to which the die is mounted. A suitable tool or wedge shall be brought in contact with the die (or carrier) at a point just above the primary substrate and a force applied perpendicular to one edge of the die (or carrier) and parallel to the primary substrate, to cause bond failure by shear. When a failure occurs, the force at the time of failure, and the failure category shall be recorded.

- 3.1.5 Test condition G Push-off test (beam lead). This test is normally employed for process control and is used on a sample of semiconductor die bonded to a specially prepared substrate. Therefore, it cannot be used for random sampling of production or inspection lots. A metallized substrate containing a hole shall be employed. The hole appropriately centered, shall be sufficiently large to provide clearance for a push tool, but not large enough to interfere with the bonding areas. The push tool shall be sufficiently large to minimize device cracking during testing, but not large enough to contact the beam leads in the anchor bond area. Proceed with push-off tests as follows: The substrate shall be rigidly held and the push tool inserted through the hole. The contact of the push tool to the silicon device shall be made without appreciable impact (less than 0.01 inch/minute (0.254 mm/minute) and forced against the underside of the bonded device at a constant rate. When failure occurs, the force at the time of failure, and the failure category shall be recorded.

- 3.1.6 <u>Test condition H Pull-off test (beam lead)</u>. This test is normally employed on a sample basis on beam lead devices which have been bonded down on a ceramic or other suitable substrate. The calibrated pull-off apparatus (see 2) shall include a pull-off rod (for instance, a current loop of nichrome or Kovar wire) to make connection with a hard setting adhesive material (for instance, heat sensitive polyvinyl acetate resin glue) on the back (top side) of the beam lead die. The substrate shall be rigidly installed in the pull-off fixture and the pull-off rod shall make firm mechanical connection to the adhesive material. The device shall be pulled within 5 degrees of the normal to at least the calculated force (see 3.2), or until the die is at 2.54 mm (0.10 inch) above the substrate. When a failure occurs, the force at the time of failure, the calculated force limit, and the failure category shall be recorded.