The documentation and process conversion measures necessary to comply with this Notice shall be completed by INCH-POUND

MIL-STD-750D NOTICE 2 23 February 1996

NOTICE OF CHANGE

# MILITARY STANDARD

# TEST METHODS FOR SEMICONDUCTOR DEVICES

TO ALL HOLDERS OF MIL-STD-750D:

### 1. THE FOLLOWING PAGES OF MIL-STD-750D HAVE BEEN REVISED AND SUPERSEDE THE PAGES LISTED:

| METHOD | NEW PAGE | DATE             | SUPERSEDED P/ | AGE DATE                 |

|--------|----------|------------------|---------------|--------------------------|

|        | 9        | 23 February 1996 | 9             | 28 February 1995         |

|        | 10       | 23 February 1996 | 10            | 28 February 1995         |

|        | 11       | 23 February 1996 | 11            | 28 February 1995         |

|        | 12       | 23 February 1996 | 12            | 28 February 1995         |

|        | 15       | 23 February 1996 | 15            | 18 May 1995              |

|        | 16       | 23 February 1996 | 16            | 18 May 1995              |

|        | 17       | 23 February 1996 | 17            | REPRINTED WITHOUT CHANGE |

|        | 18       | 23 February 1996 | 18            | 28 February 1995         |

| 1020.2 | 3        | 23 February 1996 | 3             | 28 February 1995         |

| 1020.2 | 4        | 23 February 1996 | 4             | REPRINTED WITHOUT CHANGE |

| 2037   | 1        | 23 February 1996 | 1             | REPRINTED WITHOUT CHANGE |

| 2037   | 2        | 23 February 1996 | 2             | 28 February 1995         |

2. THE FOLLOWING TEST METHODS OF MIL-STD-750D HAVE BEEN REVISED AND SUPERSEDE THE TEST METHOD LISTED:

| METHOD | DATE             | SUPERSEDED METHOD | DATE             |

|--------|------------------|-------------------|------------------|

| 1001.2 | 23 February 1996 | 1001.1            | 28 February 1995 |

| 1011.1 | 23 February 1996 | 1011              | 28 February 1995 |

| 1015.1 | 23 February 1996 | 1015              | 28 February 1995 |

| 1021.3 | 23 February 1996 | 1021.2            | 28 February 1995 |

| 1038.4 | 23 February 1996 | 1038.3            | 28 February 1995 |

| 1046.3 | 23 February 1996 | 1046.2            | 28 February 1995 |

| 2069.1 | 23 February 1996 | 2069              | 28 February 1995 |

| 2072.6 | 23 February 1996 | 2072.5            | 28 February 1995 |

| 2074.3 | 23 February 1996 | 2074.2            | 28 February 1995 |

| 2076.3 | 23 February 1996 | 2076.2            | 28 February 1995 |

| 3105.1 | 23 February 1996 | 3105              | 28 February 1995 |

| 4026.3 | 23 February 1996 | 4026.2            | 28 February 1995 |

| 4031.4 | 23 February 1996 | 4031.3            | 28 February 1995 |

|        |                  |                   |                  |

# 3. RETAIN THIS NOTICE AND INSERT BEFORE TABLE OF CONTENTS.

4. Holders of MIL-STD-750D will verify that page changes and additions indicated above have been entered. This notice page will be retained as a check sheet. This issuance, together with appended pages, is a separate publication. Each notice is to be retained by stocking points until the military standard is completely revised or canceled.

CONCLUDING MATERIAL

Custodians: Army - ER Navy - EC Air Force - 17 NASA - NA Preparing activity: DLA - ES

(Project 5961-1792)

Review activities: Army - AR, MI Navy - AS, CG, MC, SH Air Force - 19, 85, 99

- b. Connectors to test boards or trays. After the test boards are loaded with devices, inserted into the system, and brought up to the specified operating conditions, each required test voltage and signal condition shall be verified in at least one location on each test board or tray so as to assure electrical continuity and the correct application of specified electrical stresses for each connection or contact pair used in the applicable test configuration. The system may be opened for a maximum of 10 minutes.

- c. At the conclusion of the test period, prior to removal of devices from temperature and bias conditions, the voltage and signal condition verification of 4.4b shall be repeated.

- d. For class S devices, each test board or tray and each test socket shall be verified prior to test to assure that the specified bias conditions are applied to each device. This may be accomplished by verifying the device functional response at each device output(s) or by performing a socket verification on each socket prior to loading. An approved alternate procedure may be used.

4.4.1 <u>Bias interruption</u>. Where failures or open contacts occur which result in removal of the required bias stresses for any period of the required bias duration, the bias time shall be extended to assure actual exposure for the total minimum specified test duration. Any loss(es) or interruption(s) of bias in excess of 10 minutes total duration while the chamber is at temperature during the final 8 hours of burn-in shall require extension of the bias duration for an uninterrupted 8 hours minimum, after the last bias interruption.

#### 4.5 Requirements for HTRB and burn-in.

- a. The temperature of +20°C minimum is the ambient air temperature to which all devices should be exposed during power screening where room ambient is specified.

- b. An increase in effective ambient temperature from cumulative induced power to DUTs shall not result in device junction temperature exceeding maximum ratings.

- c. Ambient temperature shall not be measured in the convection current (above) or downstream (Fan Air) of DUTs.

- d. Moving air greater than 30 CFM (natural convection) may be allowed for the purpose of temperature equalization within high device density burn-in racks.

- e. High velocity or cooled air shall not be used for the purpose of increasing device ratings.

- f. Power up of burn-in racks may occur when ambient is less than specified. When thermal equilibrium has been reached, or five hours maximum has occurred, the ambient shall be at the specified value. Time accrued prior to reaching specified ambient shall not be chargeable, to the life test duration.

- g. If the ambient at or beyond the five hour point is not the specified value, a nonconformance shall exist requiring corrective action.

- h. Time is not chargeable during the period when specified conditions are not maintained. If device maximum ratings(if life test, finish the test and use for credit; if shippable, use this criteria)are exceeded and the manufacturer intends to submit the lot affected, the product on test must be evaluated by re-starting the burn-in or HTRB from zero hours at the specified temperature and verifying that the end-point failure rate is typical for this product type from a review of established records.

- i. Chamber temperature for HTRB and burn-in shall be controlled to ±3 percent of the specified value. (Unless otherwise specified in 4.1.1.) This temperature shall be maintained within the chamber. Forced air may be used to equalize temperature within the chamber but shall not be used as a coolant to increase device power capability.

- 4.6 Bias requirements.

- a. Bias errors at the power supply source caused by changing power supply loads during temperature transitions shall not exceed ±5 percent of that specified value.

SUPERSEDES PAGE 9 OF MIL-STD-750D

- b. Bias values at the source, during stabilized conditions, shall not exceed ±3 percent of the specified value.

- c. Burn-in apparatus shall be arranged so as to result in the approximate average power dissipation for each device whether devices are tested individually or in a group. Bias and burn-in circuitry tolerances should not vary test conditions to individual devices by more than ±5 percent of specified conditions.

- d. Normal variation in individual device characteristics need not be compensated for by burn-in circuitry.

- e. Burn-in equipment shall be arranged so that the existence of failed or abnormal devices in a group does not negate the effect of the test for other devices in the group. Periodic verification will assure that specified conditions are being maintained. Verification shall be performed, as a minimum, at the starting and end of screening.

- f. Lead, stud, or case mounted devices shall be mounted in their normal mounting configuration and the point of mechanical connection shall be maintained at no less than the specified ambient.

- 4.7 Destructive tests. Unless otherwise demonstrated, the following MIL-STD-750 tests are classified as destructive:

|                       | TEOT                                      |

|-----------------------|-------------------------------------------|

| METHOD NUMBER         | TEST                                      |

| 1017                  | Neutron irradiation                       |

| 1019                  | Steady state total dose irradiation       |

| 1020                  | ESDS classification                       |

| 1021                  | Moisture resistance                       |

| 1036,1037             | Intermittent operation life               |

| 1041                  | Salt atmosphere                           |

| 1042<br>(Condition D) | Burn-in/life test for power MOSFETs       |

| 1046                  | Salt spray                                |

| 1056                  | Thermal shock (glass strain)              |

| 2017                  | Die shear test                            |

| 2031                  | Soldering heat                            |

| 2036                  | Terminal strength                         |

| 2037                  | Post seal bond strength                   |

| 2075                  | Decap internal visual design verification |

| 2077                  | SEM                                       |

All other mechanical or environmental tests (other than those listed in 4.8) shall be considered destructive initially, but may subsequently be considered nondestructive upon accumulation of sufficient data to indicate that the test is nondestructive. The accumulation of data from five repetitions of the specified test on the same sample of product, without significant evidence of cumulative degradation in any device in the sample, is considered sufficient evidence that the test is nondestructive for the device of that manufacturer. Any test specified as a 100 percent screen shall be considered nondestructive for the stress level and duration or number of cycles applied as a screen.

SUPERSEDES PAGE 10 OF MIL-STD-750D

4.8 Nondestructive tests. Unless otherwise demonstrated, the following MIL-STD-750 tests are classified as nondestructive:

| METHOD NUMBER                                   | TEST                                                                                                                    |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 1001                                            | Barometric pressure                                                                                                     |

| 1022                                            | Resistance to solvents                                                                                                  |

| 1026,1027                                       | Steady-state life                                                                                                       |

| 1031,1032                                       | High temperature life (nonoperating)                                                                                    |

| 1038,1039,1040                                  | Burn-in screen                                                                                                          |

| 1042 (Condition A,B, and C)                     | Burn-n/life test for power MOSFETs                                                                                      |

| 1051 (100 cycles or less)                       | Thermal shock (temperature cycling                                                                                      |

| 1071                                            | Hermetic seal tests                                                                                                     |

| 2006                                            | Constant acceleration                                                                                                   |

| 2016                                            | Shock                                                                                                                   |

| 2026                                            | Solerability (if the original lead finish is unchanged and if the maximum allowable number of reworks is not exceeded.) |

| 2052                                            | PIND test                                                                                                               |

| 2056                                            | Vibration, variable frequency                                                                                           |

| 2066                                            | Physical dimensions                                                                                                     |

| 2069,2070,2072,2073,2074                        | Internal visual (pre-cap)                                                                                               |

| 2071                                            | External visual                                                                                                         |

| 2076                                            | Radiographic inspection                                                                                                 |

| 2081                                            | Forward instability shock test (FIST)                                                                                   |

| 2082                                            | Backward instability shock test (BIST)                                                                                  |

| 3101                                            | Thermal impedance testing of diodes                                                                                     |

| 3103                                            | Thermal impedance measurements for IGBTs                                                                                |

| 3104                                            | Thermal impedance measurements for GaAs                                                                                 |

| 3051,3052,3053<br>(with limited supply voltage) | Safe operating area (SOA) (condition A for method 3053)                                                                 |

| 3131                                            | Thermal resistance (emitter to base forward voltage, emitter-only switching method)                                     |

| 4066                                            | Surge current                                                                                                           |

| 4081                                            | Thermal resistance of lead mounted diode (forward voltage, switching method)                                            |

When the junction temperature exceeds the device maximum rated junction temperature for any operation or test (including electrical stress test), these tests shall be considered destructive except under transient surge or nonrepetitive fault conditions or approved accelerated screening when, it may be desirable to allow the junction temperature to exceed the rated junction temperature. The feasibility shall be determined on a part by part basis and in the case where it is allowed adequate sample testing shall be performed to provide the proper reliability safeguards.

SUPERSEDES PAGE 11 OF MIL-STD-750D

4.9 <u>Laboratory suitability</u>. Prior to processing any semiconductor devices intended for use in any military system or subsystem, the facility performing the test(s) must be audited by the Defense Electronics Supply Center, Sourcing and Qualification Division (DESC-ELST) and be granted written Laboratory Suitability status for each test method to be employed. Processing of any devices by any facility without Laboratory Suitability status for the test methods used shall render the processed devices nonconforming.

# 5. DETAILED REQUIREMENTS (NOT APPLICABLE)

# 6. NOTES

6.1 <u>International standardization agreement</u>. Certain provisions of this standard are the subject of international standardization agreement. When amendment, revision, or cancellation of this standard is proposed which will affect or violate the international agreement concerned, the preparing activity will take appropriate reconciliation action through international standardization channels, including departmental standardization offices, if required.

Custodians: Navy - EC Army - ER Air Force - 17 NASA - NA

Review activities: Army - AR, ER, MI Navy - AS, CG, MC, SH Air Force - 19, 85, 99 Preparing activity: DLA - EC

(Project 5961-1451)

SUPERSEDES PAGE 12 OF MIL-STD-750D

# Numerical index of test methods

| Method no.                                                                                                                                                                                                                                                                                              | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                         | Environmental tests (1000 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| *1001.2<br>*1011.1<br>*1015.1<br>1016.1<br>1017.1<br>1018<br>1019.4<br>*1020.2<br>*1021.3<br>1022.5<br>1026.5<br>1027.3<br>1031.5<br>1032.2<br>1036.3<br>1037.2<br>*1038.4<br>1039.4<br>1040<br>1041.3<br>1042.3<br>*1046.3<br>1048<br>1049<br>1051.5<br>1054.1<br>1055.1<br>1056.7<br>1061.1<br>1056.7 | Barometric pressure (reduced).<br>Immersion.<br>Steady-state primary photocurrent irradiation procedure (electron beam).<br>Insulation resistance.<br>Neutron irradiation.<br>Internal water-vapor content.<br>Steady-state total dose irradiation procedure.<br>Electrostatic discharge sensitivity (ESDS) classification.<br>Moisture resistance.<br>Resistance to solvents.<br>Steady-state operation life.<br>Steady-state operation life (sample plan).<br>High-temperature life (nonoperating).<br>High-temperature (nonoperating) life (sample plan).<br>Intermittent operation life.<br>Burn-in (for diodes, rectifiers, and zeners).<br>Burn-in (for transistors).<br>Burn-in (for thyristors (controlled rectifiers)).<br>Satt spray (corrosion).<br>Burn-in and life test for power MOSFET's or insulated gate bipolar transistors (IGBT).<br>Sat spray (corrosion).<br>Blocking life (sample plan).<br>Temperature cycling (air to air).<br>Potted environment stress test.<br>Monitored mission temperature cycle.<br>Thermal shock (liquid to liquid).<br>Temperature measurement, case and stud.<br>Dew point.<br>Hermetic seal. |

|                                                                                                                                                                                                                                                                                                         | Mechanical characteristics tests (2000 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2005.2<br>2006<br>2016.2<br>2017.2<br>2026.10<br>2031.2<br>2036.4<br>*2037<br>2046.1<br>2051.1<br>2052.2<br>2056<br>2057.1<br>2066<br>2068<br>*2069.1<br>2070.1<br>2071.3<br>*2072.6<br>2073<br>*2074.4<br>2075                                                                                         | Axial lead tensile test.<br>Constant acceleration.<br>Shock.<br>Die attach integrity.<br>Solderability.<br>Solderability.<br>Soldering heat.<br>Terminal strength.<br>Bond strength.<br>Bond strength.<br>Vibration fatigue.<br>Vibration noise.<br>Particle impact noise detection (PIND) test.<br>Vibration noise.<br>Particle impact noise detection (PIND) test.<br>Vibration, variable frequency.<br>Vibration, variable frequency.<br>Vibration, variable frequency.<br>Nyiscial dimensions.<br>External visual for nontransparent, glass-encased, double plug, noncavity, axial leaded diodes.<br>Pre-cap visual, power MOSFET's.<br>Pre-cap visual microwave discrete and multichip transistors.<br>Visual and mechanical examination.<br>Internal visual transistor (pre-cap) inspection.<br>Visual inspection for die (semiconductor diode).<br>Internal visual inspection (discrete semiconductor diodes).<br>Decap internal visual design verification.                                                                                                                                                                             |

SUPERSEDES PAGE 15 OF MIL-STD-750D

| Method no.                                                                                                                                                           | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                      | Mechanical characteristics tests (2000 series) - Continued.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *2076.3<br>2077.3<br>2081<br>2082<br>2101<br>2102                                                                                                                    | Radiography.<br>Scanning electron microscope (SEM) inspection of metallization.<br>Forward instability, shock (FIST).<br>Backward instability, vibration (BIST).<br>DPA procedures for diodes.<br>DPA procedures for wire bonded devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                      | Electrical characteristics tests for bipolar transistors (3000 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3001.1<br>3005.1<br>3011.2<br>3015<br>3020<br>3026.1<br>3030<br>3036.1<br>3041.1<br>3051<br>3052<br>3053<br>3061.1<br>3066.1<br>3076.1<br>3076.1<br>3086.1<br>3092.1 | Breakdown voltage, collector to base.<br>Burnout by pulsing.<br>Breakdown voltage, collector to emitter.<br>Drift.<br>Floating potential.<br>Breakdown voltage, emitter to base.<br>Collector to emitter voltage.<br>Collector to base cutoff current.<br>Collector to base cutoff current.<br>Collector to emitter cutoff current.<br>Safe operating area (continuous dc).<br>Safe operating area (pulsed).<br>Safe operating area (switching).<br>Emitter to base cutoff current.<br>Base emitter voltage (saturated or nonsaturated).<br>Saturation voltage and resistance.<br>Forward-current transfer ratio.<br>Static input resistance.                                                                                                                                                                                                                                                    |

| 0002.1                                                                                                                                                               | Circuit-performance and thermal resistance measurements (3100 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3101.3<br>3103<br>3104<br>*3105.1<br>3126<br>3131.2<br>3132<br>3136<br>3141<br>3146.1<br>3151<br>3161<br>3181                                                        | Thermal impedance testing of diodes.<br>Thermal impedance measurements for insulated gate bipolar transistor (delta gate-emitter on voltage method).<br>Thermal impedance measurements of GaAs MOSFET's (constant current forward-biased gate voltage method).<br>Measurement method for thermal resistance of a bridge rectifier assembly.<br>Thermal resistance (collector-cutoff-current method).<br>Thermal impedance measurements for bipolar transistors (delta base-emitter voltage method).<br>Thermal resistance (dc forward voltage drop, emitter base, continuous method).<br>Thermal resistance (forward voltage drop, collector to base, diode method).<br>Thermal resonse time.<br>Thermal time constant.<br>Thermal resistance, general.<br>Thermal impedance measurements for vertical power MOSFET's (delta source-drain voltage method).<br>Thermal resistance for thyristors. |

|                                                                                                                                                                      | Low frequency tests (3200 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3201.1<br>3206.1<br>3211<br>3216<br>3221<br>3231<br>3236<br>3240.1<br>3241                                                                                           | Small-signal short-circuit input impedance.<br>Small-signal short-circuit forward-current transfer ratio.<br>Small-signal open-circuit reverse-voltage transfer ratio.<br>Small-signal open-circuit output admittance.<br>Small-signal short-circuit input admittance.<br>Small-signal short-circuit output admittance.<br>Open circuit output capacitance.<br>Input capacitance (output open-circuited or short-circuited).<br>Direct interterminal capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                                |

SUPERSEDES PAGE 16 OF MIL-STD-750D

# Numerical index of test methods - Continued.

| Method no.                                                                                                                                                          | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                     | Low frequency tests (3200 series) - Continued.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3246.1<br>3251.1<br>3255<br>3256<br>3261.1<br>3266                                                                                                                  | Noise figure.<br>Pulse response.<br>Large signal power gain.<br>Small signal power gain.<br>Extrapolated unity gain frequency.<br>Real part of small-signal short circuit input impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                     | High frequency tests (3300 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3301<br>3306.3<br>3311<br>3320                                                                                                                                      | Small-signal short-circuit forward-current transfer-ratio cutoff frequency.<br>Small-signal short-circuit forward-current transfer ratio.<br>Maximum frequency of oscillation.<br>RF power output, RF power gain, and collector efficiency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                     | Electrical characteristics tests for MOS field-effect transistors (3400 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

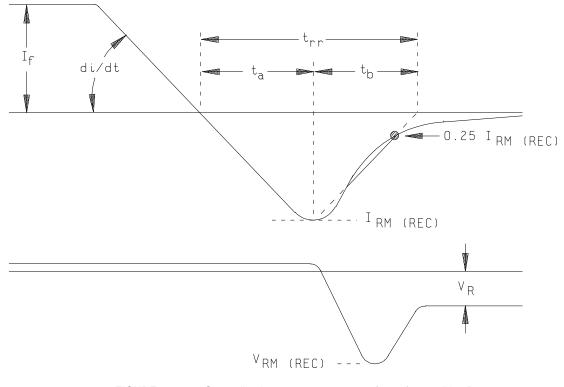

| 3401.1<br>3403.1<br>3404<br>3405.1<br>3407.1<br>3413.1<br>3413.1<br>3413.1<br>3423<br>3421.1<br>3423<br>3431<br>3433<br>3453<br>3455<br>3455<br>3455<br>3455<br>345 | Breakdown voltage, gate to source.<br>Gate to source voltage or current.<br>MOSFET threshold voltage.<br>Drain to source on-state voltage.<br>Breakdown voltage, drain to source.<br>Gate reverse current.<br>Drain current.<br>Drain reverse current.<br>Static drain to source on-state resistance.<br>Small-signal, drain to source on state resistance.<br>Small-signal, common-source, short-circuit, input capacitance.<br>Small-signal, common-source, short-circuit, reverse-transfer capacitance.<br>Small-signal, common-source, short-circuit, forward transadmittance.<br>Small-signal, common-source, short-circuit, reverse transfer admittance.<br>Small-signal, common-source, short-circuit, reverse transfer admittance.<br>Small-signal, common-source, short-circuit, input admittance.<br>Repetitive unclamped inductive switching.<br>Single pulse unclamped inductive switching.<br>Gate charge.<br>Switching time test.<br>Reverse recovery time (t <sub>rr</sub> ) and recovered charge (Q <sub>rr</sub> ) for power MOSFET (drain-to-source) and power rectifiers |

| 3474.1<br>3475.1<br>3476<br>3477.1<br>3478.1<br>3479<br>3490                                                                                                        | <ul> <li>with t<sub>rr</sub> ≤ 100 ns.</li> <li>Safe operating area for power MOSFET's or insulated gate bipolar transistors.</li> <li>Forward transconductance (pulsed dc method) of power MOSFET's or insulated gate bipolar transistors.</li> <li>Commutating diode for safe operating area test procedure for measuring dv/dt during reverse recovery of power MOSFET transistors or insulated gate bipolar transistors.</li> <li>Measurement of insulated gate bipolar transistor total switching losses and switching times.</li> <li>Power transistor electrical dose rate test method.</li> <li>Short circuit withstand time.</li> <li>Clamped inductive switching safe operating area for MOS gated power transistors.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                     | Electrical characteristics tests for Gallium Arsenide transistors (3500 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3501<br>3505<br>3510<br>3570<br>3575                                                                                                                                | Breakdown voltage, drain to source.<br>Maximum available gain of a GaAs FET.<br>1 dB compression point of a GaAs FET.<br>GaAs FET forward gain (Mag S21).<br>Forward transconductance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

REPRINTED WITHOUT CHANGE

# Numerical index of test methods - Continued.

| Method no.                                                                                                                                                                             | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                        | Electrical characteristics tests for diodes (4000 series).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

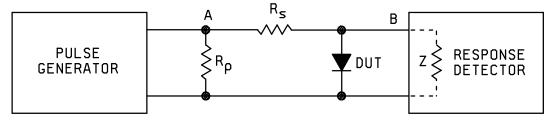

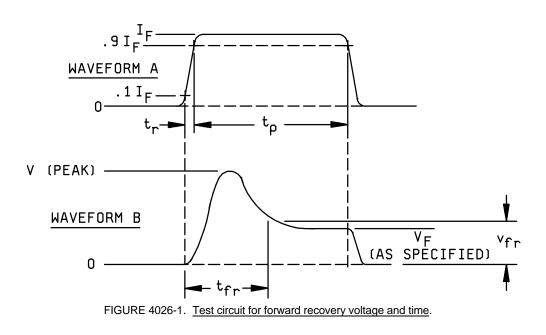

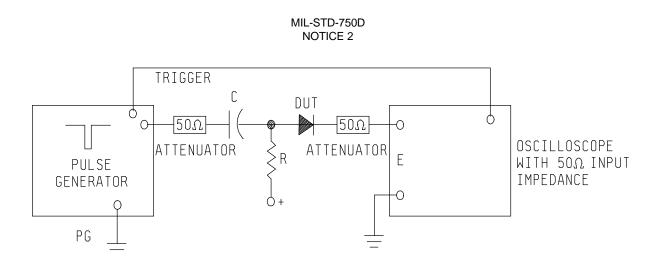

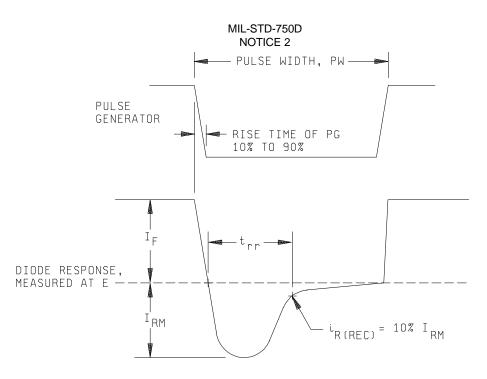

| 4000<br>4001.1<br>4011.4<br>4016.3<br>4021.2<br>4022<br>4023<br>*4026.3<br>*4031.4<br>4036.1<br>4041.2<br>4046.1<br>4051.3<br>4056.2<br>4061.1<br>4066.4<br>4071.1<br>4076.1<br>4081.2 | Condition for measurement of diode static parameters.<br>Capacitance.<br>Forward voltage.<br>Reverse current leakage.<br>Breakdown voltage (diodes).<br>Breakdown voltage (voltage regulators and voltage-reference diodes).<br>Scope display.<br>Forward recovery voltage and time.<br>Reverse recovery characteristics.<br>"Q" for voltage variable capacitance diodes.<br>Rectification efficiency.<br>Reverse current, average.<br>Small-signal reverse breakdown impedance.<br>Stored charge.<br>Surge current.<br>Temperature coefficient of breakdown voltage.<br>Saturation current.<br>Thermal resistance of lead mounted diodes (forward voltage, switching method). |

|                                                                                                                                                                                        | Electrical characteristics tests for microwave diodes (4100 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4101.3<br>4102<br>4106<br>4111.1<br>4116.1<br>4121.2<br>4126.2<br>4131.1<br>4136.1<br>4136.1<br>4141.1<br>4146.1<br>4151                                                               | Conversion loss.<br>Microwave diode capacitance.<br>Detector power efficiency.<br>Figure of merit (current sensitivity).<br>IF impedance.<br>Output noise ratio.<br>Overall noise figure and noise figure of the IF amplifier.<br>Video resistance.<br>Standing wave ratio (SWR).<br>Burnout by repetitive pulsing.<br>Burnout by single pulse.<br>Rectified microwave diode current.                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                        | Electrical characteristics tests for thyristors (controlled rectifiers) (4200 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4201.2<br>4206.1<br>4211.1<br>4216<br>4219<br>4221.1<br>4223<br>4224<br>4225<br>4226.1<br>4231.2                                                                                       | Holding current.<br>Forward blocking current.<br>Reverse blocking current.<br>Pulse response.<br>Reverse gate current.<br>Gate-trigger voltage or gate-trigger current.<br>Gate-controlled turn-on time.<br>Circuit-commutated turn-off time.<br>Gate-controlled turn-off time.<br>Gate-controlled turn-off time.<br>Forward "on" voltage.<br>Exponential rate of voltage rise.                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                        | Electrical characteristics tests for tunnel diodes (4300 series)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4301<br>4306.1<br>4316<br>4321<br>4326<br>4331                                                                                                                                         | Junction capacitance.<br>Static characteristics of tunnel diodes.<br>Series inductance.<br>Negative resistance.<br>Series resistance.<br>Switching time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

SUPERSEDES PAGE 18 OF MIL-STD-750D

- b. A new sample of devices shall be selected and subjected to the next lower voltage step used. Each device shall be tested using three positive and three negative pulses using each of the pin combinations shown in table 1020-II. A minimum of one-second delay shall separate the pulses.

- c. The sample devices shall be electrically tested to group A, subgroup II applicable (room temperature dc parameters).

- d. If one or more of the devices fail, the testing of 3.3b. and 3.3c. shall be repeated at the next lower voltage step used.

- e. If none of the devices fail, record the failure threshold determined in 3.3a. Note the highest step passed, and use it to classify the device according to table 1020-III.

| Device type                                   | Junction/polarity         |

|-----------------------------------------------|---------------------------|

| Bipolar transistor (NPN)                      | E+ to B-                  |

| Bipolar transistor (PNP)                      | E- to B+                  |

| Junction FET's (N-channel)                    | G+ to S-                  |

| Junction FET's (P-channel)                    | G- to S+                  |

| MOSFET's (N- or P-channel)                    | G to S (both polarities)  |

| Gate protected FET's (P-channel)              | G to S (both polarities)  |

| Rectifiers (include hot carrier and schottky) | A- to K+                  |

| Thyristors                                    | G to K (both polarities)  |

| Unijunctions                                  | G to B1 (both polarities) |

| Darlingtons                                   | E to B (both polarities)  |

| Small signal diodes                           | A to K (both polarities)  |

TABLE 1020-II. Junction polarities for ESD conditions test.

#### 3.4 Pin combinations to be tested.

Using table 1020-II, select the terminal to be used for the ESD tests.

| TABLE 1020-III. | Device ESD failure threshold classification. |

|-----------------|----------------------------------------------|

|                 |                                              |

| Class 1      | 0 volt to 1,999 volts       |

|--------------|-----------------------------|

| Class 2      | 2,000 volts to 3,999 volts  |

| Class 3      | 4,000 volts to 15,999 volts |

| Nonsensitive | Above 15,999 volts          |

# 3.5 Classification criteria.

Devices which fail the post test electrical at +25°C of group A, subgroup 2 of the detail specification shall be considered class 1 devices.

All devices subjected to this test shall be considered destroyed and shall not be shipped for use in any application.

SUPERSEDES PAGE 3 OF MIL-STD-750D

4. <u>Summary</u>. The following details shall be specified in the applicable purchase order or contract, if other than specified herein.

- a. Post test electricals.

- b. Special additional or substitute pin combinations, if applicable.

- c. Sample size, if other than three devices.

REPRINTED WITOUT CHANGE

METHOD 1020.2

#### METHOD 2037

#### BOND STRENGTH

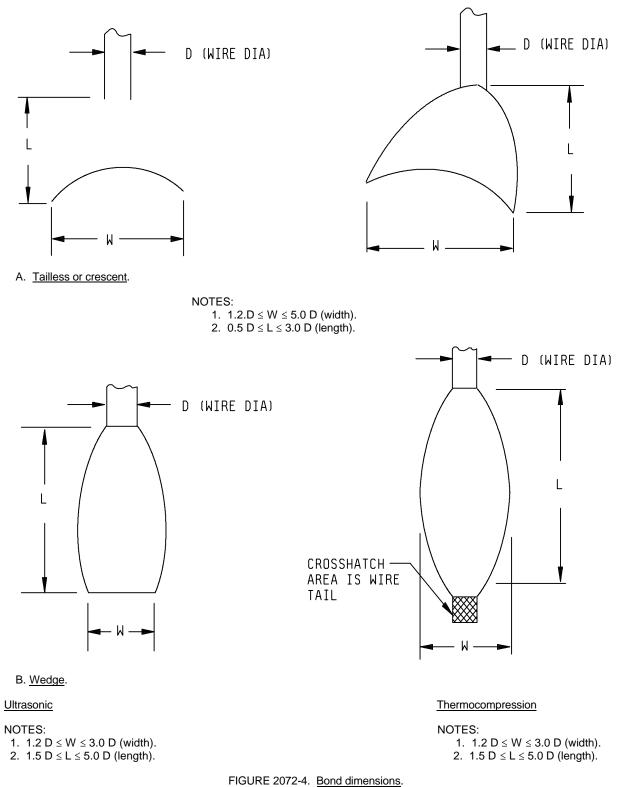

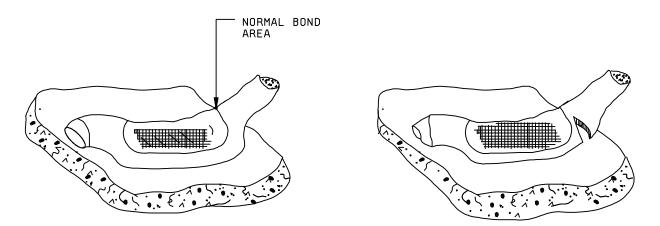

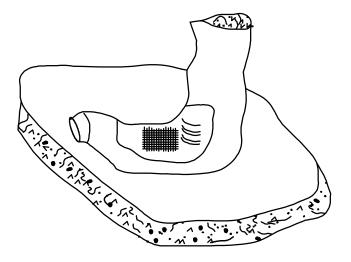

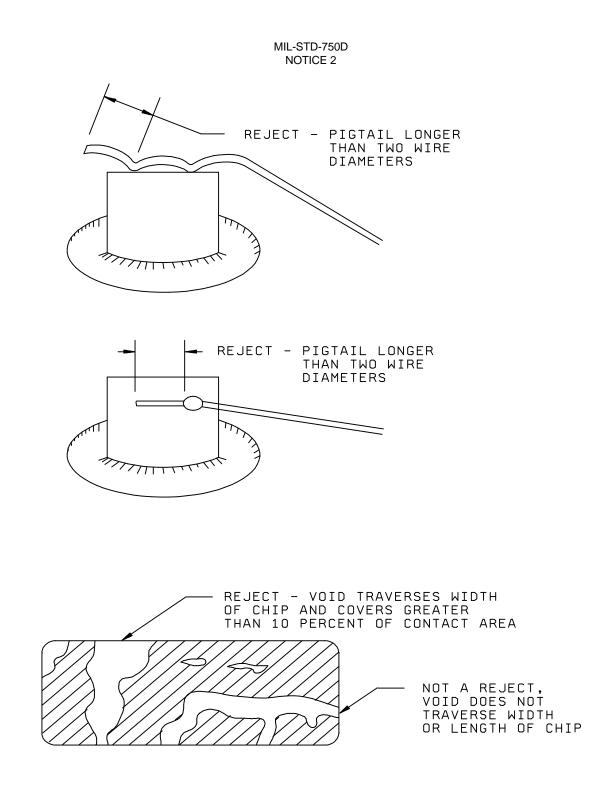

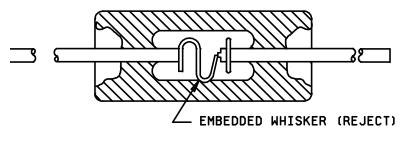

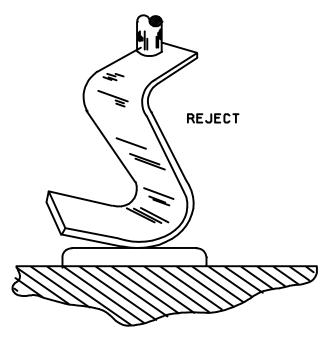

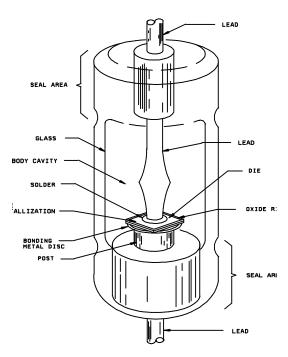

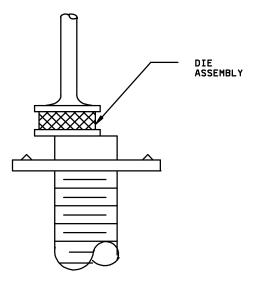

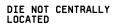

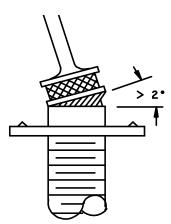

1. <u>Purpose</u>. The purpose of this test is to measure bond strengths to determine compliance with specified requirements of the applicable detail specification. This test may be applied to wire-to-die or clip-to-die bond, wire-to-package lead bond, or the wire-to-substrate bond inside the package of wire or clip connected discrete devices bonded by soldering, thermocompression, ultrasonic or related techniques.

2. <u>Apparatus</u>. The apparatus for this test shall consist of suitable equipment for applying the specified force required to cause bond failure. A measurement of the applied stress in grams force (gf) at the point of failure shall be provided by equipment capable of measuring stresses up to and including 10 gf with an accuracy of  $\pm 0.25$  gf, stresses between 10 and 50 gf with an accuracy of  $\pm 0.5$  gf, and stresses exceeding 50 gf with an accuracy of 5 percent of indicated value.

3. <u>Procedure</u>. The test shall be conducted using the test conditions specified. All bond pulls shall be counted and the specified sampling, acceptance and added sample provisions shall be observed, as applicable. Unless otherwise specified, the sample plan specified for the bond strength test shall determine the minimum sample size in terms of the minimum number of pulls to be accomplished rather than the number of complete devices in the sample (e.g., wires for test condition A, bonds for test condition B, and clips for test condition C). Where there is any adhesive, encapsulant, or other material used on the die to increase the apparent bond strength, the bond strength test shall be performed prior to application or, for post seal tests, the material shall be removed. Unless nondestructive limits are specified, all bond pulls shall be to destruction.

# 3.1 Test conditions.

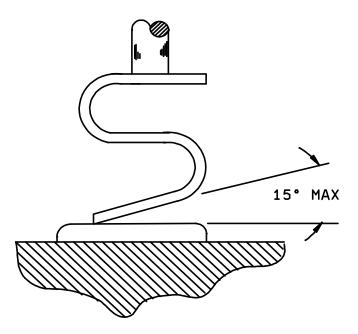

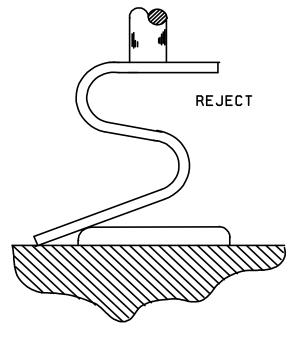

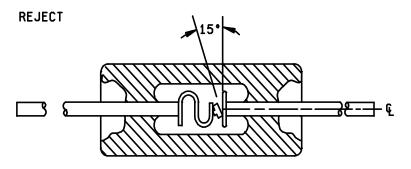

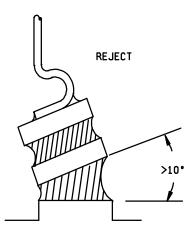

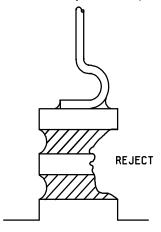

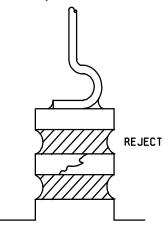

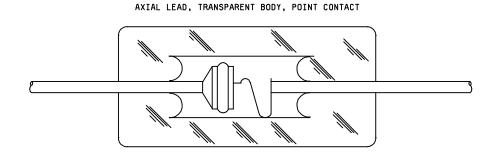

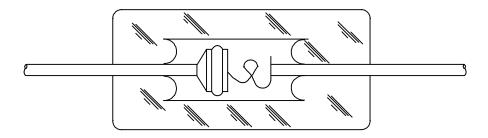

3.1.1 <u>Test condition A: Wire pull, double bond</u>. This test is normally employed for internal bonds at the die or substrate and the lead posts of discrete devices. Under this condition, both bonds are tested simultaneously by inserting a hook under the lead wire and, with the device clamped, applying the pulling force at mid-point of the wire span. The force shall be applied in the upward direction tending to cause a lift-off separation of the bond from the die and within 5° of perpendicular to: (1) the plane of the die or substrate or, (2) to a straight line between the two bonds. When a failure occurs, the force causing the failure and the failure category shall be recorded.

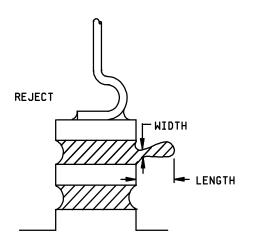

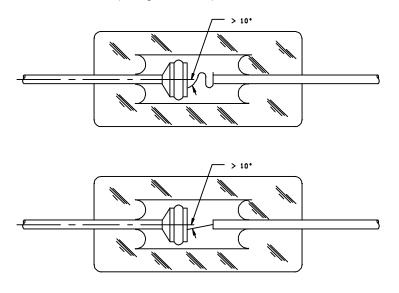

3.1.2 Test condition B: Wire pull, single bond (not recommended for wire diameters less than .005 inch (0.125 mm)). This test is employed when it is desired to test the wire bonds separately at the die or substrate and lead post or when, due to device construction, condition A is inappropriate. Product acceptance is based on testing an equal number of both bonds. When testing die and post bonds separately, the wire shall be cut to provide two ends accessible for pull testing both die and post bonds. In the case of short wire runs, it may be necessary to cut the wire close to one termination in order to allow pull at the opposite termination. The free end of the wire shall be gripped in a suitable device and simple pulling action applied. When the wire exits from the top of the die bond (ball or nailhead bonds), the force shall be applied in a direction that is within 5° of normal to the surface of the die or substrate. When the wire exits from the side of the bond (die or lead post), the force shall be applied at an angle equal to or greater than 45° to the surface of the die. When failure occurs, the force causing the failure and failure category shall be recorded.

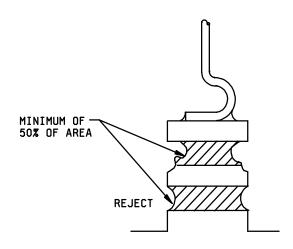

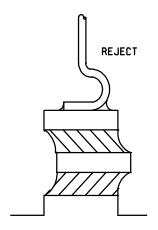

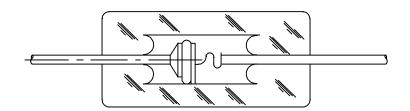

3.1.3 <u>Test condition C: Clip pull</u>. This test is employed for internal clips at the die or substrate and the lead posts of discrete devices. The pull is applied by inserting a hook under the clip as close to the die attachment point as practical with the device clamped and the pulling force applied approximately in a direction within 5° of normal to the die or substrate. When a failure occurs, the force causing the failure and the failure category shall be recorded.

3.2 <u>Failure criteria</u>. Any bond pull which results in a separation under an applied stress less than that indicated in table 2036.1 as the required minimum bond strength for the indicated test condition, composition, and construction shall constitute a failure.

3.2.1 Failure category.

REPRINTED WITOUT CHANGE

METHOD 2037

- 3.2.1.1 Failure categories for wire bonds. Failure categories for wire bonds are as follows:

- a. Wire break at neckdown point (reduction of cross section due to bonding process).

- b. Wire break at point other than neckdown.

- c. Failure in bond (interface between wire and metallization at die).

- d. Failure in bond (interface between wire and plating or metallization) at package post, substrate, or other than at the die.

- e. Lifted metallization from die.

- f. Lifted metallization or plating from substrate or package post.

- g. Fracture of die.

- h. Fracture of substrate.

- 3.2.1.2 Failure categories for clips. Failure categories for clip are as follows:

- a. Failure in bond (interface between clip and metallization) at die.

- b. Lifted metallization at die.

- c. Separation of clip from package post.

- d. Fracture of die.

The stress required to achieve separation and the category of the separation or failure shall be recorded.

3.3 <u>Procedure in the event of production sampling failure (unencapsulated devices)</u>. If a sample contains more than the allowed number of defects, the machine(s) from which the sample was taken shall not be allowed to produce additional JAN product until a sample has been tested and passed. All devices bonded on the machine(s) that produced the defective(s) since the last acceptable sample inspection will either be rejected or subjected to a 100 percent non-destructive bond pull at a force of one-half the minimum specified bond pull limit for the particular size wire (see table 2037-I or figure 2037-I). A non-destructive pull force of X - 30  $\sigma/2$  may be substituted for this value provide  $\sigma \le 0.2 X$ . The statistical data for this shall be obtained from actual pull data from the last full acceptable days production. X is the average pull strength and  $\sigma$  is the standard deviation. If 99.999 percent pure aluminum annealed wire is used, the divisor in the equation shall be changed to three and the sentence above will then read "one-third the minimum specified bond pull limit." This procedure shall not be used if the defectives resulted from die fracture since this may indicate damage to the die which cannot be screened by non-destructive testing.

- 4. <u>Summary</u>. The following details shall be specified in the detail specification:

- a. Test condition letter (see 3.).

- b. Minimum bond strength, if other than as specified in 3.2 or details of required strength distributions, if applicable.

- c. LTPD or number and selection of bond pulls to be tested on each device, and number of devices, if other than 10.

- d. Requirements for reporting of separation forces and failure categories, when applicable (see 3.2.1).

SUPERSEDES PAGE 2 OF MIL-STD-750D

METHOD 2037

## METHOD 1001.2

#### BAROMETRIC PRESSURE (REDUCED)

1. <u>Purpose</u>. The purpose of this test is to check the device capabilities under conditions simulating the low pressure encountered in the nonpressurized portions of aircraft in high altitude flight.

2. <u>Apparatus</u>. The apparatus used for the barometric-pressure test shall consist of a vacuum pump and a suitable sealed chamber having means for visual observation of the specimen under test when necessary. A suitable pressure indicator shall be used to measure the simulated altitude in feet in the sealed chamber.

3. <u>Procedure</u>. The specimens shall be mounted in the test chamber as specified and the pressure reduced to the value indicated in one of the following test conditions, as specified. Previous references to this method do not specify a test condition; in such cases, test condition B shall be used. While the specimens are maintained at the specified pressure, and after sufficient time has been allowed for all entrapped air in the chamber to escape, the specimens shall be subjected to the specified test.

| Test condition | Pressure                 | - Maximum               | Altitude |         |

|----------------|--------------------------|-------------------------|----------|---------|

|                | Inches of mercury        | Millimeters of mercury  | Feet     | Meters  |

| A              | 8.88                     | 226.00                  | 30,000   | 9,144   |

| В              | 3.44                     | 87.00                   | 50,000   | 15,240  |

| C              | 1.31                     | 33.00                   | 70,000   | 21,336  |

| D              | 0.315                    | 8.00                    | 100,000  | 30,480  |

| E              | 0.043                    | 1.09                    | 150,000  | 45,720  |

| F              | 17.300                   | 439.00                  | 15,000   | 4,572   |

| G              | 9.436 X 10 <sup>-8</sup> | 2.40 X 10 <sup>-6</sup> | 656,000  | 200,000 |

In addition the following is required:

- a. Twenty minutes before and during the test, the test temperature shall be +25°C ±3°C.

- b. The specified voltage shall be applied and monitored over the range from atmospheric pressure to the specified minimum pressure and returned so that any device malfunctions, if they exist, will be detected.

4. <u>Failure criteria</u>. A device which exhibits arc-overs, harmful coronas, or any other defect or deterioration that may interfere with the operation of the device shall be considered a failure.

- 5. <u>Summary</u>. The following conditions must be specified in the detail specification:

- a. Voltage (see 2.).

- b. Minimum pressure (see 2.).

#### METHOD 1011.1

#### **IMMERSION**

1. <u>Purpose</u>. This test is performed to determine the effectiveness of the seal of component parts. The immersion of the part under evaluation into liquid at widely different temperatures subjects it to thermal and mechanical stresses which will readily detect a defective terminal assembly, or a partially closed seam or molded enclosure. Defects of these types can result from faulty construction or from mechanical damage such as might be produced during physical or environmental tests. The immersion test is generally performed immediately following such tests because it will tend to aggravate any incipient defects in seals, seams, and bushings which might otherwise escape notice. This test is essentially a laboratory test condition, and the procedure is intended only as a measurement of the effectiveness of the seal following this test. The choice of fresh or salt water as a test liquid is dependent on the nature of the component part under test. When electrical measurements are made after immersion cycling to obtain evidence of leakage through seals, the use of a salt solution instead of fresh water will facilitate detection of moisture penetration. This test provides a simple and ready means of detection of the migration of liquids. Effects noted can include lowered insulation resistance, corrosion of internal parts, and appearance of salt crystals. The test described is not intended as a thermal-shock or corrosion test, although it may incidentally reveal inadequacies in these respects.

2. <u>Procedure</u>. The test consists of successive cycles of immersions, each cycle consisting of immersion in a hot bath of fresh (tap) water at a temperature of  $65^{\circ}C + 5^{\circ}C, -0^{\circ}C$  (149°F +9°F,  $-0^{\circ}F$ ) followed by immersion in a cold bath. The number of cycles, duration of each immersion, and the nature and temperature of the cold bath shall be as indicated in the applicable test condition listed in table 1011-1, as specified.

| Test Condition | Number of cycles | Duration of each<br>immersion<br>(Minutes) | Immersion bath (cold)                            | Temperature of cold bath<br>(°C) |

|----------------|------------------|--------------------------------------------|--------------------------------------------------|----------------------------------|

| A              | 2                | 15                                         | Fresh (tap) water                                | 25, +10, -5                      |

| В              | 2                | 15                                         | Saturated solution of sodium chloride and water. | 25, +10, -5                      |

| C              | 5                | 60                                         | Saturated solution of sodium chloride and water. | 0 ± 3                            |

The transfer of specimens from one bath to another shall be accomplished as rapidly as practicable. After completion of the final cycle, specimens shall be thoroughly and quickly washed and all surfaces wiped or air-blasted clean and dry.

3. <u>Measurements</u>. Unless otherwise specified, measurements shall be made at least 4 hours, but not more than 24 hours, after completion of the final cycle. Measurements shall be made as specified.

- 4. <u>Summary</u>. The following details are to be specifed in the individual specification:

- a. Test condition letter (see 2).

- b. Time after final cycle allowed for measurements, if other than that specified (see 3).

- c. Measurements after final cycle (see 3).

#### METHOD 1015.1

## STEADY-STATE PRIMARY PHOTOCURRENT IRRADIATION PROCEDURE (ELECTRON BEAM)