The documentation and process conversion measures necessary to comply with this revision shall be completed by 6 July 2018.

INCH-POUND

MIL-STD-750-2A w/CHANGE 3 <u>7 February 2018</u> SUPERSEDING MIL-STD-750-2A w/CHANGE 2 19 August 2016 (see 6.4)

# DEPARTMENT OF DEFENSE TEST METHOD STANDARD MECHANICAL TEST METHODS FOR SEMICONDUCTOR DEVICES PART 2: TEST METHODS 2001 THROUGH 2999

# FOREWORD

- 1. This standard is approved for use by all Departments and Agencies of the Department of Defense.

- 2. This subpart standard establishes uniform test methods for the mechanical testing to determine resistance to deleterious effects of natural elements and conditions surrounding military operations.

- 3. Comments, suggestions, or questions on this document should be addressed to: Commander, Defense Logistics Agency, DLA Land and Maritime, ATTN: VAC, P.O. Box 3990, Columbus, OH 43218–3990, or emailed to 750.TestMethods@dla.mil. Since contact information can change, you may want to verify the currency of this address information using the ASSIST Online database at https://assist.dla.mil.

# SUMMARY OF REVISION A WITH CHANGE 3 MODIFICATIONS

- 1. Test method 2068, entire method was rewritten extensively to clarify existing and add new requirements.

- 2. Test method 2071, renumbered eleven paragraphs under failure criteria.

- 3. Test method 2071, paragraph 4.2, reorganized subparagraphs and add new subparagraph to add new failure criteria.

- 4. Test method 2071, paragraph 4.4, changed paragraph title.

- 5. Test method 2071, paragraph 4.5.f, delete "shard or" and replace with "sharp or unspecified".

- 6. Test method 2071, paragraph 4.10, deleted duplicate sentence.

- 7. Test method 2101, table 2101–II, footnote 3; added two new sentences to define high and low voltage diodes.

- 8. The following modifications to MIL–STD–750–2 have been made:

| Test method | <u>Paragraph</u>          | <b>Modification</b> |

|-------------|---------------------------|---------------------|

| 2068        | All                       | Revised entirely    |

| 2071        | 4.2                       | Revised.            |

| 2071        | 4.4                       | Revised.            |

| 2071        | 4.5.f                     | Revised.            |

| 2071        | 4.10                      | Revised.            |

| 2101        | Table 2101–II, footnote 3 | Revised.            |

# CONTENTS

| PARAGRA | <u>PH</u> <u>PAGE</u>                     |

|---------|-------------------------------------------|

| FORWARI | D                                         |

| 1.      | SCOPE                                     |

| 1.1     | Purpose1                                  |

| 1.2     | Numbering system1                         |

| 1.2.1   | Classification of tests                   |

| 1.2.2   | Test method revisions                     |

| 1.3     | Methods of reference1                     |

| 2.      | APPLICABLE DOCUMENTS                      |

| 2.1     | General1                                  |

| 2.2     | Government documents1                     |

| 2.2.1   | Specifications, standards, and handbooks1 |

| 2.3     | Non-Government publications2              |

| 2.4     | Order of precedence                       |

| 3.      | DEFINITIONS                               |

| 3.1     | Acronyms, symbols, and definitions        |

| 3.2     | Acronyms used in this standard            |

| 4.      | GENERAL REQUIREMENTS                      |

| 4.1     | General4                                  |

| 4.2     | Test circuits                             |

| 4.3     | Destructive tests4                        |

| 4.4     | Non-destructive tests                     |

| 4.5     | Laboratory suitability5                   |

| 5.      | DETAILED REQUIREMENTS                     |

| 6.      | NOTES                                     |

| 6.1     | Intended use5                             |

| 6.2     | International standardization agreement6  |

| 6.3     | Subject term (key word) listing           |

| 6.4     | Supersession data                         |

| 6.5     | Change notations                          |

| CONCLUE | DING MATERIALC-1                          |

# CONTENTS

|               | CONTENTS                                                                                  |

|---------------|-------------------------------------------------------------------------------------------|

| <b>FIGURE</b> | TITLE                                                                                     |

|               |                                                                                           |

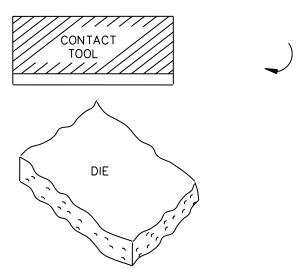

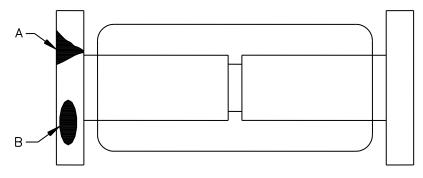

| 2017–1        | Uniform force distribution                                                                |

| 2017-2        | Rotational capability                                                                     |

| 2017–3        | Perpendicular force application                                                           |

| 2017–4        | Die shear strength criteria                                                               |

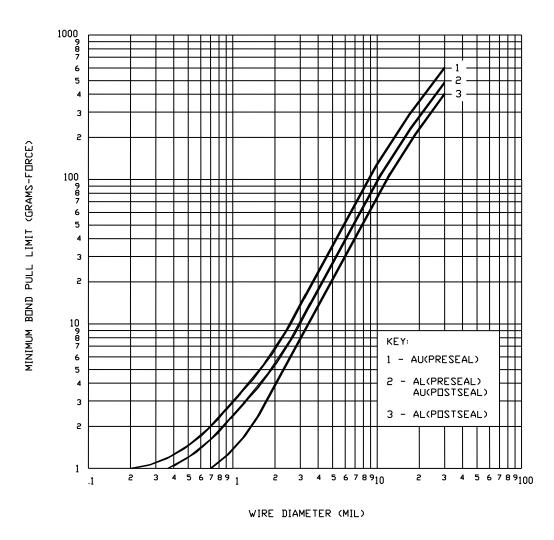

| 2037–1        | Minimum bond pull limits                                                                  |

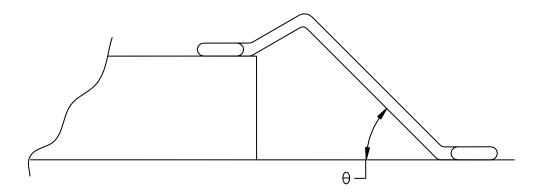

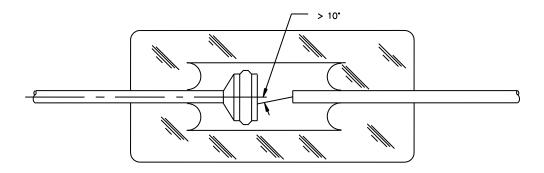

| 2037–2        | Wire loop angle                                                                           |

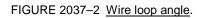

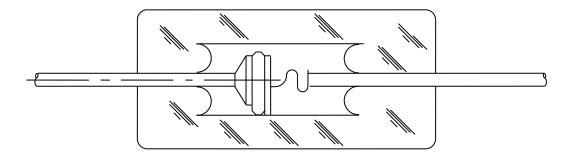

| 2037–3        | Flat loop wire pull testing                                                               |

| 2037-3        | Sample apparatus fixture with force measuring gauge                                       |

| 2038-2        |                                                                                           |

|               | Close up view of sample apparatus fixture                                                 |

| 2038-3        | Condition B                                                                               |

| 2038–4        | Condition C                                                                               |

| 2038-5        | Condition D                                                                               |

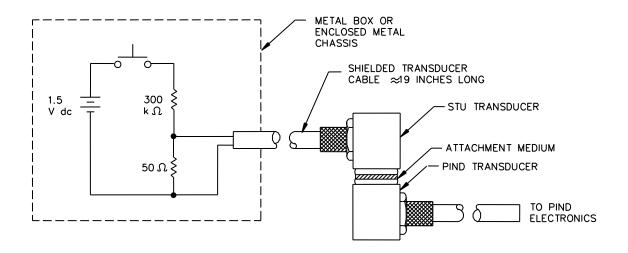

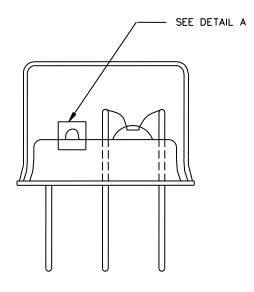

| 2052–1        | Typical STU                                                                               |

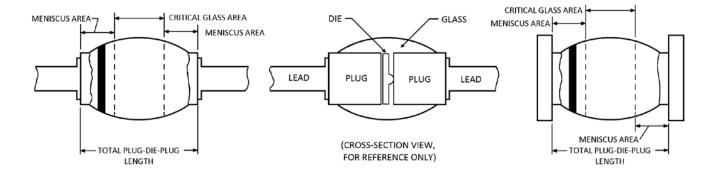

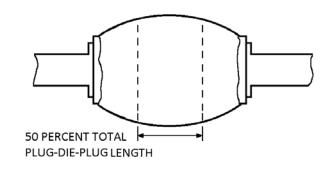

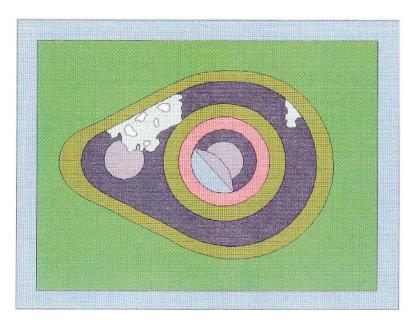

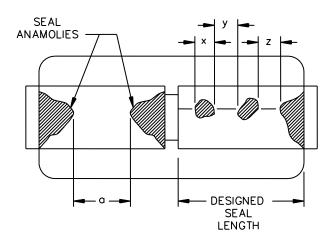

| 2068–1        | Critical glass and meniscus areas for nontransparent glass, double plug, noncavity diodes |

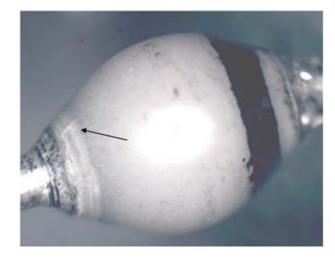

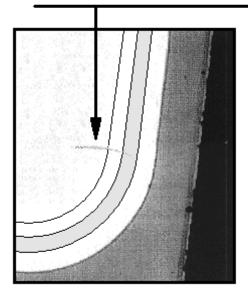

| 2068–2        | Acceptable body glass cracks                                                              |

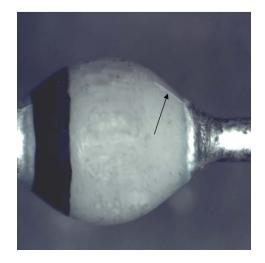

| 2068–3        | Unacceptable body glass cracks                                                            |

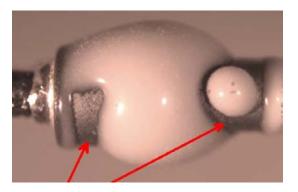

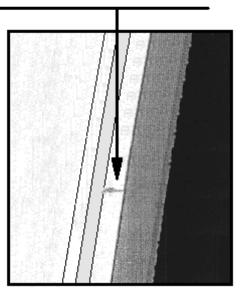

| 2068–4        | Acceptable body glass coverage                                                            |

| 2068–5        | Unacceptable body glass coverage                                                          |

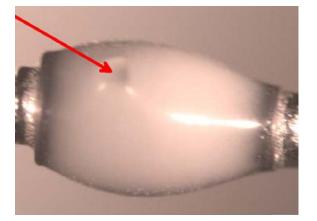

| 2068–6        | Acceptable depression                                                                     |

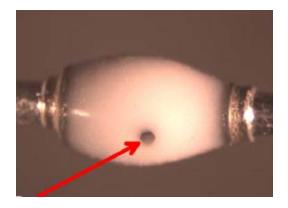

| 2068–7        | Unacceptable void                                                                         |

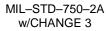

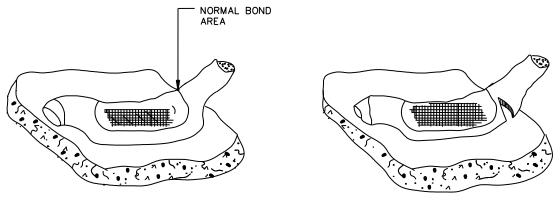

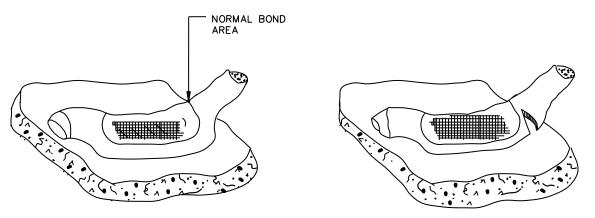

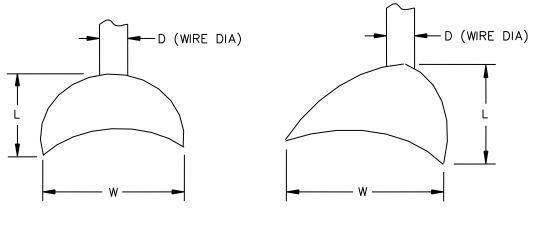

| 2069–1        | Bond dimensions                                                                           |

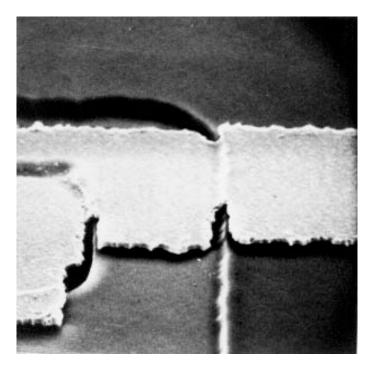

| 2069–2        | Torn bonds                                                                                |

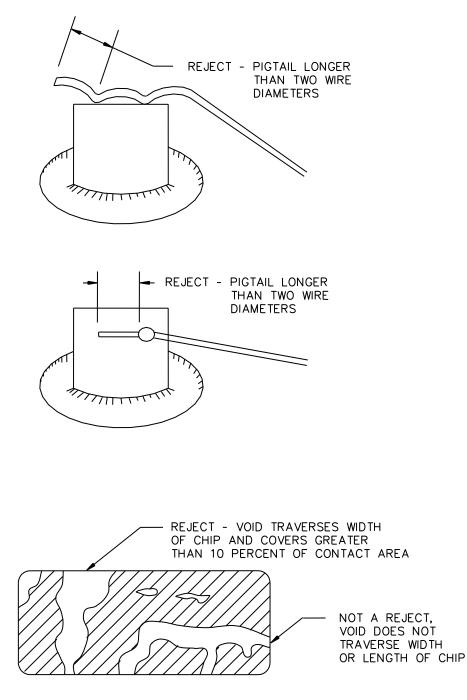

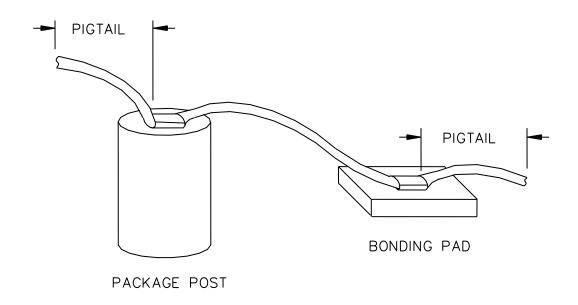

| 2069–3        | Acceptable and unacceptable voids and excessive pigtails                                  |

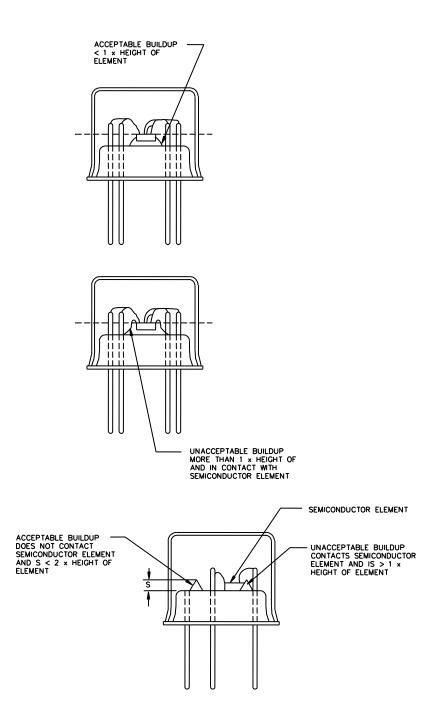

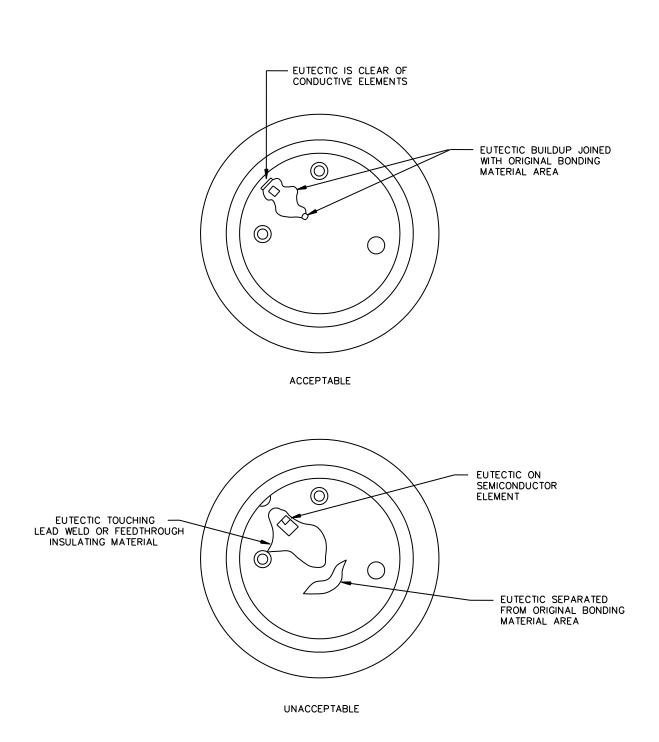

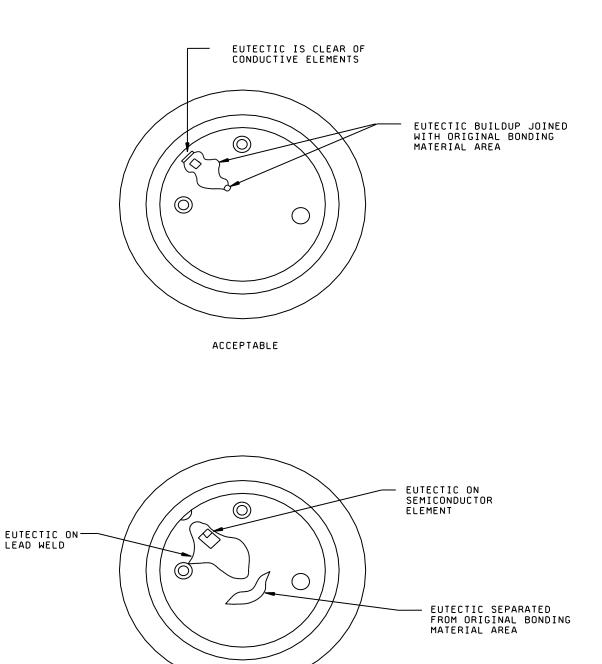

| 2069–4        | Acceptable and unacceptable bonding material build-up                                     |

| 2069–5        | Extraneous bonding material build-up                                                      |

| 2069–6        | Acceptable and unacceptable excess material                                               |

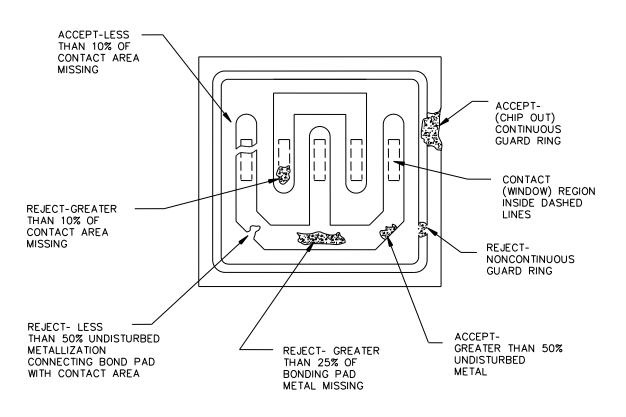

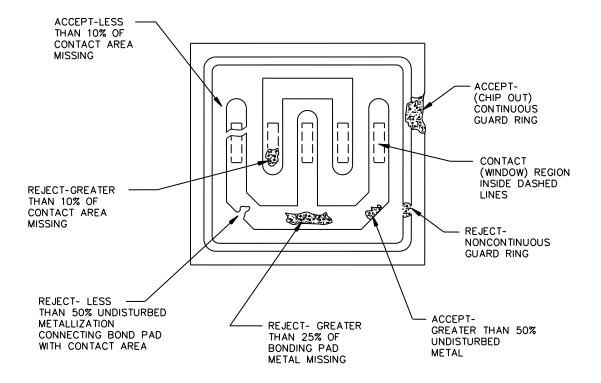

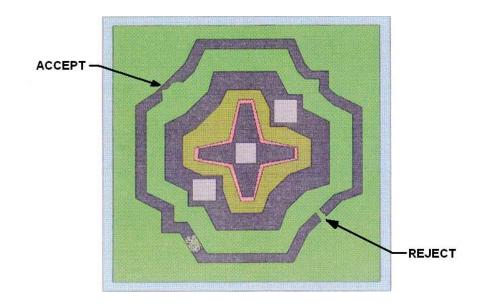

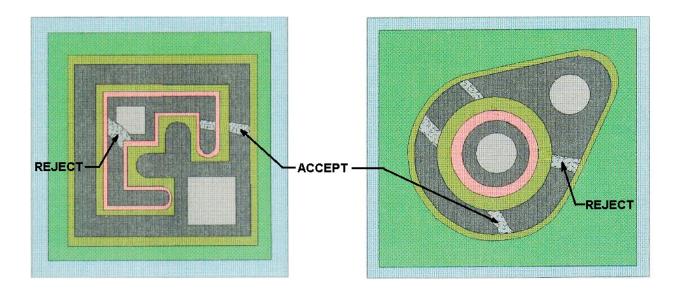

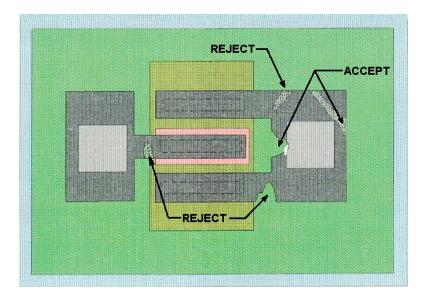

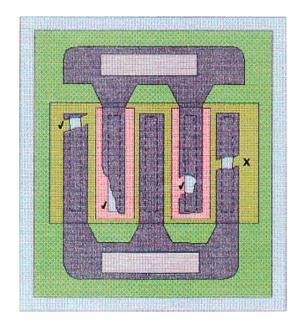

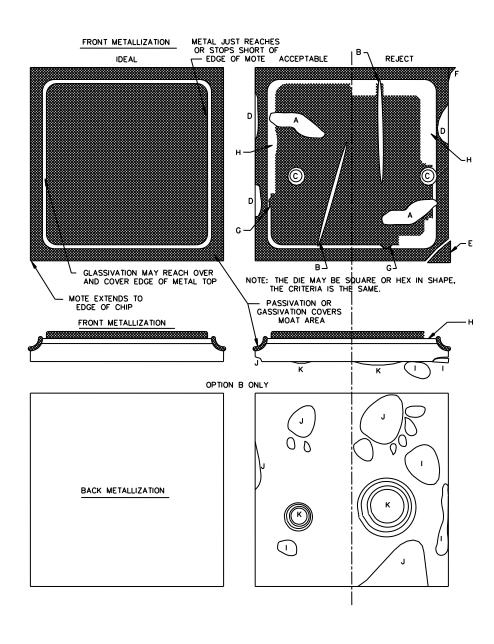

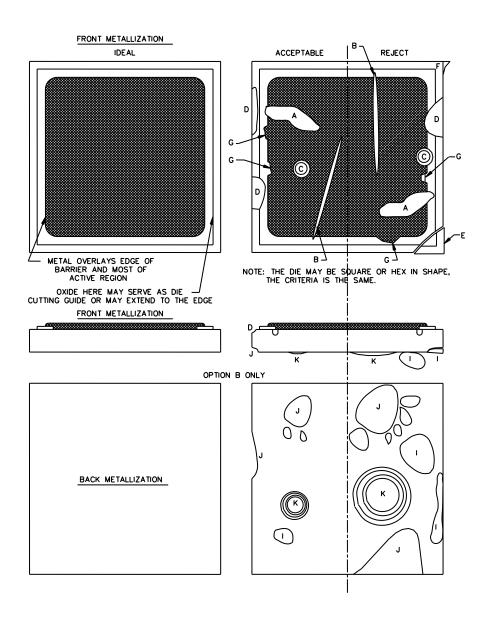

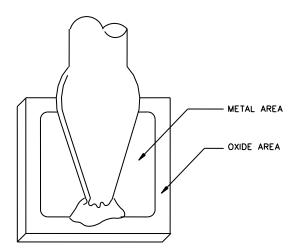

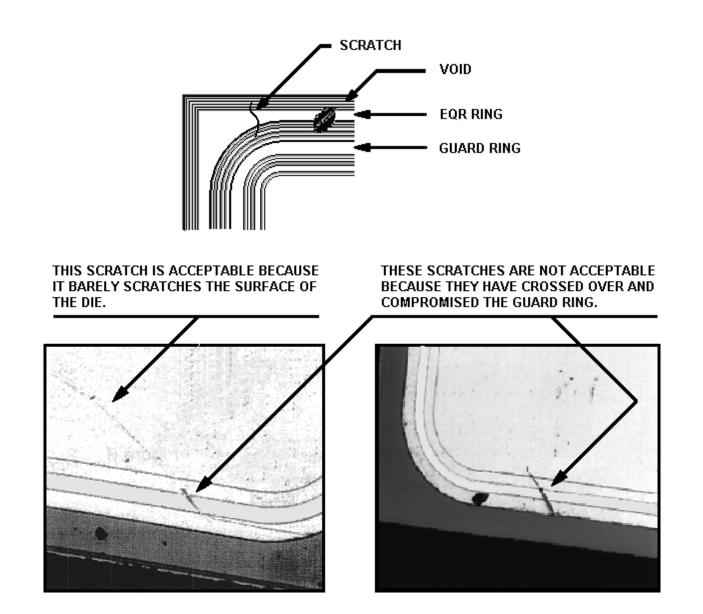

| 2070–1        | Metallization scratches and voids (expanded contact)                                      |

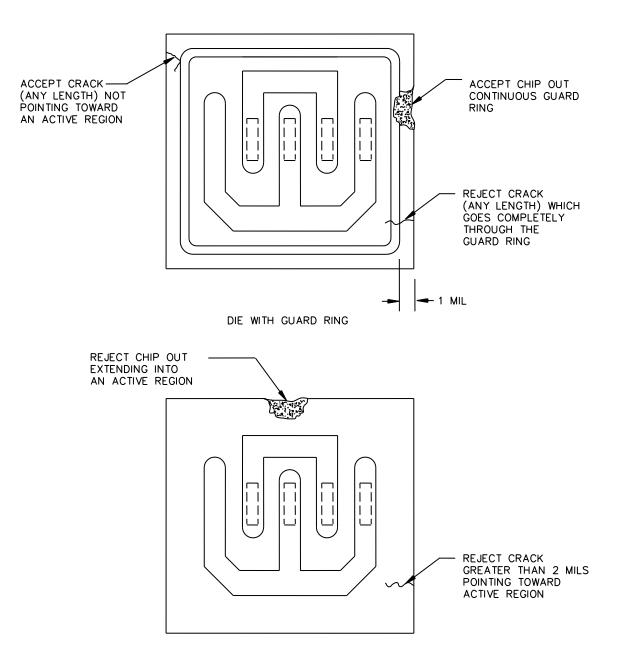

| 2070–2        | Cracks and chips                                                                          |

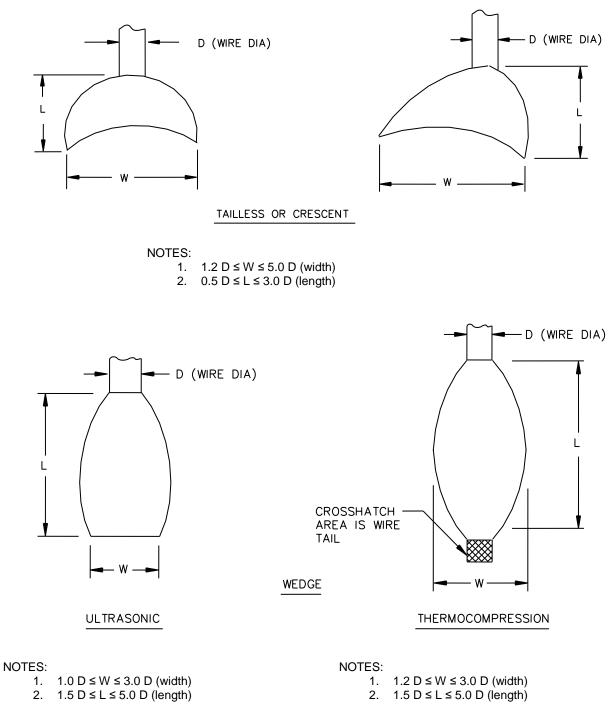

| 2070–3        | Bond dimensions                                                                           |

| 2070–4        | Lifted or torn bonds                                                                      |

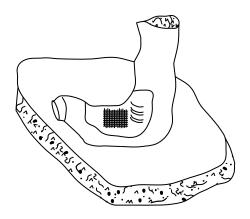

| 2070–5        | Mesh geometry                                                                             |

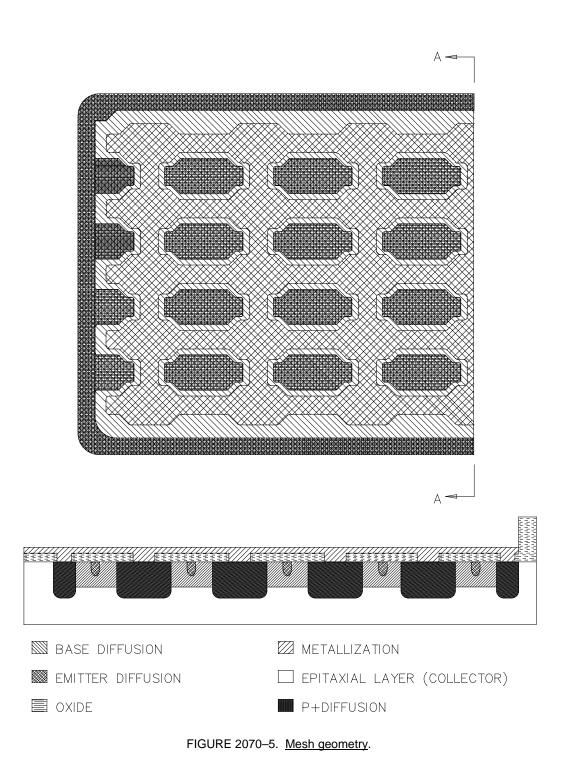

| 2070–6        | Interdigitated geometry                                                                   |

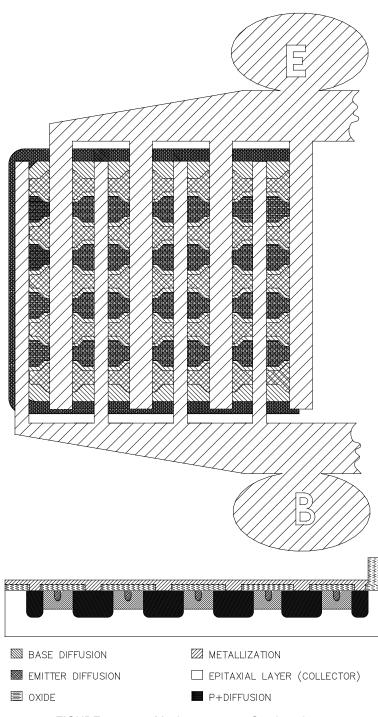

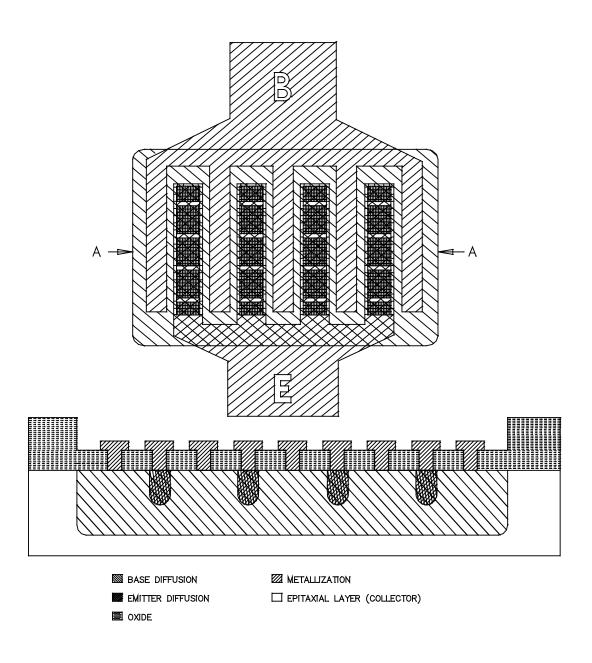

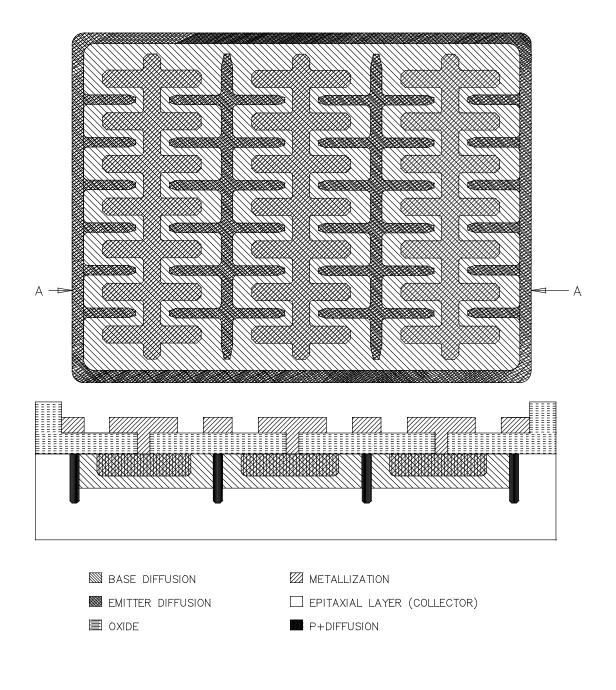

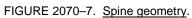

| 2070–7        | Spine geometry                                                                            |

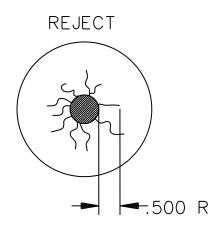

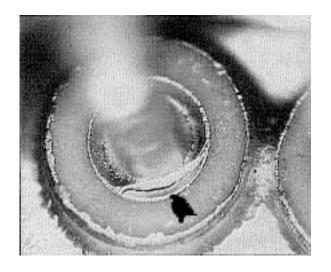

| 2071–1        | Radial cracks extending more than one-half the distance from pin to outer member          |

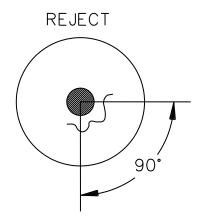

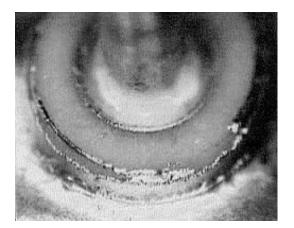

| 2071–2        | Circumferential cracks                                                                    |

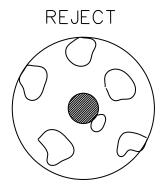

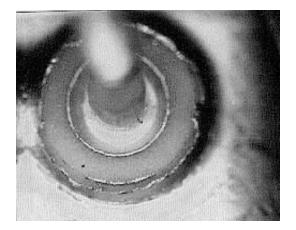

| 2071–3        | Bubbles in glass exceeding one-third of the sealing area                                  |

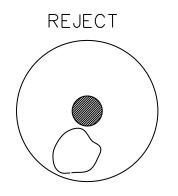

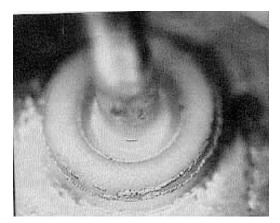

| 2071–4        | Single bubble or void                                                                     |

| 2071–5        | Two bubbles in a line                                                                     |

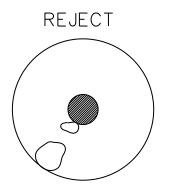

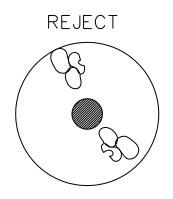

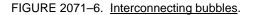

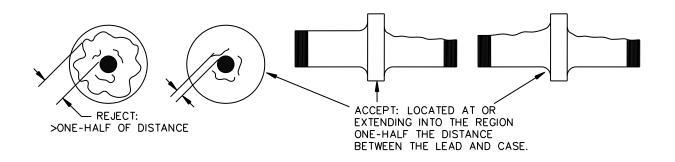

| 2071-6        | Interconnecting bubbles                                                                   |

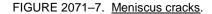

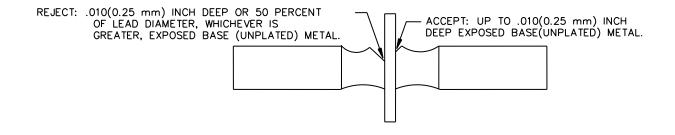

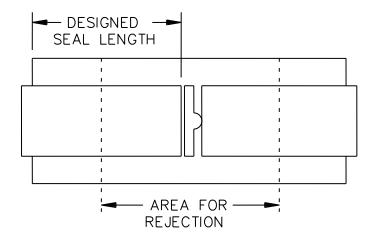

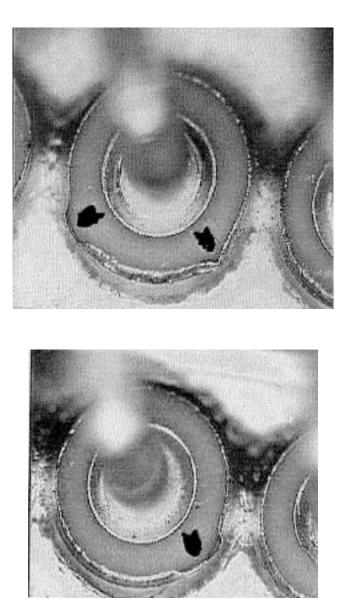

| 2071–7        | Meniscus cracks                                                                           |

| 2071-8        | Chip outs                                                                                 |

| 2071–9        | Transparent glass diode                                                                   |

| 2071–10       | Braze separation/delamination                                                             |

| 2071–11       | Crack in braze metallization                                                              |

| 2071–12       | Discontinuous braze metallization                                                         |

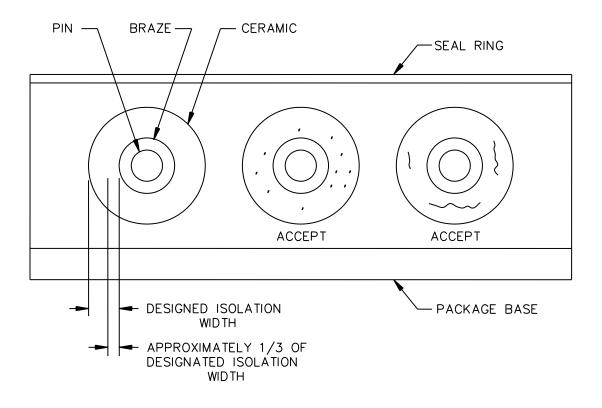

| 2071-13       | Ceramic feedthrough visual inspection criteria                                            |

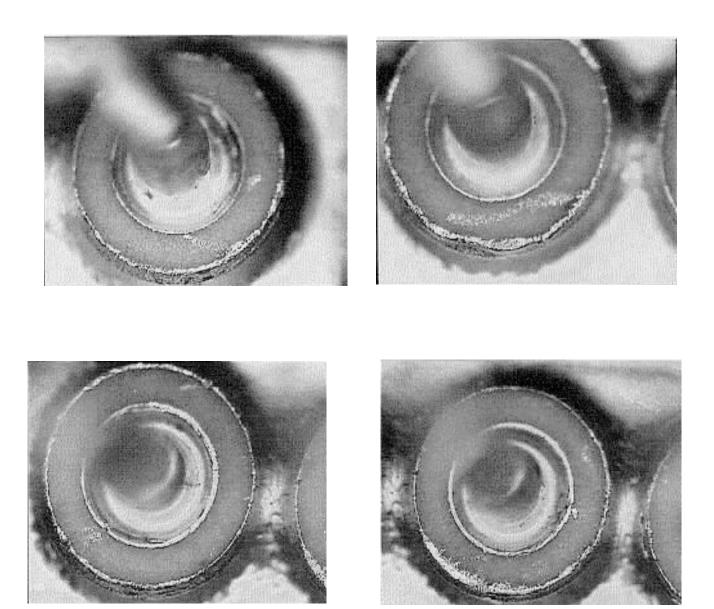

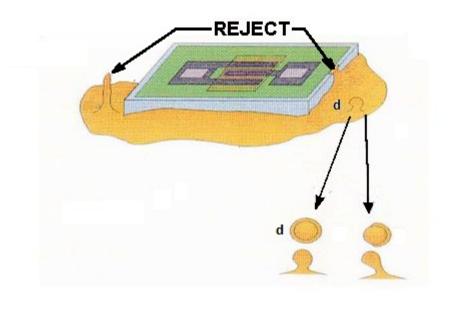

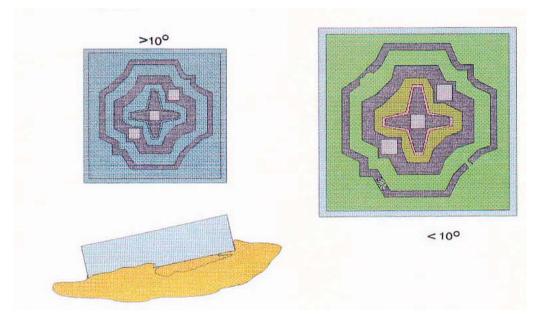

| 2071-14       | Rejectable foreign material conditions                                                    |

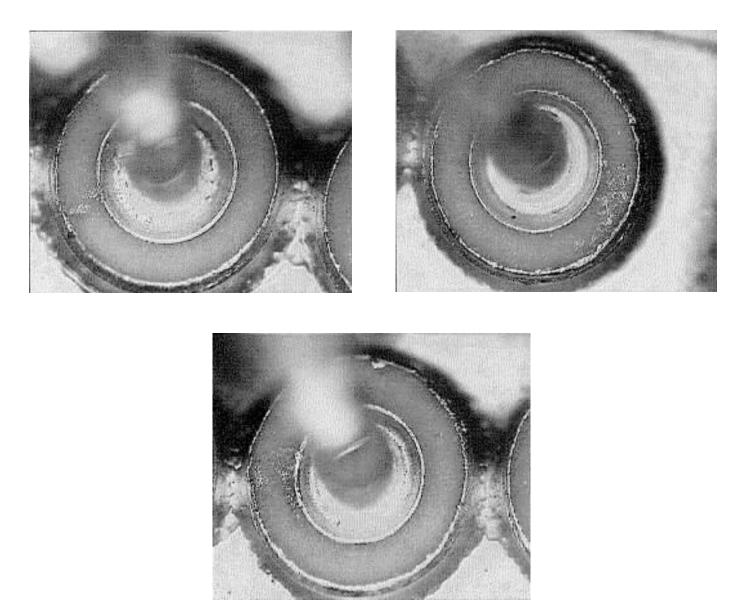

| 2071-15       | Plug to terminal interface depicting acceptable filler metal                              |

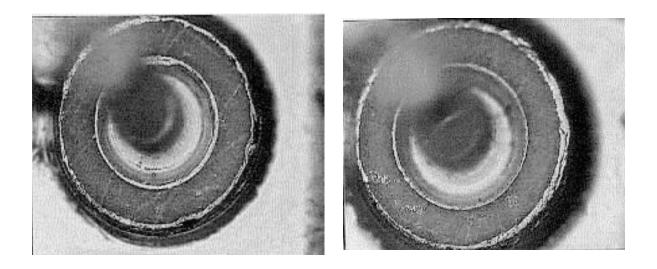

| 2071-16       | Plug to terminal interface depicting acceptable filler metal                              |

| -             |                                                                                           |

# CONTENTS

**FIGURE**

<u>TITLE</u>

| <u></u>            |                                                                                                                               |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 2072–1             | Metallization scratches, probe marks and voids                                                                                |

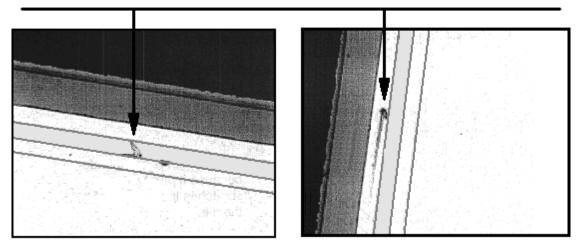

| 2072-2             | Innermost guard band metallization scratches, probe marks and voids                                                           |

| 2072-3             | Active region metallization scratches, probe marks and voids                                                                  |

| 2072-4             | Pad and contact metallization scratches, probe marks and voids                                                                |

| 2072-5             | Contact metallization scratches, probe marks and voids                                                                        |

| 2072-6             | Metallization probing damage                                                                                                  |

| 2072-7             | Metallization bridging between two normally unconnected metallization areas                                                   |

| 2072-8             | Metallization bridging between two normally unconnected metallization areas                                                   |

| 2072-9             | Metallization bridging between two normally unconnected metallization paths<br>Metallization misalignment, cross section view |

| 2072-10            | Metallization misalignment                                                                                                    |

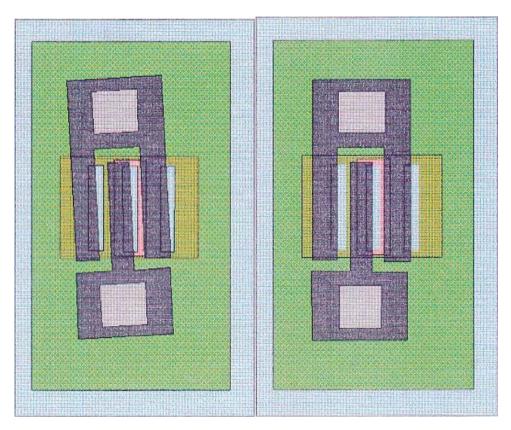

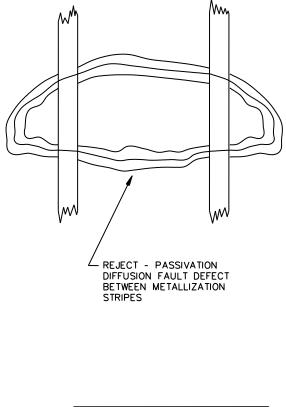

| 2072-11            | Passivation and diffusion faults                                                                                              |

| 2072–11            | Passivation and diffusion faults, cross section view                                                                          |

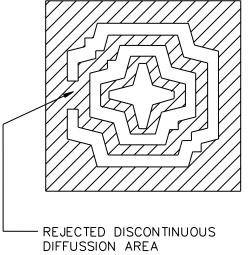

| 2072–12            | Passivation and diffusion faults                                                                                              |

| 2072–13            | Contact window in a diffused area which extends across a junction faults                                                      |

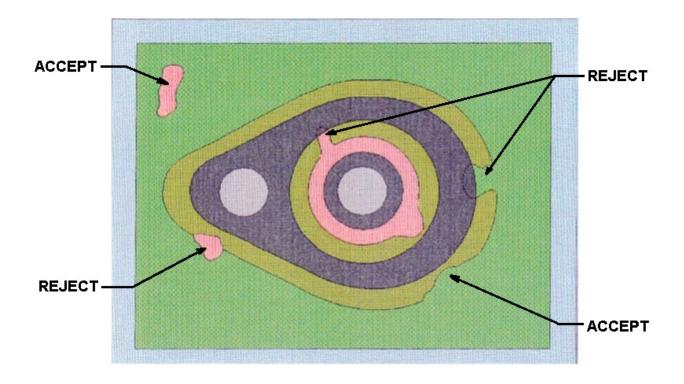

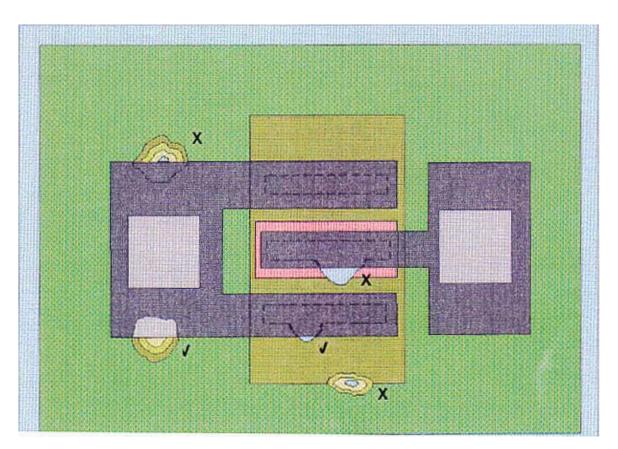

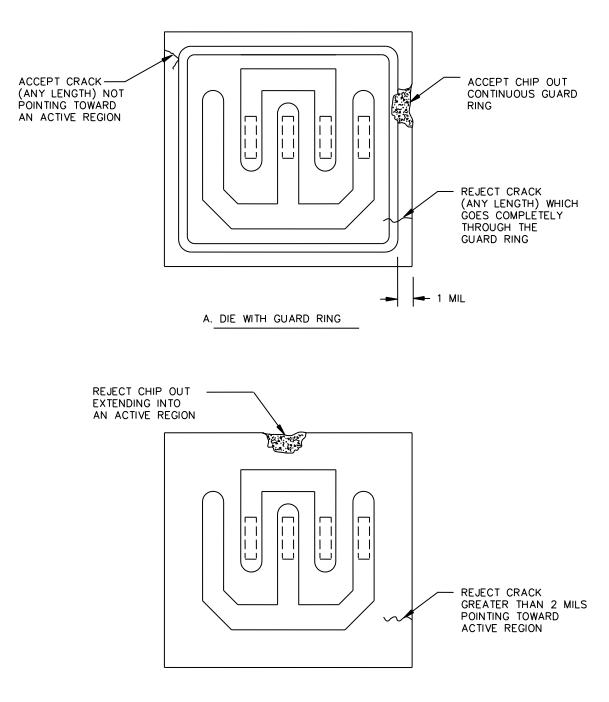

| 2072-14            | Die cracks and chips                                                                                                          |

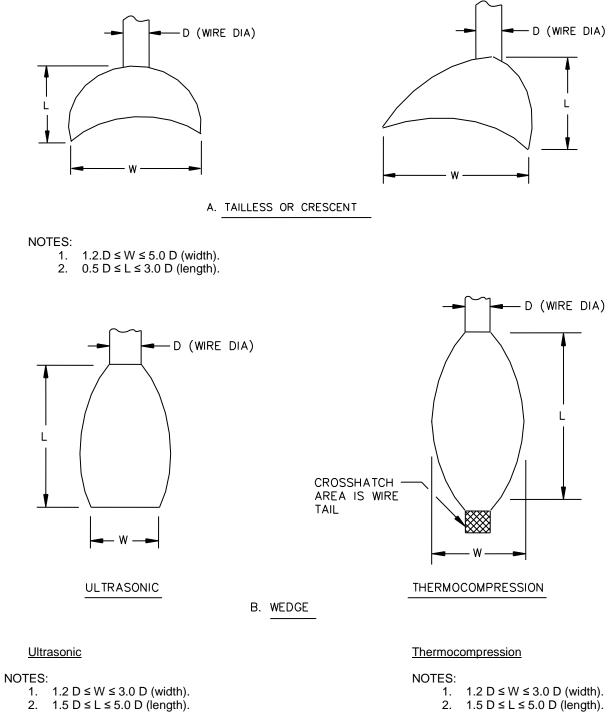

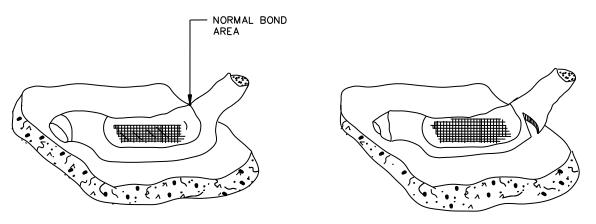

| 2072–15            | Bond dimensions                                                                                                               |

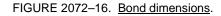

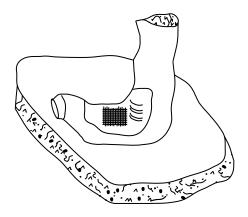

| 2072–10            | Lift and torn bonds                                                                                                           |

| 2072–17            | Ball bond diameter is less than 2 times or greater than 5 times the wire diameter                                             |

| 2072-18            | Ball bonds where the wire exit is not completely within the periphery of the ball                                             |

| 2072-19            | Ball bonds where exiting wire is not within boundaries of the bonding pad                                                     |

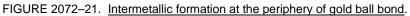

| 2072-20            | Intermetallic formation at the periphery of gold ball bond                                                                    |

| 2072-21            | Wedge bonds on the die or package post criteria                                                                               |

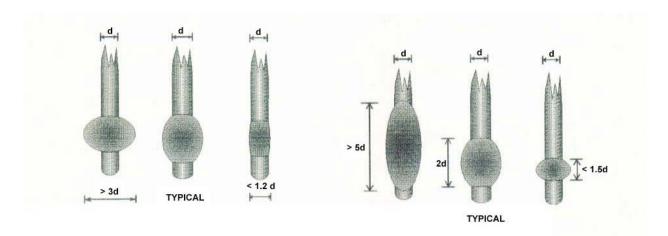

| 2072-22            | Tailless bond dimensions                                                                                                      |

|                    |                                                                                                                               |

| 2072–24<br>2072–25 | Wire bond to bonding pad area misalignment<br>Wire bond tails contacting with metallization not covered by glassivation       |

| 2072-25            | Wire bond tails contacting with metallization not covered by glassivation                                                     |

| 2072-20            | Bonds on the flat surface of the post top                                                                                     |

| 2072-27            | A bond on top of another bond                                                                                                 |

| 2072-20            | Bond to unglassivated die metallization                                                                                       |

| 2072-29            | Bond to glassivated die metallization                                                                                         |

| 2072-30            | Adjacent bonds violating separation limits                                                                                    |

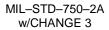

| 2072-31            | Wire that violates allowed limits                                                                                             |

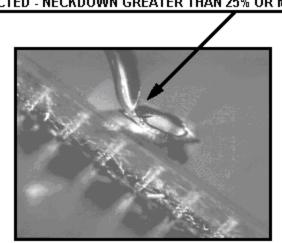

| 2072-32            | Wire nicks, tears, bonds, cuts, crimps, scoring, or neckdown                                                                  |

| 2072-33            | Bond tearing at interface of pad and wire                                                                                     |

| 2072-35            | Wire that has no arc or stress relief                                                                                         |

| 2072-35            | Wire not within 10 degrees of the perpendicular to the surface of the chip                                                    |

| 2072-30            | Excessive lead burn at lead post weld                                                                                         |

| 2072-38            | Pigtail to unglassivated active metal spacing                                                                                 |

| 2072-39            | Bow or loop in wire between double bonds at post                                                                              |

| 2072-39            | Excessive loops, bows, or sags in wire                                                                                        |

| 2072-40            | Non-embedded foreign particles present on the surface of the die                                                              |

| 2072-41            | Glass-embedded foreign particles on the die that bridge paths or junctions                                                    |

| 2072-42            | Ink on the surface of the die                                                                                                 |

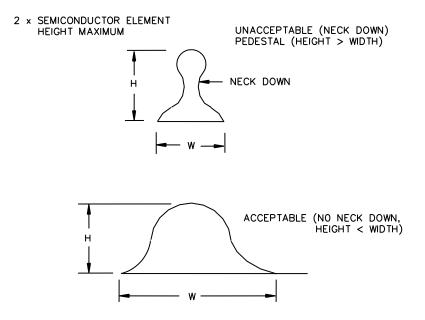

| 2072-43            | Balling of the die mounting material                                                                                          |

| 2072-44            | Tipped or tilted die                                                                                                          |

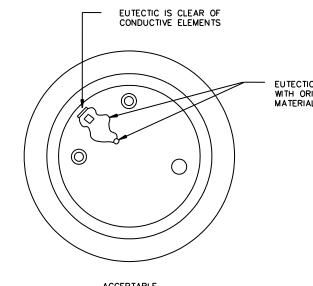

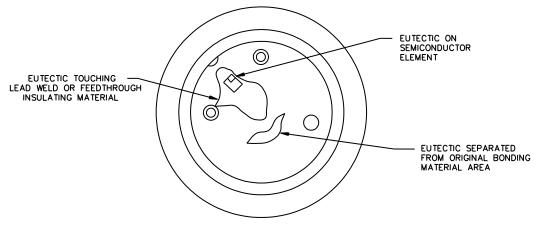

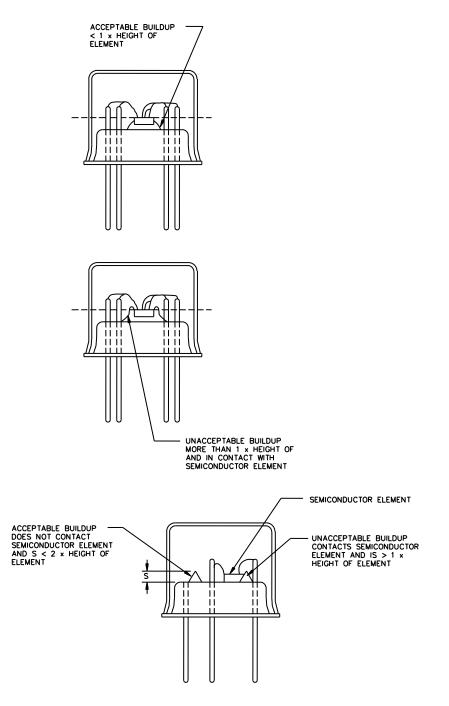

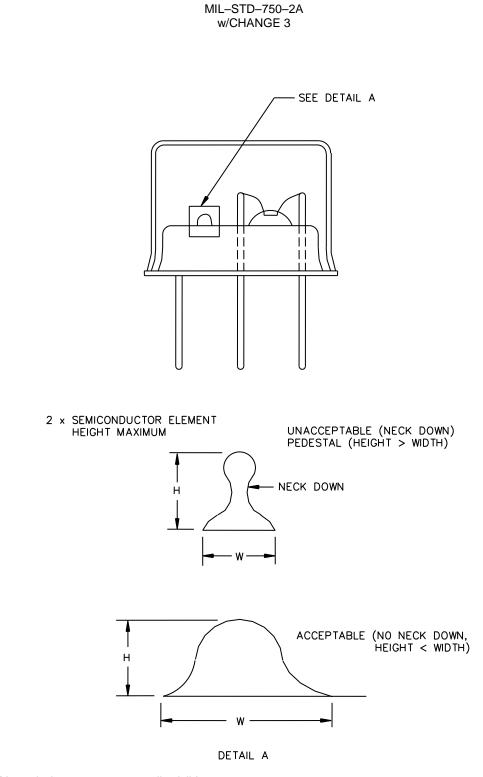

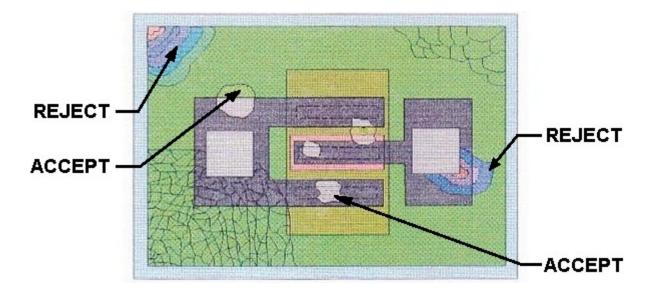

| 2072-45            | Acceptable and unacceptable bonding material build–up                                                                         |

| 2072-40            | Extraneous bonding material build–up                                                                                          |

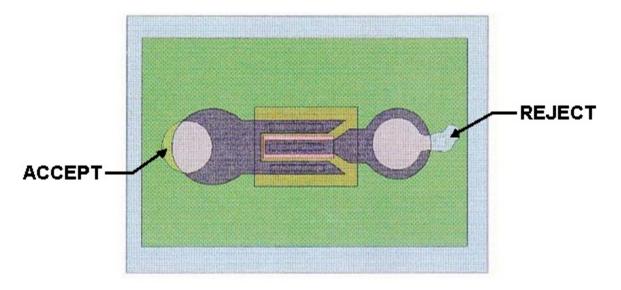

| 2072-47            | Acceptable and unacceptable excess material                                                                                   |

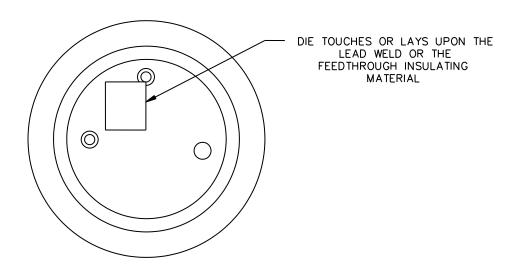

| 2072-49            | Unacceptable die placement                                                                                                    |

| 2072-49            | Two or more adjacent active metallization paths not covered by glassivation                                                   |

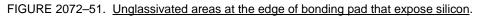

| 2072-50            | Unglassivated areas at the edge of bonding pad that expose silicon                                                            |

| 2072-51            | Glassivation covering the design bonding pad area                                                                             |

| 2012 02            | Classification optioning the design bending pad drea                                                                          |

# CONTENTS

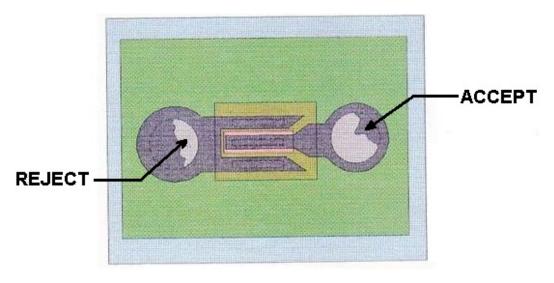

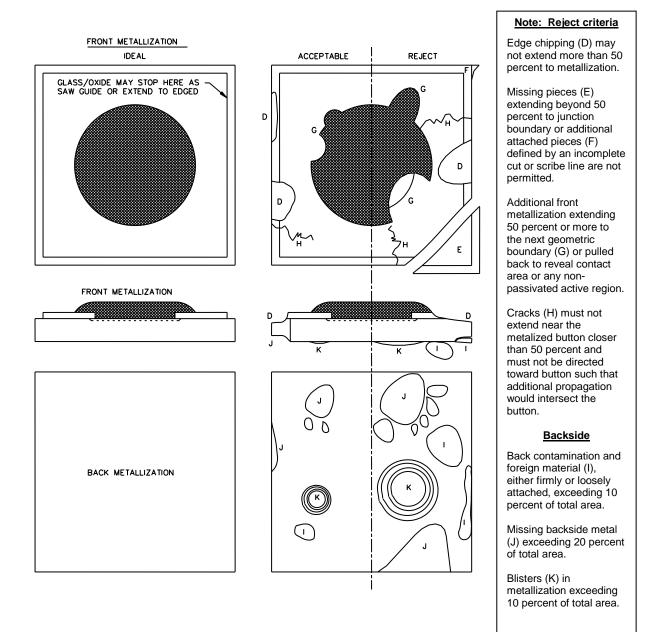

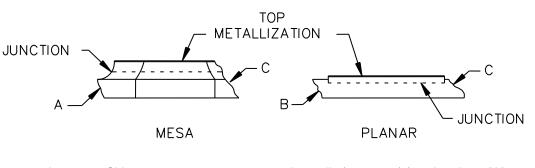

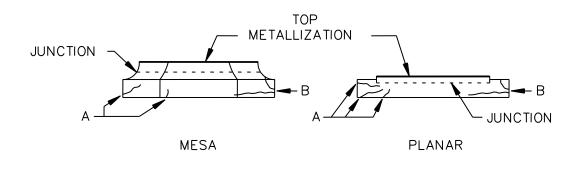

| 2073–1               | Button contact diodes                     |

|----------------------|-------------------------------------------|

| 2073–2               | High voltage planar diode l               |

| 2073–3               | High voltage planar diodes II             |

| 2073–4               | Inside moat mesa diodes                   |

| 2073–4               | Low voltage contact overlay diodes        |

| 2073-6               | Low voltage planar diode                  |

|                      |                                           |

| 2073–7               | Outside moat mesa diodes                  |

| 2073-8               | Schottky barrier diodes                   |

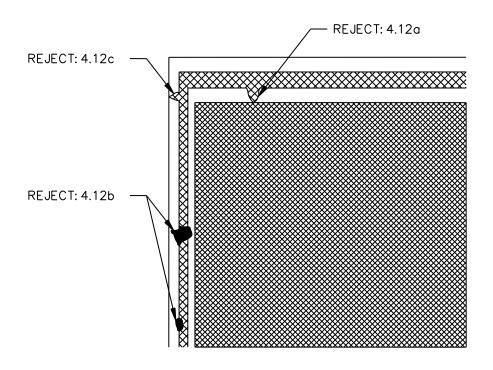

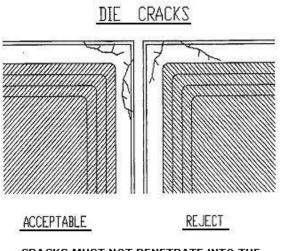

| 2074–1               | Die chip outs                             |

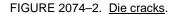

| 2074-2               | Die cracks                                |

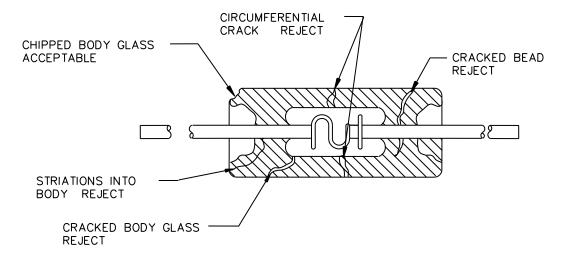

| 2074–A1              | Glass cracks and chips                    |

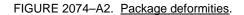

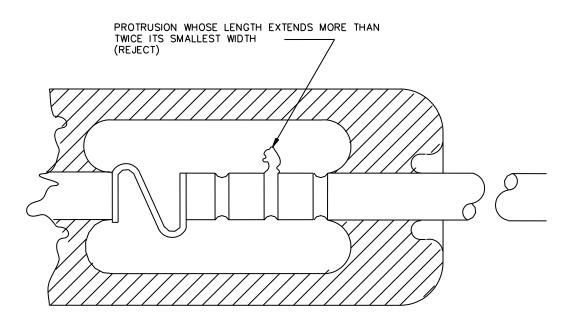

| 2074–A2              | Package deformities                       |

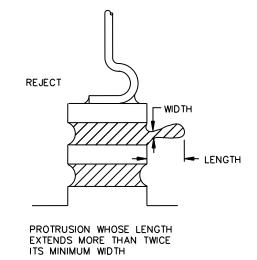

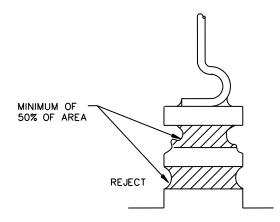

| 2074–A3              | Solder protrusions                        |

| 2074–A4              | Embedded whisker                          |

| 2074–A5              | Whisker toe contact                       |

| 2074–A6              | Whisker toe contact on top surface of die |

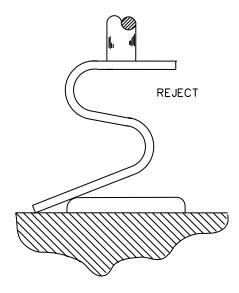

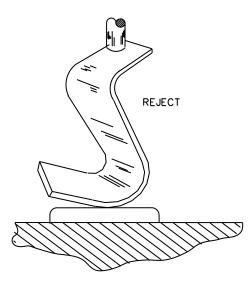

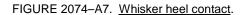

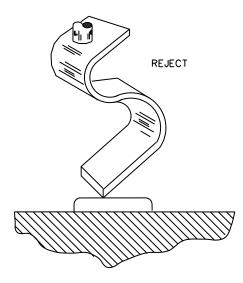

| 2074–A7              | Whisker heel contact                      |

| 2074–A8              | Whisker point contact                     |

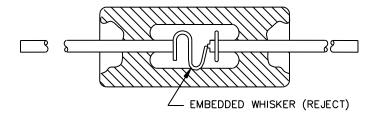

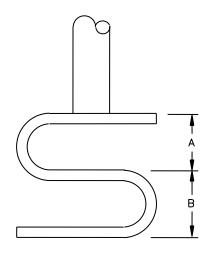

| 2074–A9              | S bend whisker compressed height          |

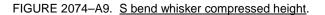

| 2074–A10             | C bend whisker compressed height          |

| 2074–A11             | Die alignment                             |

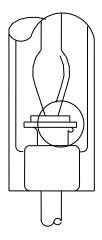

| 2074–B1              | Straight through internal construction    |

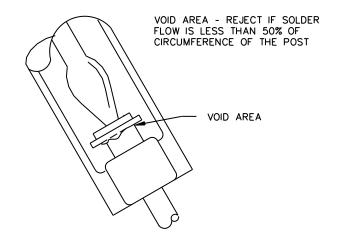

| 2074–B2              | Solder voids                              |

| 2074–B3              | Solder bridge                             |

| 2074–B4              | Solder voids                              |

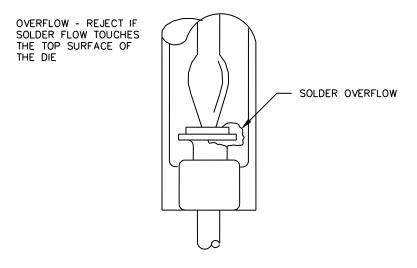

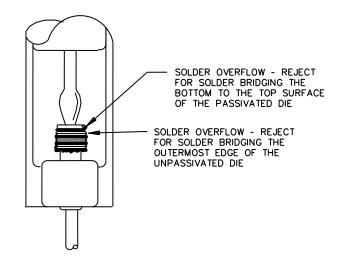

| 2074–B5              | Solder overflow                           |

| 2074–B6              | Solder slivers and spikes                 |

| 2074–B7              | Die-to-die solder connection              |

| 2074–C1              | Glass cracks                              |

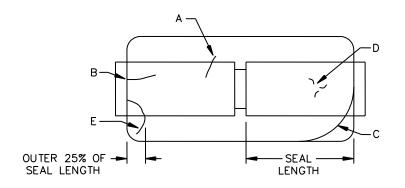

| 2074–C2              | High seal                                 |

| 2074–C3              | Insufficient seal                         |

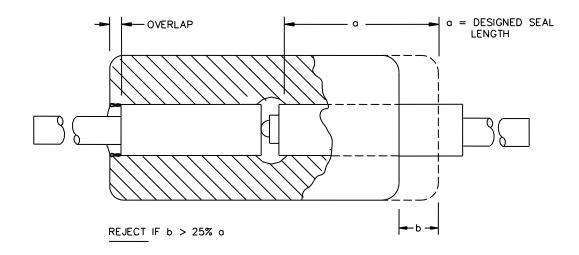

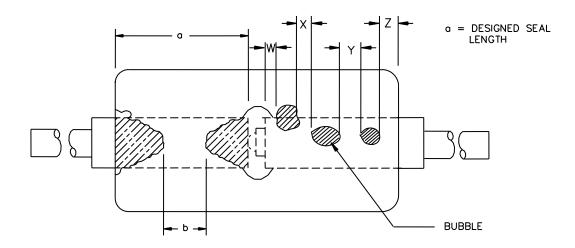

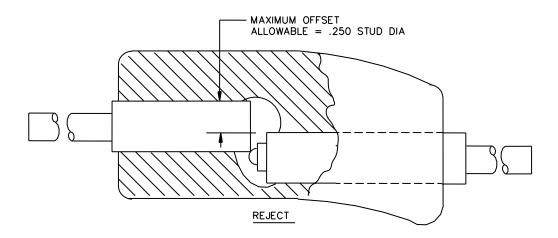

| 2074–C4              | Plug alignment                            |

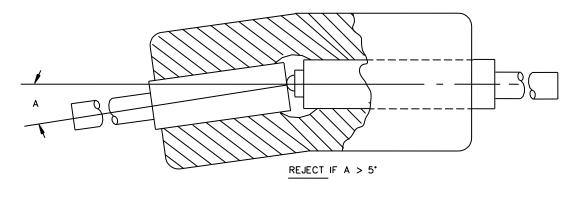

| 2074–C5              | Plug displacement                         |

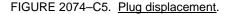

| 2074–C6              | Incomplete weld                           |

| 2074–D1              | Chip outs                                 |

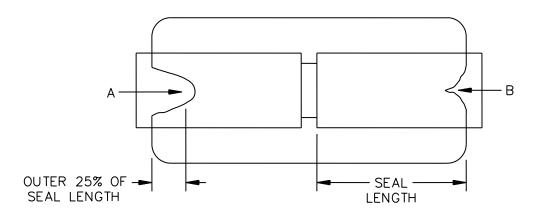

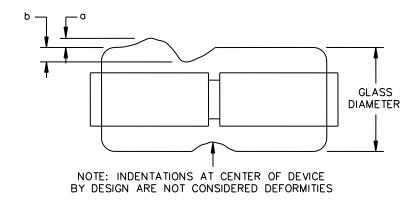

| 2074–D2              | Deformity                                 |

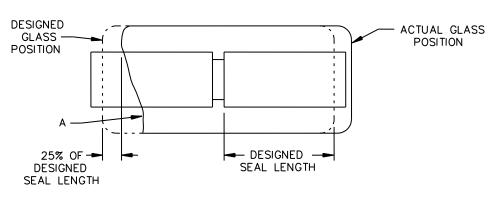

| 2074–D3              | Positioning                               |

| 2074–D4              | Insufficient seal                         |

| 2074–D5              | Tilt                                      |

| 2074–D6              | Die non-contract                          |

| 2074–D7              | Plug offset                               |

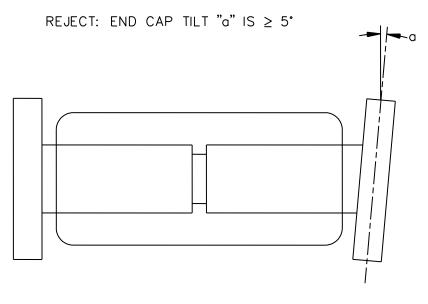

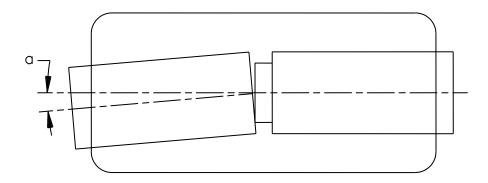

| 2074–D8              | Plug tilt angle                           |

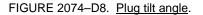

| 2074–D9              | Lead offset                               |

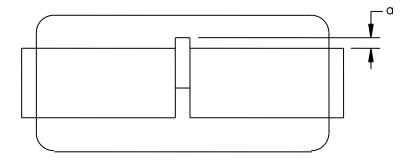

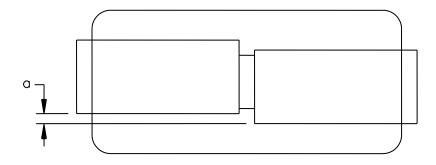

| 2074–D10             | End-cap clearance                         |

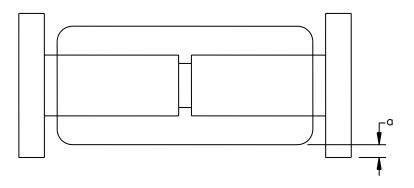

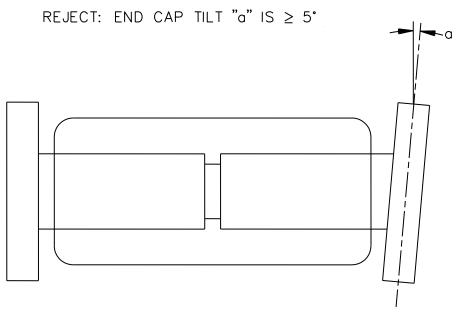

| 2074–D10<br>2074–D11 | End-cap tilt                              |

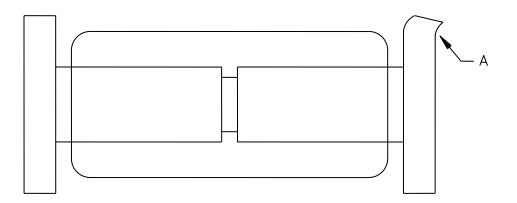

| 2074–D11<br>2074–D12 | End-cap deformation                       |

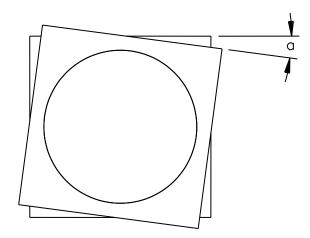

| 2074–D12<br>2074–D13 | End-cap deformation<br>End-cap rotation   |

| 2074–D13<br>2074–D14 | Mounting surface nicks and pits           |

| 2074–D14<br>2074–E1  | Whisker touches glass body wall           |

| 2074–E1<br>2074–E2   |                                           |

|                      | Whisker loops touch one another           |

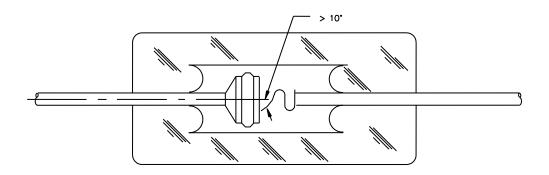

| 2074–E3<br>2074–E4   | Whisker angle over 10 degrees from normal |

| 2014-24              | Die touches glass package                 |

**FIGURE**

TITLE

# CONTENTS

**FIGURE**

TITLE

| 2074–G1 | Solder protrusion                                                                                 |

|---------|---------------------------------------------------------------------------------------------------|

| 2074–G2 | Solder flow                                                                                       |

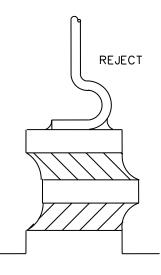

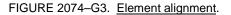

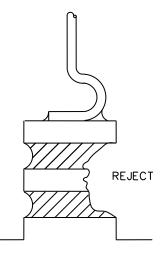

| 2074–G3 | Element alignment                                                                                 |

| 2074–G4 | Element tilt                                                                                      |

| 2074–G5 | Die chip out                                                                                      |

| 2074–G6 | Die cracks                                                                                        |

| 2074–H1 | Offset die                                                                                        |

| 2074–H2 | Tilted die                                                                                        |

| 2074–11 | Diamond base construction                                                                         |

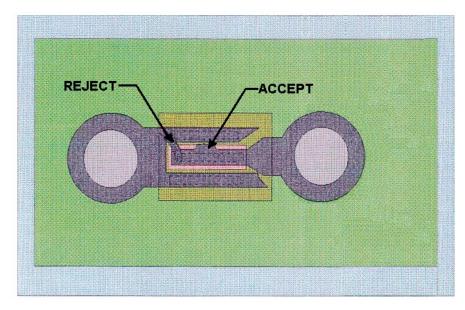

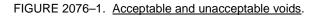

| 2076–1  | Acceptable and unacceptable voids                                                                 |

| 2076–2  | Lid seal voids and rejection criterion (drawing)                                                  |

| 2076–3  | Clearance in dual-in-line or flat pack type device                                                |

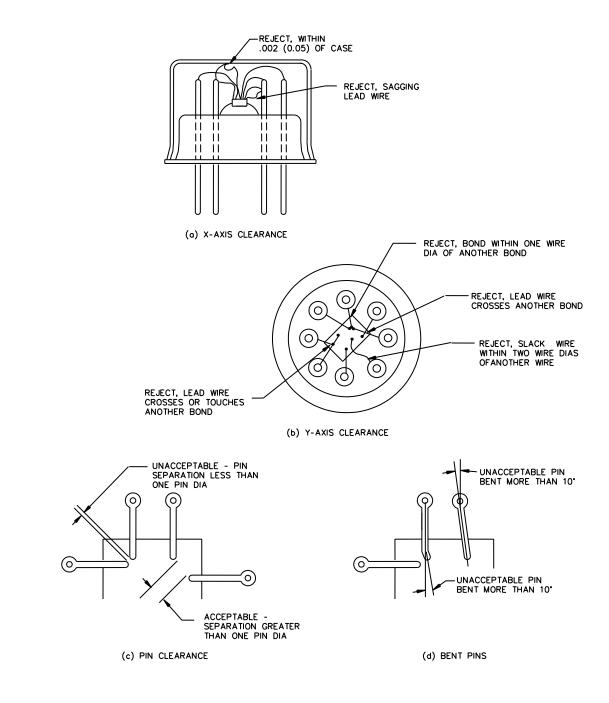

| 2076–4  | Clearance in round or box transistor type device                                                  |

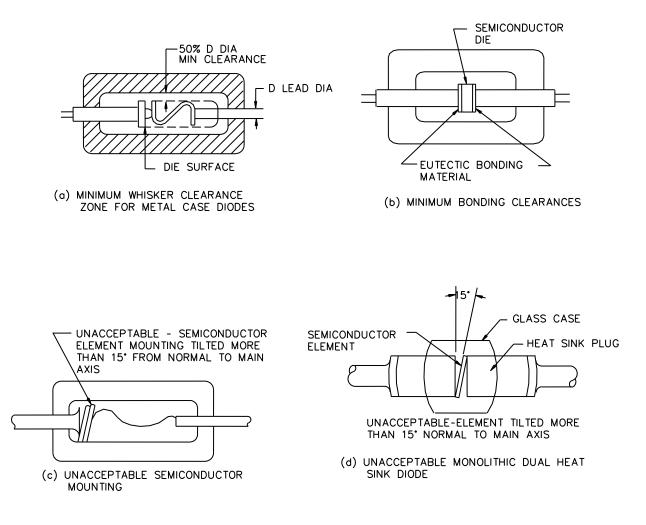

| 2076–5  | Clearance in cylindrical axial lead type device                                                   |

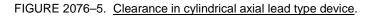

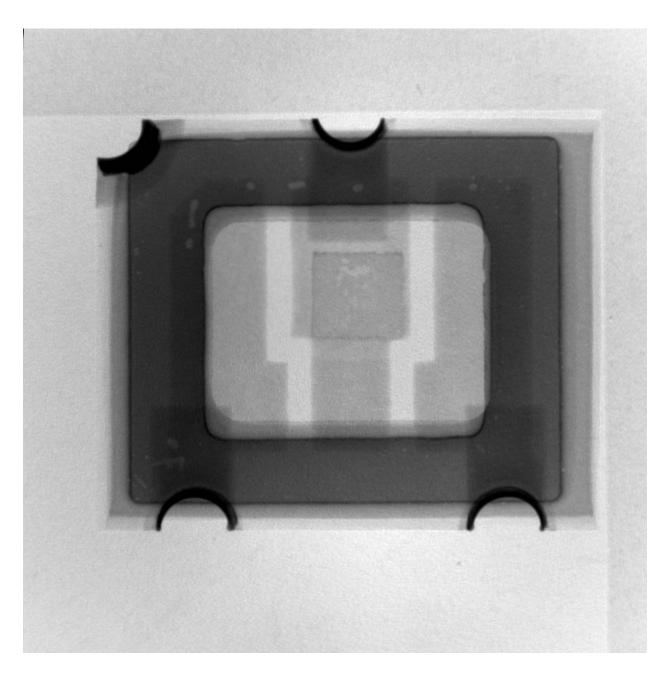

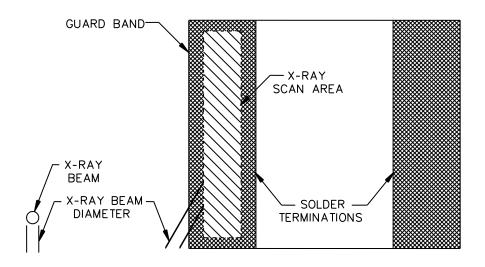

| 2076–6  | Typical digital radiography view of a UB device                                                   |

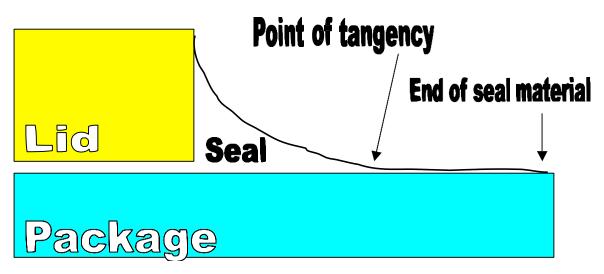

| 2076–7  | Design sealing width and seal fillet graphic                                                      |

| 2076-8  | Digital test parameter flow chart                                                                 |

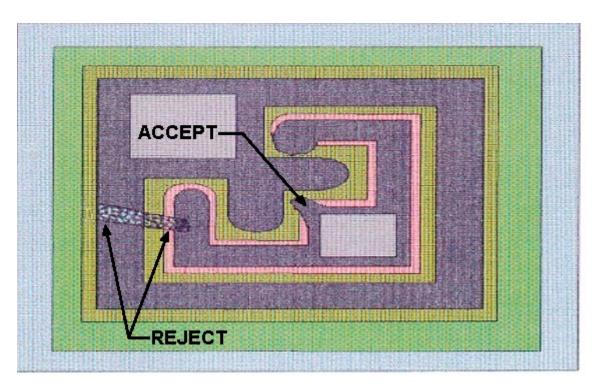

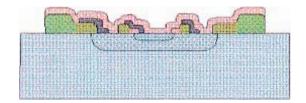

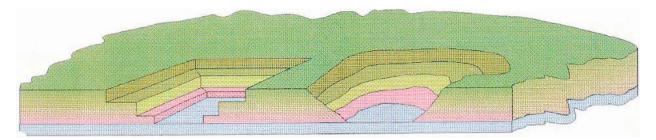

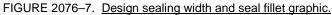

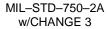

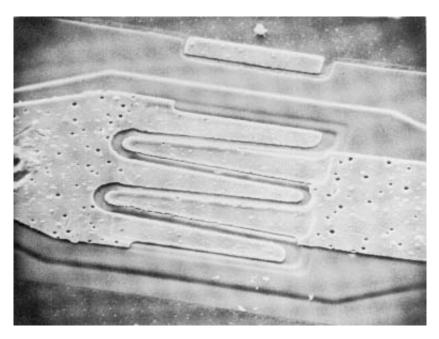

| 2077–1  | Cross-sectional planes at various passivation steps                                               |

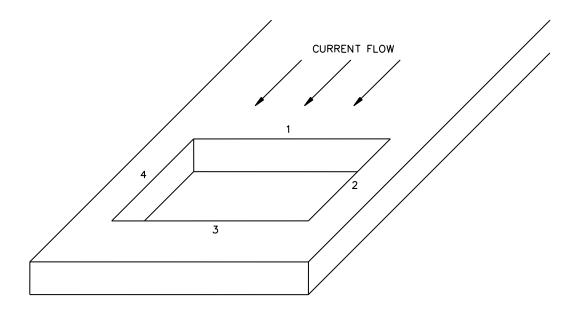

| 2077-2  | Directional edge                                                                                  |

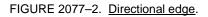

| 2077–3  | Viewing angle                                                                                     |

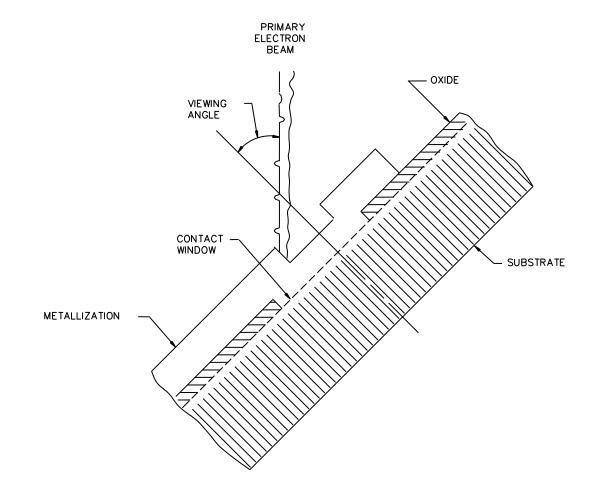

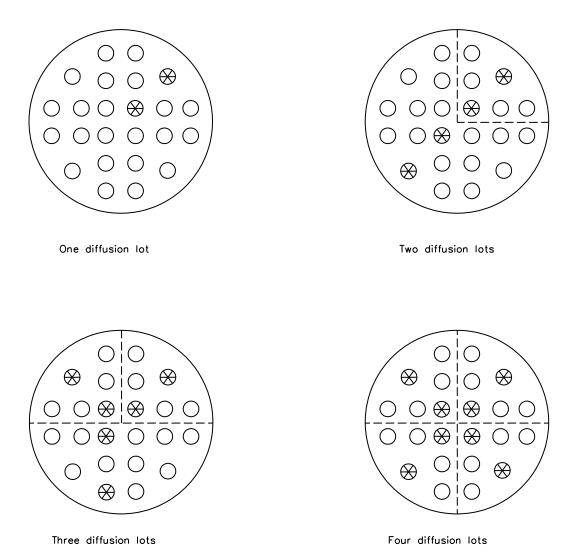

| 2077–4  | Wafer sampling procedures                                                                         |

| 2077–5  | Concept of reduction of cross sectional area of metallization as accept/reject criteria           |

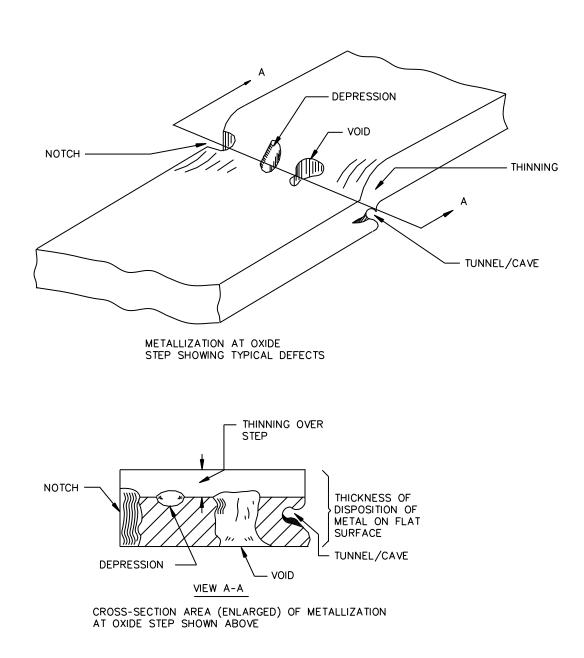

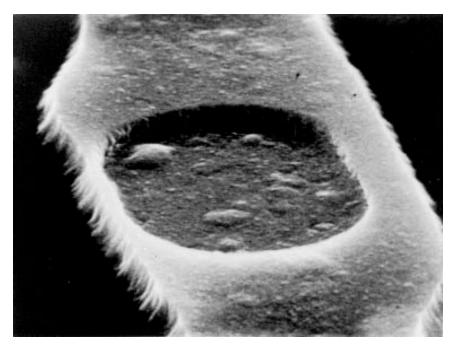

| 2077–6  | Void near oxide step at 3,400X                                                                    |

| 2077–7  | Voids at oxide step at 3,300X                                                                     |

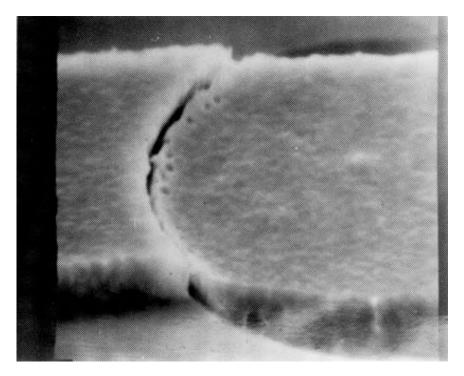

| 2077–8  | Tunnel/cave at oxide step at 10,000X                                                              |

| 2077–9  | Tunnel/cave at oxide step at 5,000X                                                               |

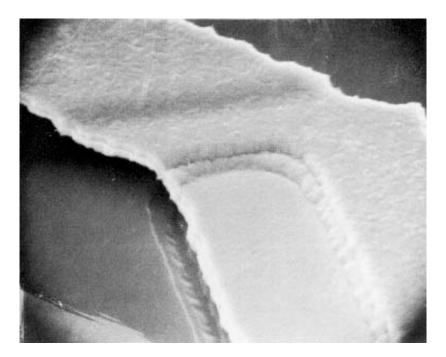

| 2077–10 | Separation of metallization at oxide step at base contact at 10,000X                              |

| 2077–11 | Separation of metallization at contact step at 7,000X                                             |

| 2077–12 | Crack-like defect at oxide step at 20,000X                                                        |

| 2077–13 | Crack-like defect at oxide step at 7,000X                                                         |

| 2077–14 | Acceptable thinning at oxide step (multi-level-metal) at 7,200X                                   |

| 2077–15 | Unacceptable thinning at oxide step (multi-level-metal) at 7,200X                                 |

| 2077–16 | Steep oxide step (MOS) at 6,000X                                                                  |

| 2077-17 | Steep oxide step (MOS) at 9,500X                                                                  |

| 2077–18 | Peeling or lifting of general metallization in contact window area at 5,000X                      |

| 2077–19 | General metallization voids at 10,000X                                                            |

| 2077-20 | General metallization voids at 5,000X (reject)                                                    |

| 2077-21 | Etch back/undercut type of notch at oxide step (multi-layered-metal) at 5,000X                    |

| 2077–22 | Barrier or adhesion layer etch back/undercut type of notch at oxide step (multi-layered-metal) at |

|         | 5,000X                                                                                            |

| 2078–1  | Metallization scratches and voids                                                                 |

| 2078-2  | Metallization scratches and voids – Continued                                                     |

| 2078–3  | Passivation and diffusion faults                                                                  |

| 2078–4  | Cracks and chips                                                                                  |

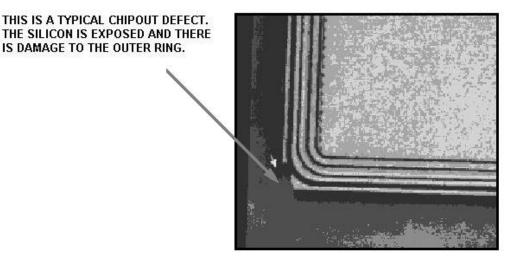

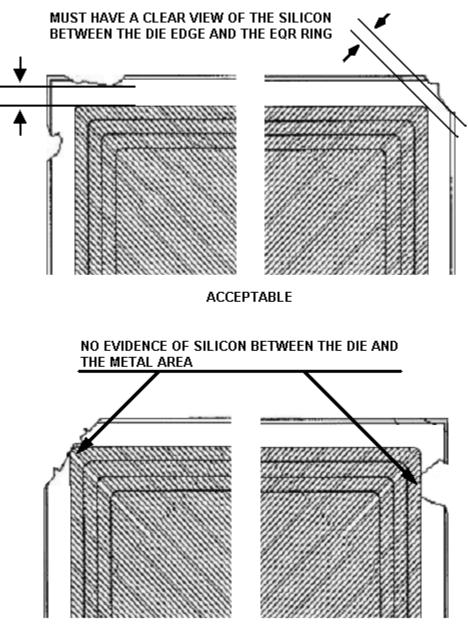

| 2078–5  | Cracks and chips (continued)                                                                      |

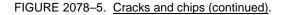

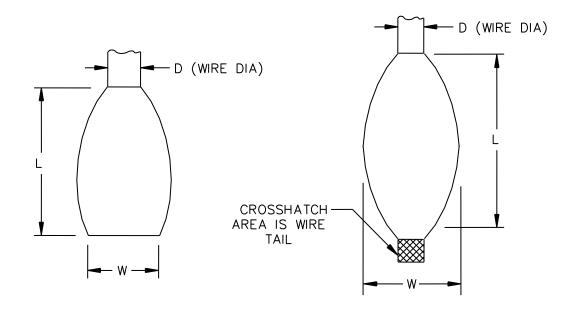

| 2078–6  | Bond dimensions, wedge                                                                            |

| 2078–7  | Bond dimensions, tailless or crescent                                                             |

| 2078–8  | Pigtail length                                                                                    |

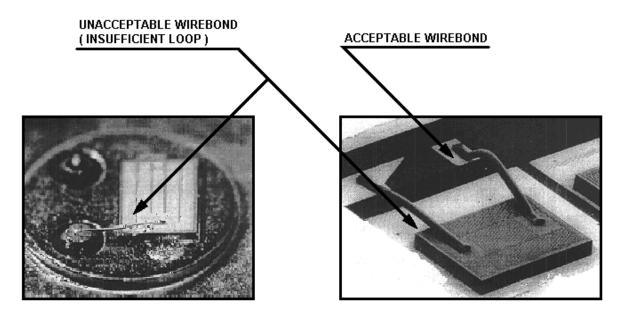

| 2078–9  | Unacceptable wirebond neckdown                                                                    |

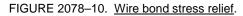

| 2078–10 | Wire bond stress relief                                                                           |

| 2078–11 | Wirebond to pad placement                                                                         |

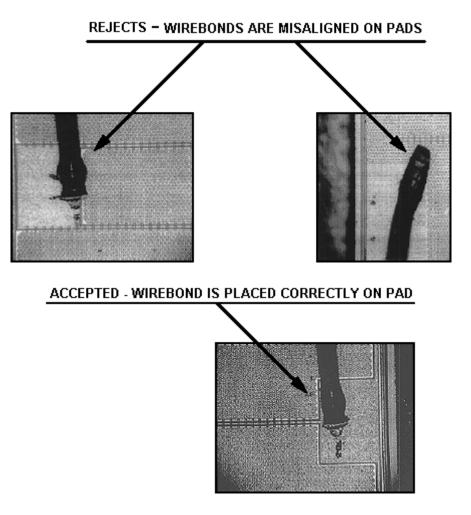

| 2078–12 | Extraneous bonding material build-up                                                              |

| 2078–13 | Acceptable and unacceptable excess material                                                       |

|         |                                                                                                   |

#### CONTENTS

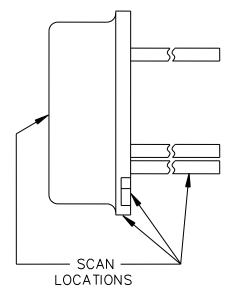

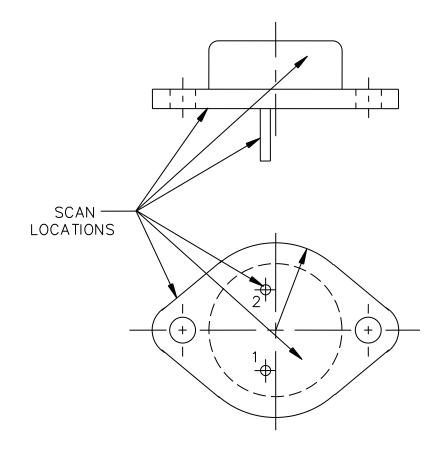

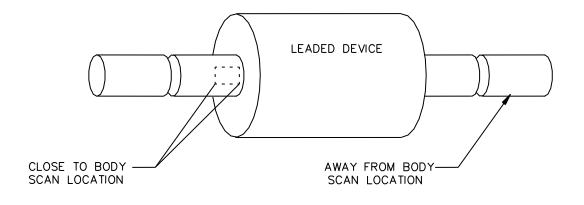

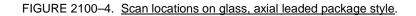

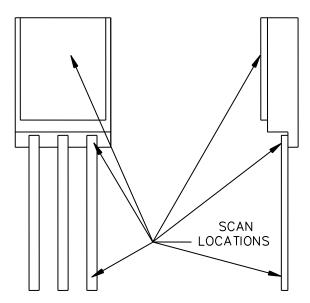

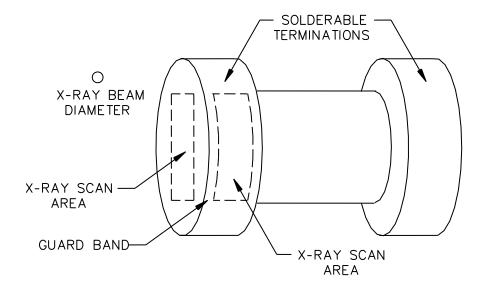

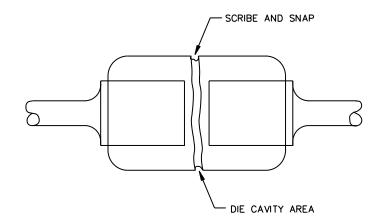

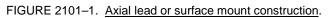

2100-1 Typical scan location on flat surface mounted devices 2100–2 Scan locations on can style package Scan locations on metal base flange mount style package 2100-3 Scan locations on glass, axial leaded package style 2100-4 Scan locations - ceramic, metal sealed, single in-line package 2100-5 Scan locations on metal electrode face (MELF) style package 2100-6 2101–1 Axial lead or surface mount construction 2101-2 Axial lead or surface mount construction 2101-3 Stud package TABLE TITLE **Destructive tests** Non-destructive tests 2031–I **Test conditions** 2037-I Minimum bond strength 2052-l Package height vs. test frequency for 20 g acceleration (condition A) 2070-I GaAs microwave device high magnification requirements 2070-II **Resistor criteria** 2072-I Die magnification requirements Magnification requirements 2073-I Wafer sampling procedures 2077–I 2077-II Examination procedure for sample dice Die magnification requirements 2078–I

Mandatory procedures Die attach criteria

FIGURE

Т

Ш

2101–I

2101-II

I

TITLE

# CONTENTS

| TEST METHOD NO. | TITLE                                                                                             |

|-----------------|---------------------------------------------------------------------------------------------------|

| 2005.2          | Axial lead tensile test                                                                           |

| 2006.2          | Constant acceleration                                                                             |

| 2016.2          | Shock                                                                                             |

| 2017.3          | Die attach integrity                                                                              |

| 2026.12         | Solderability                                                                                     |

| 2031.5          | Resistance to soldering heat                                                                      |

| 2036.5          | Terminal strength                                                                                 |

| 2037.1          | Bond strength (destructive bond pull test)                                                        |

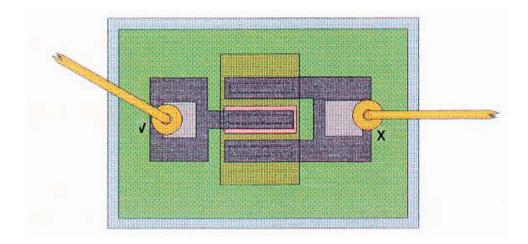

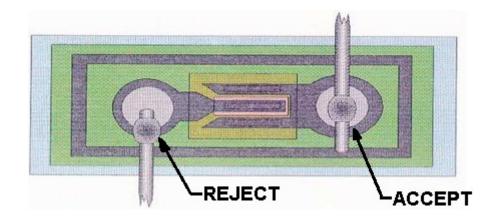

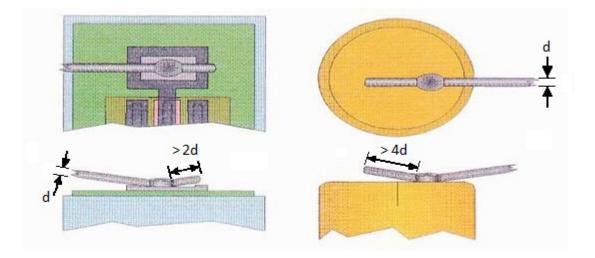

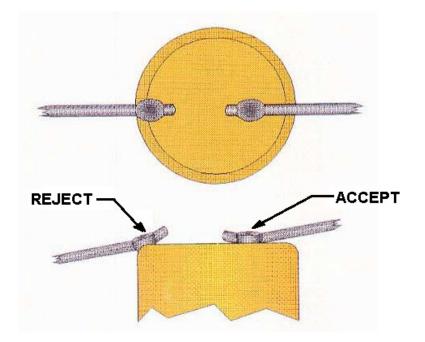

| 2038            | Surface mount end cap bond integrity                                                              |

| 2046.2          | Vibration fatigue                                                                                 |

| 2051.1          | Vibration noise                                                                                   |

| 2052.5          | Particle impact noise detection (PIND) test                                                       |

| 2056.3          | Vibration, variable frequency                                                                     |

| 2057.4          | Vibration, variable frequency (monitored)                                                         |

| 2066            | Physical dimensions                                                                               |

| 2068.1          | External visual for nontransparent glass-encased, double plug, noncavity axial leaded diodes      |

| 2069.2          | Pre–cap visual, power MOSFET's                                                                    |

| 2070.2          | Pre-cap visual microwave discrete and multichip transistors                                       |

| 2071.10         | Visual and mechanical examination                                                                 |

| 2072.9          | Internal visual transistor (pre-cap) inspection                                                   |

| 2073.2          | Visual inspection for die (semiconductor diode)                                                   |

| 2074.6          | Internal visual inspection (discrete semiconductor diodes)                                        |

| 2075.1          | Decap internal visual design verification                                                         |

| 2076.6          | Radiography                                                                                       |

| 2077.5          | Scanning electron microscope inspection of metallization                                          |

| 2078.1          | Internal visual for wire bonded diodes/rectifiers                                                 |

| 2081            | Forward instability, shock (FIST)                                                                 |

| 2082            | Backward instability, vibration (BIST)                                                            |

| 2100            | X–ray fluorescence (XRF) scan locations for discrete semiconductor Tin – Lead content<br>analysis |

| 2101.5          | Destructive physical analysis for diodes                                                          |

| 2102.2          | Destructive physical analysis for wire bonded devices                                             |

| 2103            | Design verification for surface mount devices                                                     |

I

I

I

#### 1. SCOPE

1.1 <u>Purpose</u>. Part 2 of this test method standard establishes uniform test methods for the mechanical testing to determine resistance to deleterious effects of natural elements and conditions surrounding military operations. For the purpose of this standard, the term "devices" includes such items as transistors, diodes, voltage regulators, rectifiers, tunnel diodes, and other related parts. This part of a multipart test method standard is intended to apply only to semiconductor devices.

1.2 <u>Numbering system</u>. The test methods are designated by numbers assigned in accordance with the following system.

1.2.1 <u>Classification of tests</u>. The mechanical test methods included in this part of a multipart test method standard are numbered 2005 to 2103 inclusive.

1.2.2 <u>Test method revisions</u>. Revisions are numbered consecutively using a period to separate the test method number and the revision number. For example, 2005.2 is the second revision of test method 2005.

1.3 <u>Method of reference</u>. When applicable, test methods contained herein should be referenced in the individual specification or specification sheet by specifying the test method number and the details required in the summary of the applicable test method should be listed. To avoid the necessity for changing documents that refer to test methods of this standard, the revision number should not be used when referencing test methods. (For example: Use 2005 versus 2005.2.)

#### 2. APPLICABLE DOCUMENTS

2.1 <u>General</u>. The documents listed in this section are specified in sections 3 and 4 and the individual test methods of this standard. This section does not include documents cited in other sections of this standard or recommended for additional information or as examples. While every effort has been made to ensure the completeness of this list, document users are cautioned that they must meet all specified requirements documents cited in sections 3 and 4, and the individual test methods of this standard, whether or not they are listed.

#### 2.2 Government documents.

2.2.1 <u>Specifications, standards, and handbooks</u>. The following specifications, standards, and handbooks form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

# DEPARTMENT OF DEFENSE SPECIFICATIONS

MIL-PRF-19500 - Semiconductor Devices, General Specification for.

## DEPARTMENT OF DEFENSE STANDARDS

| MIL-STD-750   | _ | Test Methods For Semiconductor Devices.               |

|---------------|---|-------------------------------------------------------|

| MIL-STD-750-1 | _ | Environmental Test Methods For Semiconductor Devices. |

| MIL-STD-750-3 | - | Electrical Test Methods For Semiconductor Devices.    |

| MIL-STD-883   | _ | Test Method Standard Microcircuits.                   |

FEDERAL STANDARDS

| FED-STD-595             | _ | Colors used in Government Procurement. |

|-------------------------|---|----------------------------------------|

| FED-STD-595/15102-15123 | _ | Blue, Gloss.                           |

| FED-STD-595/25102-25109 | _ | Blue, Semi-gloss.                      |

(Copies of these documents are available online at http://quicksearch.dla.mil.)

2.3 <u>Non-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### ASME INTERNATIONAL (ASME)

ASME Y14.38 – Abbreviations and Acronyms for Use on Drawings and Related Documents.

(Copies of these documents are available online at http://www.asme.org or from ASME International, Three Park Avenue, New York, NY 10016–5990.)

ASTM INTERNATIONAL (ASTM)

ASTM D1867 – Standard Specification for Copper-Clad Thermosetting Laminates for Printed Wiring.

(Copies of these documents are available online at http://www.astm.org or from ASTM International, 100 Barr Harbor Drive, P.O. Box C700, West Conshohocken, PA 19428–2959.)

## INTERNATIONAL ORGANIZATION FOR STANDARDIZATION (ISO)

| ISO 14644–1 | _ | Cleanrooms and Associated Controlled Environments - Part 1: Classification of Air |

|-------------|---|-----------------------------------------------------------------------------------|

|             |   | Cleanliness.                                                                      |

| ISO 14644–2 | _ | Cleanrooms and Associated Controlled Environments – Part 2: Specifications for    |

|             |   | Testing and Monitoring to Prove Continued Compliance with ISO 14644–1.            |

(Copies of these documents are available online at http://www.iso.ch or from the International Organization for Standardization American National Standards Institute, 11 West 42<sup>nd</sup> Street, 13<sup>th</sup> Floor, New York, NY 10036.)

IPC – ASSOCIATION CONNECTING ELECTRONICS INDUSTRIES (IPC)

| J-STD-002 | _ | Solderability Tests for Component Leads, Terminations, Lugs, Terminals and      |

|-----------|---|---------------------------------------------------------------------------------|

|           |   | Wires.                                                                          |

| J-STD-004 | _ | Requirements for Soldering Fluxes.                                              |

| J–STD–005 | - | Requirements for Soldering Pastes.                                              |

| J-STD-006 | _ | Requirements for Electronic Grade Solder Alloys and Fluxed and Non-fluxed Solid |

|           |   | Solders for Electronic Soldering Applications.                                  |

| IPC-9701  | _ | Performance Test Methods and Qualification Requirements for Surface Mount       |

|           |   | Solder Attachments.                                                             |

(Copies of these documents are available online at http://www.ipc.org or from IPC – Association Connecting Electronics Industries, 3000 Lakeside Drive, Suite 309 S, Bannockburn, IL 60015–1249.)

JEDEC - SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

JEDEC JESD213 – Common Test Method for Detecting Component Surface Finish Materials.

(Copies of this document are available online at http://www.jedec.org or from JEDEC, 3103 North 10<sup>th</sup> Street, Suite 240-S Arlington, VA 22201–2107.)

NCSL INTERNATIONAL (NCSL)

NCSL Z540.3 – Requirements for the Calibration of Measuring and Test Equipment.

(Copies of this document are available online at http://www.ncsli.org or can be obtained through NCSL International, 2995 Wilderness Place, Suite 107, Boulder, CO 80301–5404.)

2.4 <u>Order of precedence</u>. Unless otherwise noted herein or in the contract, in the event of a conflict between the text of this document and the references cited herein (except for related applicable specification sheet, the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

# 3. DEFINITIONS

3.1 <u>Acronyms, symbols, and definitions</u>. For the purposes of this test method standard, the acronyms, symbols, and definitions specified in MIL–PRF–19500, ASME Y14.38, and herein apply.

3.2 <u>Acronyms used in this standard</u>. Acronyms used in this test method standard are defined as follows:

| a.                               | BIST                                    | -           | Backward instability shock test.                                                                                                                                                         |

|----------------------------------|-----------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b.                               | dB                                      | -           | Decibel.                                                                                                                                                                                 |

| C.                               | DPA                                     | -           | Destructive physical analysis.                                                                                                                                                           |

| d.                               | DUT                                     | -           | Device under test.                                                                                                                                                                       |

| e.                               | FET                                     | -           | Field-effect transistor.                                                                                                                                                                 |

| f.                               | FIST                                    | -           | Forward instability shock test.                                                                                                                                                          |

| g.                               | GaAs                                    | -           | Gallium Arsenide.                                                                                                                                                                        |

| h.                               | Hz                                      | -           | Hertz.                                                                                                                                                                                   |

| i.                               | mA                                      | -           | Milliamps                                                                                                                                                                                |

| j.                               | mV                                      | -           | Milivolts.                                                                                                                                                                               |

|                                  |                                         |             |                                                                                                                                                                                          |

| k.                               | MOSFET                                  | -           | Metal oxide semiconductor field-effect transistor.                                                                                                                                       |

| k.<br>I.                         | MOSFET<br>NIST                          | -           | Metal oxide semiconductor field-effect transistor.<br>National Institute of Standards and Technology.                                                                                    |

|                                  |                                         | -<br>-<br>- |                                                                                                                                                                                          |

| I.                               | NIST                                    | -<br>-<br>- | National Institute of Standards and Technology.                                                                                                                                          |

| l.<br>m.                         | NIST<br>PIND                            | -<br>-<br>- | National Institute of Standards and Technology.<br>Particle impact noise detection.                                                                                                      |

| l.<br>m.<br>n.                   | NIST<br>PIND<br>RF                      | -           | National Institute of Standards and Technology.<br>Particle impact noise detection.<br>Radio frequency.                                                                                  |

| l.<br>m.<br>n.<br>o.             | NIST<br>PIND<br>RF<br>rms               |             | National Institute of Standards and Technology.<br>Particle impact noise detection.<br>Radio frequency.<br>Root means square.                                                            |

| l.<br>m.<br>n.<br>o.<br>p.       | NIST<br>PIND<br>RF<br>rms<br>SEM        | -           | National Institute of Standards and Technology.<br>Particle impact noise detection.<br>Radio frequency.<br>Root means square.<br>Scanning electron microscope.                           |

| l.<br>m.<br>n.<br>o.<br>p.<br>q. | NIST<br>PIND<br>RF<br>rms<br>SEM<br>STU | -           | National Institute of Standards and Technology.<br>Particle impact noise detection.<br>Radio frequency.<br>Root means square.<br>Scanning electron microscope.<br>Sensitivity test unit. |

#### 4. GENERAL REQUIREMENTS

4.1 <u>General</u>. Unless otherwise specified in the individual test method, the general requirements of MIL-STD-750 shall apply.

4.2 <u>Test circuits</u>. The test circuits shown in the test methods of this test method standard are given as examples which may be used for the measurements. They are not necessarily the only test circuits which can be used; however the manufacturer shall demonstrate to the Government that other test circuits which they may desire to use will give results within the desired accuracy of measurement. Circuits are shown for PNP transistors in one circuit configuration only. They may readily be adapted for NPN devices and for other circuit configurations.

4.3 <u>Destructive tests</u>. Unless otherwise demonstrated, the test methods listed in table I shall be classified as destructive. MIL-STD-750 covers the necessary actions needed to reclassify a test method as non-destructive.

| Test method number | Test                                      |

|--------------------|-------------------------------------------|

| 2017               | Die shear test                            |

| 2017               | Solderability                             |

| 2031               | Soldering heat                            |

| 2036               | Terminal strength                         |

| 2037               | Post-seal bond strength                   |

| 2038               | Surface mount end cap bond integrity      |

| 2075               | Decap internal visual design verification |

| 2077               | SEM                                       |

TABLE I. Destructive tests.

All other mechanical tests (other than those listed in 4.4) shall be considered destructive initially, but may subsequently be considered non-destructive upon accumulation of sufficient data to indicate that the test is non-destructive. The accumulation of data from five repetitions of the specified test on the same sample of product, without significant evidence of cumulative degradation in any device in the sample, is considered sufficient evidence that the test is non-destructive for the device of that manufacturer. Any test specified as a 100-percent screen shall be considered non-destructive for the stress level and duration or number of cycles applied as a screen.

4.4 <u>Non-destructive tests</u>. Unless otherwise demonstrated, the test methods listed in table II shall be classified as nondestructive.

| Test method number           | Test                                                                                                                     |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2006                         | Constant acceleration                                                                                                    |  |  |  |

| 2016                         | Shock                                                                                                                    |  |  |  |

| 2026                         | Solderability (if the original lead finish is unchanged and if the maximum allowable number of reworks is not exceeded.) |  |  |  |

| 2052                         | PIND test                                                                                                                |  |  |  |

| 2056                         | Vibration, variable frequency                                                                                            |  |  |  |

| 2066                         | Physical dimensions                                                                                                      |  |  |  |

| 2069, 2070, 2072, 2073, 2074 | Internal visual (pre-cap)                                                                                                |  |  |  |

| 2071                         | External visual                                                                                                          |  |  |  |

| 2076                         | Radiographic inspection                                                                                                  |  |  |  |

| 2081                         | FIST                                                                                                                     |  |  |  |

| 2082                         | BIST                                                                                                                     |  |  |  |

#### TABLE II. Non-destructive tests.

NOTE: When the junction temperature exceeds the device maximum rated junction temperature for any operation or test (including electrical stress test), these tests shall be considered destructive except under transient surge or nonrepetitive fault conditions, or approved accelerated screening, when it may be desirable to allow the junction temperature to exceed the rated junction temperature. The feasibility shall be determined on a part by part basis and, in the case where it is allowed adequate sample testing, shall be performed to provide the proper reliability safeguards.

4.5 <u>Laboratory suitability</u>. Prior to processing any semiconductor devices intended for use in any military system or sub-system, the facility performing the test(s) shall be audited by the DLA Land and Maritime, Sourcing and Qualification Division and be granted written laboratory suitability status for each test method to be employed. Processing of any devices by any facility without laboratory suitability status for the test methods used shall render the processed devices nonconforming.

# 5. DETAILED REQUIREMENTS

This section is not applicable to this standard.

#### 6. NOTES

(This section contains information of a general or explanatory nature that may be helpful, but is not mandatory.)

6.1 <u>Intended use</u>. The intended use of this test method standard is to establish appropriate conditions for testing semiconductor devices to give test results that simulate the actual service conditions existing in the field. This test method standard has been prepared to provide uniform test methods, controls, and procedures for determining with predictability the suitability of such devices within military, aerospace and special application equipment.

6.2 <u>International standardization agreement</u>. Certain provisions of this test method standard are the subject of international standardization agreement. When amendment, revision, or cancellation of this test method standard is proposed which will affect or violate the international agreement concerned, the preparing activity will take appropriate reconciliation action through international standardization channels, including departmental standardization offices, if required.

6.3 Subject term (key word) listing.

Destructive tests Laboratory suitability Mechanical characteristics tests Non-destructive tests

6.4 <u>Supersession data</u>. The main body and five parts (-1 through -5) of this revision of MIL-STD-750 replace superseded MIL-STD-750E.

6.5 <u>Change notations</u>. The margins of this standard are marked with vertical bars to indicate modifications generated by this change. This was done as a convenience only and the Government assumes no liability whatsoever for any inaccuracies in these notations. Bidders and contractors are cautioned to evaluate the requirements of this document based on the entire content irrespective of the marginal notations.

#### METHOD 2005.2

## AXIAL LEAD TENSILE TEST

1. <u>Purpose</u>. The purpose of this test method is to establish the capability of axial lead glass body diodes to be free of intermittents or opens when measured in the forward mode under conditions of tensile stress and controlled temperature. This test may be destructive.

## 2. Apparatus.

- Digital volt meter and constant current source capable of supplying 100 mA of dc current to the DUT. A battery supply is preferred but if a constant current supply is used, a voltage clamp of approximately five volts shall be used.

- Load cell with 10 pounds (4.56 Kg) full scale dial (or equivalent) capable of measuring 8 pounds (3.63 Kg) ±10 percent.

- c. Pull test fixture capable of clamping both ends of the diode while applying an 8 pound (3.63 Kg) axial pull. One clamp must be electrically isolated allowing the diode forward voltage to be monitored.

- d. Hot air supply capable of heating the diode ambient to  $T_A = +150^{\circ}C \pm 5^{\circ}C$  (T<sub>J</sub> approximately +175°C).

3. <u>Procedure</u>. The diode under test shall be mounted in the pull test fixture. The electrical monitoring equipment shall be connected to the diode leads. A forward current of 100 mA is passed through the diode while noting the forward voltage. The ambient temperature of the diode is then increased to  $+150^{\circ}C \pm 5^{\circ}C$ . NOTE: The diode junction temperature (T<sub>J</sub>) will be approximately  $+25^{\circ}C$  higher than ambient (T<sub>J</sub> approximately  $+175^{\circ}C$ ) due to the thermal resistance of the diode when testing small (computer) diodes at 100 mA dc in the forward direction. A silicon diode (computer type) also has an approximate negative  $1.2 \text{ mV/}^{\circ}C$  temperature coefficient at 100 mA. Therefore a 150 mV decline (100 mV minimum) in voltage should be expected during the ambient temperature increase (from  $+25^{\circ}C$  to  $+150^{\circ}C$ ). After stabilizing at this temperature, then the axial lead pull force of eight pounds shall be applied while observing the forward voltage change.

4. <u>Criteria for rejection</u>. An acceptable device shall not exhibit a forward voltage increase of more than 30 mV during the 8 pound pull. Any instability or open is cause for rejection.

5. <u>Summary</u>. The following conditions shall be specified in the applicable performance specification sheet or acquisition document:

- a. Ambient test temperature, if other than  $+150^{\circ}C \pm 5^{\circ}C$ .

- b. Measurement current, if other than 100 mA dc.

- c. Axial tensile stress, if other than 8 pounds (3.63 Kg).

- d. Allowable change in forward voltage, if other than 30 mV.

This page is intentionally left blank.

#### METHOD 2006.2

# CONSTANT ACCELERATION

1. <u>Purpose</u>. The constant acceleration test is used to determine the effect on semiconductor devices of a centrifugal force. This test is an accelerated test designed to indicate types of structural and mechanical weaknesses not necessarily detected in shock and vibration tests.

2. <u>Apparatus</u>. Constant acceleration tests shall be made on an apparatus capable of meeting the minimum requirements of the individual specification sheets.

3. <u>Procedure</u>. The device shall be restrained by its case, or by normal mountings, and the leads or cables secured. A centrifugal acceleration of the value specified shall then be applied to the device for one minute in each of the orientations  $X_1$ ,  $X_2$ ,  $Y_1$ ,  $Y_2$ ,  $Z_1$ , and  $Z_2$ . The acceleration shall be increased gradually, to the value specified, in not less than 20 seconds. The acceleration shall be decreased gradually to zero in not less than 20 seconds.

Unless otherwise specified, test condition D (condition B for devices with power ratings  $\geq$  10 watts at T<sub>c</sub> = +25°C) shall apply. Note: The stress level(s) are absolute minimums with no lower tolerances.

| Test condition | Stress level (g) |  |  |

|----------------|------------------|--|--|

| А              | 5,000            |  |  |

| В              | 10,000           |  |  |

| С              | 15,000           |  |  |

| D              | 20,000           |  |  |

| E              | 30,000           |  |  |

| F              | 50,000           |  |  |

| G              | 75,000           |  |  |

| Н              | 100,000          |  |  |

| J              | 125,000          |  |  |

4. <u>Summary</u>. The following conditions shall be specified in the applicable performance specification sheet or acquisition document:

- Amount of centrifugal force to be applied, in gravity units (g), if other than test condition D (condition B for devices with power ratings ≥ 10 watts at Tc = +25°C) (see 3).

- b. Measurements to be made after test.

- c. Any variations in duration or limitations to orientation.

- d. Sequence of orientations, if other than as specified.

This page is intentionally left blank.

#### METHOD 2016.2

#### SHOCK

1. <u>Purpose</u>. This test method is intended to determine the ability of the semiconductor devices to withstand moderately severe shocks such as would be produced by rough handling, transportation, or field operation. Shocks of this type may disturb operating characteristics or cause damage similar to that resulting from excessive vibration, particularly if the shock pulses are repetitive.

2. Apparatus. The shock testing apparatus shall be capable of providing shock pulses of the specified peak acceleration and pulse duration to the body of the device. The acceleration pulse, as determined from the output of a transducer with a natural frequency greater than or equal to five times the frequency of the shock pulse being established, shall be a half-sine waveform with an allowable distortion not greater than  $\pm 20$  percent of the specified peak acceleration. The pulse duration shall be measured between the points at 10 percent of the peak acceleration during rise time and at 10 percent of the peak acceleration during decay time. Absolute tolerances of the pulse durations of 2 ms and greater. For specified duration less than 2 ms, absolute tolerances shall be the greater of  $\pm 0.1$  ms or  $\pm 30$  percent of the specified duration.

3. <u>Procedure</u>. The shock-testing apparatus shall be mounted on a sturdy laboratory table, or equivalent base, and leveled before use. The device shall be rigidly mounted or restrained by its case with suitable protection for the leads. The device shall be subjected to the specified number of blows in the specified direction. For each blow, the carriage shall be raised to the height necessary for obtaining the specified acceleration and then allowed to fall. Means may be provided to prevent the carriage from striking the anvil a second time. Electrical load conditions and measurements to be taken during the shock test, if applicable, shall be as specified. End-point measurements shall be as specified.

4. <u>Summary</u>. The following conditions shall be as specified in the applicable performance specification sheet or acquisition document:

- a. Acceleration and duration of pulse (see 2).

- b. Number and direction of blows (see 3).

- c. Electrical-load conditions, if applicable (see 3).

- d. Measurements during shock, if applicable (see 3).

- e. End-point measurements (see 3).

This page is intentionally left blank.

#### METHOD 2017.3

## DIE ATTACH INTEGRITY

1. <u>Purpose</u>. The purpose of this test method is to establish the integrity of the semiconductor die attachment to the package header or other substrate.

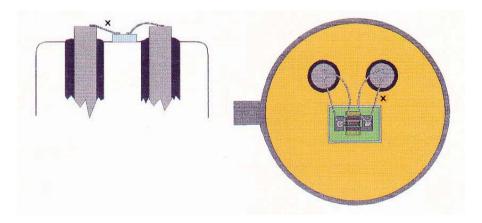

2. <u>Apparatus</u>. The test equipment shall consist of a force-applying instrument with an accuracy of ±5 percent of full scale or 50 grams, whichever is less. A circular dynamometer with a lever arm or a linear motion force-applying instrument may be used to apply the force required for testing. The test equipment shall have the following capabilities:

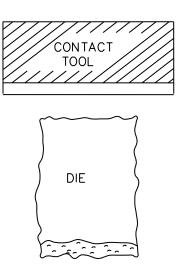

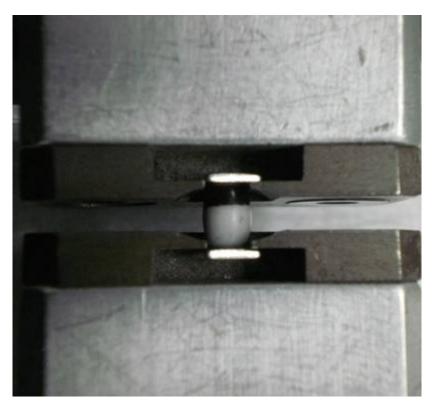

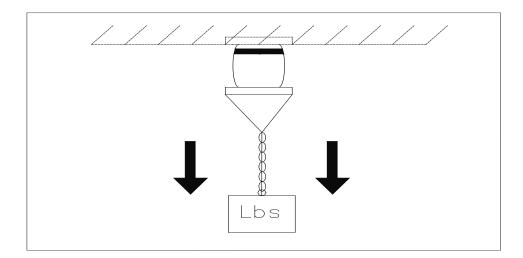

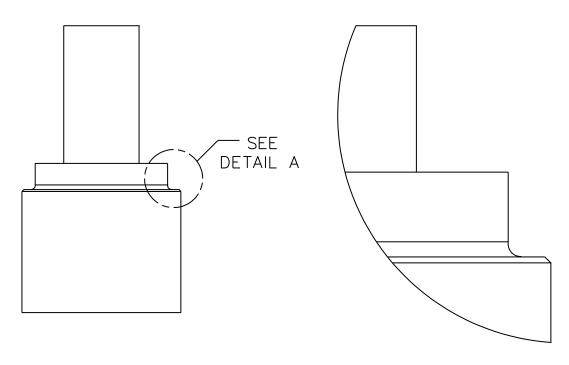

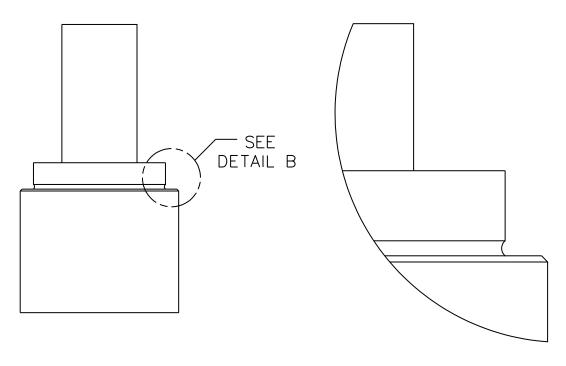

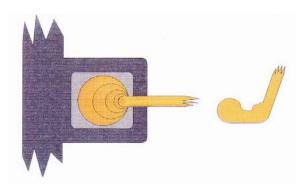

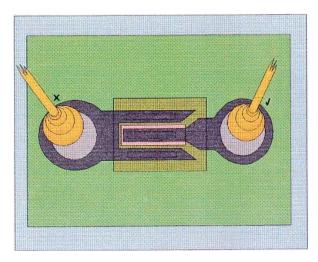

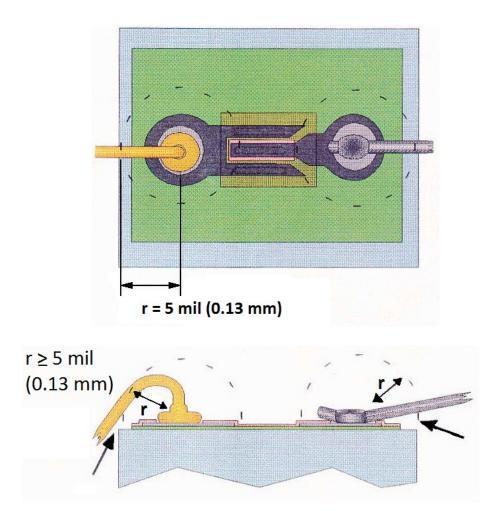

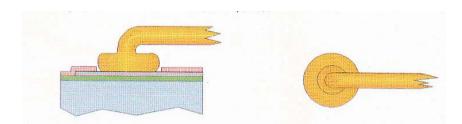

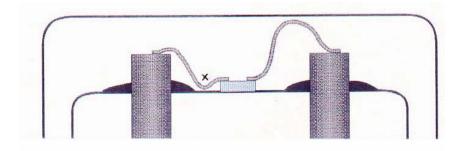

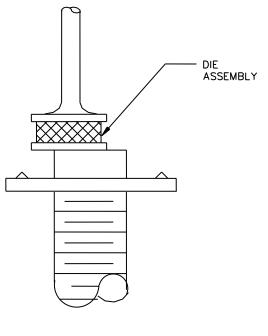

- a. A die contact tool which applies a uniform distribution of the force gradually to an edge of the die (see figure 2017–1).

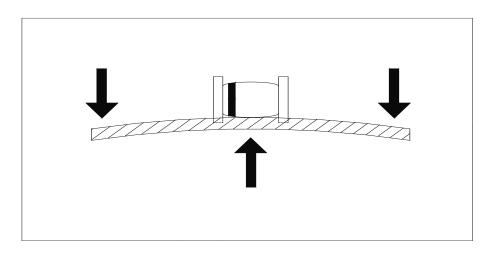

- b. Provisions to assure that the face of the die contact tool is perpendicular to the die mounting plane of the header or substrate.

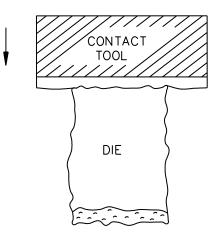

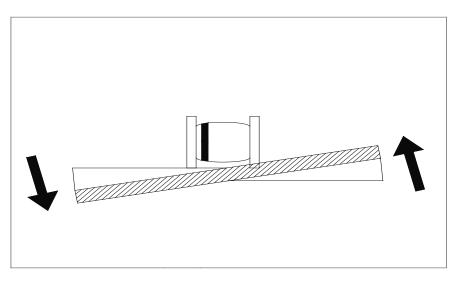

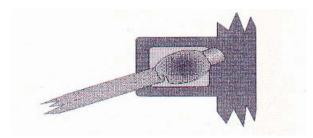

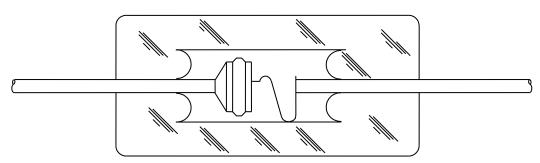

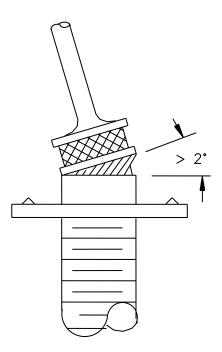

- c. A rotational capability, relative to the header/substrate holding fixture and the die contact tool, to facilitate line contact parallel to the edge of the die; the tool applying the force to the die shall contact the die edge from end-to-end (see figure 2017–2).

- d. A binocular microscope with a minimum magnification of 10X and sufficient lighting for visual inspection of the die and die contact tool interface during testing.

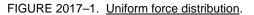

- e. Optional apparatus for devices with a die area less than 25.5 x 10<sup>-4</sup> square inches (1.645 mm<sup>2</sup>) instead of a calibrated instrument. Any hand held tool may be used. The general requirements of 2.a., 2.b., and 2.d. shall apply. The tool which shall apply a uniform perpendicular force to the edge of the die (see figures 2017–1, 2017–2, and 2017–3) and a microscope with a minimum magnification of 10X shall be used.

- f. Apparatus for test condition C: A hammer, chisel, or spring loaded punch are suitable.

- 3. <u>Test condition A die shear</u>. For die directly bonded to a header or substrate.

3.1 <u>Procedure</u>. The test shall be conducted as defined herein or to the test conditions specified in the applicable specification sheet consistent with the particular part construction. All die strength tests shall be counted and the specific sampling, acceptance, and added sample provisions shall be observed, as applicable. (This test shall be considered destructive.)

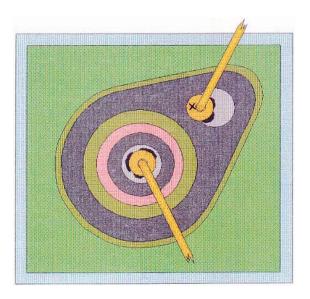

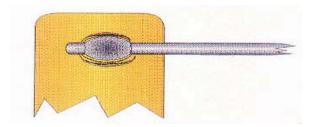

3.1.1 <u>Shear strength</u>. A force sufficient to shear the die from its mounting, or equal to twice the minimum specified shear strength (see figure 2017–4), whichever occurs first, shall be applied to the die using the apparatus of 2 above.

- a. When a linear motion force-applying instrument is used, the direction of the applied force shall be parallel with the plane of the header or substrate and perpendicular to the edge of the die being tested.

- b. When a circular dynamometer with a lever arm is employed to apply the force required for testing, it shall be pivoted about the lever arm axis and the motion shall be parallel with the plane of the header or substrate and perpendicular to the edge of the die being tested. The contact tool attached to the lever arm shall be at a proper distance to assure an accurate value of applied force.

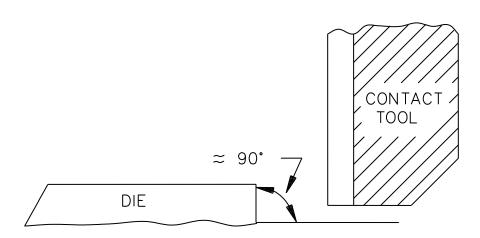

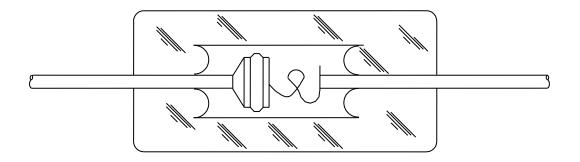

- c. The die contact tool shall apply a force gradually from zero to a specified value against an edge of the die which most closely approximates a 90 degree angle with the base of the header or substrate to which it is bonded (see figure 2017–3). For rectangular die, the force shall be applied perpendicular to the longer side of the die. When constrained by package configurations, any available side of the die may be tested if the above options are not available.

- d. After initial contact with the die edge and during the application of force, the relative position of the contact tool shall not move vertically such that contact is made with the header/substrate or die attach material. If the tool rides over the die, a new die may be substituted or the die may be repositioned, provided that the requirements of 3.1.3 are met.

#### 3.1.2 Criteria for device acceptability.

3.1.2.1 Failure criteria. A device will be considered a failure if the die bond shears as follows:

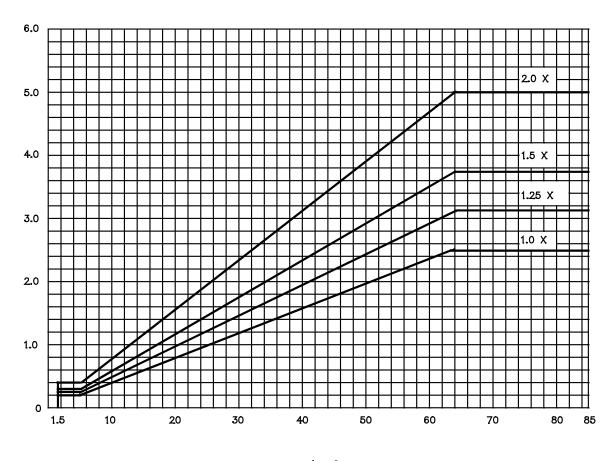

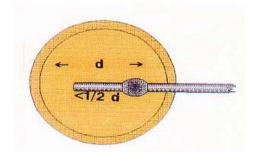

- a. With a force less than the minimum shear strength requirements specified on figure 2017-4 (1.0 X line).

- b. With a force less than 1.25 times (1.25 X line) the minimum shear strength requirements (1.0 X line) specified on figure 2017–4 and evidence of adhesion, of the die attach material, less than 50 percent of the die attach area. Evidence of adhesion shall be in the form of attach medium to the intended area on the substrate, the element or combination of both.

- c. With a force less than 1.5 times (1.5 X line) the minimum shear strength requirements (1.0 X line) specified on figure 2017–4 and evidence of adhesion, of the die attach material, less than 25 percent of the die attach area. Evidence of adhesion shall be in the form of attach medium to the intended area on the substrate, the element or combination of both.

- d. With a force less than 2.0 times (2.0 X line) the minimum shear strength requirements (1.0 X line) specified on figure 2017–4 and evidence of less than 10 percent adhesion of the die attach material. Evidence of adhesion shall be in the form of attach medium to the intended area on the substrate, the element or combination of both.

3.1.2.2 <u>Acceptance criteria</u>. A device will be considered acceptable if the die bond:

- a. Does not shear with a force equal to or greater than 2.0 times (2.0 X line) the minimum shear strength requirements (1.0 X line) specified on figure 2017–4.

- b. Shears with evidence of remaining semiconductor material equal to or greater than 50 percent of the die attach area regardless of the shearing force applied. (This criteria applicable only for devices with die area less than 25.5 x 10<sup>-4</sup> square inches (1.645 mm<sup>2</sup>).

NOTE: Residual semiconductor material attached in discrete areas of the die attach medium shall be considered as evidence of such adhesion.

3.1.2.3 <u>Separation categories</u>. When specified, the force required to achieve separation and the category of the separation shall be defined as:

- a. Shearing of the die with residual silicon remaining.

- b. Separation of die from die attach material.

- c. Separation of die and die attach material from package.

METHOD 2017.3

3.1.3 <u>Test condition A summary</u>. The following details shall be specified in the applicable performance specification sheet or acquisition document:

- a. The minimum die attach strength if other that shown on figure 2017-4.

- b. Test condition letter.

- c. Sample size and accept number.

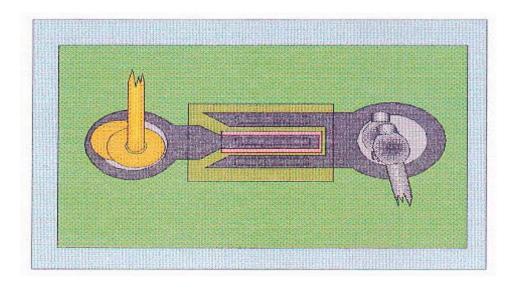

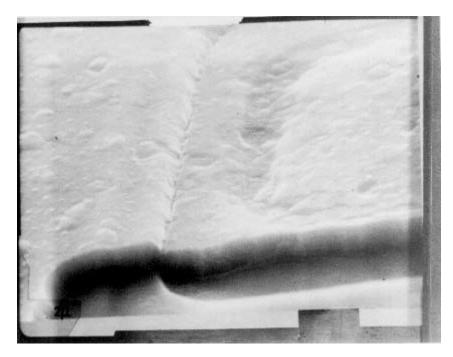

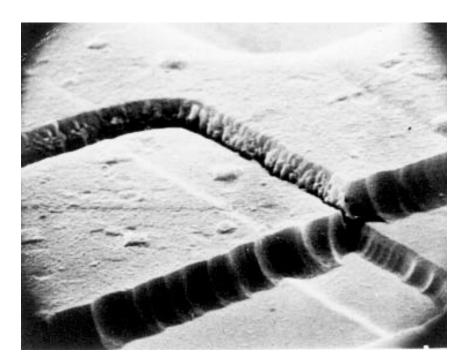

FIGURE 2017-2. Rotational capability.

METHOD 2017.3

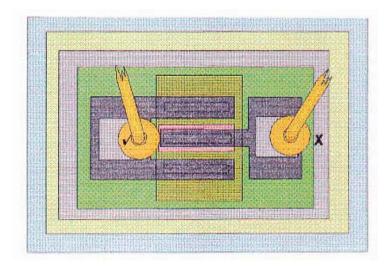

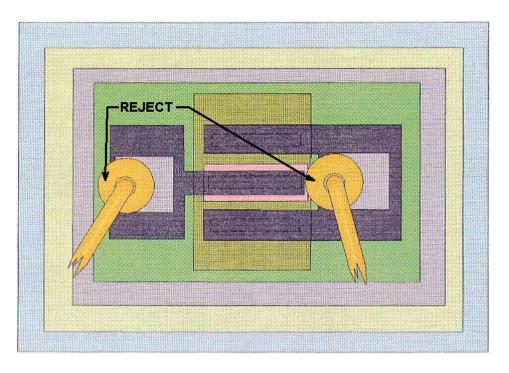

FIGURE 2017-3. Perpendicular force application.

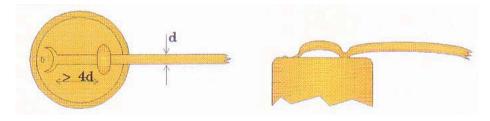

4. <u>Test condition B – mechanical impact</u>. Test condition B may be used on devices which have a metallurgical bond between a header or contact plate and the silicon die on only one side of the die and is to be used for those devices with a contact plate bonded to both sides of the die or to one side of the die with the other side bonded to a header. This method shall not be used for die with area less than  $25.5 \times 10^{-4}$  square inches (1.645 mm<sup>2</sup>).

# NOTES:

- 1. All die area larger than 64 x 10<sup>-4</sup> square inches (4.13 mm<sup>2</sup>) shall withstand a minimum force of 2.5 kg or a multiple there of.

- 2. All die area larger than or equal to 5 x 10<sup>-4</sup> square inches (0.32 mm<sup>2</sup>) but smaller than or equal to 64 x 10<sup>-4</sup> square inches (4.13 mm<sup>2</sup>) shall withstand a minimum force as determined from the chart of figure 2017–4. The chart is based on a force of 0.04 kg for every one ten-thousandth (10<sup>-4</sup>) square inch at (1X) level. Similarly, the required minimum force is 0.05 kg for every 10<sup>-4</sup> square inches (0.065 mm<sup>2</sup>) at (1.25X) level and is 0.08 kg for every 10<sup>-4</sup> square inches (0.065 mm<sup>2</sup>) at (2X) level.

- All die area smaller than 5 x 10<sup>-4</sup> square inches (0.32 mm<sup>2</sup>) shall withstand a minimum force (1.0X) of 0.04 kg/10<sup>-4</sup> square inches (0.04 kg/0.065 mm<sup>2</sup>) or a minimum force (2X) of 0.08 kg/10<sup>-4</sup> square inches (0.08 kg/0.065 mm<sup>2</sup>).

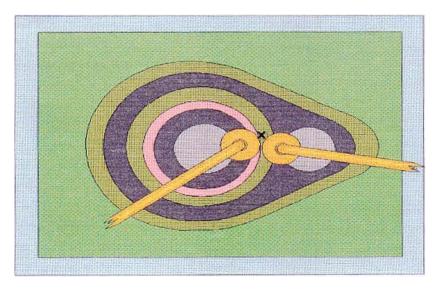

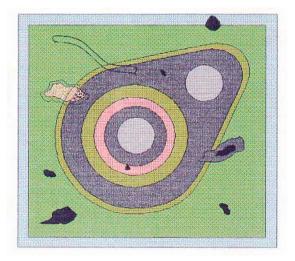

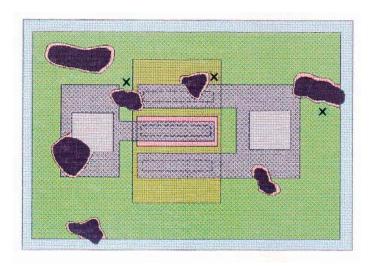

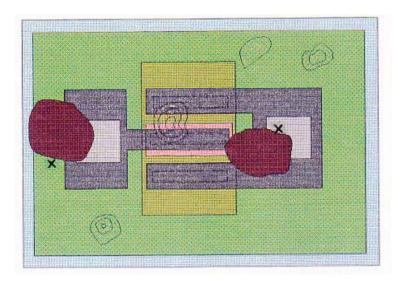

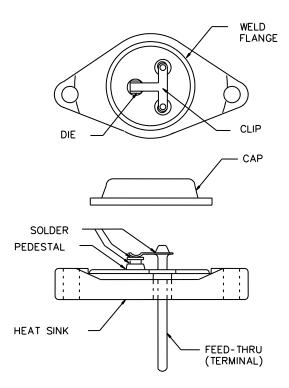

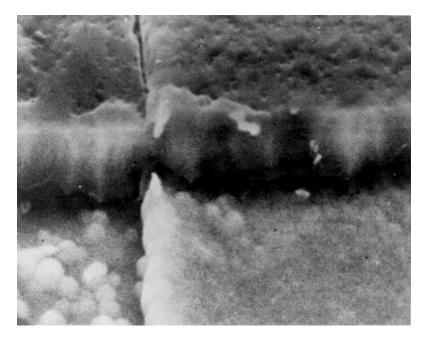

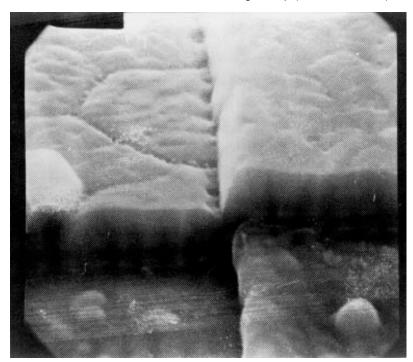

FIGURE 2017-4. Die shear strength criteria (minimum force versus die attach area).

4.1 <u>Procedure</u>. The die assemblies are placed on a suitable anvil. For die with a contact plate or header on only one side, the die is struck with a ball peen hammer such that the silicon is shattered. The silicon will not be adhered to those areas of the bond where solder, braze, or alloy voids exist and the voids will thus be visible. The contact plate or header can now be visually examined to determine the size and density of any voids. The size and density of the voids are compared to the established visual standards for acceptable die attachment. For die with both sides die attached (a contact plate on both sides or a header on one side and contact plate on the other) the die can be struck with a hammer on one contact plate or cleaved by striking with a chisel on the edge. If cleaved with a chisel, each side should be struck with a hammer to break free any voided silicon. Visual comparison to the standards is then done as above.

- 4.2 Precautions. The following precautions shall be observed during test:

- a. Use of a chisel or hammer can result in flying debris. Eye protection and protective clothing must be worn.

- b. Breaking of the silicon can result in the exposure of sharp edges. Care in handling must be taken to avoid injury.

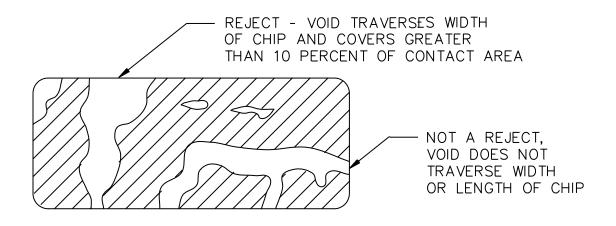

- 4.3 Failure criteria. A device will be considered a failure if:

- a. Any single void has an area greater than 3 percent of the total die area.

- b. The sum total of all void areas exceeds 6 percent of the total die area.

4.4. <u>Test condition B summary</u>. The following details shall be specified in the applicable performance specification sheet or acquisition document:

- a. A test condition letter.

- b. Sample size for each batch or run.

#### METHOD 2026.12

#### SOLDERABILITY

1. <u>Purpose</u>. The purpose of this test method is to provide a referee condition for the evaluation of the solderability of terminations (including leads up to .125 inch (3.18 mm) in diameter) that will be assembled using tin lead eutectic solder. This evaluation is made on the basis of the ability of these terminations to be wetted and to produce a suitable fillet when coated by tin lead eutectic solder. These procedures will test whether the packaging materials and processes used during the manufacturing operations process produce a device that can be successfully soldered to the next level assembly using tin lead eutectic solder. A preconditioning test is included in this test method which degrades the termination finish to provide a guardband against marginal finishes.

2. <u>Procedure</u>. The solderability test shall be performed in accordance with the current revision of J–STD–002 and herein. The following details and exceptions shall apply.

2.1 <u>Contractual agreements</u>. The contractual agreements statement in J–STD–002 shall not apply. Any exceptions to the requirements specified in J–STD–002 and this test method shall be documented in the individual military procurement document or approved by the procuring military activity.

2.2 <u>Conditioning requirements</u>. Unless specific exception has been granted in the contractual agreement, all semiconductor devices shall undergo high humidity (steam) preconditioning.

2.2.1 <u>Steam conditioning</u>. Before the application of flux and subsequent solderability testing, test specimens shall be conditioned at a steam temperature which is 7°C (12.6°F) below the local boiling point. All test specimens shall be placed into the steam conditioning chamber such that no test specimens have their leads or terminations touching, and that condensation forming will drain away from the lead or terminations to the package body. Test specimens shall not be stacked in a manner which restricts their surface exposure to steam nor shall they be placed closer than .39 inches (10 mm) from the outer chamber walls, and shall not touch the inner container walls. In addition, no portion of the test specimen shall be less than 1.57 inches (40 mm) above the water level.

2.2.2 <u>Steam conditioning apparatus</u>. The steam conditioning chamber shall be constructed of non-corrodible materials such as borosilicate glass, quartz glass, stainless steel or PTFE. The test specimen holder shall be non-reactive to prevent galvanic corrosion. The container shall be insulated. A safe means to prevent excessive pressure and a means of maintaining adequate water level shall be provided. Neither shall cause the vapor to cool below the specified temperature. Condensate shall drip freely back to the water. Care shall be taken to minimize contact between the condensate and the specimens.

2.2.3 <u>Post conditioning drying</u>. After steam conditioning is complete, test specimens shall be immediately removed from the conditioning chamber and ambient air dried. Solderability testing shall be performed within 72 hours of removal from the conditioning chamber.

2.3 Coating durability.

- a. Category 2 For stranded wire (1 hour ±5 minutes steam preconditioning with insulation removed).

- b. Category 3 For all other components (8 hours ±15 minutes steam preconditioning).

2.4 Test method. The test method from J-STD-002 shall be used as follows:

- Test A For through hole mount and surface mount leaded components, solid wire less than .045 inch (1.14 mm) diameter and stranded wire 18 AWG or smaller. If not otherwise specified in the procurement document, angle of immersion for surface mount leaded components shall be 90 degrees.

- Test B For surface mount leadless components.

- Test C For lugs, tabs, terminals, solid wire greater than .045 inch (1.14 mm) diameter and stranded wire greater than 18 AWG.

3. <u>Summary</u>. The following details shall be specified in the applicable performance specification sheet or acquisition document:

- a. Depth of immersion if other than specified.

- b. Angle of immersion for surface mount leaded components, if other than 90 degrees.

- c. Measurements after test, where applicable.

#### METHOD 2031.5

# RESISTANCE TO SOLDERING HEAT