MIL-D-81347C(AS) <u>13 March 1974</u> SUPERSEDING MIL-D-81347B(AS) 12 August 1971

# MILITARY SPECIFICATION

#### DATA ANALYSIS PROGRAMMING GROUP

## AN/AYA-8B

This specification has been approved by the Naval Air Systems Command, Department of the Navy

1. SCOPE

1.1Scope- The equipment \* covered by this specification shall allowcommunication between Computer CP-901/ASQ-114 and the computer driven peripheral equipments.

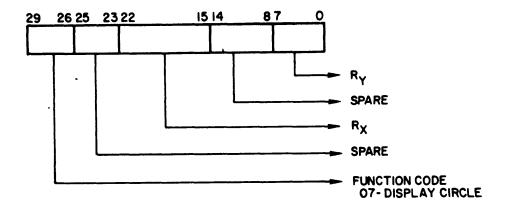

1.2 <u>Classification</u> - The equipment covered by this specification shall

| Type Designation                                                       | Applicable Paragraph |

|------------------------------------------------------------------------|----------------------|

| Data Amlysis Logic Unit MX-8023A/AYA-8 (Logic Unit 1)                  | 3.5.1                |

| Data Analysis Logic Unit MX-8024A/AYA-8 (Logic Unit 2)                 | 3.5.2                |

| Data Analysis Logic Unit MX-8034/AYA-8 (Logic Unit 3)                  | 3.5.3                |

| Data Analysis Logic Unit MX-9360/AYA-8B (Logic Unit 4)                 | 3.5.4                |

| Control-Indicator C-7627(P)/AYA-8 (Universal Keyset)<br>(3 per system) | 3.5.5                |

| Control-Indicator C-7629/AYA-8 (Pilot's Keyset)                        | 3.5.5                |

| Control-Indicator C-7628/AYA-8 (Ordnance Panel)                        | 3.5.5                |

| Electrical Test Panel SB-3152/AYA-8 (Armament/Ordnam<br>Test Panel)    | 3.5.5                |

1.3 <u>Associated Equipment</u> - This equipment shall operate with the associated equipment listed in 6.7. Magnetic Tape Transport RD-319A/AYA-8 is identified as a part of Data Analysis Programming Group AN/AYA-8B but is supplied separately and is covered by a separate specification. Therefore it is treated as an associated equipment and listed in 6.7.

\* Data Analysis Programming Group AN/AYA-8B is commonly referred to as Data Processing System or DPS.

# 2. APPLICABLE DOCUMENTS

2.1 General. - The following documents form a part of this specifi-. cation to the extent specified herein. Listed are the issues of the documents in effect for the previous procurement. However, in lieu of the issue listed, the contractor shall use the latest issue in effect of these documents where feasible. If the use of the latest issue will affect design performance, or interchangeability of any replaceable part, then the issue of the document listed below shall be used.

## **SPECIFICATIONS**

| <u>Military</u>               |                                                                                                                                               |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| MIL-C-3608A<br>22 March 1969  | Connectors, Coaxial Radio Frequency Series BNC and Associated Fittings, General Specification for Use                                         |

| MIL-E-5400H<br>1 June 1965    | Electronic Equipment, Aircraft, General Specifications for                                                                                    |

| MIL-T-5422E<br>15 Nov 1961    | Testing, Environmental, Aircraft Electronic Equipment                                                                                         |

| MIL-F-5591B<br>19 Nov 1963    | Fasteners, Panel                                                                                                                              |

| MIL-I-6181D<br>25 Nov 1959    | Interference Control Requirements, Aircraft Equipment                                                                                         |

| MIL-C-6781B<br>13 Sept 1960   | Control Panel, Aircraft Equipment, Racker Console Mounted                                                                                     |

| MIL-M-7793C<br>14 Aug 1961    | Meter, Time Totalizing                                                                                                                        |

| MIL-E-17555F<br>5 Mar 1965    | Electronic and Electrical Equipment and Associated Repair<br>Parts, Preparation for Delivery of                                               |

| MIL-T-18303A<br>1 May 1963    | Test Procedures: Preproduction and Inspection, for Aircraft Electronic Equipment, Format for                                                  |

| MIL-N-18307C<br>1 Oct 1958    | Nomenclature and Nameplates for Aeronautical Electronic and Associated Equipment                                                              |

| MIL-S-19500D<br>11 May 1964   | Semiconductor Devices, General Specification for                                                                                              |

| MIL-P-23377A<br>30 Sept 1964  | Primer Coating; Epoxy-Polyamide, Chemical and Solvent Resistant                                                                               |

| MIL-F-25173A<br>23 Nov 1959   | Fasteners, Control Panel, Aircraft Equipment                                                                                                  |

| MIL-C-26482D<br>10 May 1966   | Connector, Electric, Circular, Miniature, Quick Disconnect                                                                                    |

| MIL-C-81511<br>15 Mar 1967    | Connectors, Electrical, Circular, High Density, Quick<br>Disconnect, Environment Resisting, General Specifications for                        |

| Naval Air Systems Command     |                                                                                                                                               |

| AR-34<br>26 Mar 1969          | Failure Classification for Reliability Testing, General Requirements for                                                                      |

| WR-101<br>Part I -28 Feb 1966 | Weapon Requirements for Advanced ASW Electronic Systems<br>Part I - Electromagnetic Control Requirements for Advanced<br>ASW Avionics Systems |

| Part II -3 Mar 1966           | Part II - Selection and Testing of Microelectronic Circuits for<br>Advanced ASW Avionic Systems                                               |

| WS-8506<br>15 Dec 1966        | Requirements for Digital Computer Program Documentation                                                                                       |

# STANDARDS

| 3 611 | • .    |

|-------|--------|

| N/11  | itary  |

| 11111 | Ital y |

| MIL-STD-454C<br>15 Oct 1970   | Standard General Requirements for Electronic Equipment            |

|-------------------------------|-------------------------------------------------------------------|

| MIL-STD-470<br>21 Mar 1966    | Maintainability Program Requirements (for Systems and Equipment)  |

| MIL-STD-471<br>15 Feb 1966    | Maintainability Demonstration                                     |

| MIL-STD-701E<br>30 Dec 1964   | Preferred and Guidance List of Semiconductor Devices              |

| MIL-STD-704A<br>9 August 1966 | Electric Power, Aircraft Characteristics and Utilization of       |

| MIL-STD-781A<br>10 Dec 1965   | Reliability Tests, Exponential Distribution                       |

| MIL-STD-785<br>30 June 1965   | Requirements for Reliability Program (for System and Equipment)   |

| MIL-STD-794<br>10 Mar 1965    | Parts and Equipment, Procedures for Packaging and Packing of      |

| MS-17322C                     | Meter, Time Totalizing, 115Volt -400 Cycle                        |

| MS-25212C<br>25 Aug 1960      | Control Panel, Console Type, Aircraft Equipment, Basic Dimensions |

| MS-25213A<br>25 Aug 1960      | Control Panel, Aircraft Equipment, Typical Installation           |

| FED-STD-595<br>1 Mar 1956     | Color                                                             |

|                               |                                                                   |

Naval Air Systems Command

EI-515A

Avionics Installation Instructions for Data Analysis Programming Group AN/AYA-8B

2.1.1 Availability of Documents -When requesting specifications, standards, drawings, and publications, refer to both title and number. Copies of this specification and applicable specifications required by contractors in connection with specific procurement functions may be obtained upon application to the Commanding Officer, Publications and Forms Center (NPFC 1032), Code 105, 5801 Tabor Avenue, Philadelphia, Pennsylvania 19120.

3. **REQUIREMENTS**

3.1

duction testing.

Preproduction - The specification makes provision for prepro-

3.2 <u>Parts and Materials</u> - In the selection of parts and materials, fulfillment of major design objectives shall be the prime consideration. In so doing the following shall govern: (1) Microelectronic devices shall conform to requirements

specified in WR-101, Part II.

Specification MIL-E-5400.

(2) Other parts and materials requirements shall conform to

(3) Nonrepairable subassemblies, as outlined in Specification MIL-E-5400, shall be used when practicable. The general size of the subassembly and the amount of circuitry to be included therein shall be approved by the procuring activity. Nonrepairable subassemblies must be reliable.

(4) When previously produced models of this equipment did not use repairable subassemblies, the design shall not be changed to employ nonrepairable assemblies without the approval of the procuring activity.

3.2.1 <u>Nonstandard Parts and Materials Approval</u> - Approval for the use of nonstandard parts and materials (including electron tubes, transistors and diodes) other than microelectronic devices shall be obtained as outlined in Specification MIL-E-5400. Microelectronic devices shall be approved as outlined in WR-101, Part II, Amendment 1.

3.2.2 <u>Electron Devices</u> - Transistors and diodes shall be chosen and applied as outlined in Specification MIL-S-19500 and MIL-STD-701.

3.2.3 <u>Maintenance Modules</u> - The electronic portions of the equipment shall be divided into maintenance modules as defined in 3.3.7.2.1.

3.3 <u>Design and Construction</u> - The equipment shall conform with all the applicable requirement specification MIL-E-5400 for design, construction and workmanship, except as otherwise specified herrein

\*3.3.1 <u>Total Weight</u> - The total weight of the DPS equipment shall be minimum consistent with good design and shall not exceed 776 pounds.

3.3.2 <u>Reliability</u>

3.3.2.1 <u>Reliability Program</u> - The contractor shall establish and conduct a reliability program in accordance with MIL-STD-785.

3.3.2.2 <u>Operational Stability</u> - The equipment shall operate with satisfactory performance for the life of the equipment without the necessity for readjustment of any control, which are inaccessible to the operator during normal use.

3.3.2.3 <u>Operating Life</u> - The equipment shall have a total operating life of 50,000 hours with reasonable servicing and replacement of parts. Parts requiring scheduled replacement and the replacement interval shall be specified by the contractor.

3.3.2.4 <u>Specified Mean-Time-Between-Failures (MTBF)</u> - The specified Mean-Time-Between-Failures (MTBF) for theb respective units of Data Analysis Programming Group AN/AYA-8B when tested and accepted as outlined under the requirements of 4.4.3 shall be as follows:

| Logic Unit I      |      |       | 800 nours    |

|-------------------|------|-------|--------------|

| Logic Unit 2      |      |       | 800 hours    |

| Logic Unit 3      |      |       | 800 hours    |

| Logic Unit 4      |      |       | 600 hours ** |

| Universal Keyset  |      |       | 110 hours    |

| Pilot's Keyset    |      |       | 440 hours    |

| Ordnance Panel    |      |       | 270 hours    |

| Armament/Ordnance | Test | Panel | 930 hours    |

|                   |      |       |              |

\*\*(The Drum subassembly of the Magnetic Drum Memory requiring depot maintenance shall have an MTBF of 1500 hours or greater.)

3.3.2,5 <u>Time Totalizing Meter</u> - The equipment shall contain time totalizing meters in accordance with Specification MIL-M-7793. A time totalizing meter type MS-17322-6A shall be included in each separate item, except panels and keysets. Logic Unit 4 shall have two meters. In Logic Unit 4 a separate meter shall be supplied for the Magnetic Drum Memory subassembly of the Drum Auxillary Memory Subunit.

3. 3.3

3.3.3.1 <u>Cables</u> - The equipment shall provide for the use of cables in accordance with specification WR- 101, Part 1.

Cabling and Connections

3.3.3.2 <u>Interconnection Cabling</u> - The equipment shall be capable of satisfactory operation using external wiring in accordance with the applicable requirements of Specification WR-101 Part 1, except as modified herein, and the detailed requirements of EI-515. External cables and that portion of the connectors attached to the cables shall not be supplied as part of the equipment.

3.3.3.2.1 <u>Twisted Pair Cable</u> - Twisted pair cable shall be in accordance with EI-515. In twisted pair transmission neither lead shall be grounded on the receiving end.

3.3.3.2.2 <u>Triaxial Cable</u> - All triaxial cable shall be Amphenol 421-033 or equivalent in accordance with EI-515. In triaxial signal transmissions the inner shield shall be grounded on the transmitting end only.

3.3.3 .2.3 <u>Single Wire Cable</u> - In signal wire transmissions the reference lead supplied by the signal source shall not be grounded on the receiving end.

3.3.3 .2.4 <u>Number of Wires per Terminal</u> - Attachment of wires and leads shall be in accordance with Requirement 5 of MIL-STD-454 except that the number of wires per terminal shall be limited only to the extent that no wires shall be wrapped on another wire.

3.3.3.3 <u>Connectors</u> - The equipment shall use external connectors in accordance with the requirements of Installation Instructions EI-515. Triaxial connectors shall be hermetically sealed triaxial BNC type receptacles conforming to the requirements outlined in paragraph 3 of MIL-C-3608 except that the part shall have an additional contact between the inner and outer contact. Protective locking caps in accordance with 3.4.6 of MIL-C-81511 will not be required.

3.3.4 <u>Control Panels</u> - All rack or console mounted control panels shall conform to the applicable requirements of Specification MIL-C-6781 except that edge-lighting shall not be required. The configuration of all control panels must be approved by the procuring activity prior to preproduction testing.

3.3.5 <u>Interchangeability</u> - The equipment shall meet the interchangeability requirements of Specification MIL-E-5400.

3.3.6 <u>Interference Control</u> - The equipment shall conform with all of the requirements of WR-101, Part I for design, construction and workmanship, except as specified herein. A Control Plan will be prepared in accordance with WR-101, Part I.

3.3.7

#### <u>Maintainability</u>

3.3.7.1 <u>Maintainability Program</u> - The contractor shall establish and conduct a maintainability program in accordance with MIL-STD-470 and MIL-STD-471 Method 2. All maintenance actions shall be capable of being performed by a technician with a comprehensive ability level as follows:

(1) Civilian Education - High school graduate or equivalent.

(2) Technical Training - Navy, Class A technicians school

appropriate to the maintenance task

addition to technical training.

(3) Experience - Two (2) years of technical experience in

3.3.7.2 <u>Maintainability Definitions</u> - The following definitions shall apply to the terminology as used in this specification.

3.3.7.2.1 <u>Maintenance Module</u> - A maintenance module shall be defined as the least complex segment of each part of the DPS which is capable of being removed and reinserted within the DPS through the use of a connector or captive mounting bolts/screws rather than by soldering (brazing) or welding.

## 3.3.7.2.1.1 <u>Maintenance Module Requirements</u>

(1) A module shall be packaged in such form that it can be plugged into and removed from its subunit (functional group of maintenance modules) or assembly without the use of special tools.

(2) A maximum of 46 different modules shall be used in Logic Units 1, 2, 3 and 4, exclusive of their power supplies and the Magnetic Drum Memory Subassembly.

3.3.7.2.2 <u>Subunit</u> - A subunit is a functional group of maintenance modules. Each subunit containing its associated maintenance modules shall be either a single plug-in, removable assembly, or due to size or packaging limitations, a number of plug-in, removable assemblies.

| 3.3.7.2.3 | Subunit Types          | - The types | of subunits | shall be | as specified he | erein. |

|-----------|------------------------|-------------|-------------|----------|-----------------|--------|

| 3.3.7.3   | <u>Maintainability</u> | Requiremen  | <u>ts</u>   |          |                 |        |

3.3.7.3.1 <u>Maintainability Philosophy</u> - To provide for increased system effectiveness, maintainability y shall receive equal considerate ion with such factors as cost, physical parameters, and reliability. The maintenance philosophy for avionics equipment is that of fault isolation to and repair by replacement of individual modules without removing the units from the operational environment in the aircraft. Where feasible, fault isolation shall be computer initiated utilizing a diagnostic program. Where not feasible, equipments shall provide self-test features and readily accessible test points to accommodate standard test equipment affording fault isolation to the individual replaceable module.

- 3.3.7.3.2 Fault Detection and Isolation

- 3.3.3.2.1 Operator Methods

Three methods of fault detection and isolation for each subunit of the DPS (excluding power supplies and Maintenance Control Panels) and associated peripherals shall be provided:

- (1) Integration Test

- (2) System Test Program

- (3) Maintenance Control Panel Tests

The associated peripherals shall be defined as the external devices to which the subunit interface. The associated peripherals for the DPS subunits are defined as follows: TACCO Tray, Sensor Station 3 Control Tray, Universal Keysets, Pilot Keyset, Ordnance Panel, ARO Display, Armament/Ordnance Test Panel, Magnetic Tape Transport, TACCO and Sensor Station 3 Multipurpose Displays, Pilot Display, Auxiliary Display, and Omega.

#### 3.3.7.3.2.2

#### Integration Tests

The Integration Tests shall utilize the computer, the Maintenance Control Panel and the subunit external test points for the detection of malfunctions in the communication paths between equipments. The Integration Tests shall consist of a series of short programs or subroutines, operator initiated, interspersed by manual checks to exercise all communication paths between the computer, DPS, and associated peripherals. The Integration Test snail be used primarily during the initial integration of a given equipment into the total system and will therefore require a high degree of operator training. The contractor shall provide Integration Test Specifications for each subunit (excluding power supplies) of the DPS.

The Integration Test Specifications shall be submitted to the

Procuring Agency for approval.

3.3.7.3.2.3

System Test Program

The System Test Program shall utilize the computer for on-line fault detection and isolation of the DPS subunits and associated peripherals. The System Test program shall be divided into the following sections:

(1) System GO/NO-GO Tests (SYGNOG)

(2) Diagnostic Test

3.3.7.3.2.3.1 System GO/NO-Go Tests (SYGNOG)

The SYGNOG tests shall utilize the computer for a GO/NO-GO check of each subunit. The SYGNOG test shall test every logic element of the subunit in so far as possible. The only limitations imposed on the test will be those required for safety. The operator shall be the initiator of the test and will be available for visual monitoring of faults (which the computer cannot detect ) and the activating of those computer inputs which require manual operation. The contractor shall provide a SYGNOG test specification for each subunit of the DPS.

The SYGNOG test shall be documented in accordance with WS-8506. The primary purpose of the SYGNOG test shall be to detect the presence of faults and reform the operator of operational readiness of the subunit under test. The SYGNOG test for each DPS subunit shall include the associated peripheral to which the DPS subunit interfaces.

The SYGNOG test documentation shall be submitted to the Pro-

curing Agent y for approval.

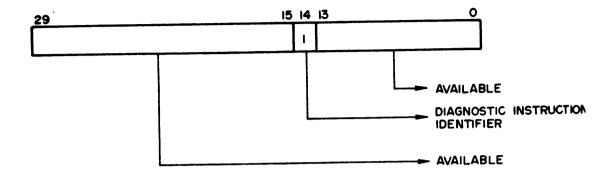

3.3.7.3.2.3.2

Diagnostic Tests

The Diagnostic Program shall utilize the computer to diagnose equipment malfunctions for each subunit of the DPS (excluding power supply and Maintenance Control -Panel subunits). The Diagnostic Program shall be capable of delineating any subunit failure to such a level that any further isolation and replacement of the failed module may be accomplished in 15 minutes or less for 50% of such failures and in 30 minutes or less for 95% of such failures. To the extent permitted by the characteristics of the subunit, the Diagnostic Program shall satisfy the following requirements:

(1) <u>Comprehensive</u> - Every logical element shall be tested in all of its functions within the limits of the Diagnostic Hardware constraint.

(2) <u>Automatic</u> - Operator intervention shall be held to a minimum. To satisfy this requirement, test loops should be included in the design of those subunits which receive data from and transmit data to the computer. The Test Loops shall permit the computer to selectively monitor the performance of the logic elements in the subunit for the purposes of fault detection and isolation. The criterion to be used in the design of the Test Loops is as follows: The amount of hardware for the Test Loops shall not exceed 15% of the total hardware for the unit. A computer input channel shall be assigned to Logic Unit 3 for monitoring of the test loops by the Diagnostic Programs. The Diagnostic specifications module for each subunit of the DPS shall include the peripheral equipment to which it interfaces.

The Diagnostic Program specifications for each subunit of the DPS shall be in accordance with WS-8506 and shall be submitted to the Procuring Agent y for approval.

3.3.7.3.2.4

## Maintenance Control Panel Tests

The Maintenance Control Panel Test shall provide the Off-Line maintenance capability for the DPS. Maintenance Control Panel Tests shall provide an example of detailed operating procedures for the Maintenance Control Panel, test description for each subunit, library of normal operation codes, test codes, and test point waveforms for the normal operation in order to provide a functional check of each subunit. The goal of the MCP tests shall be to provide sufficient documentation to enable a Maintenance Technician to analyze the problem and formulate his own detailed detection and isolation procedures. The contractor shall provide a Maintenance Control Panel test for each subunit (excluding power supplies and the Maintenance Control Panel Subunit) of the DPS. (The MCP is used as a tool to test the Logic Unit proper, but has no self-test capability.) The tests shall include Universal Keysets, Pilot Keyset, Ordnance Panel, TACCO Control Tray, Sensor Control Tray, Armament/Ordnance Panel and Magnetic Tape Transport in addition to all logic subunits except Power Supplies. The use of the peripheral equipments not listed herein may be used as an aid to the technician for the purpose of monitoring outputs and stimulating inputs to each DPS subunit as needed. The Maintenance Control Panel tests shall be included as part of the Organizational Maintenance Instruction Manuals for each Logic Unit and shall be validated and approved as such.

3.3.7.3.3 <u>Test Point Requirement</u> - Any test points required shall accommodate general purpose test equipment, i. e., multimeter or oscilloscope probes. In the event test points cannot accommodate standard probes, use of adapters will be permitted. These adapters are to be provided with and secured to the unit.

3.3.7.3.4 <u>Special Support Equipment (SSE)</u> - There shall be no special support equipment for support of the equipment except as expressly authorized by the procuring activity.

3.3.8 <u>Nomenclature and Nameplates</u> - Nomenclature assignment and nameplate approval for equipment identification shall be in accordance with Specification MIL-N-18307.

3.3.9 <u>Standard Conditions</u> - The following conditions shall be used to establish normal performance characteristics under standard conditions and for making laboratory bench tests.

| Temperature            | Room ambient (25°C ±5°C)                 |

|------------------------|------------------------------------------|

| Altitude               | Normal Ground                            |

| Vibration              | None                                     |

| Humidity               | Room ambient up to 90% relative humidity |

| Input Power<br>Voltage | 115 ±1.0 VAC, 3 phase 400 Hz ±1%         |

3.3.10 <u>Service Conditions</u> - The equipment shall operate satisfactorily under any of the environmental service conditions or reasonable combination of these conditions as specified in Specification MIL-E-5400 for Class 1AX equipment, except as modified herein.

3.3.10.1 <u>Vibration</u> - The equipment shall operate satisfactorily when subjected to the vibration requirements of MIL-E-5400 Curve I from 5 to 32 Hz and  $\pm 2$  g from 32 to 500 Hz.

3.3.10.2 <u>Attitude</u> - The equipment shall operate satisfactorily in all attitudes and orientations within  $\pm 90^{\circ}$  of its normal mounting orientation.

3.3.10.3 <u>Fungus Treatment</u> - Equipments shall be fungus-proofed by selection of parts and materials that are non-nutrient for fungus, or the parts and materials shall be so treated prior to their use in the equipment that over-all spraying of the equipment is not necessary.

# 3.3.10.4

# Explosion Proofing Not required.

3.3. 10.5 <u>Temperature</u> - The equipment shall operate as specified herein from -25°C to and including +55°C. The equipment shall also operate as specified for tests above +55°C per MIL-T-5422 except for the Drum Auxiliary Memory Subunit (DAMS) of Logic Unit 4 which shall not be required to meet the DAMS error rate requirements. However, no damage or degradation shall occur to the DAMS during high temperature MIL-T-5422 tests. From below -25°C to -54°C the equipment shall not be required to meet specification performance requirements; however, no damage or degradation shall occur to the equipment within the -25°C to -54°C limits.

3.3.10.6 <u>Altitude</u> - The equipment shall operate satisfactorily up to a maximum altitude of 15,000 feet.

3.3.11 <u>Warm-Up Time</u> - The time required for the equipment to warm up prior to operation shall be kept to a minimum and shall not exceed 0.5 minutes from  $0^{\circ}$  to and ineluding +55°C and 5 minutes from less than 0°C to and including -25 'C.

3.3.12

#### Power

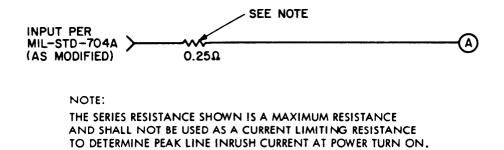

3.3.12.1 Primary Input Power Requirements - The equipment shall meet all applicable requirements of MIL-STD-704 and shall give specified performance from the following power sources with characteristics as defined in MIL-STD-704 having limits as modified herein. The equipment shall operate within the bounds of limits 2 and 3 of Figure 3 of MIL-STD-704 except that the lower limit of curve 3 shall not fall below 80 volts. Operational malfunction may occur when the input voltage exceeds the above limits but remains within limits 1 and 4 of Figure 3 of MIL-STD-704. However, no damage shall be suffered by the equipment under transient conditions defined herein. Normal operation shall autoctmatically be resumed upon return of the input voltage to levels within limits 2 and 3 as modified herein. The power required shall not exceed the following specified amounts.

(1) AC Power (Three-Phase) 115/200 V, Category B

| Logic Unit 1      | 588 VA |

|-------------------|--------|

| Logic Unit 2      | 609 VA |

| Logic Unit 3      | 609 VA |

| Logic Unit 4      | 810 VA |

| Universal Keyset  | 24 VA  |

| Pilot's Keyset    | 24 VA  |

| Ordnance Panel    |        |

| Armament/Ordnance |        |

| Test Panel        | 78 VA  |

(2) AC Power (Single Phase) 115 V, Category B

| Logic Unit 1          | 30.5 VA |

|-----------------------|---------|

| Logic Unit 2          | 30.5 VA |

| Logic" Unit 3         | 30.5 VA |

| Logic Unit 4          | 30.5 VA |

| Universal Keyset (es) | 77 VA   |

| Pilot's Keyset        | 50 VA   |

| Ordnance Panel        | 22 VA   |

| Armament/Ordnance     |         |

| Test Panel            |         |

3.3.12.1.1 <u>AC Power</u> - The equipment shall operate on an input voltage of 115 volts, line to neutral, 200 volts line to line, three phase 400 Hz as described in MIL-STD-704 Category B mode of operation except as modified herein.

3.3.12.1.2 <u>AC Over Voltage</u> - The input voltage transients shall remain within limits 1 and 2 of MIL-STD-704, Figure 3, for normal and abnormal operating conditions.

3.3.12.1.3 <u>AC Under Voltage</u> - The input voltage transients shall remain within limits 3 (as modified herein) and 4 of MIL-STD-704, Figure 3, for normal and abnormal operating conditons.

3.3.12.1.4 Loss Of Power - No damage shall result from accidental or deliberate stoppage of electrical power to the equipment regardless of the time in its operating cycle that such a stoppage should occur, and regardless of the time interval that elapses before power is restored.

3.3.12.1.5 <u>DC Power</u> - The use of 28 Volts DC aircraft power is specifically prohibited, except where specified as a requirement.

3.3.12.2 <u>Power Supply Subunit</u> - Each unit of the system shall have a power supply subunit which shall meet the requirements of MIL-STD-704, as modified herein.

3.3.12.2.1 <u>Power Control Switch</u> - A power control switch for activating and deactivating each power supply shall be supplied, except for keysets and panels.

3.3.12.2.2 <u>Overload Protection</u> - The power supply shall be protected from external overload conditions including short circuiting.

3.3.12.2.3 <u>Over Voltage Protection</u> - The power supply shall provide over voltage protection to the DPS under both normal and abnormal operation conditions. When normal operation is affected by an over voltage condition, indication of such a condition shall be provided.

3.3.12.2.4 <u>Under Voltage Protection</u> - The power supply shall provide under voltage protection to the DPS for both normal and abnormal operating conditions. When normal operation is affected by an under voltage condition, indication of such a condition shall be provided.

| 3.3.12.2.5 | <u>Power Supply Or</u><br><u>Memory)</u> | utput Conditions (Excluding the Magnetic Drum |

|------------|------------------------------------------|-----------------------------------------------|

| Voltage    | <b>Regulation</b>                        | DPS Operating Limits                          |

| +5 VDC     | $\pm 5\%$                                | ± 1 10%                                       |

| -10 VDC    | ±5%                                      | ± 10%                                         |

3.3.12.2.6 <u>Normal Operation</u> - The equipment shall operate under normal electric-system operation of MIL-STD-704, Section 6 except as specified herein.

3.3.12.2.7 <u>Protective Devices</u> - Circuit breakers shall be used in lieu of fuses whenever possible. All circuit breakers shall be accessible without removing equipment from racks. Fuses, if used, shall be of types and ratings readily available from Navy supply,

3.3.12.2.8 <u>Overtemperature Sensor</u> - Each logic unit power supply excluding the Magnetic Drum Memory Subassembly power supply shall contain thermal sensing circuitry to detect the maximum safe operating temperature and provide a signal to the aircraft power distribution system. The overtemperature signal shall be used by the airframe contractor to provide a warning to the TACCO Station operator that the respective Logic Unit is operating beyond the upper design thermal limit. The logic unit shall not automatically shut down as a result of the overtemperature sensor.

10

3.3.13 <u>Special Support Equipment</u> - Self-test features shall be such as to obviate the need for any Special Support Equipment for preflight, post-flight checks of fault isolation. There shall be no special support equipment for support of the equipment except as expressly authorized by the government.

3.3.14 <u>Adjustments</u> - In order to decrease the complexity of the maintenance tasks, the equipment should be designed to require no periodic adjustments, alignment or calibration. If adjustments are mandatory, they shall be capable of being made in the aircraft using simple tools and/or General and Standard Test Equipment.

3.4 <u>Performance</u> - Unless otherwise specified, values set forth to establish the requirements for satisfactory performance apply to performance under both standard and extreme service conditions. When reduced performance under the extreme conditions is acceptable, tolerances or values setting forth acceptable variations from the performance under standard conditions will be specified herein.

3.4.1 <u>Description of System</u> - The DPS shall be comprised of one each of Logic Units 1, 2, 3 and 4, three Universal Keysets, one Pilot's Keyset, one Armament/Ordnance Test Panel and one Ordnance Panel. (Refer to 1.3 regarding Magnetic Tape Transport.)

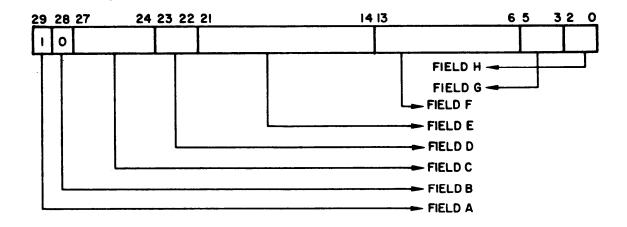

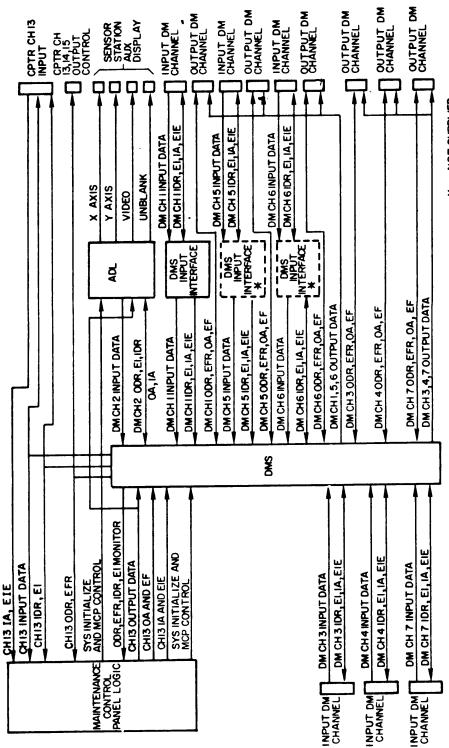

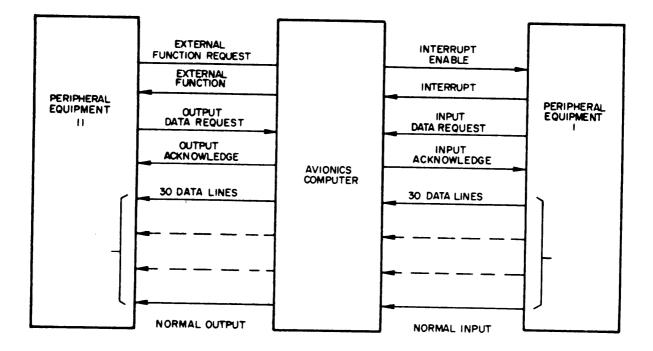

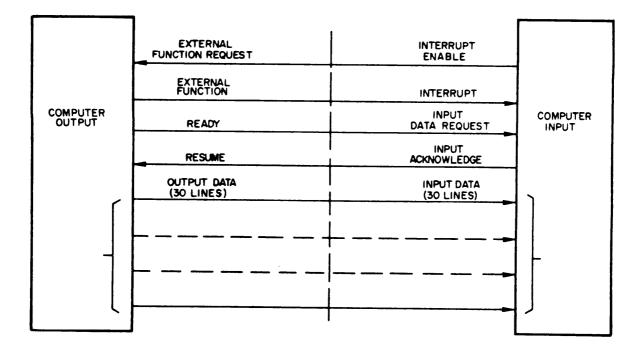

3.4. 1.1 <u>Computer Input/Output</u> - The subunits, which are assigned to a Computer Input and/or Output Channel will communicate with the computer in a 30 bit (max) parallel mode over the Input and/or Output Channel. The Input/Output Unit of the computer shall provide computer control of and communications with peripheral equipment. Up to 16 channels of input and 16 channels of output shall be provided in the Input/Output Unit. Each channel shall provide parallel data transfer for up to 30 data bits. Each group of four input channels and the corresponding group of four output channels shall have access to an assigned 32,768 word memory group, with selectability to other 32,768 word groups of a maximum 131,072 word memory by back panel wire change. In the delivered configuration, the four output data channels from each of the four output registers shall be bussed into one 30-twisted-pair cable. Each of these output groups shall be provided with control lines for four peripherals. Thus the output configuration will provide four data output channels from the 1/0 unit with control lines for a total of 16 peripherals.

Each of the computer I/O unit I/O groups contains a timeshared output register, input selection circuits, local I/O control and priority circuits.

Since the Output Register in an 1/0 group is time-shared by up to four Output peripherals, the 30 data lines emanating from the register are common to the four output peripherals, i. e., an I/O group transmits the data to the four output peripherals over a single 30-twisted-pair cable and the control lines for the four Output peripherals determine which peripheral is to sample the data. The control lines for the four channels are independent. Subunits which communicate with the same I/O group have been assigned to the same logic unit. This permits a logic unit to buffer all incoming computer data with a single group of 30 input amplifiers. (Input amplifiers are defined in Appendix 11.)

Logic Units 2, 3, and 4 each require three computer output channels. Logic Unit 1 contains two subunits which are assigned a computer output channel. As indicated, a computer 1/0 group is capable of servicing up to four output peripherals, and since none of the logic units require more than three output channels, each logic unit shall make the 30 data lines from the computer 1/0 subunit available for "bussing" to one additional output peripheral. The data lines from the computer shall remain available for "bussing" regardless of the number of subunits removed from the logic unit.

3.4.1.1,1 A failure in Logic Unit 4 electronics shall not preclude normal operation of computer charnels O through 11 used in the aircraft with Logic Units 1, 2, and 3.

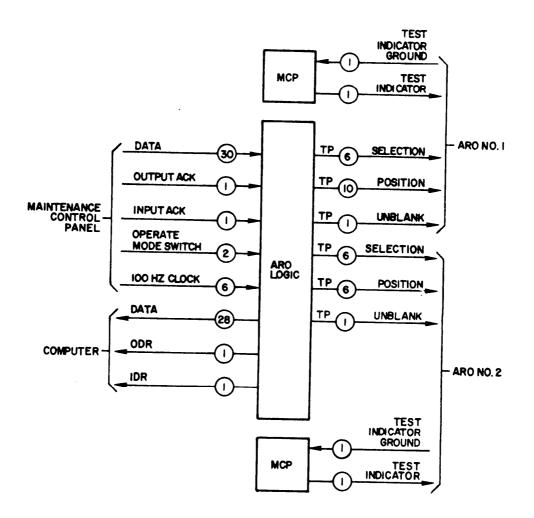

3.4.1.2 <u>Maintenance Control Panel</u> - Each logic unit shall contain a Maintenance Control Panel (MCP), which shall, as a minimum, provide the maintenance operator with the capability of monitoring the data and control lines associated with any computer input or output peripheral contained in the logic unit, and of operating anyone computer input or output peripheral contained within the logic unit off-line from the computer in either single step or continuous mode operation. The MCP shall also provide any additional maintenance functions described in the detailed requirements for the Logic Unit.

#### NOTE

Since the Maintenance Control Panels for the four logic units are nearly identical, only one detailed descriptions given for an MCP. (See MCP section for Logic Unit 1, 3.5.1.4.9.)

3.4.1.3 <u>Power Control Panel</u> - All subunits of each logic unit, except the MCP/MCPL subunits and the MTL subunit shall have on/off switches located on the power control panel. All MCP/MCPL subunits and the MTL subunit shall decontrolled by the master power on/off switch for the logic unit. Operation of the subunit switches shall be defined as an abnormal operating condition for the DPS.

3.4.1.4 <u>Logic Units</u> - Each of the four logic units is comprised of a number of subunits (functional groups of modules). Two criteria were used in the grouping of the subunits into logic units.

(1) Computer Input/Output Channel Assignment

(2) Functional Relationship

3.4.2 subunits:

Logic Unit 1 Subunits - Logic Unit 1 shall contain the following

No. Required

| Digital Input Multiplexer               | 1 |

|-----------------------------------------|---|

| Digital Output Multiplexer              | 1 |

| TACCO Tray Logic                        | 1 |

| Universal Keyset Logic                  | 3 |

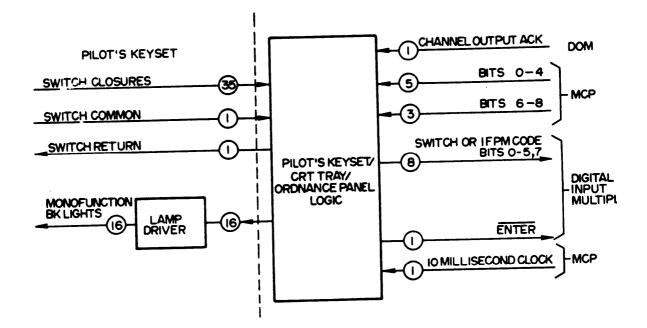

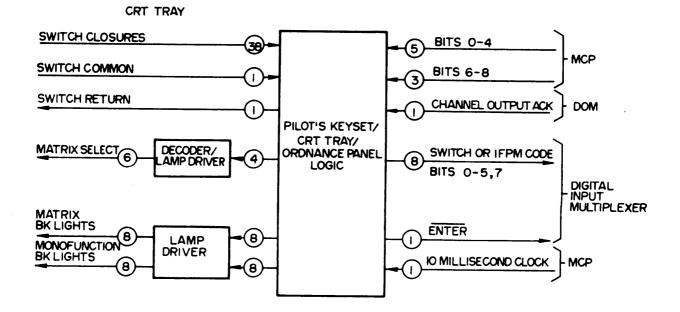

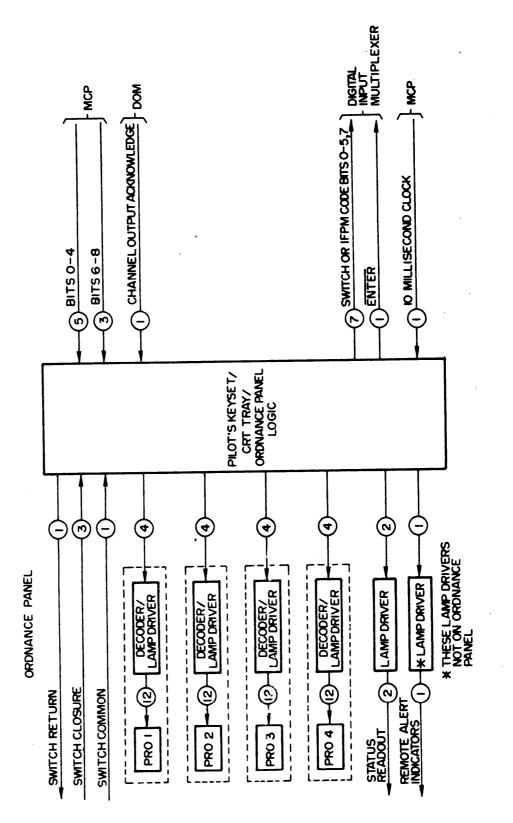

| Pilot Key set/CRT Tray/Oral Panel Logic | 3 |

| Status Logic                            | 1 |

| Sono Receiver Logic                     | 1 |

| Auxiliary Readout (ARO) Display         |   |

| Interface Logic                         | 1 |

| Maintenance Control Panel/Logic         | 1 |

| Power Supply                            | 1 |

|                                         |   |

3.4.3 subunits:

Logic Unit 2 Subunits - Logic Unit 2 shall contain the following

| No. | Required |  |

|-----|----------|--|

|     | -        |  |

| 1 |

|---|

|   |

| 1 |

| 1 |

| 1 |

| 1 |

| 1 |

| 1 |

|   |

| 3.4.4                                                                                                              | Logic Unit 3 Subunits - Logic Unit 3 shall contain the following                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| subunits:                                                                                                          | No. Required                                                                                                                                                                                                    |

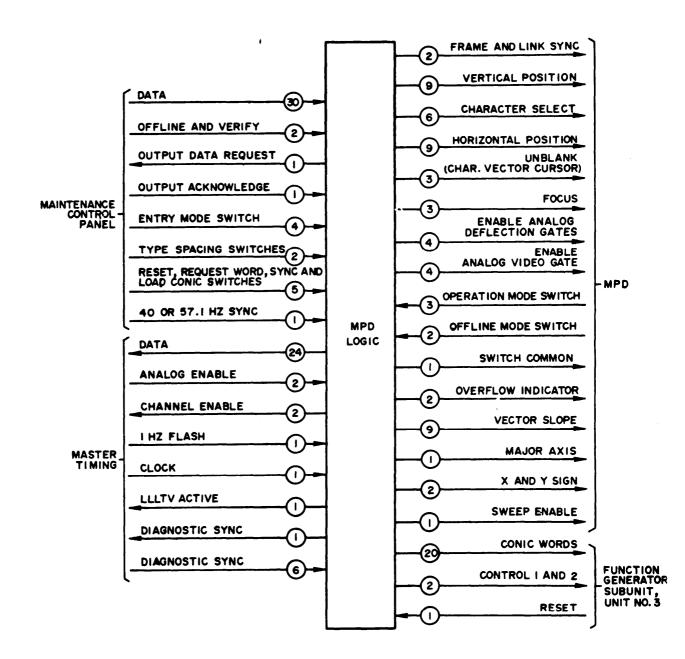

|                                                                                                                    | Multi-Purpose Display (MPD)Interface2Pilot Display Interface1Function Generator1Master Timing Logic1Maintenance Control Panel,' Logic1Power Supply1                                                             |

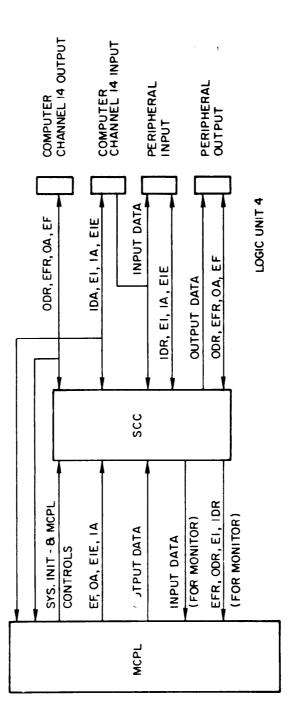

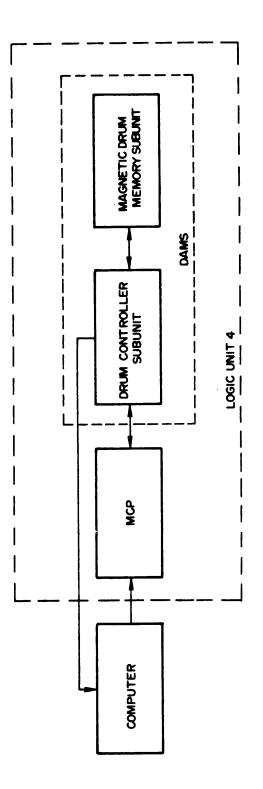

| 3.4.5<br>subunits:                                                                                                 | Logic Unit 4 Subunits - Logic Unit 4 shall contain the following                                                                                                                                                |

| subumts.                                                                                                           | No. Required                                                                                                                                                                                                    |

|                                                                                                                    | Data Multiplexer Subunit1Auxiliary Display Logic1Drum Auxiliary Memory Subunit1Maintenance Control Panel/Logic1Spare Computer Channel Subunit1Power Supply1                                                     |

| 3.4.6                                                                                                              | Keysets and Panels - Included in the system shall be the following                                                                                                                                              |

| separate items:                                                                                                    | No. Required                                                                                                                                                                                                    |

|                                                                                                                    | Universal Keysets3Pilot Keyset1Ordnance Panel1Armament 'Ordnance Test Panel1                                                                                                                                    |

| 3.4.7 form the following system functions                                                                          | Logic Unit 1 Functions - The subunits of Logic Unit 1 shall per-<br>in conjunction with other equipments.                                                                                                       |

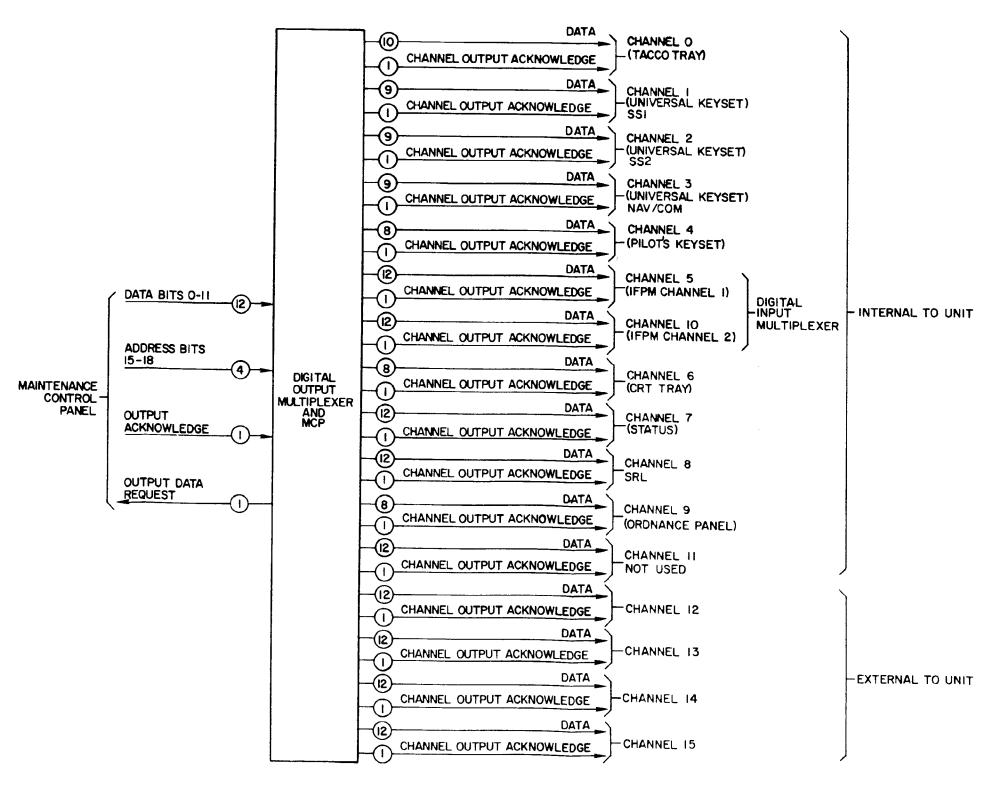

| mits one computer input channel to                                                                                 | (1) <u>Digital Input Multiplexer</u> - The Digital Input Multiplexer per-<br>service up to 16 input peripheral equipments.                                                                                      |

| permits one computer output channel                                                                                | (2) <u>Digital Output Multiplexer</u> - The Digital Output Multiplexer to service up to 16 output peripheral equipments.                                                                                        |

| Logic allow the Tactical Coordinator<br>the computer. This information trans<br>permits the TACCO to prosecute the | (3) <u>TACCO Tray Logic</u> - The TACCO Tray and TACCO Tray (TACCO) to enter information into and receive information from sfer, in conjunction with the data presented on the TACCO MPD, e tactical situation. |

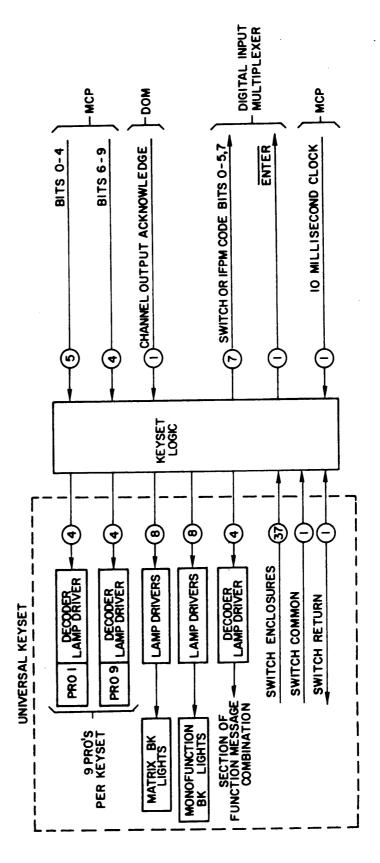

| Universal Keyset allow a sensor ope computer.                                                                      | (4) Universal Keyset Logic - A Universal Keyset Logic and a erator to enter information into and receive information from the                                                                                   |

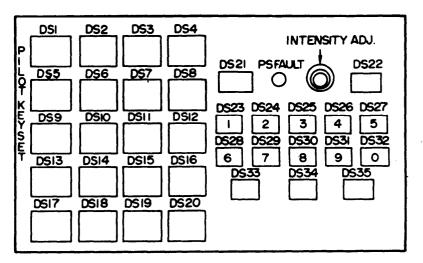

| set allow the pilot to enter informati                                                                             | (5) <u>Pilot Keyset Logic</u> - The Pilot Keyset Logic and Pilot's Key-<br>ion into and receive information from the computer.                                                                                  |

| mit the operator to enter information                                                                              | (6) <u>CRT Tray Logic</u> - The CRT Tray Logic and CRT Tray per-<br>n into and receive information from the computer.                                                                                           |

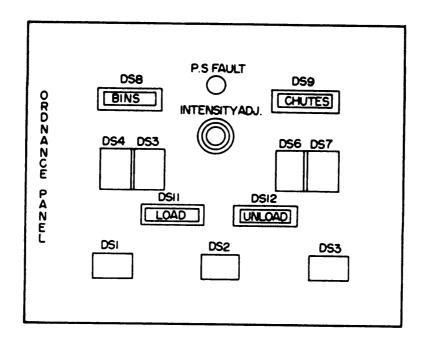

| nance Panel permit the operator to                                                                                 | (7) <u>Ordnance Panel Logic</u> - The Ordnance Panel Logic and Ord-<br>enter information into and receive information from the computer.                                                                        |

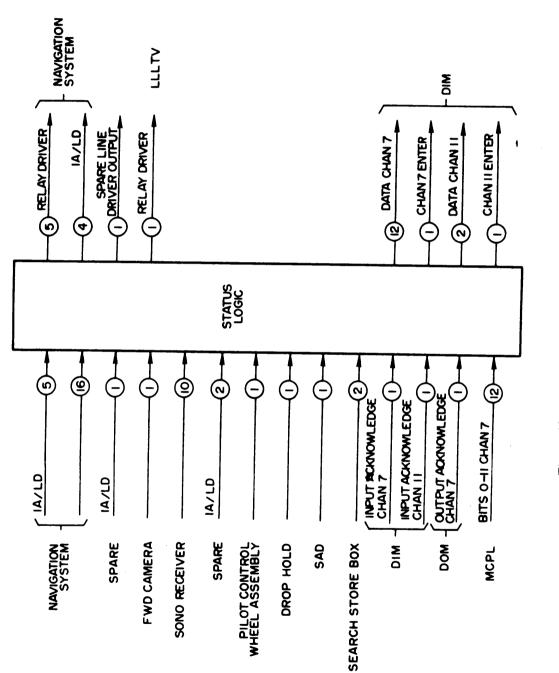

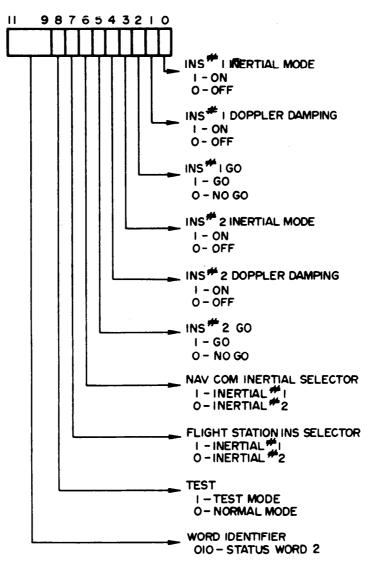

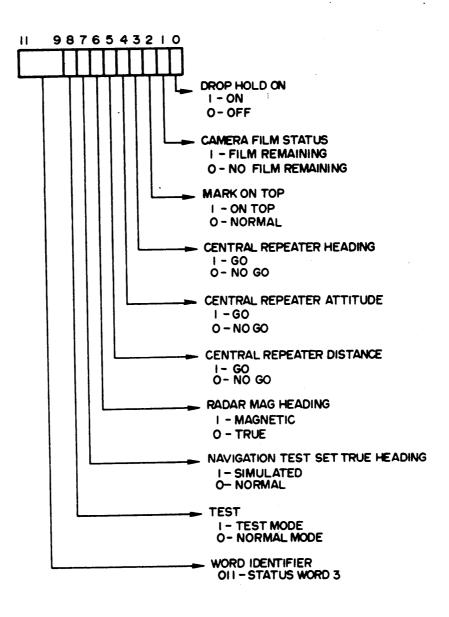

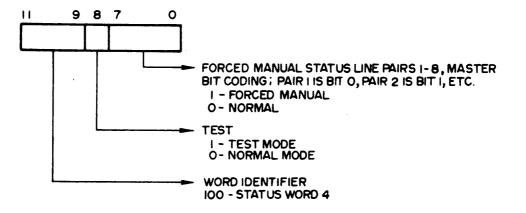

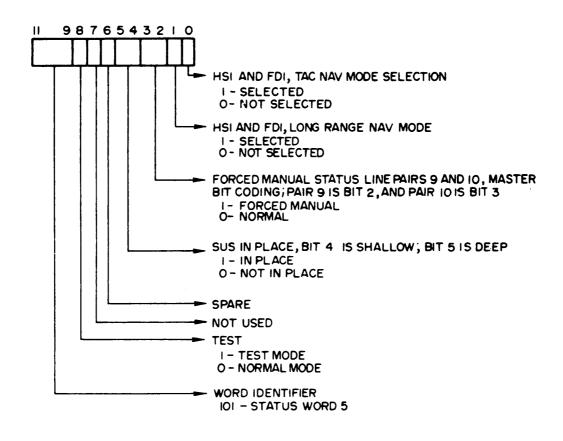

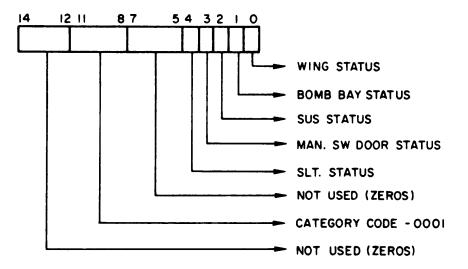

| of status data from several aircraft transmission of data from the comp                                            | (8) <u>Status Logic</u> - The Status Logic provides for the transmission systems to the computer. The status logic also provides for puter to the navigation system.                                            |

|                                                                                                                    | 13                                                                                                                                                                                                              |

|                                                                                                                    |                                                                                                                                                                                                                 |

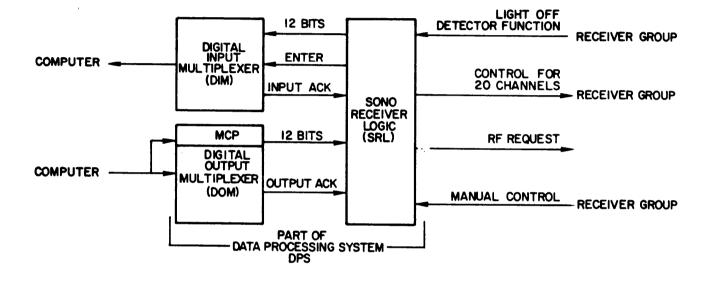

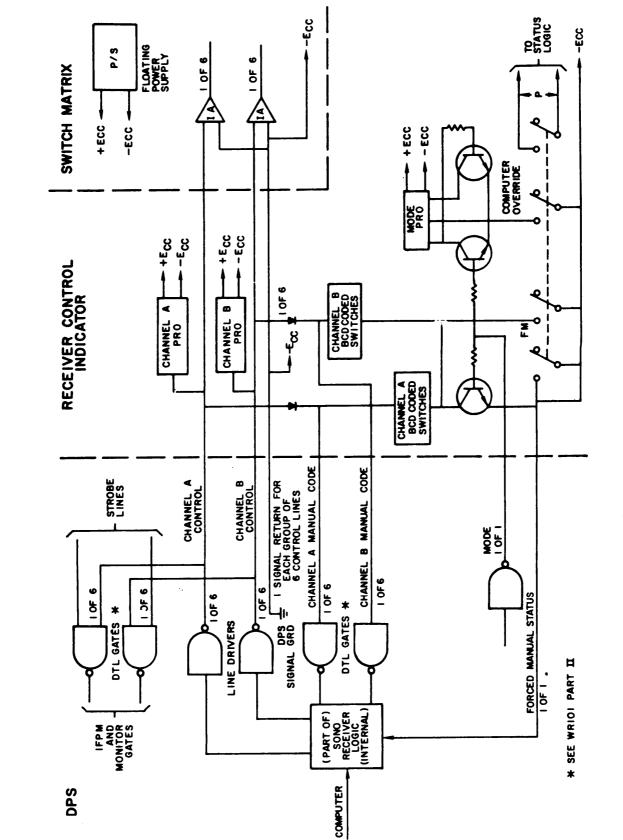

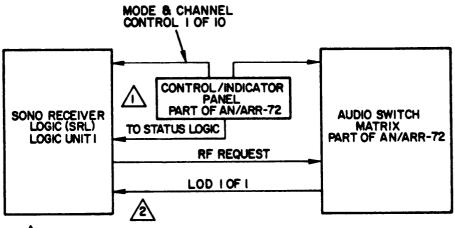

(9) <u>Sono Receiver Logic</u> - All acoustic processors in the P-3C system receive their signals from the ARR-72 Sonobuoy Receiver. The ARR Sonobuoy Receiver consists of 31 fixed tuned receivers, each providing an audio signal output. These 31 outputs are sent to the switching matrix, the function of which is to switch 20 or less of them to 20 acoustic processing channels. Manual channel selection is accomplished through the use of nine remote Control/Indicator Panels. These nine panels serve 18 of the 20 processing channels. The other two channels have no manual control. Each half panel contains a thumbwheel capable of selecting one of 31 receivers, a decimal readout to indicate which receiver is selected, an "AGC" indicator for that receiver, and a Manual/Auto mode lamp. The SRL provides an integrated Computer/Manual tuning mode for the 31 receivers used in this system. This will allow the following operating modes:

(a) Computer control of the ARR-72 Switching Matrix with indication of channel status given to the operator.

(b) Direct operator control of the Switching Matrix with indication of the channel status given to the computer.

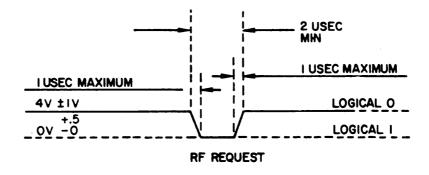

Additional control shall provide both computer selection of either mode, and manual overrides to force the SRL to mode (b) above. An additional requirement is to make it possible for the computer to monitor all RF activity within the ARR-72 spectrum. This allows the computer to select RF channels prior to launch, and to monitor sonobuoy operation (light-off) immediately after launch.

The logic provides logical signals so that the 20 acoustic processing channels may be switched to the desired RF channels. Additionally, one output channel is provided for the TACCO. The Light Off Detector Logic serves to provide logical signals to the matrix in order to call up the desired RF level (AGC) signal.

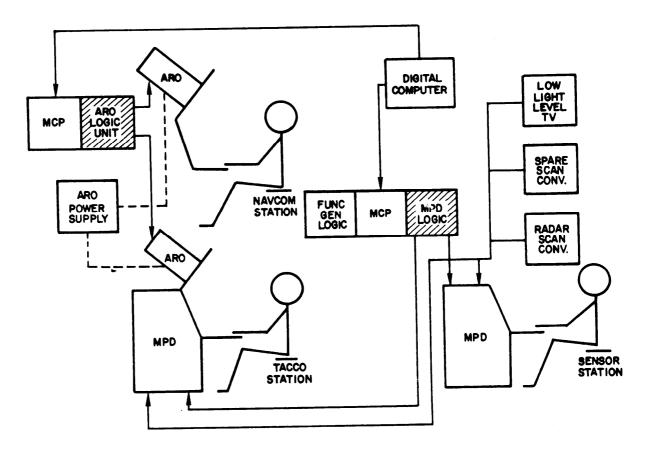

(10) <u>Auxiliary Readout (ARO) Display Interface Logic</u> - The ARO Display Interface Logic provides the interface between the computer and Auxiliary Readout Displays. The Auxiliary Readout Display provides a means for displaying computer generated tableau information on a Charactron-type display. One ARO is located at the TACCO Station and the other ARO is at the NAV/COM operator station.

3.4.8 Logic Unit 2 Functions - The subunits of Unit 2 shall perform the following system functions :

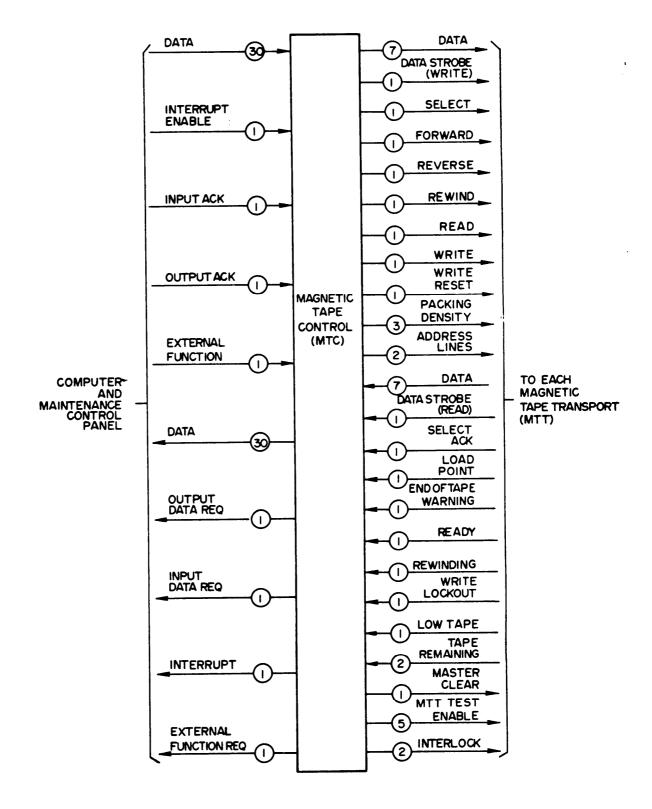

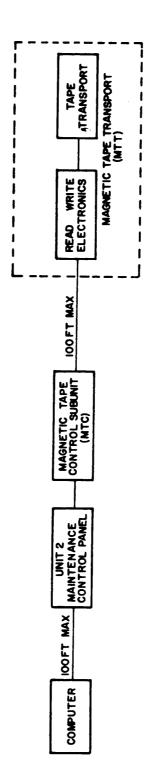

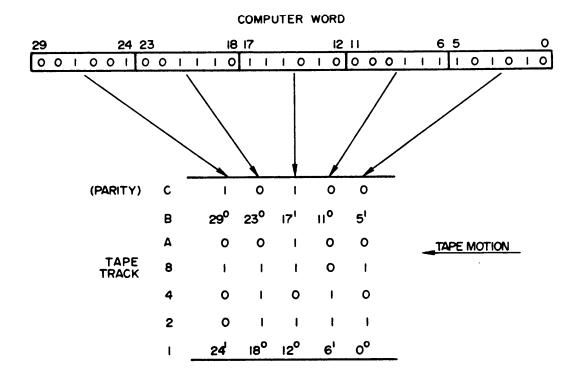

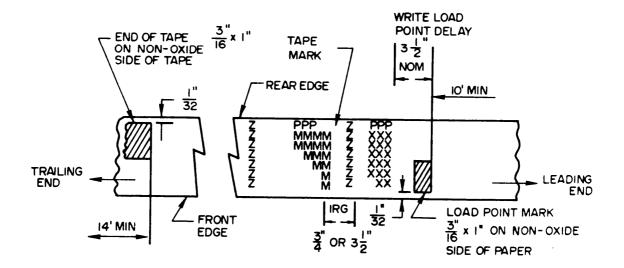

(1) <u>Digital Magnetic Tape Subsystem (DMTSS)</u> - The Digital Magnetic Tape Subsystem shall provide rapid retrieval of supplemental programs required during the mission, such as classification programs; and rapid interchange of operational programs with systems tests, integration tests, and diagnostic programs. The subsystem shall also record in-flight data (events) for use in post-flight data reduction and analysis.

The Digital Magnetic Tape Subsystem shall consist of a Magnetic Tape Subunit and a Magnetic Tape Transport.

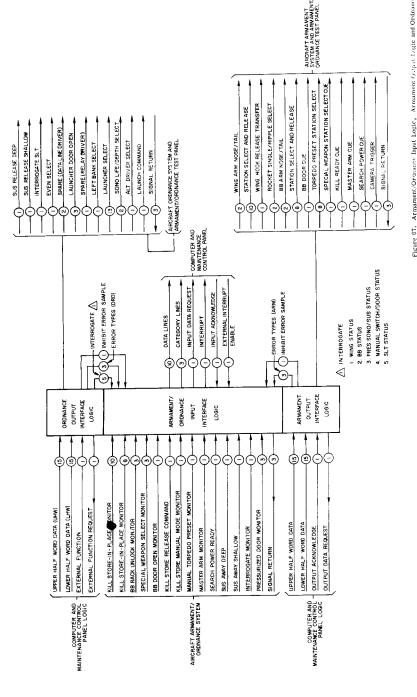

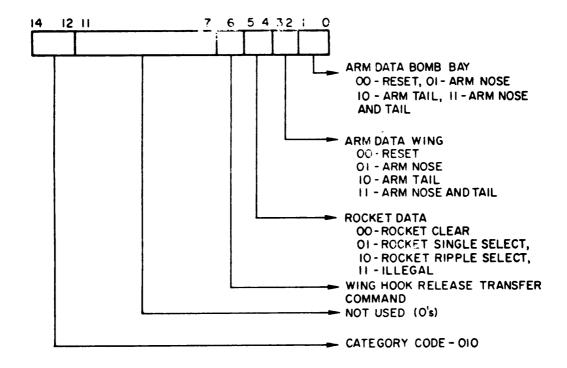

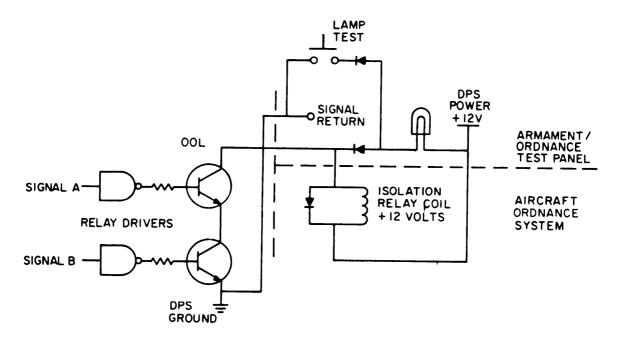

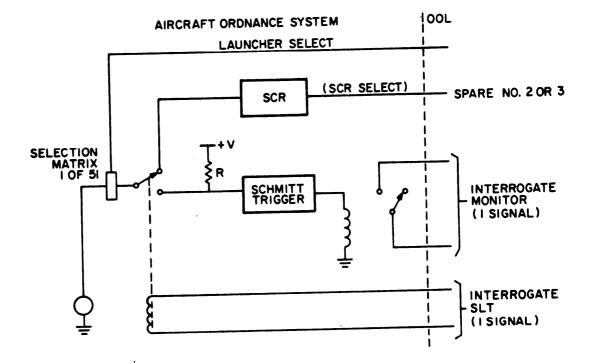

(2) <u>Armament/Ordnance Input Logic</u> - The Armament/Ordnance Input Logic shall transmit to the computer an Armament Status Word which notifies the computer of ' the Armament and Ordnance System Status or Change of Status, i. e. ,

(a) Readiness of Search and Kill Store Weapons

(b) Change in Status of these Search and Kill Store Weapons

(c) Recognition and transmission of an error or malfunction

in the Subsystem operation,

(d) Launch indication of Search and Kill Store Weapons.

(3) <u>Armament Output Logic</u> - The Armament Output Logic shall provide the capability for the computer program to select, arm, and release torpedoes, conventional and nuclear depth charges, rockets and mines, either individually or in salvo.

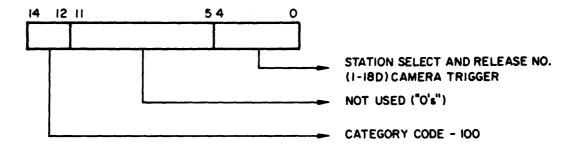

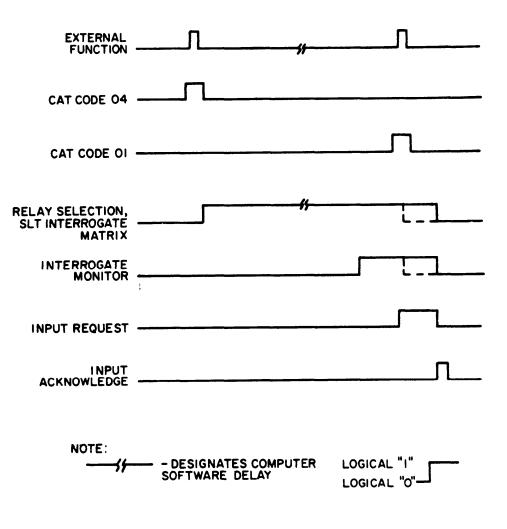

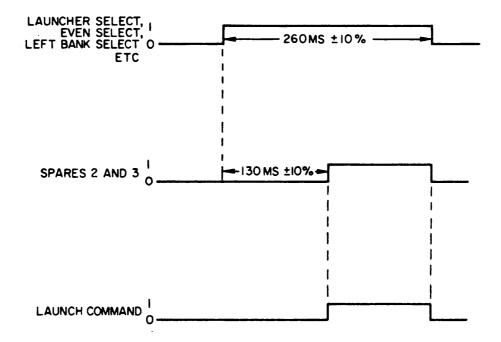

(4) <u>Ordnance Output Logic</u> - The Ordnance Output Logic shall provide the capability for the computer program to select and launch sonobuoys, explosive sound sources, and smoke markers at the appropriate time with the required accuracy and launch rates.

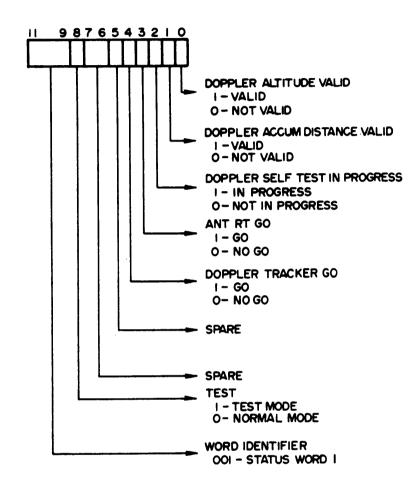

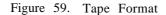

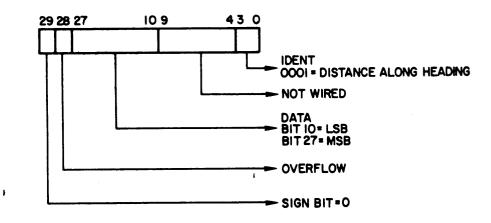

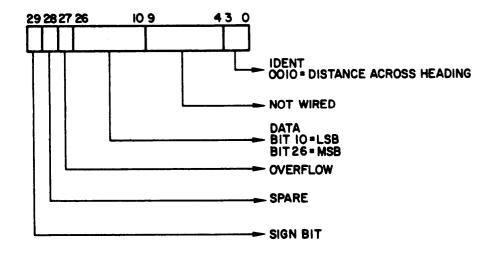

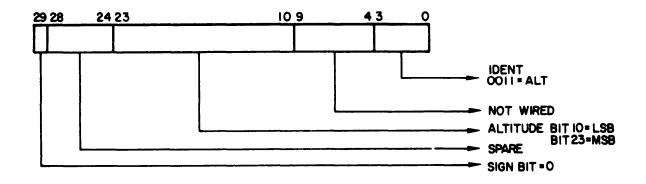

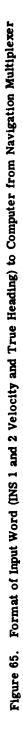

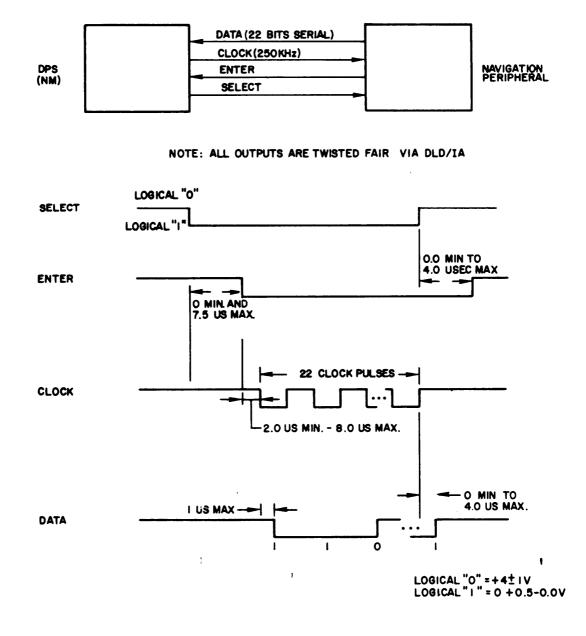

(5) <u>Navigation Multiplexer (NM)</u> - The NM provides an interface between the Inertial Platform and the Doppler to the computer.

3.4.9 <u>Logic Unit 3 Functions</u> - The subunits of Logic Unit 3 shall perform the following system functions:

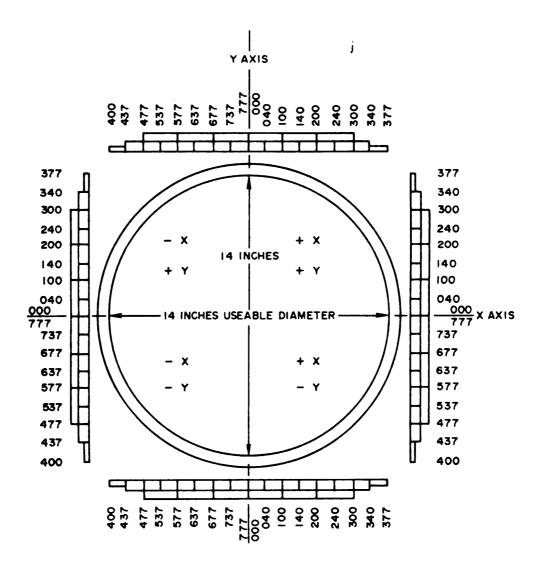

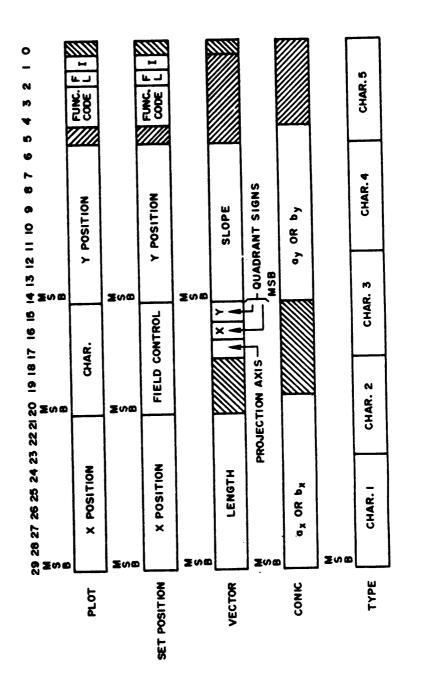

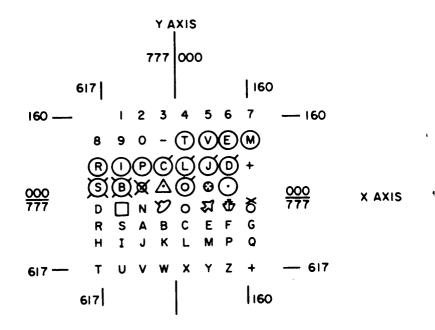

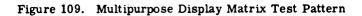

(1) <u>Multipurpose Display (MPD) Logic</u> -The MPD Logic shall display tactical data, and comes under computer control in such away that the tactical plot of the ASW situation may be presented on the MPD. Furthermore, Scan Converted Radar data may bepresented on the MPD in conjunction with the tactical plot. The second Scan Converter is provided for future sensor equipments.

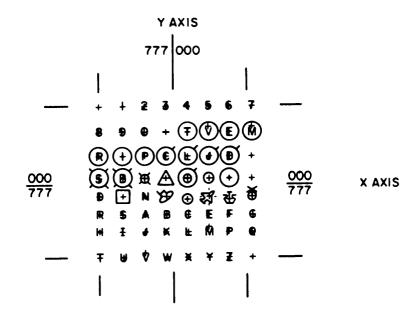

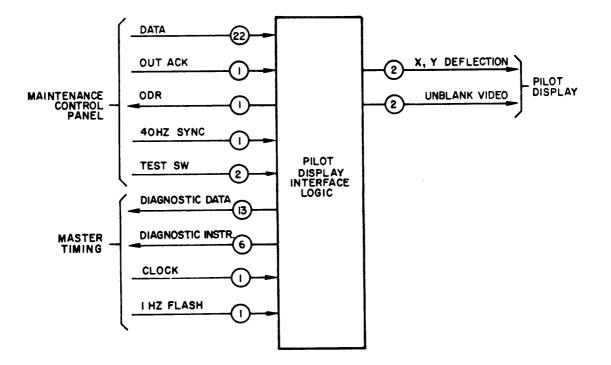

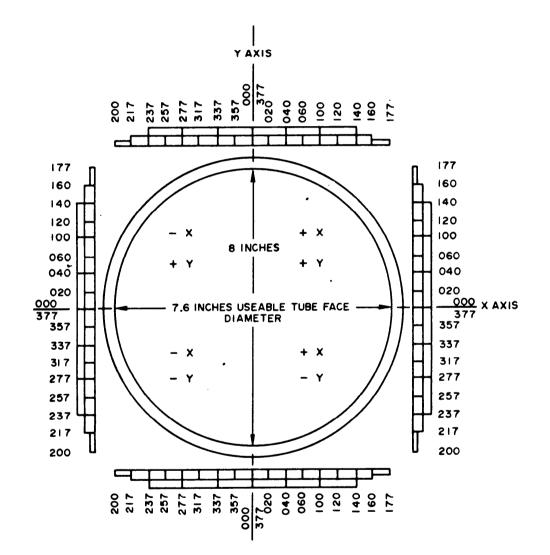

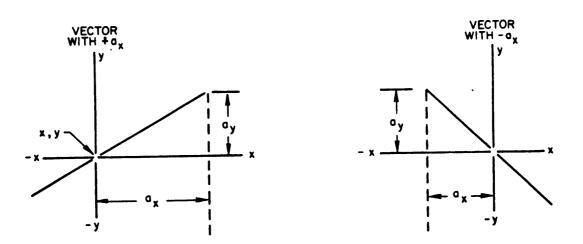

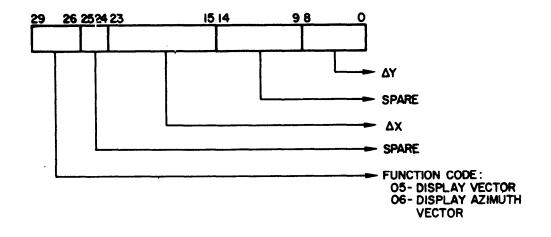

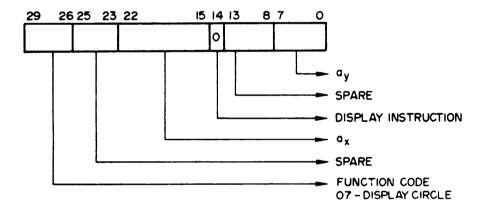

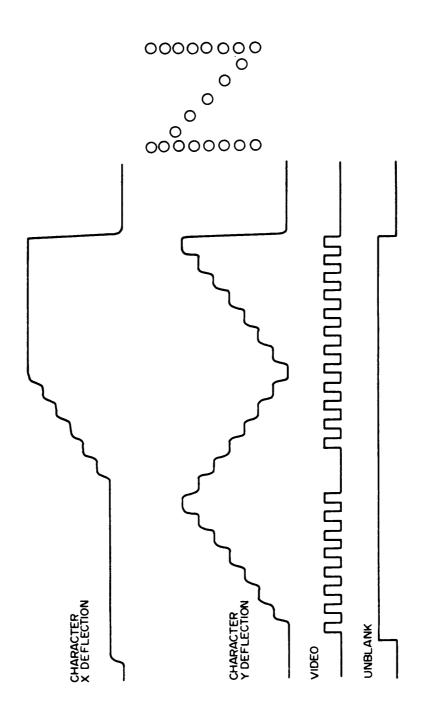

(2) <u>Pilot Display Interface Logic</u> -The Pilot Display interface Logic, under computer command, shall provide timing, control, deflection and video signals to control the presentation of tactical data on the Pilot Display. The tactical data shall consist of the aircraft symbol with track vector, fly-to-points, vectors, circles, flashing symbols, tabular information and the entire alphanumeric repertoire as required.

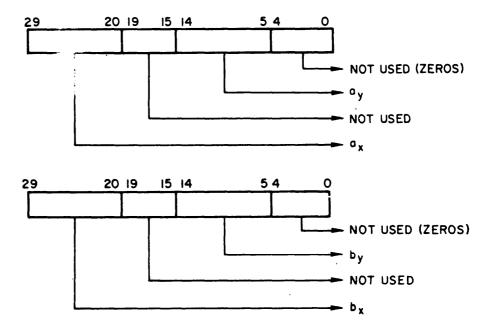

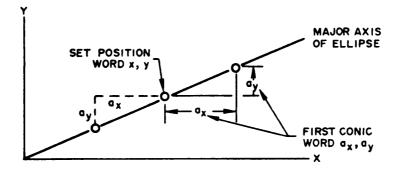

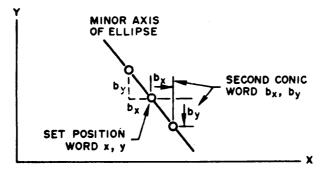

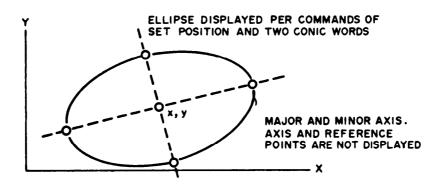

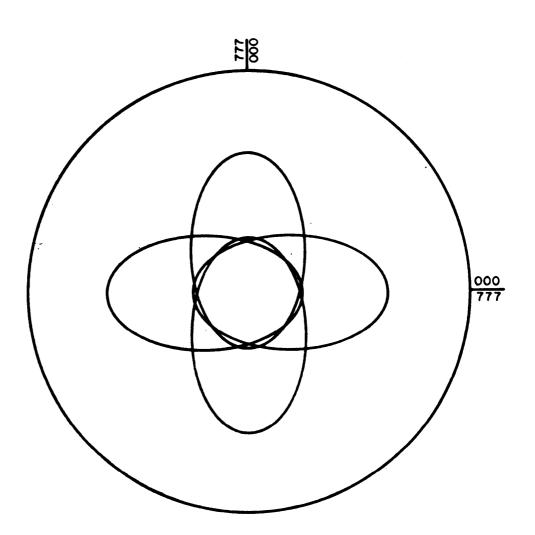

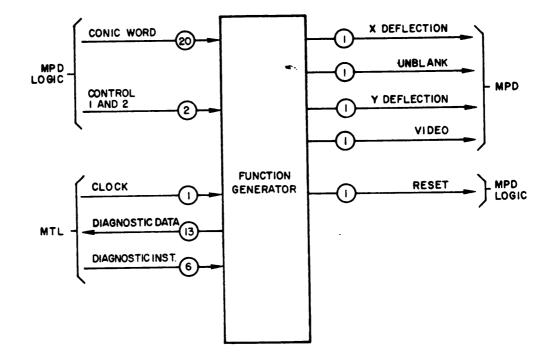

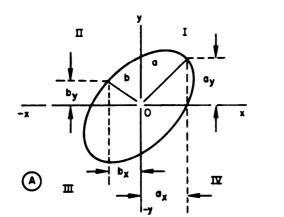

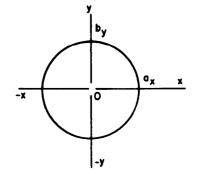

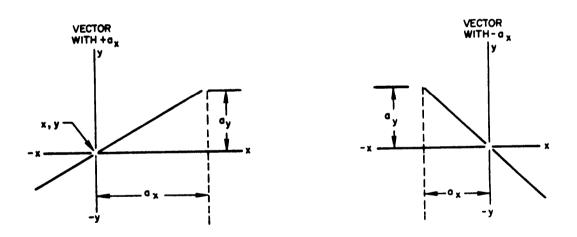

(3) <u>Function Generator Logic</u> - The Function Generator shall accept digital inputs that describe ellipses, circles and straight lines, process this data and generate the appropriate analog sine wave and unblank signal outputs to a CRT display system so as to cause ellipses, circles or straight lines to be displayed.

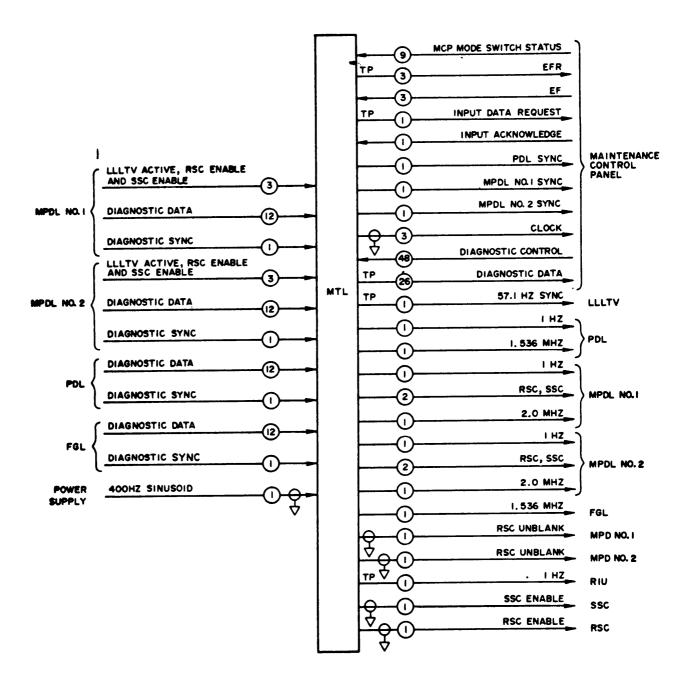

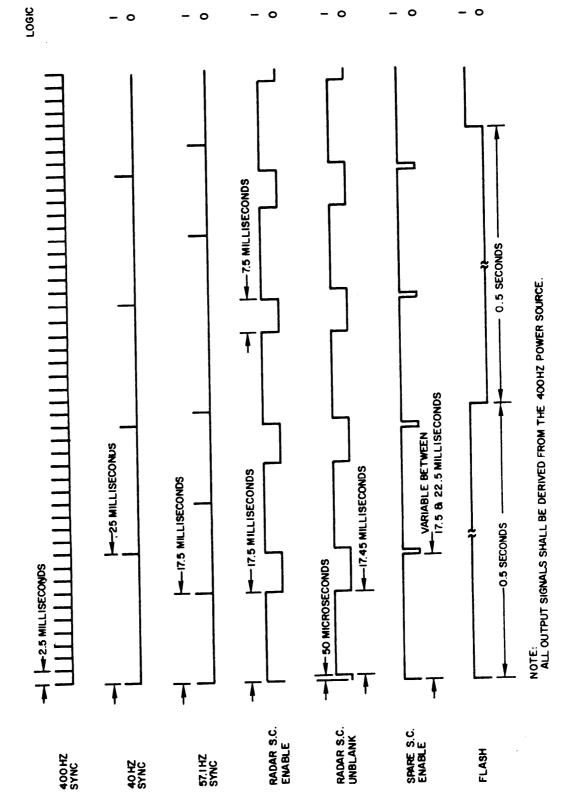

(4) <u>Master Timing Logic</u> - The Master Timing Logic (MTL) shall provide the timing and control signal necessary to "'line-lock" (sync) all display operations to the aircraft's 400 Hz power source. The MTL shall receive signals from MPD 1 Logic and MPD 2 Logic; and transmit signals to the MPD 1, MPD 1 Logic, MPD 2, MPD 2 Logic, Radar Interface Unit, Spare Scan Converter, Pilot Display Logic and Low Light Level TV.

3.4.10 Logic Unit 4 Functions - The subunits of Logic Unit 4 shall perform the following system functions:

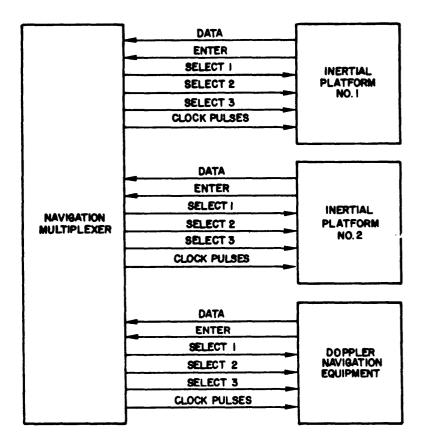

(1) <u>Data Multiplexer Subunit</u> - The eight channel Data Multiplexer Subunit (DMS) is a digital interface unit capable of servicing eight peripheral equipments (one at a time) with input/output channel capability from a single computer channel.

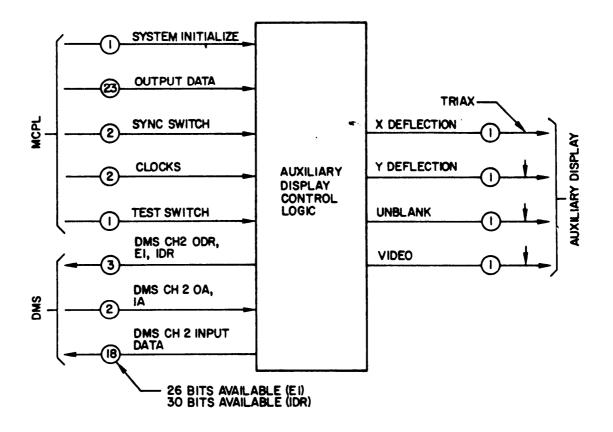

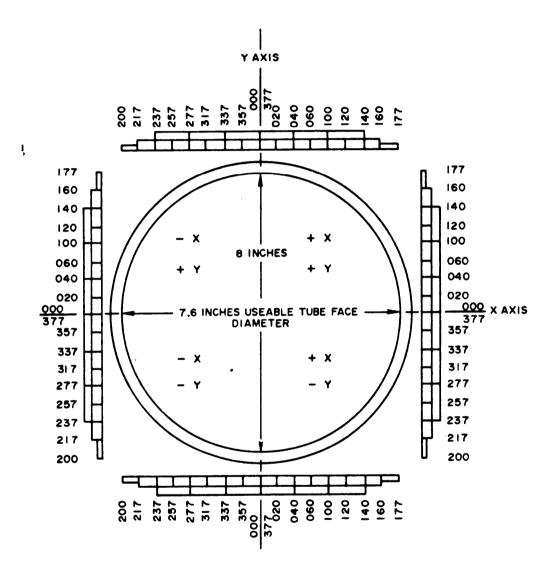

(2) <u>Auxiliary Display Logic</u> - The Auxiliary Display Control Logic (ADL) under computer command (via DMS Output Charnel 2) shall provide timing, control deflection and video signals to control the presentation of functional data on a display at Sensor Stations land 2.

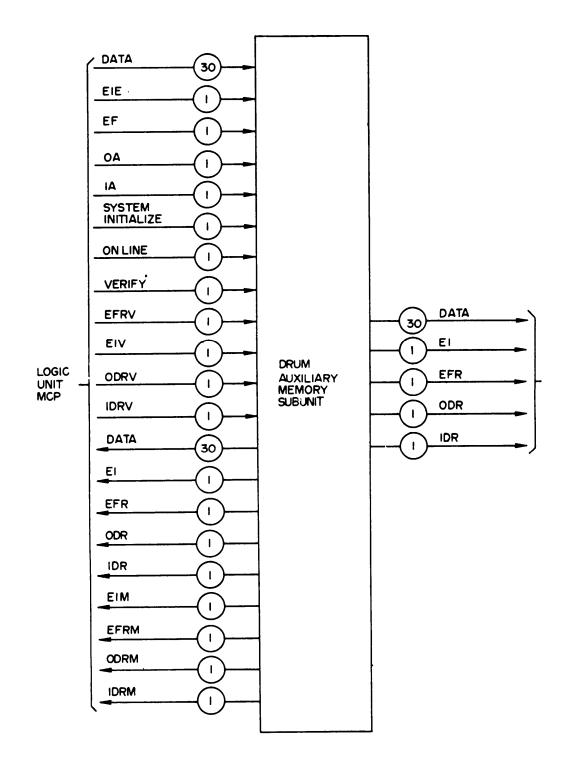

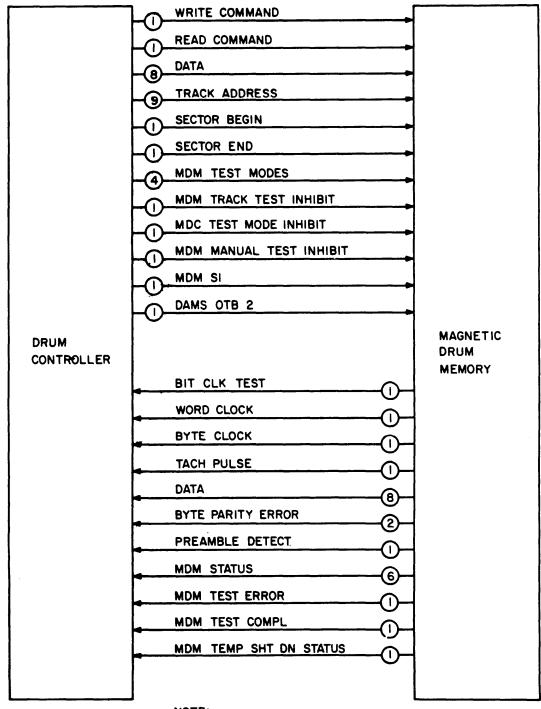

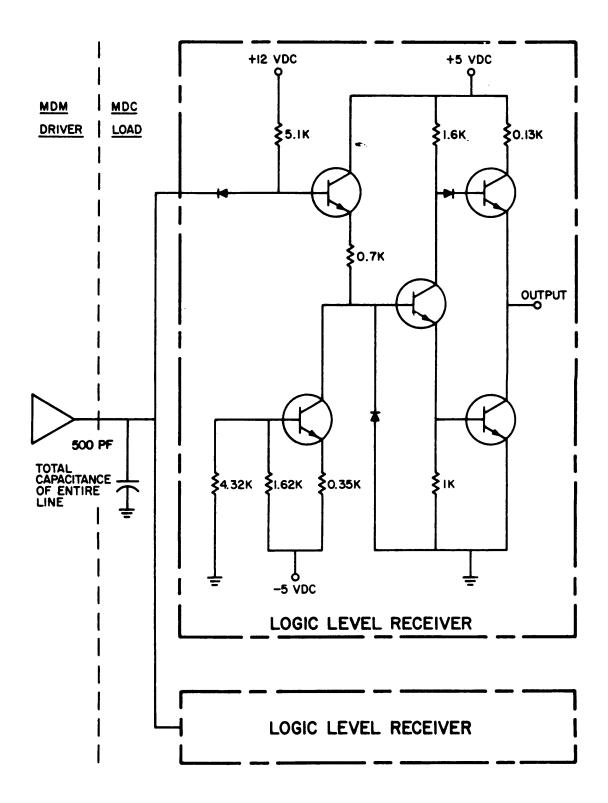

(3) <u>Drum Auxiliary Memory Subunit</u> - The Drum Auxiliary Memory Subunit (DAMS) shall provide rapid access and transfer of computer program segments. The DAMS shall also provide for rapid storage of computer data for purposes such as program recovery. The DAMS shall be functionally independent of all other subunits of Logic Unit 4 with the exception of the Maintenance Control Panel Subunit.

(4) <u>Spare Computer Channel Subunit</u> - Logic Unit 4 shall provide for an interface designated as Spare Computer Channel. Logic Unit 4 shall provide one input and one output connector compatible with full computer I/O capability for the spare channel.

3.4.11 <u>Keyset and Panel Functions</u> - The functions of the remaining items of the DPS are as follows:

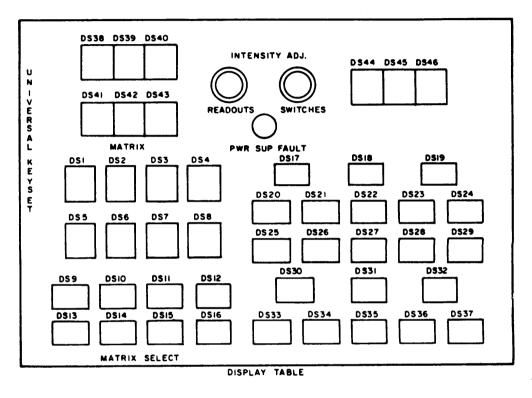

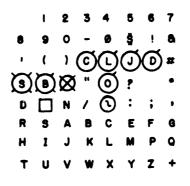

3.4.11.1 <u>Universal Keyset</u> - The Universal Keyset shall contain data entry and readout devices.

3.4. 11.2 <u>Pilot Keyset</u> - The Pilot's Keyset shall contain 35 momentary Switches. This Keysetshall redesigned to communicate with the computer via the Keyset Logic and the Digital Input and Output Multiplexers.

3.4. 11.3 <u>Ordnance Panel</u> - The Ordnance Panel displays computer command information to the Ordnance operator concerning Search Stores, i.e. , Bin and Chute number and Status information.

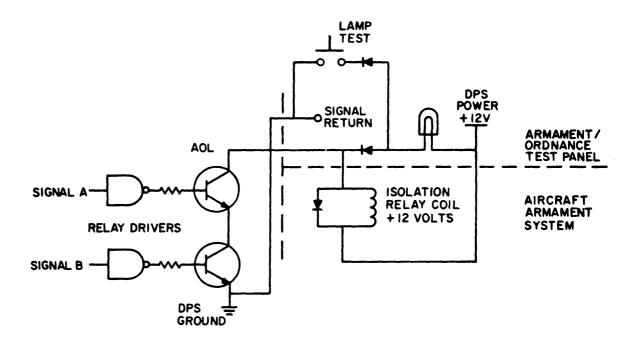

3.4.11.4 <u>Armament/Ordnance Test Panel</u> - The panel shall provide an operator with a means of monitoring the performance of the Armament/Ordnance Logics.

| 3.5      | Detail Requirements                                    |

|----------|--------------------------------------------------------|

| 3.5.1    | Data Analysis Logic Unit MX-8023A/AYA-8 (Logic Unit 1) |

| 3.5, 1.1 | Function - See 3.4.7                                   |

|          |                                                        |

3.5. 1.2 <u>Form Factor</u> - Refer to illustration in EI-515, Avionics Installation Instructions for Data Analysis Programming Group AN/AYA-8B.

3.5. 1.3 <u>Weight</u> - The total weight of Logic Units 1, 2, 3 and 4 shall not exceed 680 pounds.

| 3.5. 1.4.1 | 1.4.1 | Digital | Input | Multiplexer 1 |

|------------|-------|---------|-------|---------------|

|            |       |         |       |               |

|            |       |         |       |               |

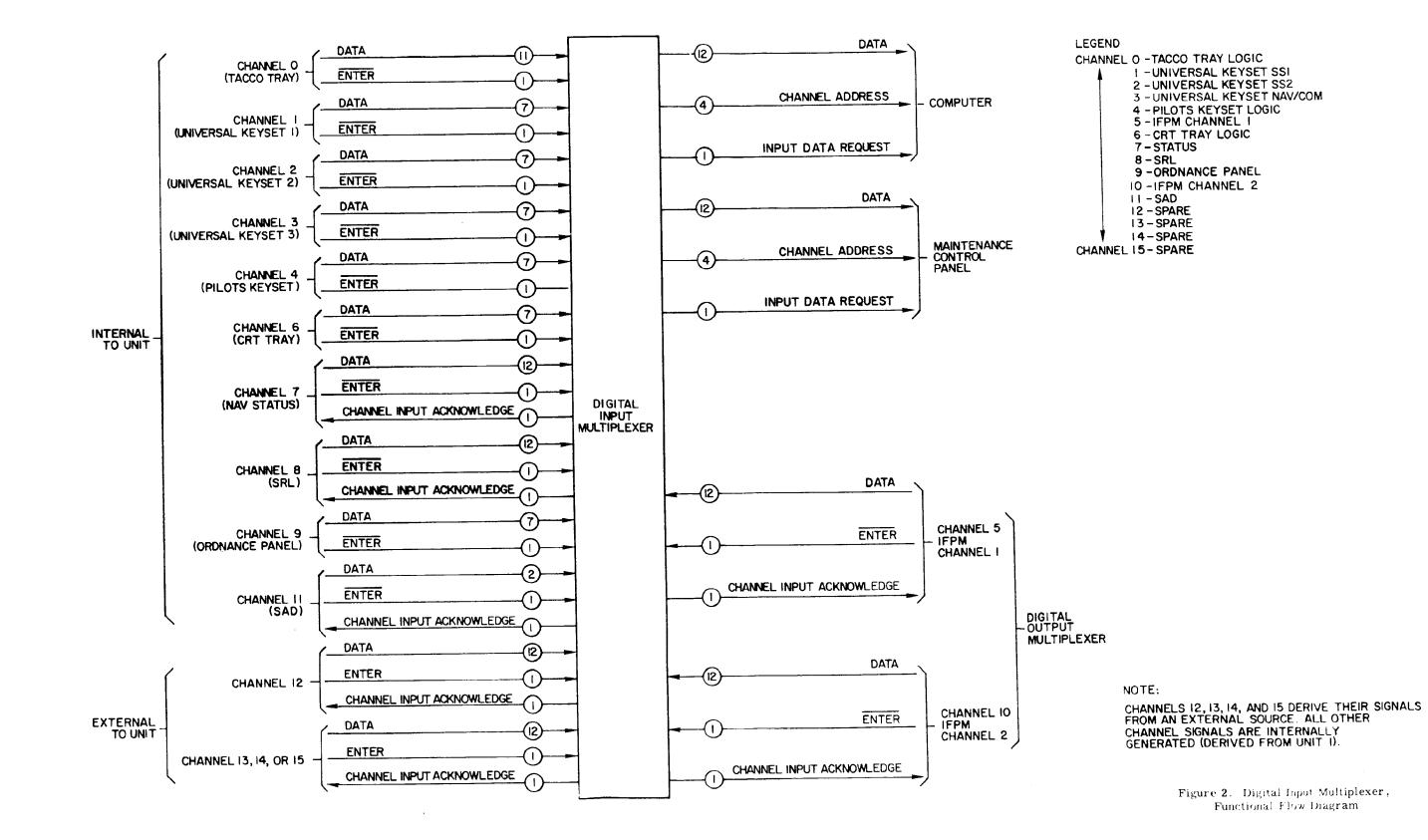

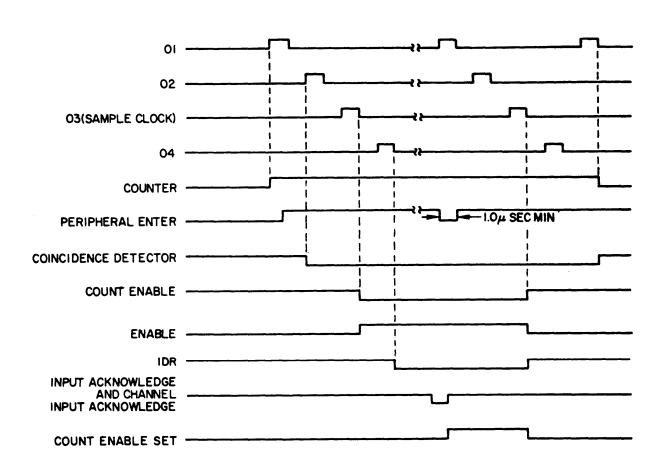

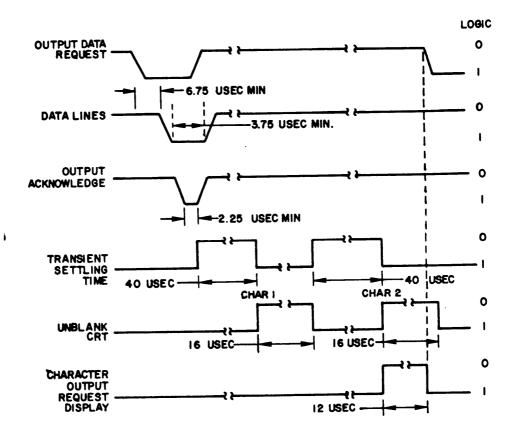

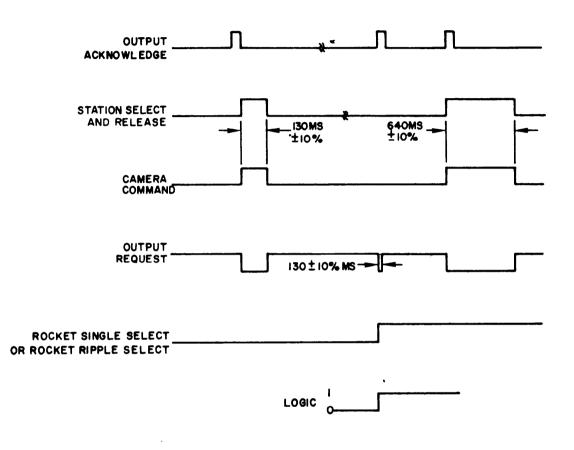

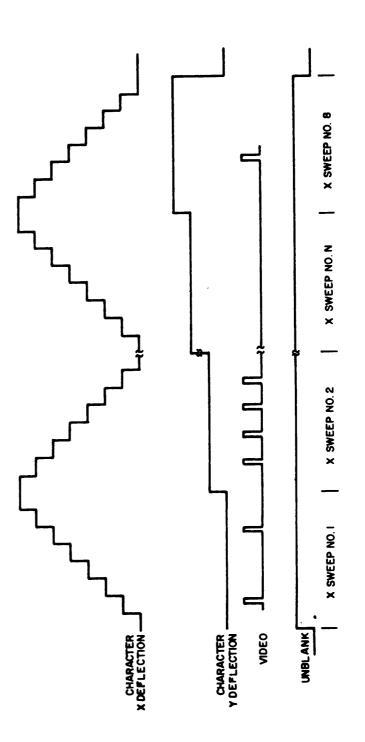

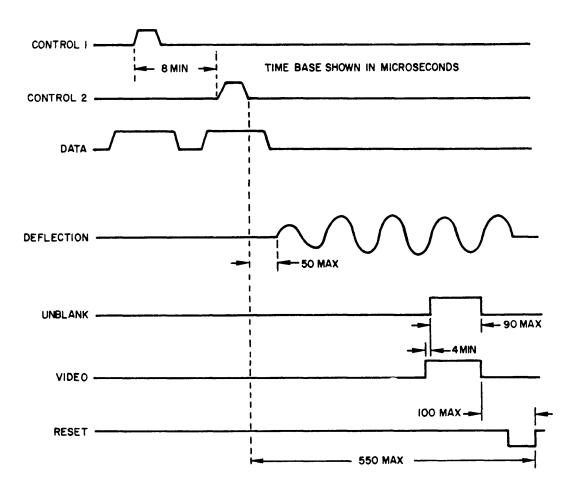

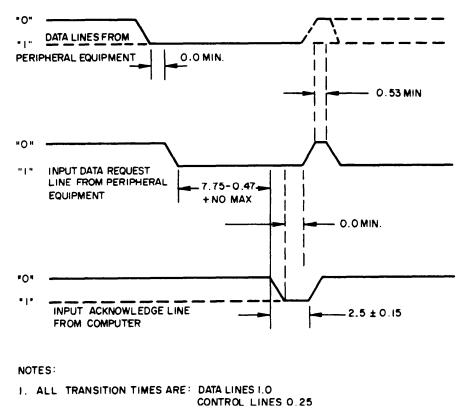

3. 5.1.4.1.1 <u>Functional Description</u> - The computer is capable of servicing 16 input peripheral equipments which utilize the normal input data transfer. The DPS contains more than 16 input peripherals;-however, the rate and priority of the data to many of the the peripherals do not demand real time access to the computer memory: i.e. , many of the peripherals can communicate with the computer via a buffer unit. In the DPS, this common input buffer is termed the Digital Input Multiplexer (DIM). Figure 2 is a functional flow diagram for the DIM. Figure 3 is a timing diagram.

3.5.1.4.1.2 <u>General Description -</u> The DIM shall provide the capability of transmitting up to 12 data bits from each of the 16 input peripherals to the computer via a single computer input channel. The operation of the DIM shall be independent of the Digital Output Multiplexer (DOM) except for test loops.

| 3.5.1.4.1.3 | Operating | Requirements |

|-------------|-----------|--------------|

|             |           |              |

3.5.1.4.1.3.1 Data Transfer - Peripheral Equipment to Computer via Digital <u>Input Multiplexer</u> - An input peripheral equipment which communicates with the computer via the DIM shall be able to transmit one 12-bit word to the computer by following the control line sequence given below:

(1) A peripheral equipment places its data on the 12 data lines

to the DIM.

(2) The peripheral equipment sets the Enter line to the DIM to indicate that it has data ready for transmission.

(3) The DIM detects the Enter signal.

(4) The DIM places the 12 data bits from the peripheral equipment and 4 address bits on the computer data lines.

(5) The DIM sets the Input Data Request line to indicate that it has data ready for transmission to the computer except for channel 11 where it raises an Interrupt.

(6) The computer 1/0 subunit detects the Input Data Request.

(7) The computer samples the 16 data lines, at its convenience.

(8) The computer sets the Input Acknowledge line indicating

that it has sampled the data.

(9) The DIM drops the data lines and the Input Data Request

line.

(10) The DIM sets the Channel Input Acknowledge line to the peripheral equipment indicating that 'the computer has sampled the data lines.

(11) The peripheral equipment drops the data at its convenience. The DIM shall not transmit any further data from this peripheral equipment to the computer until the equipment drops and then sets its Enter line indicating new data.

3.5.1.4.1.3.2

#### Timing, Priority and Initialization

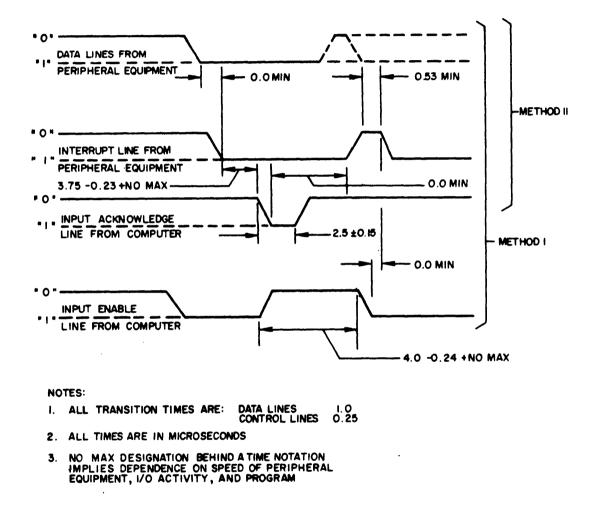

(1) Since the peripheral equipments, which communicate with the computer via the DIM, operate independently of each other, a number of equipments may raise their Enter lines (indicating data is ready for transmission to the computer) simultaneously. The DIM shall sequentially scan the Enter lines from the peripheral equipments, stopping and entering the data from the first peripheral equipment with its Enter line set. The trailing edge of the Input Acknowledge shall start the DIM scanning again: the scan shall commence at the Enter line of the next peripheral equipment in the normal scan sequence. The order in which the DIM scans the peripheral equipments is designated by the channel numbers assigned to the equipments. There shall be no priority in the DIM, except for channel 11; if a number of peripheral equipments simultaneously set their Enter lines, the peripheral equipment serviced first by the DIM shall depend on the position of the scanner; e.g., if peripheral equipments 1, 2, and 8 simultaneously set their Enter lines and the scanner normally scans sequentially from channel O through 15 and the scanner is at channel 6, the data from channel 8 shall be entered first and then channels 1 and 2 shall be serviced in that order before 8 can be serviced again. Upon receipt of a channel 11 Enter, the DIM shall complete the transmission of any channel being processed and then transmit channel 11 data.

(2) The time required for the DIM to scan all the Enter lines from the 16 peripheral equipments, when none of the Enter lines is set, shall not exceed 64 microseconds,

(3) The time between the detection of an active Enter line by the scanner and the raising of the Input Data Request line to the computer shall not exceed six microseconds,

(4) The DIM shall be self-initializing; i.e., when power is applied to the DIM, no spurious data shall be transmitted to the computer and the DIM shall be ready for normal operation.

3.5. 1.4.1.4

Test Loops

3.5. 1.4.1.4.1 <u>In-Flight Performance Monitoring Channels</u> - Two of the channels of the DIM shall be designated as test channels. The setting of the Enter and Data lines for these channels shall be controlled by the computer program via the DOM. The DIM shall scan the Enter lines and transmit the data from these channels the same as it would for any other peripheral equipment. This loop operation, computer to DOM to DIM to computer, shall permit the computer program to monitor automatically the performance of the DOM and DIM. The test loops shall be utilized for inflight performance monitoring and diagnostic programs.

3. 5.1.4.1.5 Interface Requirements - Refer to Figure 2, the functional flow diagram for the DIM.

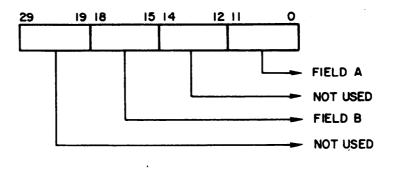

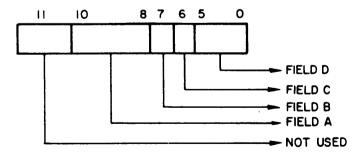

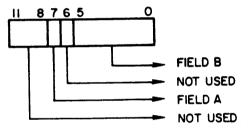

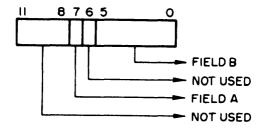

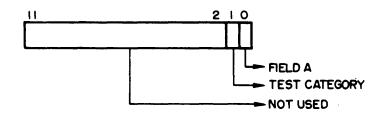

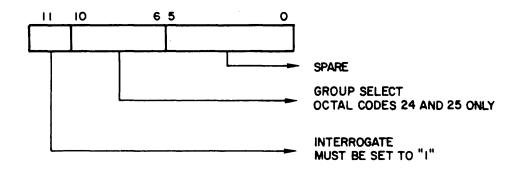

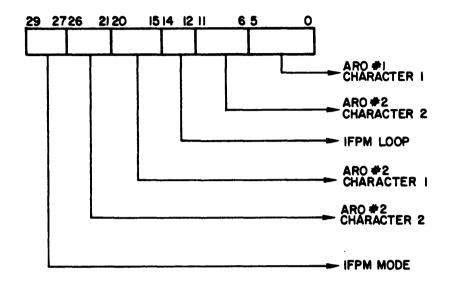

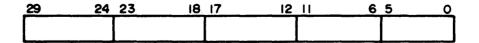

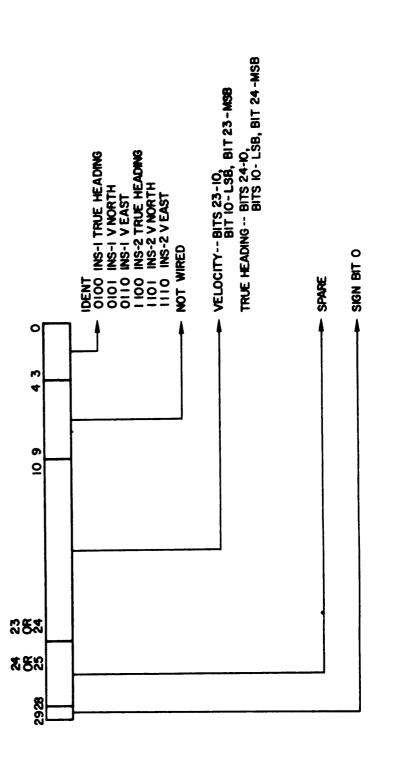

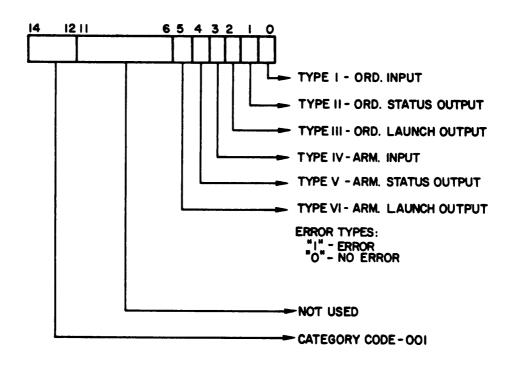

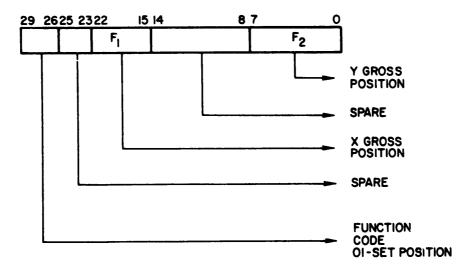

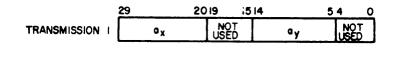

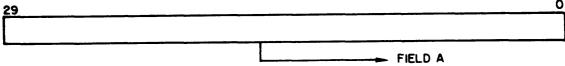

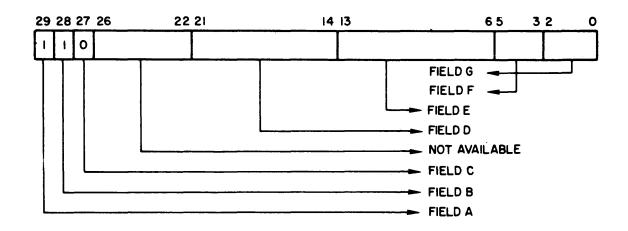

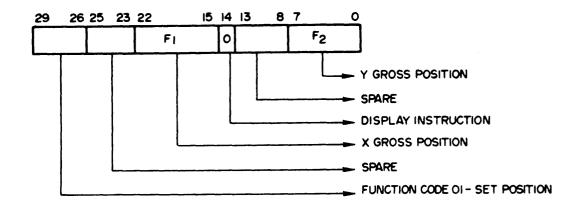

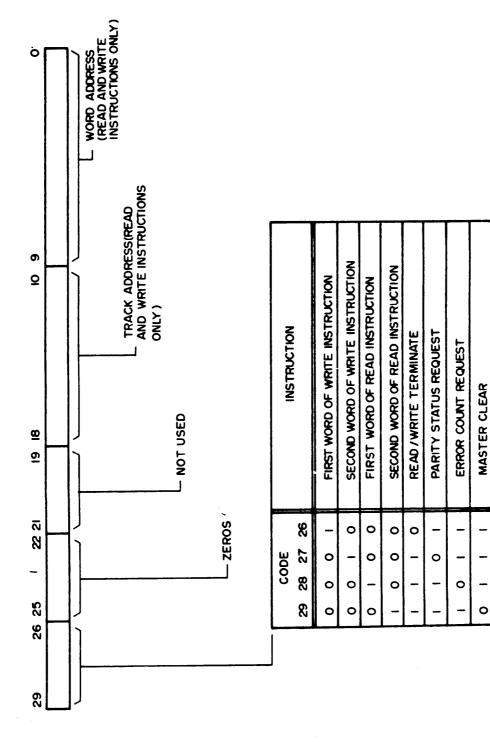

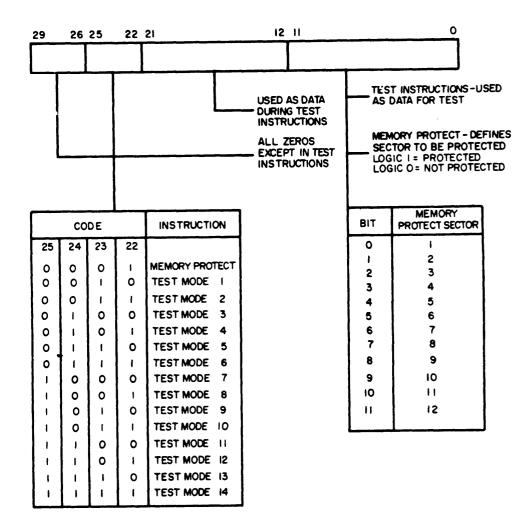

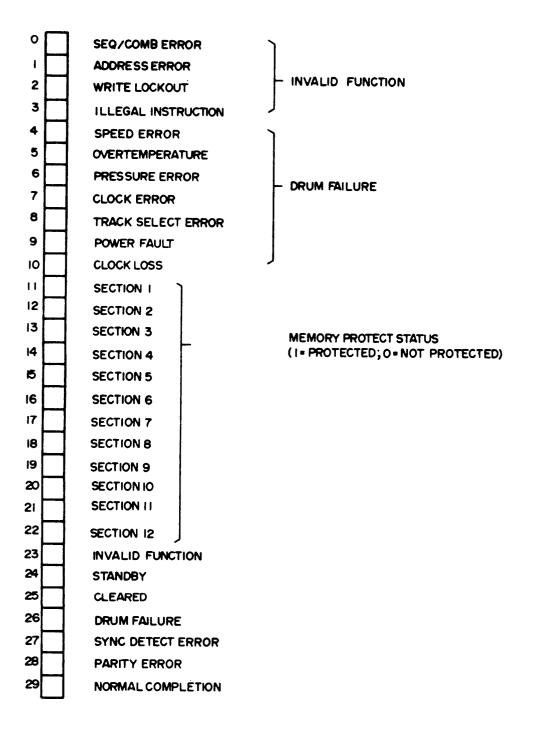

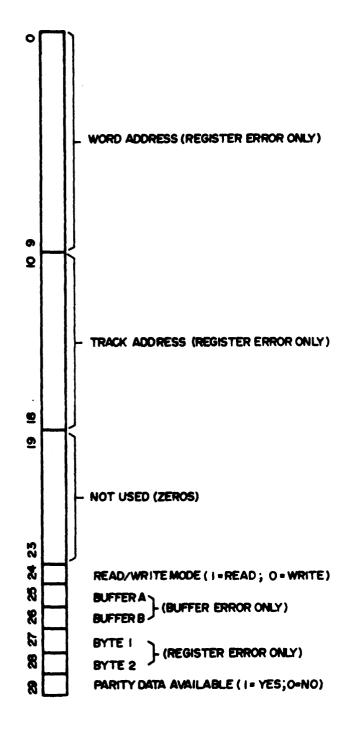

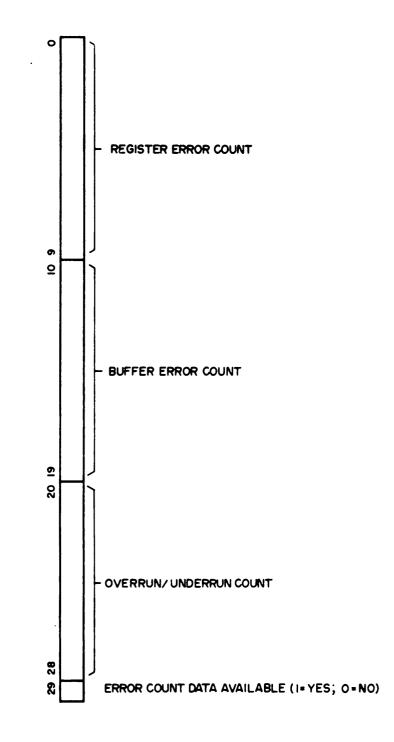

3. 5.1,4.1.5.1 Format of Input Word to Computer from Digital Input Multiplexer - Refer to the format shown in Figure 1.

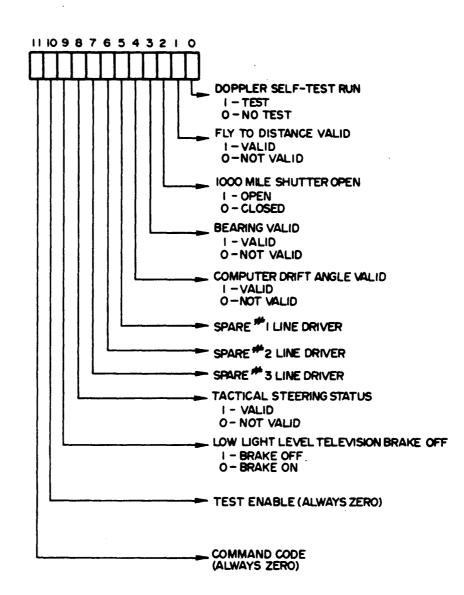

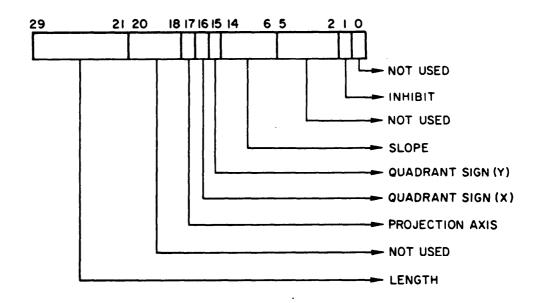

Figure 1. Format of Input Word to Computer from Digital Input Multiplexer

(1) <u>Field A</u> - represents the data bits from the peripheral equipment being serviced by the DIM.

(2) <u>Field B</u> - represents the address of the peripheral equipment selected by the DIM. The functional flow diagram (Figure 2) indicates the DIM channel assignments for the peripheral equipments.

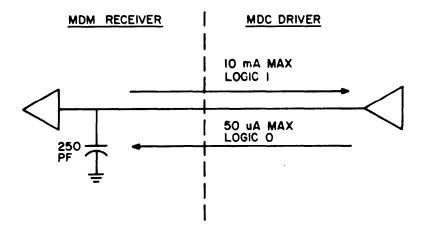

3.5.1.4.1.5.2 <u>Digital Input Multiplexer to Computer</u> - Communications between the computer and the DIM shall be in accordance with Appendix I. Data transfer is accomplished by the Input Data Request/Input Acknowledge scheme.

3.5.1.4.1.5.3 <u>Digital Input Multiplexer to Maintenance Control Panel</u> - Communications between the Maintenance Control Panel and the DIM shall be in accordance with 3.5.1.4.9.

3.5.1.4.1.5.4 Peripheral Equipments Contained Within Logic Unit 1 and Digital Input Multiplexer.

3.5.1.4.1.5.4.1

Signal Characteristics

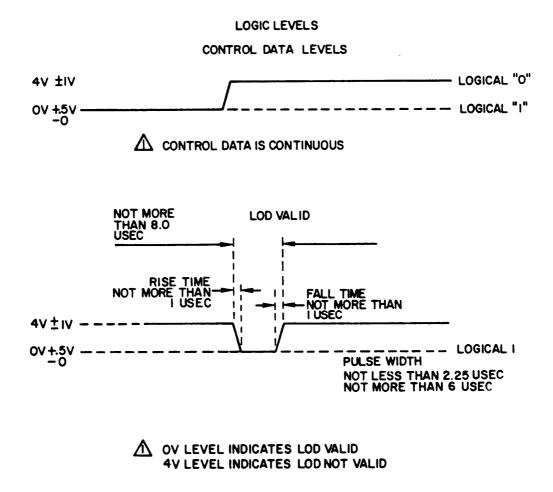

(1) logical "1" =  $+5 \pm 1.5$  volts logical "0" =  $0 \pm 1/2$  -0.0 volts

(2) <u>Enter</u> - The Enter line from a peripheral equipment shall change from a logical "1" to a logical "0" when new data is available. The Enter line shall remain stable for a minimum of 20 milliseconds or until a Channel Input Acknowledge signal is recieved from the DIM.

(3) <u>Data</u> - All data lines from a peripheral equipment shall remain stable for a minimum of 20 milliseconds or until a Channel Input Acknowledge is received by the equipment.

(4) <u>Channel Input Acknowledge</u> - The DIM shall transmit a Channel Input Acknowledge signal to the peripheral when the data from the peripheral equipment has been received by the computer. The Channel Input Acknowledge signal shall be a logical "1" signal of 2.2 microseconds minimum duration. The Channel Input Acknowledge signal indicates to the peripheral equipment that it may drop its Enter line at its convenience. The TACCO, Universal Keysets and Pilot/CRT/ORD Keysets shall not require an Input Acknowledge to reset their Enters.

3.5.1.4.1.5.5 <u>Peripheral Equipments External to Logic Unit 1 (Channels 12, 13, 14, and 15) and Digital Input Multiplexer.</u>

3.5. 1.4.1.5.5.1

Signal Characteristics

(1) logical "l" =  $0 \pm 1/2 - 0.0$  volt logical "0" =  $4 \pm 1$  volts

(2) All signals between the DIM and the external peripheral equipments shall be transmitted over twisted pair cables.

(3) Enter - Same as 3.5.1.4.1.5.4.1 (2)

(4) <u>Data</u> - The data lines from an external peripheral equipment shall be stable at least one microsecond before the Enter line is set and shall remain stable until a Channel Input Acknowledge signal is received from the DIM, The selective enabling of data from an external peripheral equipment for transmission to the computer shall be performed in the DIM and hence no Data Enable signal shall be required for the data to be transmitted from the external peripheral equipment to the DIM.

(6) Channel Input Acknowledge - Same as 3.5.1 .4.1.5.4.1 (4).

.

## 21/22

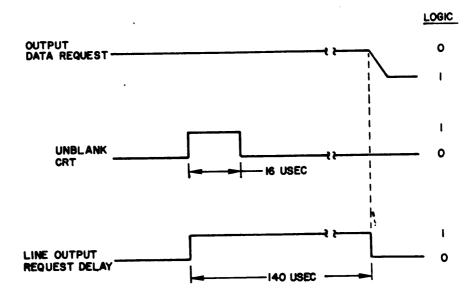

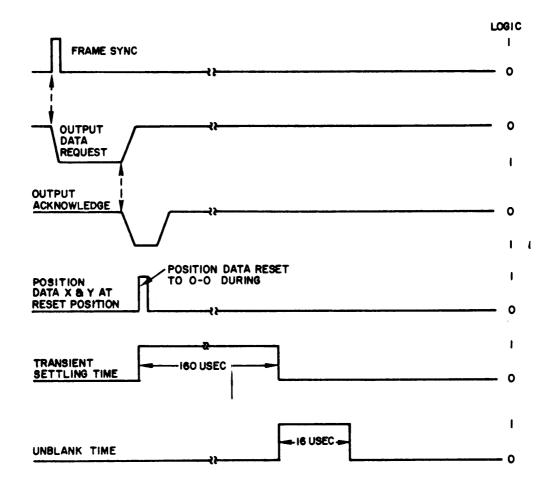

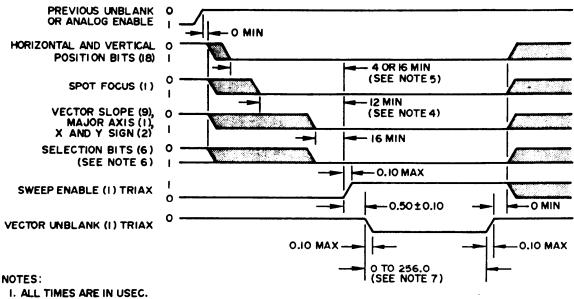

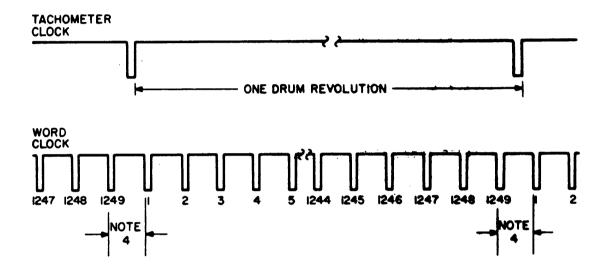

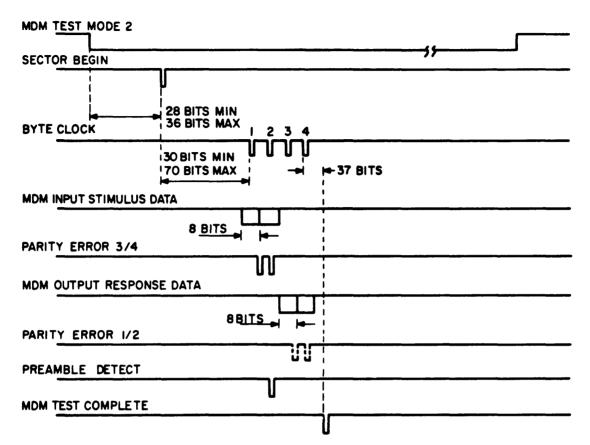

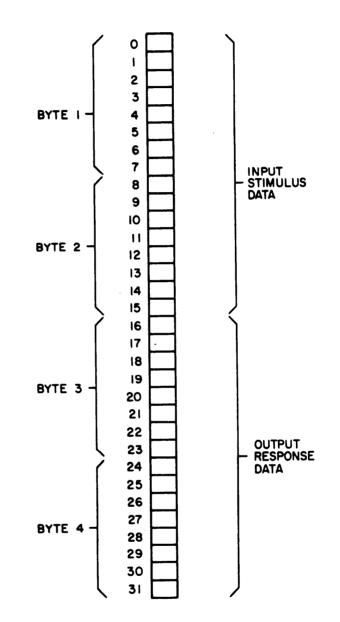

Figure 3. Digital Input Multiplexer, Timing Diagram

23/24

Downloaded from http://www.everyspec.com

# 3.5.1.4.2

# Digital Output Multiplexer

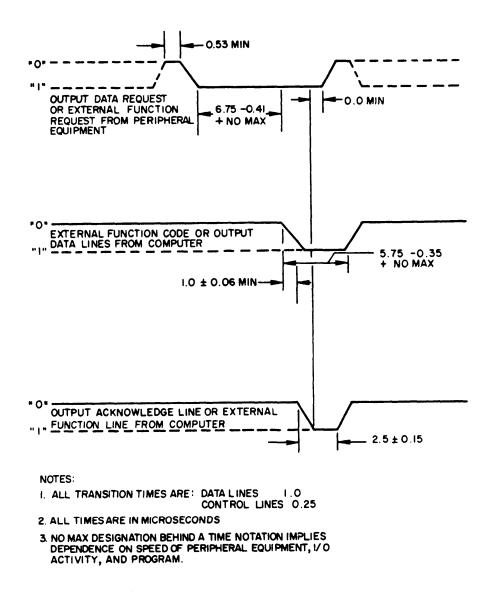

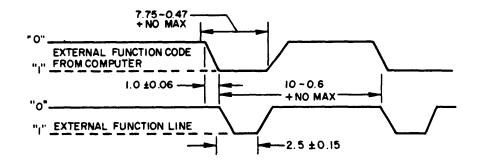

3.5.1.4.2.1 Functional Description - The Computer is capable of servicing 16 output peripheral equipments which utilize the normal output data transfer. The DPS contains more than 16 output peripherals; however, the rate and priority of the data from many of these peripherals do not demand realtime access to the computer memory; i.e., many of the output peripherals can communicate with the computer via a buffer unit. In the DPS, this common output buffer is termed the Digital Output Multiplexer (DOM). Figure 5 is a functional flow diagram for the DOM.

3.5.1.4.2.2 <u>General Description</u> - The DOM shall provide the capability of transmitting up to 12 data bits from the computer to each of 16 output peripherals via a single computer output channel. The operation of the DOM shall be independent of the DIM except for test loops.

#### 3.5.1.4.2.3 Operating Requirements

3.5.1.4.2.3.1 <u>Data Transfer</u> - Computer to Peripheral Equipment via Digital Output Multiplexer - The computer shall be able to output one 12-bit data word to one of the 16 peripheral equipments by following the control sequence given below:

(1) The computer program initiates a normal output buffer for

the channel assigned to the DOM.

is in a condition to accept data.

(3) The computer 1/0 subunit detects the Output Data Request.

(2) The DOM sets the Output Data Request line indicating that it

(4) The computer, at its convenience, places 12 data bits and

4 address bits (identifying the peripheral equipment to receive the data) on 16 computer data lines.

(5) The DOM transmits the 12 data bits to each of the 16 periph-

eral units.

(6) The computer sets the Output Acknowledge line, indicating that the data is ready for sampling.

(7) The Digital Output Multiplexer decodes the address and

transmits the Output Acknowledge signal to the peripheral equipment specified by the address code.

(8) The peripheral equipment, upon receipt of the Output Acknowledge signal from the DOM, samples the 12 data lines.

(9) The Computer drops the Output Acknowledge.

(10) The DOM drops the Output Acknowledge to the peripheral equipment, indicating that the period for sampling the data is terminated.

3.5.1.4.2.3.2 <u>Timing</u> - The DOM shall be capable of processing one computer output word every 10 microseconds.

#### 3.5.1.4.2.4 <u>Test Loops</u>

3.5.1.4.2.4.1 <u>In-Flight Performance Monitoring Channels</u> - Two of the channels (5 and 10) of the DOM shall be designated as test channels. When the computer program addresses these channels, the 12 data bits accompanying the test channel addresses shall be stored in the DOM. When the data is stable, the DOM shall set the Enter line of the DIM channel corresponding to the test channel addressed by the computer; i.e., if the computer transmits data to channel 5, the DOM shall set the Enter line and transmit the stored data on the DIM channel 5 input data lines; the Enter line and data shall be reset when a Channel Input Acknowledge signal is received from the DIM: the same procedure shall be followed for DOM channel 10. This loop operation, computer to DOM to DIM to computer, shall permit the computer program to monitor automatically the performance of the DOM and DIM. The test loops shall be utilized for in-flight performance monitoring and diagnostic programs.

3.5.1.4.2.5 diagram for the DOM. Interface Requirements - Refer to Figure 5, the functional flow

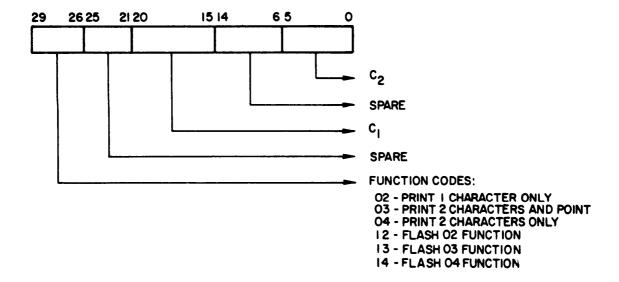

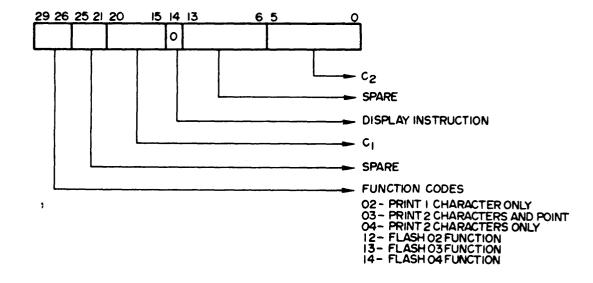

3.5.1.4.2.5.1

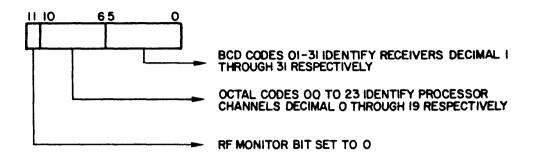

Format of Output Word to Digital Output Multiplexer from

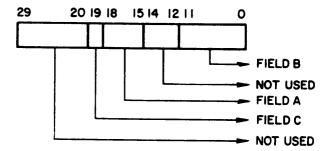

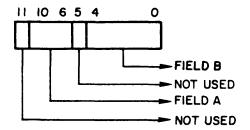

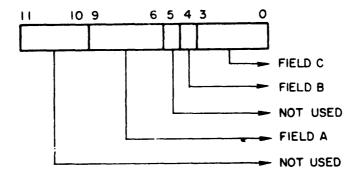

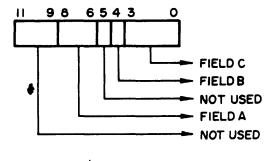

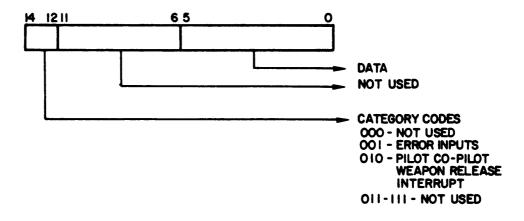

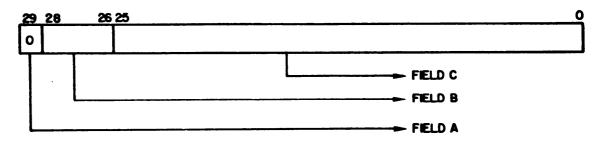

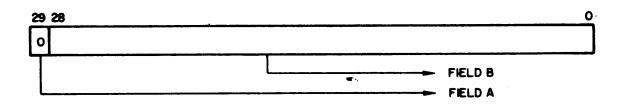

Computer - Refer to Figure 4.

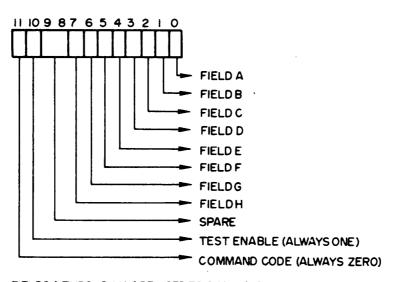

Figure 4. Format of Output Word to Digital Output Multiplexer from Computer

(1) Field A - Represents the address of the peripheral equipment which shall receive the channel Output Acknowledge indicating that the peripheral equipment should sample the data lines from the DOM.

(2) Field B - Represents the data for the peripheral equipment,

(3) Field C - A general clear to all DIM-DOM internal charnels.

3.5.1.4.2,5.2 Computer to Digital Output Multiplexer via Maintenance Control Panel - Communications between the Computer and the DOM shall be in accordance with Appendix I and the Maintenance Control Panel description in 3.5.1.4.9.

| 3.5.1.4.2.5,3<br>Output Multiplexer | Peripheral Equipments Contained Within Logic Unit 1 and Digital |

|-------------------------------------|-----------------------------------------------------------------|

| 3.5.1.4.2.5.3.1                     | Signal Characteristics                                          |

(1) logical "0" = 0.0=0.5-0.0 volts logical "1" =  $+5 \pm 1.5$  volts

(2) Channel Output Acknowledge Signal - The DOM shall transmit a Channel Output Acknowledge signal to a peripheral equipment when bits 15 - 18 of an output word from the computer contain the binary equivalent of the 'peripheral equipment channel address. The channel addresses for each of the peripheral equipments are shown in the functional flow diagram for the DOM (Figure 5). The Channel Output Acknowledge shall be a logical "l" signal of 2.2 microsecond minimum duration.

(3) <u>Data</u> - The DOM shall transmit the data received from the Computer to each of the 16 peripheral equiments. The data lines to the peripheral equipments shall have the same timing as that specified for normal output in Appendix 1.

| 3.5. 1,4.2.5.4<br><u>Output Multiplexer</u> | Peripheral Equipments External to Logic Unit 1 and the Digital                            |

|---------------------------------------------|-------------------------------------------------------------------------------------------|

| 3.5. 1.4.2.5.4.1                            | Signal Characteristics                                                                    |

|                                             | (1) logical "1"= 0.0+0.5-0. Volt<br>logical "0" = $+4 \pm 1$ Volts                        |

| ments shall be transmitted over tw          | (2) All signals between the DOM and the external peripheral equip-<br>visted pair cables. |

(3) Channel Output Acknowledge - Same as 3.5.1 .4.2.5.3.1 (2).

(4) Data -Same as 3.5.1.4.2.5.3.1 (3).

Figure 5. Digital Output Multiplexer, Functional Flow Diagram

Downloaded from http://www.everyspec.com

# 3.5.1.4.3

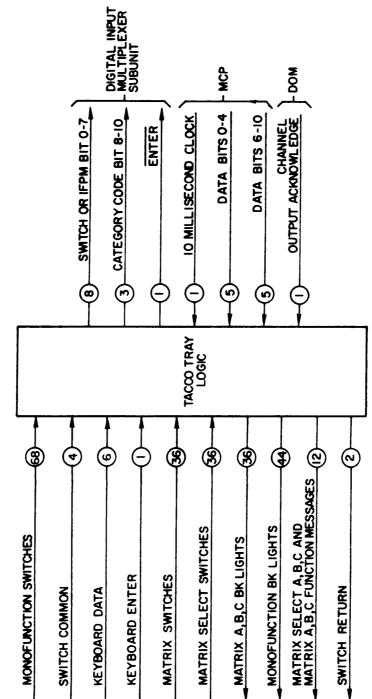

TACCO Tray Logic

3.5.1.4.3.1 Functional Description - The TACCO Tray Logic (TTL) is an interface unit between the TACCO Tray and the computer (via the Digital Input/Output Multiplexer). The TACCO Tray will be a physical part of the MPD Display Console, located at the TACCO Station. The TACCO Tray provides the operator with the controls needed to execute the tactical situation. Using the controls on the Tray, the TACCO can utilize the DPS and computer to:

(1) Communicate with the sensor operators.

(2) Control the display of data from the sensor operators and the major subsystems on the MPD Display at the TACCO station.

(3) Initiate computer implemented functions which affect the operation of the Navigation, Communication, Sensor, Armament, and Ordnance subsystems.

Figure 8 is a functional flow diagram for the TTL.

3.5.1.4.3.2 <u>General Description</u> - The TACCO Tray Logic shall provide:

(1) The encoding and transmission of data from the TACCO Tray

to the computer.

(2) The decoding and storage of data from the computer to the

TACCO Tray.

3.5.1.4.3.3 operating Requirements - The TTL shall detect the depression of any switch on the tray and transmit a code identifying the depressed switch to the computer via the DIM. The operator will not have two switches depressed at the same time. The TTL shall interpret the computer output word received from the DOM and perform one of the following operations:

(1) Store the four bits of the computer word which specify the combination of function messages to be illuminated on the Matrix A Readout switches and the Matrix Select A switch to be lit. This four bit code shall be supplied to the TACCO Tray.

(2) Store the four bits of the computer word which specify the combination of function messages to be illuminated on the Matrix B Readout switches and the Matrix Select B switch to be lit. This four bit code shall be supplied to the TACCO Tray.

(3) Store the four bits of the computer word which specify the combination of function messages to be illuminated on the Matrix C Readout switches and the Matrix Select C switch to be lit. This four bit code shall be supplied to the TACCO Tray.

(4) Set or reset one of the 36 flip-flops. Each flip-flop shall control the illumination of the colored backfground (message 12) on one of the Matrix A, B, and C Readout switches. An output from each of the flip-flops shall be supplied to the TACCO Tray.

(5) Reset the 12 flip-flops which control the illumination of the colored background (message 12) on the Matrix A Readout switches.

(6) Reset the 12 flip-flops which control the illumination of the colored background (message 12) on the Matrix B Readout switches.

(7) Reset the 12 flip-flops which control the illumination of the coolered background (message 12) on the Matrix C Readout switches.

(8) Set or reset one of 44 flip-flops. Each flip-flop shall control the illumination of the colored background on one of the 44 computer lit Monofunction switches. An output from each of the flip-flops shall be supplied to the TACCO Tray.

(9) Reset 24 of the flip-flops which control the illumination of a colored background on 24 of the Monofunction switches.

(10) Reset the 20 flip-flops not covered in (9). Each flip-flop controls the illumination of a colored background on a Monofunction switch.

(11) Enable one of the test loops contained in the TTL.

The TTL shall be self-initializing; i.e., when power is applied to the TTL, no spurious data shall be transmitted to the DIM and the TTL shall be ready for normal operation.

3.5.1.4.3.4 <u>Test Loops</u> - Test loops shall be designed into the TTL. The test loops shall permit the computer program to exercise the TTL and monitor the performance for possible logic malfunctions. The test loops shall be comprehensive; i.e., they shall exercise every logic element in the TTL in all of its functions insofar as possible. The test loops shall be utilized for inflight performance monitoring (IFPM) and diagnostic programs.

3.5.1.4.3.5 Interface Requirements - Refer to the functional flow diagram for the TTL Subunit (Figure 8).

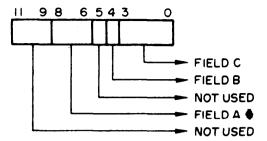

3.5.1.4.3.5.1 <u>Tray Logic</u> - Refer to Figure 6. Format of Input Word to Digital Input Multiplexer from TACCO

(1) <u>Field A</u> - Identifies the switch group transmitting the data.

| BIT | 10 | 9 | 8 |                                                              |

|-----|----|---|---|--------------------------------------------------------------|

|     | 0  | 0 | 0 | - self encoding keyboard or (30)<br>Monofunction switch data |

|     | 0  | 0 | 1 | - (38) Monofunction switch data                              |

|     | 0  | 1 | 0 | - Matrix Select switch data                                  |

|     | 1  | 0 | 0 | - Matrix data                                                |

(2) Field B - Identifies test loop operation data; i. e, , if bit 7

is a logical "I", the data contained in the remainder of the input word to the computer is not the result of a switch depression on the TACCO Tray but is due to test loop operation of the TTL by the computer program.

(3) <u>Field C</u> - Distinguishes self-encoding keyboard data from the Monofunction data in the switch group, identified by Field A being binary zero. Keyboard data is identified by a logical "1" in this position.

Figure 6. Format of Input Word to Digital Input Multiplexer from TACCO Tray Logic

(4) <u>Field D-</u> Identifies the switch or key depressed in the witch group or it contains the data resulting from test loop operation.

NOTE

Bits 0-10 of the input word to the DIM will constitute bits 0-10 of the input word to the computer from the DIM .

3.5.1.4.3.5.2 <u>Multiplexer</u> - Refer to Figure 7.

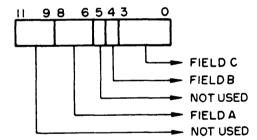

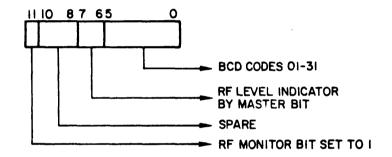

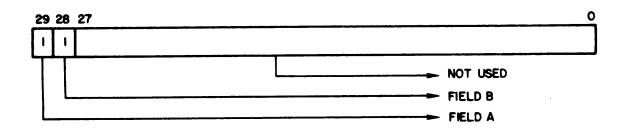

Format of Output Word to TACCO Tray Logic from Digital Output

Figure 7. Format of Output Word to TACCO Tray Logic from Digital Output Multiplexer

(1) Field A- Indicates which of the following operations is to be

performed:

indicate one of the following:

(a) The flip-flop specified by Field B shallbe set or reset. The flip-flop may control the lighting of a colored background on a Monofunctionor Matrix switch, or the flip-f lop may control the enabling of a test loop.

(b) Reset a group of flip-flops. The flip-flop may control the illumination of colored backgrounds on the Matrix A or Matrix B or Matrix C switches or Monofunction switch group 1 or 2,

(c) Bits 0-3 of Field B constitute a message combination selection code for Matrix A, or B, or C and shall be stored in the appropriate register.

(2) Field B - Depending upon the Field A code, this field shall

(a) The flip-flop to be set or reset

(b) The Matrix message combination selection code

3.5.1.4.3.5.3 <u>TACCO Tray Logic to Digital Input Multiplexer</u> - Communications between the TTL and DIM shall be in accordance with 3.5.1.4.1.

3.5.1.4.3.5.4 <u>Digital Output Multiplexer to TACCO Tray Logic</u> - Communications between the DOM and the TTL shall be in accordance with 3.5.1.4.2.

3.5.1.4,3.5.5 <u>Clock Signal from Maintenance Control Panel Logic to TACCO</u> <u>Tray Logic</u> - A 10 millisecond clock signal for the TTL shall be generated in the MCPL.

3.5.1.4.3.5.6 Data Bits 0-4 from Maintenance Control Panel Logic to TACCO Tray Logic - Computer output data bits 0-4 shall be buffered in the MCPL.

| 3.5.1.4.3.5.7   | TACCO Tray to TACCO Tray Logic                          |

|-----------------|---------------------------------------------------------|

| 3.5.1.4.3.5.7.1 | Signal Characteristics                                  |

|                 | (1) logical "1"= 0.0+0.5-0.0 Volt<br>logical "0" = open |