The documentation and process conversion measures necessary to comply with this revision shall be completed by 10 September 2014.

**INCH-POUND**

MIL-PRF-19500P w/AMENDMENT 2 10 April 2014 SUPERSEDING MIL-PRF-19500P w/AMENDMENT 1 16 May 2012

# PERFORMANCE SPECIFICATION

# SEMICONDUCTOR DEVICES, GENERAL SPECIFICATION FOR

Comments, suggestions, or questions on this document should be addressed to: DLA Land and Maritime, ATTN: VAC, P.O. Box 3990, Columbus, OH 43218-3990 or emailed to <a href="mailto:semiconductor@dla.mil">semiconductor@dla.mil</a>. Since contact information can change, you may want to verify the currency of this address information using the ASSIST Online database at <a href="https://assist.dla.mil">https://assist.dla.mil</a>.

AMSC N/A FSC 5961

This page intentionally left blank.

| <u>PARAGRAPH</u>                                                                              | <u>PAGE</u> |

|-----------------------------------------------------------------------------------------------|-------------|

| 1. SCOPE                                                                                      | 1           |

| 1.1 Scope                                                                                     |             |

| 1.2 Description                                                                               |             |

| 1.3 Identification                                                                            |             |

| 1.3.1 Quality level for encapsulated devices                                                  | 1           |

| 1.3.2 Quality level for unencapsulated devices.                                               |             |

| 1.3.3 Manufacturers and critical interface identifiers                                        | 2           |

| 1.3.4 RHA designator                                                                          |             |

| 1.3.5 Component designation                                                                   |             |

| 1.3.6 Identification number                                                                   |             |

| 1.3.7 Suffix letters                                                                          |             |

| 1.3.8 Device substitutions.                                                                   |             |

| 2. APPLICABLE DOCUMENTS                                                                       | 3           |

| 2.1 General                                                                                   |             |

| 2.2 Government documents                                                                      | 3           |

| 2.2.1 Specifications, standards, and handbooks                                                | 3           |

| 2.3 Non-Government publications.                                                              |             |

| 2.4 Order of precedence                                                                       |             |

| 3. REQUIREMENTS                                                                               | 4           |

| 3.1 Specification sheets                                                                      |             |

| 3.1.1 Implementation date                                                                     |             |

| 3.2 Qualification                                                                             |             |

| 3.2.1 Certification options                                                                   |             |

| 3.2.2 Allowable alternate design, materials, and construction                                 |             |

| 3.3 Performance requirements for JAN, JANTX, JANTXV, and JANS devices, and JANHC and JANKC of | lie5        |

| 3.4 Reference to specification sheets                                                         |             |

| 3.5 Certification                                                                             |             |

| 3.5.1 Transitional certification to appendix C                                                | 5           |

| 3.5.2 DMS approval                                                                            |             |

| 3.5.3 DMS listing                                                                             | 6           |

| 3.5.4 MIL-STD-750 laboratory suitability.                                                     | 6           |

| 3.6 Traceability.                                                                             | 6           |

| 3.7 Certification of conformance and acquisition traceability.                                |             |

| 3.8 Critical interface and materials                                                          | /           |

| 3.9 Lead and terminal finish                                                                  |             |

| 3.10 Marking                                                                                  |             |

| 3.10.2 Marking on initial container (unit package).                                           |             |

| 3.10.3 Special marking                                                                        |             |

| 3.10.3.1 ESDS identifier                                                                      |             |

| 3.10.3.2 Beryllium oxide package identifier                                                   |             |

| 3.10.4 Marking legibility                                                                     | ۰<br>و      |

| 3.10.5 Polarity marking of unidirectional diodes and thyristors.                              | 8           |

| 3.10.5.1 Diodes.                                                                              |             |

| 3.10.5.2 Thyristors                                                                           |             |

| 3.10.6 PIN                                                                                    |             |

| 3.10.6.1 JAN and J marking                                                                    |             |

| 3.10.6.1.1 JAN branded prefix                                                                 |             |

| 3.10.7 Manufacturer's designating symbol.                                                     |             |

| 3.10.8 Lot identification code                                                                |             |

| 3.10.8.1 Lot identification code suffix letter.                                               |             |

| 3.10.8.2 Code for plants                                                                      |             |

| 3.10.9 Serialization                                                                          |             |

| 3.10.10 DMS marking                                                                           |             |

| 3.10.11 Country of origin                                                                     |             |

|                                                                                               |             |

| PARAGRAPH CONTENTS                                                         | <u>PAGE</u> |

|----------------------------------------------------------------------------|-------------|

| 3.10.12 Manufacturer's name, abbreviation, or trademark                    | 10          |

| 3.10.13 Marking option                                                     | 10          |

| 3.11 Solderability                                                         |             |

| 3.12 ESD control.                                                          |             |

| 3.13 Recycled, recovered, environmentally preferable or biobased materials |             |

| 3.14 Pure tin                                                              |             |

| 3.15 Workmanship                                                           |             |

| 4. VERIFICATION                                                            |             |

| 4.1 Classification of inspections                                          |             |

| 4.2 Quality system                                                         |             |

| 4.3 Device verification                                                    |             |

| 4.4 Test modification, reduction, or elimination                           | 11          |

|                                                                            |             |

| 5.1 Packaging5.2 Shipping containers                                       |             |

| 6. NOTES                                                                   |             |

| 6.1 Intended use                                                           |             |

| 6.2 Acquisition requirements                                               |             |

| 6.2.1 Order requirements                                                   |             |

| 6.3 Qualification                                                          |             |

| 6.4 Supersession information                                               |             |

| 6.4.1 Methods of qualification                                             |             |

| 6.4.2 QML format                                                           |             |

| 6.5 Subject term (key word) listing                                        |             |

| 6.6 PIN                                                                    | 14          |

| 6.7 Environmentally preferable material                                    | 14          |

| 6.8 Tin whisker growth                                                     | 14          |

| 6.9 Amendment notations                                                    |             |

| DEFINITIONS                                                                |             |

| A.1 SCOPE                                                                  |             |

| A.1.1 Scope                                                                |             |

| A.2 APPLICABLE DOCUMENTS                                                   | 15          |

| A.3 SEMICONDUCTOR COMMON DEFINITIONS                                       |             |

| A.3.1 Absolute maximum ratings                                             |             |

| A.3.2 Ambient temperature                                                  |             |

| A.3.3 Anode                                                                |             |

| A.3.4 Assembly lot.                                                        |             |

| A.3.4.1 Sublot                                                             |             |

| A.3.5 Specification sheet                                                  |             |

| A.3.5.1 MIL-STD-750 details                                                |             |

| A.3.7 Breakdown voltage                                                    |             |

| A.3.8 Case mount.                                                          |             |

| A.3.9 Case mount.                                                          |             |

| A.3.10 Case temperature                                                    |             |

| A.3.11 Cathode                                                             |             |

| A.3.12 Characteristic                                                      |             |

| A.3.13 Control plans                                                       |             |

| A.3.14 Constant current source                                             |             |

| A.3.15 Constant voltage source                                             |             |

| A.3.16 Disc type                                                           |             |

| A.3.17 Engineering evaluation                                              |             |

| A.3.18 Expanded metallization                                              |             |

| A.3.19 Failure analysis                                                    |             |

| A.3.20 Forward bias                                                        |             |

| CONTENTS                                                                          |             |

|-----------------------------------------------------------------------------------|-------------|

| <u>PARAGRAPH</u>                                                                  | <u>PAGE</u> |

| A.3.21 Failure mode and effects analysis (FMEA)                                   | 17          |

| A.3.22 Hermetically sealed package                                                |             |

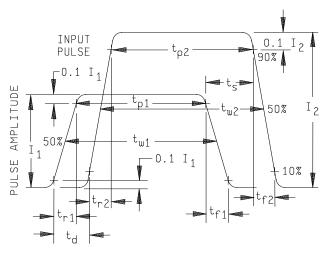

| A.3.23 Impulse waveform                                                           | 18          |

| A.3.23.1 Virtual front duration                                                   |             |

| A.3.23.2 Impulse duration                                                         |             |

| A.3.24 Internal Free Cavity Volume                                                |             |

| A.3.25 Line                                                                       |             |

| A.3.26 Metallurgical bond, diode construction, and thermal matching.              |             |

| A.3.26.1 Double plug construction                                                 |             |

| A.3.26.2 Dash-one construction                                                    |             |

| A.3.26.3 Category I metallurgical bond                                            |             |

| A.3.26.4 Category II metallurgical bond                                           |             |

| A.3.26.5 Category III metallurgical bond                                          |             |

| A.3.26.6 Non-cavity double plug diode                                             |             |

| A.3.26.7 Thermally matched axial leaded diodes                                    |             |

| A.3.26.8 Metallurgically bonded-thermally matched-noncavity double plug construct |             |

| A.3.27 Noise figure                                                               |             |

| A.3.28 Open circuit.                                                              |             |

| A.3.29 Package type                                                               |             |

| A.3.29.1 Case isolated package                                                    |             |

| A.3.29.2 Metal Electrode Leadless Face (MELF).                                    |             |

| A.3.30 Pulse                                                                      | 19          |

| A.3.31 Pulse average time                                                         | 20          |

| A.3.32 Pulse delay time                                                           | 20          |

| A.3.33 Pulse fall time.                                                           | 20          |

| A.3.34 Pulse rise time.                                                           |             |

| A.3.35 Pulse storage time                                                         |             |

| A.3.36 Pulse time                                                                 |             |

| A.3.37 Radiation failures                                                         |             |

| A.3.38 Radiation hardness assurance (RHA).                                        |             |

| A.3.39 Rating                                                                     |             |

| A.3.40 Reverse bias                                                               |             |

| A.3.41 Semiconductor devices                                                      |             |

| A.3.41.1 Die design                                                               |             |

| A.3.42 Semiconductor diode                                                        |             |

| A.3.43 Semiconductor junction                                                     |             |

| A.3.44 Short circuit                                                              |             |

| A.3.45 Small signal                                                               |             |

| A.3.46 Storage temperature                                                        |             |

| A.3.47 Stack junction rectifier diode                                             |             |

| A.3.48 Temperature coefficient                                                    |             |

| A.3.50 Thermal equilibrium                                                        |             |

| A.3.51 Thermal regulation A.3.51 Thermal resistance                               |             |

|                                                                                   |             |

| A.3.52 Thyristor                                                                  |             |

| A.4 TRANSISTOR DEFINITIONS                                                        |             |

| A.4.1 Junction transistors, multijunction types                                   |             |

| A.4.1.1 Base                                                                      |             |

| A.4.1.2 Collector                                                                 |             |

| A.4.1.3 Cutoff current                                                            |             |

| A.4.1.4 Emitter                                                                   |             |

| A.4.1.5 Junction, collector                                                       |             |

| A.4.1.6 Junction, emitter                                                         |             |

| A.4.1.7 Saturation                                                                |             |

| / C. T. T. Odlaration                                                             |             |

| CONTENTS                                                       |             |

|----------------------------------------------------------------|-------------|

| <u>PARAGRAPH</u>                                               | <u>PAGE</u> |

|                                                                | •           |

| A.4.2 Unijunction transistors                                  |             |

| A.4.2.1 Peak point                                             |             |

| A.4.2.2 Unijunction transistor                                 |             |

| A.4.2.3 Valley point                                           |             |

| A.4.3 Field-effect transistors (FET).                          | 22          |

| A.4.3.1 Depletion-mode operation                               |             |

| A.4.3.2 Depletion-type FET                                     | 22          |

| A.4.3.3 Drain                                                  |             |

| A.4.3.4 Enhancement-mode operation                             | 22          |

| A.4.3.5 Enhancement-mode FETA.4.3.6 FET                        |             |

|                                                                |             |

| A.4.3.7 Gate                                                   |             |

| A.4.3.8 Insulated-gate FET                                     | 22          |

| A.4.3.10 MOSEET                                                |             |

| A.4.3.10 MOSFET                                                |             |

| A.4.3.11 N-channel FETA.3.12 P-channel FET                     |             |

|                                                                |             |

| A.4.3.13 SourceA.5 DIODE AND RECTIFIER DEFINITIONS             |             |

|                                                                |             |

| A.5.1 Signal diodes and rectifier diodes.                      |             |

| A.5.1.1 Semiconductor rectifier diode                          |             |

| A.5.1.2 Semiconductor signal diode                             |             |

| A.5.2 Microwave diodes                                         |             |

| A.5.2.1 Detector diode                                         |             |

| A.5.2.2 Gunn diode.                                            |             |

| A.5.2.3 Impact, avalanche, and transit time diode (IMPATT).    |             |

| A.5.2.4 Limited space-charge accumulation diode (LSA)          |             |

| A.5.2.5 Matched pair                                           |             |

|                                                                |             |

| A.5.2.7 Mixer diode                                            |             |

| A.5.2.6 Trapped plasma availanche transit time diode (TRAFATT) |             |

| A.5.3.1 Tunnel diodes                                          |             |

| A.5.3.2 Backward diode                                         |             |

| A.5.2 Voltage-regulator and voltage-reference diodes           |             |

| A.5.4.1 Voltage-reference diode                                | 22          |

| A.5.4.2 Voltage-regulator diode                                | 23          |

| A.5.5 Current-regulator diodes                                 |             |

| A.5.5.1 Current-regulator diodes                               |             |

| A.5.6 Varactor diodes.                                         |             |

| A.5.6.1 Varactor diodes.                                       |             |

| A.5.6.2 Tuning diode                                           |             |

| A.5.7 Transient voltage suppressors                            |             |

| A.5.7 Transient voltage suppressors                            |             |

| A.5.7.2 Avalanche-junction                                     |             |

| A.5.7.3 Clamping voltage                                       |             |

| A.5.7.4 Clamping factor                                        |             |

| A.5.7.5 Peak impulse current                                   |             |

| A.5.7.6 Standby current                                        |             |

| A.5.7.7 Repetitive peak pulse power                            |             |

| A.5.7.8 Response time                                          |             |

| ·                                                              |             |

| A.5.7.9 Voltage overshootA.5.7.10 Forward surge current        |             |

| A.5.7.10 Forward surge current                                 |             |

| A.6. CLASSES OF THYRISTORS DEFINITIONS                         |             |

| CONTENTS                                                                       |             |

|--------------------------------------------------------------------------------|-------------|

| <u>PARAGRAPH</u>                                                               | <u>PAGE</u> |

| A.C.4. Thuristan                                                               | 0.4         |

| A.6.1 Thyristor                                                                |             |

| A.6.1.1 Bi-directional diode thyristor                                         |             |

|                                                                                |             |

| A.6.1.3 N-gate thyristor                                                       |             |

| A.6.1.5 Reverse blocking diode thyristor.                                      |             |

| A.6.1.6 Reverse blocking triode thyristor                                      |             |

| A.6.1.7 Reverse conducting diode thyristor                                     |             |

| A.6.1.8 Reverse conducting triode thyristor                                    |             |

| A.6.1.9 Turn off thyristor                                                     |             |

| A.6.2 Physical structure terms                                                 |             |

| A.6.2.1 Gate                                                                   |             |

| A.6.2.2 Main terminals                                                         |             |

| A.6.3 Electrical characteristic and rating terms                               |             |

| A.6.3.1 Anode to cathode voltage-current characteristic (anode characteristic) |             |

| A.6.3.2 Breakover point                                                        |             |

| A.6.3.3 Negative differential resistance region                                |             |

| A.6.3.4 Off impedance                                                          | 25          |

| A.6.3.5 Off-state                                                              |             |

| A.6.3.6 On impedance                                                           |             |

| A.6.3.7 On-state                                                               |             |

| A.6.3.8 Principal current                                                      |             |

| A.6.3.9 Principal voltage                                                      |             |

| A.6.3.10 Principal voltage-current characteristic (principal characteristic)   |             |

| A.6.3.11 Reverse blocking impedance.                                           |             |

| A.6.3.12 Reverse blocking state                                                |             |

| A.6.3.13 Switching quadrant                                                    |             |

| A.7 OPTOELECTRONIC DEVICE DEFINITIONS                                          | 26          |

| A.7.1 Optoelectronic device                                                    |             |

| A.7.1.1 Conversion efficiency                                                  |             |

| A.7.1.2 Dark condition                                                         |             |

| A.7.1.3 Dark current                                                           |             |

| A.7.1.4 Light current                                                          |             |

| A.7.1.5 Photoconductive diode                                                  |             |

| A.7.1.6 Photocurrent                                                           |             |

| A.7.1.7 Photodiode                                                             |             |

| A.7.1.8 Photodiode, avalanche                                                  |             |

| A.7.1.9 Photoemitter                                                           |             |

| A.7.1.10 Photosensitive device                                                 |             |

| A.7.1.11 Photothyristor                                                        |             |

| A.7.1.12 Phototransistor                                                       | 26          |

| A.7.1.13 Photovoltaic diode                                                    | 26          |

| A.7.2 Photoemitting devices                                                    | 26          |

| A.7.2.1 Avalanche luminescent diode                                            | 26          |

| A.7.2.2 Infrared emitting diode                                                |             |

| A.7.2.3 Light emitting diode                                                   |             |

| A.7.2.4 Radiant efficiency                                                     | 26          |

| A.7.3 Optocouplers                                                             | 27          |

| A.7.3.1 Photodarlington coupler                                                |             |

| A.7.3.2 Photodiode coupler                                                     |             |

| A.7.3.3 Photothyristor coupler                                                 | 27          |

| A.7.3.4 Phototransistor coupler                                                | 27          |

| A.8 ELECTRICAL AND ENVIRONMENTAL STRESS SCREENING DEFINITIONS                  | 27          |

| A.8.1 Electrical and environmental stress screening                            | 27          |

| A.8.2 Power burn-in                                                            | 27          |

| <u>PARAGRAPH</u>                                            | <u>PAGE</u> |

|-------------------------------------------------------------|-------------|

| A.8.2.1 Rectifying ac power burn-in                         | 27          |

| A.8.2.2 Steady-state dc power burn-in                       |             |

| A.8.3 High temperature reverse bias                         |             |

| A.8.3.1 Steady-state dc high temperature reverse bias       |             |

| A.8.3.2 Half-wave high temperature reverse bias             |             |

| A.8.3.3 Full-wave high temperature blocking bias            |             |

| A.8.4 Operating life                                        |             |

| A.8.4.1 Rectifying ac operating life                        | 27          |

| A.8.4.2 Steady-state dc operating life                      |             |

| A.8.4.3 Intermittent operating life                         |             |

| A.8.4.3.1 Rectifying ac intermittent operating life         |             |

| A.8.4.3.2 DC intermittent operating life.                   |             |

| A.8.5 Blocking life                                         | 28          |

| A.8.5.1 Steady-state dc blocking life                       | 28          |

| A.8.5.2 Half-wave blocking life                             |             |

| A.8.5.3 Full-wave blocking life                             |             |

| A.8.6 Temperature cycling (air to air).                     |             |

| A.8.7 Thermal shock (liquid to liquid).                     |             |

| A.8.8 Thermal impedance                                     |             |

| A.8.9 Surge                                                 |             |

| ABBREVIATIONS AND SYMBOLS                                   |             |

| B.1 SCOPE                                                   |             |

| B.1.1 Scope                                                 |             |

| B.2 APPLICABLE DOCUMENTS                                    | 29          |

| B.3 SEMICONDUCTOR ABBREVIATIONS AND SYMBOLS                 |             |

| B.3.1 Abbreviations.                                        |             |

| B.3.2 Symbols B.4 TRANSISTORS SYMBOLS                       |             |

| B.4.1 Junction transistors                                  |             |

| B.4.2 FET symbols                                           |             |

| B.4.3 Unijunction transistor symbols                        |             |

| B.5 DIODES AND RECTIFIERS SYMBOLS                           |             |

| B.5.1 Diodes and rectifier symbols                          | 40          |

| B.5.2 Microwave diode symbols                               |             |

| B.5.3 Tunnel diodes and backward diode symbols              |             |

| B.5.4 Voltage regulator and voltage-reference diode symbols | 43          |

| B.5.5 Current regulator diode symbols                       |             |

| B.5.6 Varactor diode symbols                                |             |

| B.5.7 Transient voltage suppressor symbols                  |             |

| B.6 THYRISTORS SYMBOLS                                      | 45          |

| B.6.1 Thyristor symbols                                     | 45          |

| B.7 OPTOELECTRONIC DEVICES SYMBOLS                          | •           |

| B.7.1 Optoelectronic device symbols                         |             |

| B.7.2 Photosensitive device symbols                         |             |

| B.7.3 Photoemitting device symbols                          |             |

| B.7.4 Optocoupler (photocoupler and opto-isolator) symbols  |             |

| QUALITY MANAGEMENT PROGRAM                                  |             |

| C.1 SCOPE                                                   |             |

| C.1.1 Scope                                                 |             |

| C.2 APPLICABLE DOCUMENTS                                    |             |

| C.2.1 General                                               |             |

| C.2.2 Non-Government publications                           |             |

| C.2.3 Order of precedence                                   | 51          |

| C.3. QUALITY MANAGEMENT (QM) PROGRAM                        |             |

| C.3.1 QM approach                                           |             |

| <u>PARAGRAPH</u>                                                         | <u>PAGE</u> |

|--------------------------------------------------------------------------|-------------|

| C.3.1.1 QM plan                                                          | 52          |

| C.3.1.1.1 Quality improvement plan                                       | 52          |

| C.3.1.2 Failure analysis                                                 | 52          |

| C.3.1.3 Statistical process control (SPC) plan                           | 52          |

| C.3.1.4 Certification and qualification plan.                            |             |

| C.3.1.5 Conversion/review of customer requirements                       |             |

| C.4 TECHNICAL REVIEW BOARD                                               | 52          |

| C.4.1 TRB responsibilities                                               | 52          |

| C.4.1.1 Organizational structure                                         | 52          |

| C.4.2 TRB duties                                                         | 53          |

| C.4.3 TRB input                                                          | 53          |

| C.4.4 TRB authority                                                      |             |

| C.4.5 TRB status reporting                                               |             |

| C.5 QUALITY PLANNING                                                     |             |

| C.5.1 Product quality planning                                           |             |

| C.5.1.1 Technology process flowchart                                     |             |

| C.5.2 FMEA                                                               |             |

| C.5.3 Control plans                                                      | 55          |

| C.6. QM CERTIFICATION                                                    |             |

| C.6.1 QM program certification process                                   | 55          |

| C.7 CHANGE PROCEDURES                                                    |             |

| C.7.1 Design, construction and process change control procedures         |             |

| C.7.1.1 Change notification                                              | 56          |

| C.7.2 Design and process methodology change                              | 56          |

| C.8. QUALIFICATION, VALIDATION, OPTIMIZATION, AND CONTINUOUS IMPROVEMENT |             |

| C.8.1 QML processing                                                     |             |

| C.8.1.1 Design qualification                                             |             |

| C.8.1.1.1 General elements of a design qualification program             |             |

| C.8.1.2 Detailed elements of a design qualification program              | 57          |

| C.8.2 Process optimization                                               |             |

| C.8.2.1 Test optimization                                                |             |

| C.8.2.2 Methods of test optimization                                     |             |

| C.8.3 Process validation: On-going reliability or conformance inspection |             |

| C.8.3.1 On-going reliability guidance criteria                           | 58          |

| C.8.3.1.1 General elements of an on-going reliability program            |             |

| C.8.4 Continuous improvement                                             |             |

| C.8.4.1 Quality and productivity improvement                             |             |

| C.8.4.2 Measures and methodologies                                       |             |

| C.8.5 Qualification                                                      |             |

| C.9 Maintaining QM program certification.                                |             |

| C.10 Removal of TRB authority                                            |             |

| QUALITY SYSTEM                                                           |             |

| D.1 SCOPE                                                                |             |

| D.1.1 Scope                                                              |             |

| D.2 APPLICABLE DOCUMENTS                                                 |             |

| D.2.1 General                                                            |             |

| D.2.2 Non-Government publications                                        |             |

| D.2.3 Order of precedence                                                |             |

| D.3 REQUIREMENTS                                                         |             |

| D.3.1 Responsibility and authority                                       |             |

| D.3.1.1 Basic and contracted plant requirements.                         |             |

| D.3.1.1.1 Definition of a manufacturer                                   |             |

| D.3.1.1.1 Basic plant                                                    |             |

| D.3.1.1.1.2 Contracted plant                                             |             |

| D.3.1.1.1.2.1 Contracted assembly plant                                  | 62          |

| <u>PARAGRAPH</u>                                               | <u>PAGE</u> |

|----------------------------------------------------------------|-------------|

| D.3.1.1.2.2 Contracted wafer fabrication plant                 |             |

| D.3.1.1.3 Wafer fabrication                                    |             |

| D.3.1.2 Responsibility of the manufacturer                     | 63          |

| D.3.1.3 Management responsibility                              |             |

| D.3.1.3.1 Personnel                                            | 63          |

| D.3.1.3.2 Resources                                            |             |

| D.3.1.4 Organization                                           | 63          |

| D.3.1.4.1 Management representative                            |             |

| D.3.1.5 Management review                                      | 64          |

| D.3.1.5.5 Qualified Products Technical Review Board (QPTRB)    | 64          |

| D.3.1.5.5.1 Organizational structure                           | 64          |

| D.3.1.5.5.2 QPTRB duties                                       |             |

| D.3.1.5.5.2.1 QPTRB input                                      | 64          |

| D.3.1.5.5.2.2 QPTRB output                                     |             |

| D.3.2 Quality system program                                   |             |

| D.3.2.1 Quality system requirements                            |             |

| D.3.2.2 Process flows                                          |             |

| D.3.2.3 Quality system procedures                              |             |

| D.3.2.4 Quality planning                                       |             |

| D.3.2.4.1 FMEA                                                 |             |

| D.3.2.4.2 Control plans                                        |             |

| D.3.2.4.3 Contracted assembly plant                            |             |

| D.3.2.4.4 Business interruption control plans                  |             |

| D.3.2.4.5 Incoming, in-process, and outgoing inventory control | 66          |

| D.3.3 Conversion of specification requirements                 |             |

| D.3.4 Control interface control                                |             |

| D.3.4.1 Design, materials, and processing documentation        |             |

| D.3.4.2 Design changes                                         |             |

| D.3.5 Document control                                         |             |

| D.3.5.1 Document control procedures                            |             |

| D.3.5.2 Document approval and issue                            |             |

| D.3.5.3 Document changes.                                      |             |

| D.3.6 Purchasing                                               |             |

| D.3.6.1 Acquisition documentation                              |             |

| D.3.8 Product identification and traceability                  |             |

| D.3.9 Process control                                          |             |

| D.3.9.1 Statistical process control (SPC)                      |             |

| D.3.9.2 Environmental controls                                 |             |

| D.3.9.3 Chemical controls                                      |             |

| D.3.9.4 Wafer lot process and inspection                       |             |

| D.3.9.4.1 Process                                              |             |

| D.3.9.4.2 Inspection.                                          |             |

| D.3.9.5 Process monitor programs                               |             |

| D.3.10 Inspection and testing.                                 |             |

| D.3.10.1 Inspection of purchased materials                     |             |

| D.3.10.1.1 Certified supplier program                          |             |

| D.3.10.2 In-process quality control                            |             |

| D.3.10.2.1 Manufacturer imposed tests                          |             |

| D.3.10.3 Testing and screening operations                      |             |

| D.3.10.4 Final inspection and testing                          |             |

| D.3.10.4.1 Qualification and conformance inspection            |             |

| D.3.10.5 Inspection and test verification                      |             |

| D.3.11 Control of inspection measuring and test equipment      |             |

| D.3.11.1 Test programs and setups                              |             |

| <u>PARAGRAPH</u>                                                     | <u>PAGE</u> |

|----------------------------------------------------------------------|-------------|

| D.3.11.2 Test equipment maintenance and calibration system           | 74          |

| D.3.11.3 Conditions and methods of test                              |             |

| D.3.11.4 Electrical test equipment verification                      | 74          |

| D.3.12 Inspection and test status                                    |             |

| D.3.12.1 Inspection and test status                                  |             |

| D.3.13 Control of nonconforming product                              |             |

| D.3.13.1 Reworked product                                            |             |

| D.3.13.2 Rework provisions                                           |             |

| D.3.13.2.1 Wafer rework                                              |             |

| D.3.13.2.2 Assembly rework                                           |             |

| D.3.13.2.3 Rework of assembled devices                               |             |

| D.3.13.2.3.1 Irradiation of assembled devices                        | 75          |

| D.3.13.3 Rejected lots                                               | 75          |

| D.3.14 Corrective and preventive action                              | 75          |

| D.3.14.1 Corrective action                                           | 75          |

| D.3.14.2 Preventive action                                           |             |

| D.3.15 Handling, storage, packaging, and delivery                    | 76          |

| D.3.15.1 Security of completed devices                               | 76          |

| D.3.15.2 Electrostatic discharge sensitive (ESDS) program            | 76          |

| D.3.16 Quality records                                               |             |

| D.3.17 Internal quality audits                                       |             |

| D.3.17.1 Internal audit program                                      |             |

| D.3.17.1.1 Internal audit checklist                                  |             |

| D.3.17.2 Audit schedules and frequencies                             |             |

| D.3.17.3 Auditors                                                    |             |

| D.3.17.4 Audit deficiencies                                          |             |

| D.3.18 Training                                                      |             |

| D.3.18.1 Personnel performing quality operations                     |             |

| D.3.18.2 Training requirements                                       |             |

| D.3.19 Servicing                                                     |             |

| D.3.20 Statistical techniques                                        |             |

| D.3.20.1 SPC program.                                                | 77          |

| STANDARD VERIFICATION SYSTEM FOR QUALIFED PRODUCTS                   |             |

| E.1 SCOPE                                                            |             |

| E.1.1 Scope                                                          |             |

| E.2 APPLICABLE DOCUMENTS                                             | /9          |

| E.2.1 General E.2.2 Non-Government publications                      | 79          |

|                                                                      |             |

| E.2.3 Order of precedenceE.3 GENERAL TEST AND INSPECTION INFORMATION |             |

| E.3.1. Wafer lots                                                    |             |

| E.3.1.1 Formation of inspection lots                                 | 80          |

| E.3.1.1.1 JAN, JANTX, and JANTXV inspection lot                      |             |

| E.3.1.1.1 Inspection sublot                                          | 90          |

| E.3.1.2 JANS lots                                                    |             |

| E.3.1.2.1 Scanning electron microscope (SEM) inspection              |             |

| E.3.1.2.2 JANS inspection lots                                       |             |

| E.3.2 Structurally identical device types                            |             |

| E.3.3 Disposal of samples.                                           |             |

| E.3.4 Destructive tests                                              |             |

| E.3.5 Nondestructive tests                                           |             |

| E.3.6 Resubmitted lots                                               |             |

| E.3.6.1 Resubmitted lots of JAN, JANTX, JANTXV, and JANS             |             |

| E.3.6.2 Resubmitted lots of RHA devices                              |             |

| E.3.7 Conditions and methods of test                                 |             |

|                                                                      |             |

| E.3.7.1 Alternative test methods. E.3.7.2 Procedure in case of test equipment failure or human error. E.3.7.2.1 Particle impact noise detector (PIND) test equipment failure or error. E.3.7.2.1 Particle impact noise detector (PIND) test equipment failure or error. E.3.8 JANS electrical test data. E.3.8 JANS electrical test data. E.3.9 JAN, JANTX, JANTXV electrical test data. E.3.9 JAN, JANTX, JANTXV electrical test data. E.3.9 JAN, JANTX, JANTXV electrical test data. E.4.1 Qualification inspection. E.4.2 Inspection routine. E.4.2 Inspection routine. E.4.2.1 Cualification to electrostatic discharge sensitivity (ESDS) classes. E.4.2.1 Cualification by extension. E.4.2.1 Cualification by extension. E.4.3 End-points. E.4.4 Selection of samples. E.4.5 End-points. E.4.5 Cualification inspection lot release. E.5 SCREENING. E.5.1 Screening. E.5.2 Screening. E.5.3 JANTX and JANTXV PDA. E.5.2 JANTY and JANTXV PDA. E.5.3.1 JANTX and JANTXV PDA. E.5.3.2 JANTX and JANTXV PDA. E.5.3.3 JANTX and JANTXV PDA. E.5.3.3 JANTX and JANTXV PDA. E.5.3.4 Lead forming for JANTX and JANTXV. E.5.4.3 Lead forming for JANTX and JANTXV. E.5.4.4 Lead forming for JANTX and JANTXV. E.5.5.5 Laser Marking for JAN, JANTX, and JANTXV Types. E.5.5 Lead Marking for JAN, JANTX, and JANTXV. E.5.4.5 JANS product. E.5.5.5 Laser Marking for JAN, JANTX, and JANTXV. E.5.4.5 Lead forming for JANTX and JANTXV. E.5.5.6 Lead forming for JANTX and JANTXV. E.5.6.1 PiND test for JANS devices. E.5.6.1 Inspection. E.5.6.1 Connormance. E.5.6.2 Connormance. E.5.6.3 Group B inspection.  E.6.6 Group E inspection.  E.6.6 Group E inspection.  E.6.7 Group Ainspection.  E.6.8 Connormance. E.6.8 Group E inspection.  E.6.9 Connormance. E.6.1 Connormance. E.6.1 Connormance. E.6.2 Connormance. E.6.3 Connormance. E.6.4 Connormance. E.6.5 Connormance. E.6.6 Group E inspection. E.6.6 Group E inspection. E.6.7 Group B inspection. E.6.8 Connormance. E.6.8 Connormance. E.6.8 Connormance. E.6.9 Connormance. E.6.1 Connormance. E.6.1 Connormance. E.6.2 Connormance. E.6.3 Connormance. E.6 | <u>PARAGRAPH</u>                                                                          | <u>PAGE</u> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------|

| E 3.7.2 Procedure in case of test equipment failure or human error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                           |             |

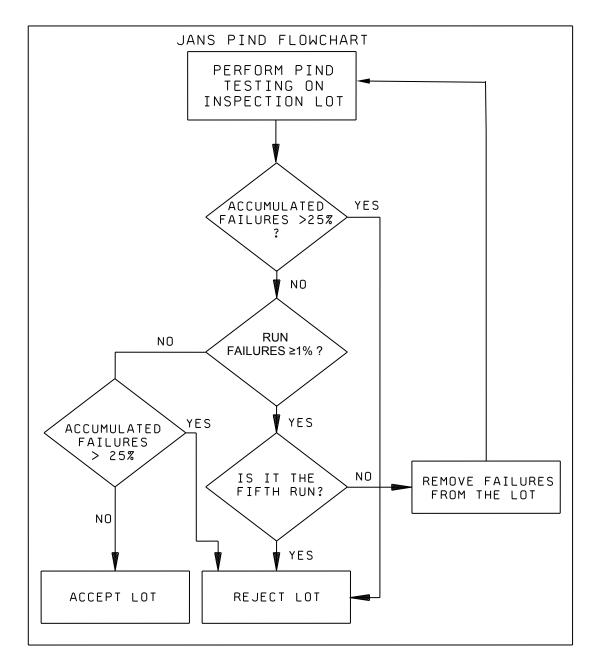

| E.3.7.2.1 Particle impact noise detector (PIND) test equipment failure or error.  86. E.3.8.1 Sunmary of parts fallout. E.3.9 Preservation of lot identity. E.4.2 Preservation of lot identity. E.4.2 VERIFICATION.  86. E.4.4 Cipulification inspection. 86. E.4.2 Inspection routine. 87. E.4.2.1 Qualification to electrostatic discharge sensitivity (ESDS) classes. 87. E.4.2.1 ESDS. 88. E.4.2 Qualification by extension. 89. E.4.2 Edection of samples. 89. E.4.3 End-points. 89. E.4.5 Identification of samples. 89. E.5.2 Percent defective allowable (PDA. 80. E.5.2.1 JANTX and JANTXV PDA. 80. E.5.2.1 JANTX and JANTXV PDA. 80. E.5.3.2 Bin and cell pre and post burn-in electrical measurements. 80. E.5.3.3 Identification procedures for screening of JANTX and JANTXV types. 81. E.5.3.2 Bin and cell pre and post burn-in electrical measurements. 81. E.5.3.3 Identification and conformance inspection where JAN is not covered by the specification sheet. 82. E.5.4.1 Lead forming for JANTX and JANTXV 81. E.5.3.4 Lead forming for JANTX and JANTXV 82. E.5.4.2 Lead forming for JANTX and JANTXV 83. E.5.3.4 Sum-in socket verification for JANS. 82. E.5.4.5 Burn-in socket verification for JANS. 82. E.5.4.1 PIND test for JANS devices 83. E.5.4.2 Identification and conformance inspection where JAN is not covered by the specification sheet. 84. E.5.3.4 Lead forming for JANTX and JANTXV 85. E.5.4.1 PIND test for JANS devices 85. E.5.4.2 Identification and conformance inspection where JAN is not covered by the specification for JANS. 82. E.5.4.4 Laser Marking for JANS. 82. E.5.5.4 E |                                                                                           |             |

| E.3.7.3 Standard mixer diodes and holders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | E.3.7.2 Procedure in case of test equipment failure or human error                        | 85          |

| E 3.8 JANS electrical test data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | E.3.7.2.1 Particle impact noise detector (PIND) test equipment failure or error           | 86          |

| E 3.8 J. Summary of parts fallout E 3.9 Preservation of lot identity  86 E.3.9 Preservation of lot identity  86 E.4 VERRIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                           |             |

| E 3.9 JAN, JANTX, JANTXV electrical test data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           |             |

| E 3.9 Preservation of lot identity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                           |             |

| E.4. VERIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                           |             |

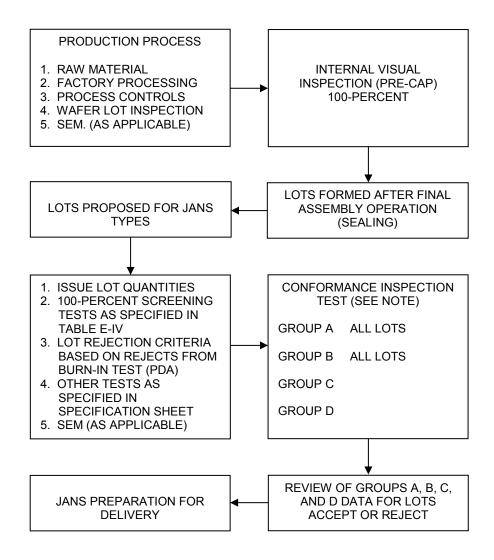

| E.4.1 Qualification inspection       .86         E.4.2 Inspection routine       .87         E.4.2.1 LeSDS       .88         E.4.2.2 Qualification by extension       .88         E.4.2.3 End-points       .89         E.4.4 Selection of samples       .89         E.4.5 Identification of samples       .89         E.4.6 Qualification inspection lot release       .90         E.5 SCREENING       .90         E.5.1 Screening       .90         E.5.2 Percent defective allowable (PDA       .90         E.5.2.1 JANTX and JANTXV PDA       .90         E.5.2.2 JANS PDA       .90         E.5.3.3 Alternate procedure for screening of JANTX and JANTXV types       .91         E.5.3.3 Alternate procedure for screening of JANTX and JANTXV types       .91         E.5.3.3 Alternate procedures for qualification and conformance inspection where JAN is not covered by the specification sheet       .91         E.5.3.5 Laser Marking for JANTX and JANTXV       .91         E.5.3.5 Laser Marking for JANTX and JANTXV       .91         E.5.4.1 PIND test for JANS devices       .91         E.5.4.2 Lead forming for JANS       .92         E.5.4.3 Burn-in socket verification for JANS       .92         E.5.4.3 Burn-in socket verification for JANS       .92         E.5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           |             |

| E.4.2 Inspection routine E.4.2.1 Qualification to electrostatic discharge sensitivity (ESDS) classes E.4.2.1 LESDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                           |             |

| E 4.2.1 Qualification to electrostatic discharge sensitivity (ESDS) classes E.4.2.2 Qualification by extension 88 E.4.3 End-points 89 E.4.4 Selection of samples 89 E.4.5 Identification of samples 89 E.4.5 Identification inspection lot release 90 E.5 SCREENING 90 E.5.1 Screening 90 E.5.2 Percent defective allowable (PDA 90 E.5.2.1 JANTX and JANTXV PDA 90 E.5.2.2 JANS PDA 90 E.5.3 JANTX and JANTXV Product 90 E.5.3.1 Alternate procedure for screening of JANTX and JANTXV types 91 E.5.3.2 Bin and cell pre and post burn-in electrical measurements 91 E.5.3.3 Alternate procedures for qualification and conformance inspection where JAN is not covered by the specification sheet 91 E.5.3.5 Laser Marking for JANTX and JANTXV 91 E.5.3.5 Laser Marking for JANTX and JANTXV 91 E.5.4.1 PIND test for JANS devices 91 E.5.4.2 Burn-in socket verification for JANS 92 E.5.4.1 Burn-in socket verification for JANS 92 E.5.4.1 Alser Marking for JANS 92 E.5.4.1 In Nonconformance 97 E.6.1 Conformance inspection 97 E.6.1.1 Nonconformance 97 E.6.2 Group A inspection 97 E.6.3 Group B inspection 97 E.6.3 Group B inspection 97 E.6.4 Croup C sample selection 98 E.6.4 Croup C inspection 98 E.6.4 Croup C inspection 99 E.6.5 Alternate group E testing procedures 99 E.6.6 A Group E inspection 99 E.6.6 CA Alternate group E testing procedures 99 E.6.6 CA Alternate group E testing procedures 99 E.6.6 CA Coroup B, C, D, and E end-points 99 E.6.7 Groups B, C, D, and E end-points 99 B.6.8 CA Coroup B, C, D, and E end-points 99 B.6.9 CA CEPTANCE 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           |             |