NOTE: HIL-STD-2165A has been redesignated as a handbook, and is to be used for guidance purposes only. This document is no longer to be cited as a requirement. For administrative expediency, the only physical change from MIL-STD-2165A is this cover page. However, this document is no longer to be cited as a requirement. If cited as a requirement, contractors may disregard the requirements of this document and interpret its contents only as quidance document and interpret its contents only as guidance.

| NOT MEASUREMENT |

|-----------------|

| SENSITIVE       |

MIL-HDBK-2165 31 Julv 1995 SUPERSEDING MIL-STD-2165A 01 February 1993

# DEPARTMENT OF DEFENSE

# TESTABILITY HANDBOOK FOR SYSTEMS AND EQUIPMENT

AMSC No. N6742

AREA ATTS DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

### FOREWORD

1. This military standard is approved for use by all Departments and Agencies of the Department of Defense.

2. Beneficial comments (recommendations, additions, deletions) and any pertinent data which may be of use in improving this document should be addressed to: Commander, Naval Sea Systems Command, ATTN: SEA 05Q42, 2531 National Center Bldg. 3, Washington, DC 20362-5160 by using the self-addressed Standardization Document Improvement Proposal (DD Form 1426) appearing at the end of this document or by letter.

3. Testability addresses the extent to which a system or unit supports fault detection and fault isolation in a confident, timely and cost-effective manner. The incorporation of adequate testability, including built-in test (BIT), requires early and systematic management attention to testability requirements, design and measurement.

4. This standard prescribes a systematic approach to establishing and conducting a testability program. Included are:

- (a) Testability program planning

- (b) Testability reviews

- (c) Diagnostic concepts and testability requirements

- (d) Inherent testability design and assessment

- (e) Test design and assessment.

5. This standard also prescribes the integration of these testability program requirements with design and engineering functions, and with other closely related, interdisciplinary program requirements, such as reliability, maintainability and logistic support.

6. Five appendices are included to augment the tasks of this standard:

- (a) Appendix A provides guidance in the selection and application of testability program tasks and depicts the interface with other engineering and logistics disciplines.

- (b) Appendix B describes the inherent testability assessment which provides a measure of testability early in the design phase.

- (c) Appendix C provides a glossary of terms used in this standard.

- (d) Appendix D provides requirements for UUT compatibility with offline ATE (applicable to Navy procurements only).

- (e) Appendix E defines the System Synthesis Model (SSM) input date sheets as they relate to the Consolidated Automated Support System (CASS).

.

# MIL-STD-2165A

# CONTENTS

| Paragraph                                                                                                                                                                                                                                                        | <u>PAGE</u>                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| <pre>1. SCOPE<br/>1.1 Purpose<br/>1.2 Application<br/>1.3 Tailoring of tasks</pre>                                                                                                                                                                               | 1<br>1<br>1<br>1           |

| <ol> <li>APPLICABLE DOCUMENTS</li></ol>                                                                                                                                                                                                                          | 1<br>1<br>1<br>2           |

| 3. DEFINITIONS                                                                                                                                                                                                                                                   | 2<br>2<br>2                |

| <ol> <li>GENERAL REQUIREMENTS</li></ol>                                                                                                                                                                                                                          | 2<br>2<br>3<br>3           |

| <ol> <li>DETAILED REQUIREMENTS</li> <li>Task descriptions</li> <li>Task integration</li> </ol>                                                                                                                                                                   | 3<br>3<br>3                |

| <ul> <li>6. NOTES</li> <li>6.1 Intended use</li> <li>6.2 Issue of DODISS</li> <li>6.3 Data requirements</li> <li>6.4 Subject term (key word) listing</li> <li>6.5 Changes from previous issue</li> </ul>                                                         | 4<br>4<br>4<br>4<br>4<br>5 |

| TASK SECTION 100 PROGRAM MONITORING AND CONTROL<br>Task 101, Testability Program Planning<br>Task 102, Testability Reviews                                                                                                                                       | . 7<br>9                   |

| TASK SECTION 200 DESIGN AND ANALYSIS                                                                                                                                                                                                                             |                            |

| Task 201, Diagnostic Concepts and Testability<br>Requirements<br>Task 202, Inherent Testability Design and<br>Assessment                                                                                                                                         | 12<br>14                   |

| Task 203, Test Design and Assessment                                                                                                                                                                                                                             | 16                         |

| <ul> <li>A. Testability Program Guidance</li> <li>B. Inherent Testability Assessment</li> <li>C. Glossary</li> <li>D. Unit Under Test Compatibility with Automatic</li> <li>Test Equipment</li> <li>E. System Synthesis Model (SSM) Input Data Sheets</li> </ul> | 21<br>41<br>63<br>67<br>73 |

iii

## 1. SCOPE

1.1 <u>Purpose</u>. This standard prescribes a uniform approach to testability program planning, establishment of diagnostic concepts and testability (including BIT) requirements, testability and test design and assessment, and requirements for conducting testability program reviews.

1.2 <u>Application</u>. This standard is applicable to the development of all types of components, equipments, and systems for the Department of Defense. Appropriate tasks of this standard are to be applied during the Conceptual phase, Demonstration and Validation phases, Full-scale Development phase and Production phase of the system acquisition process.

1.3 <u>Tailoring of tasks</u>. Tasks described are intended to be tailored to the particular needs of the system or equipment acquisition program. Application guidance and rationale for selecting and tailoring tasks are included in appendix A and the associated Testability Analysis Handbook.

2. APPLICABLE DOCUMENTS

2.1 <u>Government documents</u>.

2.1.1 <u>Specifications, standards, and handbooks</u>. The following specifications, standards, and handbooks form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DODISS) and supplement thereto, cited in the solicitation (see 6.2).

#### SPECIFICATION

| MILITARY    |                                               |

|-------------|-----------------------------------------------|

| MIL-H-46855 | - Human Engineering Requirements for Military |

|             | Systems, Equipment and Facilities.            |

#### STANDARDS

| MILITARY .     |                                                                                                      |

|----------------|------------------------------------------------------------------------------------------------------|

| MIL-STD-470    | - Maintainability Program for Systems & Equipment.                                                   |

| MIL-STD-721    | - Definitions of Terms for Reliability and<br>Maintainability.                                       |

| MIL-STD-785    | - Reliability Program for Systems and Equipment<br>Development and Production.                       |

| MIL-STD-1309   | - Definitions of Terms for Test, Measurement and Diagnostic Equipment.                               |

| MIL-STD-1388-1 | - Logistic Support Analysis.                                                                         |

| MIL-STD-1521   | <ul> <li>Technical Reviews and Audits for Systems,<br/>Equipments, and Computer Software.</li> </ul> |

(Unless otherwise indicated, copies of federal and military specifications, standards, and handbooks are available from the Standardization Documents Order Desk, Bldg. 4D, 700 Robbins Avenue, Philadelphia, PA 19111-5094.)

## MIL-STD-2165A

2.2 Order of precedence. In the event of a conflict between the text of this document and the references cited herein, the text of this document takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. DEFINITIONS

3.1 <u>Definitions</u>. The definitions included in MIL-STD-1309 and MIL-STD-721 shall apply. In addition, the definitions of appendix C are applicable.

3.2 <u>Acronyms and abbreviations</u>. The following acronyms and abbreviations listed in this military standard are defined as follows:

| а.         | ATE   |    | automatic test equipment                       |

|------------|-------|----|------------------------------------------------|

|            | BIT   |    | built-in test                                  |

|            | BITE  |    | built-in test equipment                        |

|            | CAD   |    | computer-aided design                          |

| е.         | CDR   |    | critical design review                         |

|            | CDRL  |    | contract data requirements list                |

| g٠         | CI    |    | configuration item                             |

| h.         | CND   | -  | cannot duplicate                               |

| <b>i</b> . | CE    | ٠. | concept exploration                            |

| j.         | DID   | -  | data item description                          |

| k.         | d&v   | -  | demonstration and validation                   |

| 1.         | ED/M  | •  | engineering development and manufacturing      |

| т.         | EO    | -  | electro-optical                                |

| n.         | FMEA  | -  | failure modes and effects analysis             |

|            |       |    | failure modes and effects criticality analysis |

| p.         | FQR   | -  | formal qualification review                    |

| q.         | ID    | -  | interface device                               |

| r.         | I/0   | -  | input or output                                |

| s.         | ILSMT | -  | integrated logistic support management team    |

| t.         | LSA   | ~  | logistic support analysis                      |

|            |       |    | mechanical systems condition monitoring        |

|            |       |    | production and deployment                      |

|            |       | -  | preliminary design review                      |

|            | RF    |    | radio frequency                                |

| y.         | ROM   |    | read only memory                               |

|            | SDR   |    | system design review                           |

| aa.        | T&E   |    | test and evaluation                            |

|            | TPS   | -  | test program set                               |

|            | TRD   |    | test requirements document                     |

|            | UUT   |    | unit under test                                |

|            | •     |    |                                                |

## 4. GENERAL REQUIREMENTS

4.1 <u>Scope of testability program</u>. This standard is intended to define and facilitate interdisciplinary efforts required to develop testable systems and equipments. The testability program scope includes:

- (a) Support of an integrated. diagnostic concept, whereby all elements associated with effective and efficient diagnostics are planned for, and integrated into, a cohesive fielded capability which satisfies weapon system mission and performance requirements.

- (b) Support of and integration with, maintainability design, including requirements for performance monitoring and corrective maintenance action at all levels of maintenance.

- (c) Support of integrated logistic support requirements, including the support and test equipment element and other logistic elements.

- (d) Support of, and integration with, design engineering requirements, including the hierarchical development of testability designs from the piece part to the system levels.

4.2 <u>Testability program requirements</u>. A testability program shall be established which accomplishes the following general requirements:

- (a) Development of a testability program plan.

- (b) Establishment of sufficient, achievable, and affordable diagnostic

- concept and testability built-in and off-line test performance requirements.

- (c) Integration of testability into equipments and systems during the design process in coordination with the maintainability design process.

- (d) Evaluation of the extent to which the design meets testability requirements.

- (e) Inclusion of testability in the program review process.

4.3 <u>Application of requirements</u>. Detailed testability requirements described in this standard are to be selectively applied and are intended to be tailored, to particular systems and equipment acquisition programs. Appendix A provides rationale and guidance for the selection and tailoring of testability program tasks.

#### 5. DETAILED REQUIREMENTS

5.1 <u>Task descriptions</u>. Individual task requirements are provided for the establishment of a testability program for system and equipment acquisition. The tasks are categorized as follows:

TASK SECTION 100. PROGRAM MONITORING AND CONTROL

Task 101 Testability Program Planning Task 102 Testability Reviews

TASK SECTION 200. DESIGN AND ANALYSIS

| Task 201 | Diagnostic Concepts and Testability Requirements |

|----------|--------------------------------------------------|

| Task 202 | Inherent Testability Design and Analysis         |

|          | Assessment                                       |

| Task 203 | Test: Design and Assessment                      |

# MIL-STD-2165A

5.2 <u>Task integration</u>. The individual task requirements provide for integration with other specified engineering and management tasks to preclude duplication and overlap, while ensuring timely consideration and accomplishment of testability requirements.

6, NOTES

(This section contains information of a general or explanatory nature that may be helpful, but is not mandatory.)

6.1 <u>Intended use</u>. This standard is intended to prescribe a systematic approach to establishing and conducting a testability program for systems and equipments.

6.2 <u>Issue of DODISS</u>. When this standard is used in acquisition, the applicable issue of the DODISS must be cited in the solicitation (see 2.1.1).

6.3 <u>Data requirements</u>. The following Data Item Descriptions (DID's) must be listed, as applicable, on the Contract Data Requirements List (DD Form 1423) when this standard is applied on a contract, in order to obtain the data, except where DOD FAR Supplement 27.475-1 exempts the requirement for a DD Form 1423.

| Reference Paragraph                      | DID Number    | DID Title                                                 | Suggested Tailoring                     |

|------------------------------------------|---------------|-----------------------------------------------------------|-----------------------------------------|

| Task 101.1                               | DI-ATTS-81270 | Testability program<br>plan                               | • • -                                   |

| Task 102.1                               | DI-E-5423     | Design review data<br>package                             | Equivalent DID may be used              |

| Task 201.4.1                             | DI-ATTS-81271 | Testability require-<br>ments analysis<br>report          |                                         |

| Task 202.4.2<br>and 202.4.4              | DI-ATTS-81272 | Inherent testability<br>design and assess-<br>ment report | ,                                       |

| Task 203.4.3,<br>203.4.4, and<br>203.4.6 | DI-ATTS-81273 | Test design and<br>assessment report                      | · • • · · · · · · · · · · · · · · · · · |

| Appendix D<br>50.2.1                     | DI-ATTS-81291 | Compatibility<br>Problem Report                           |                                         |

| Appendix D<br>50.3                       | DI-ATTS-91292 | UUT Input/Output<br>Description                           |                                         |

The above DID's were those cleared as of the date of this standard. The current issue of DoD 5010.12-L, Acquisition Management Systems and Data Requirements Control List (AMSDL), must be researched to ensure that only current, cleared DID's are cited on the DD Form 1423.

6.4 Subject term (key word) listing.

Diagnostics Diagnostic requirements Diagnostic testing Embedded test External test Fault detection Fault isolation Test assessment Test design

6.5 <u>Changes from previous issue</u>. Marginal notations are not used in this revision to identify changes with respect to the previous issue due to the extensiveness of the changes.

ς.

Custodians:Preparing activity:Army - CRNavy - SHNavy - SH(Project ATTS-8904)Air Force - 17

# TASK SECTION 100

# PROGRAM MONITORING AND CONTROL

## TASX 101

#### TESTABILITY PROGRAM PLANNING

101.1 <u>PURPOSE</u>. To plan for a testability program which will identify and integrate all testability and test design management tasks required to accomplish program requirements, as specified in a testability program plan (see 6.3).

## 101.2 TASK DESCRIPTION.

101.2.1 Identify a single organizational element within the performing activity which has overall responsibility and authority for implementation of the testability program. Establish analyses and data interfaces among the organizational elements responsible for each of the elements of the diagnostic capability.

101.2.2 Establish a procedure by which testability requirements are based on mission needs and system performance requirements and are traceable throughout the design process and are integrated with other design requirements, and how these requirements are disseminated to design personnel and subcontractors. Establish controls for ensuring that each subcontractor's testability practices are consistent with overall system or equipment requirements.

101.2.3 Identify testability design guides and analysis models and procedures to be imposed upon the design process. Plan for the review, verification, and utilization of testability data submissions.

101.2.4 Describe the approach to be used for establishing vertical test traceability to ensure compatibility of testing among all levels of testing, including factory testing. The approach must address both the compatibility of testing tolerances among levels and the compatibility of testing environments.

101.2.4.1 Describe the approach to be used to identify high-risk diagnostic technology applications and to provide procedures to lower these risks.

101.2.4.2 Describe the approach to be used to ensure integration and compatibility between testability and other diagnostic elements (that is, technical information, personnel, and training) and among all levels of maintenance.

101.2.4.3 Define the means for demonstrating and validating that the diagnostic capability meets specified requirements, using maintainability demonstrations, test program verification, and other demonstration methods.

101.2.4.4 Define an approach and methodology to ensure that as test and evaluation of the system progresses, problems presented by new failure modes, test voids, ambiguities, and test tolerance difficulties are recognized and defined, and solutions are traceable to diagnostic hardware and software, and manual procedures updates.

101.2.4.5 Define an approach for the analysis of production and acceptance test and evaluation results to determine how BIT hardware and software, ATE hardware and software, and maintenance documentation performed as a means for satisfying production testing, as well as meeting testability requirements.

101.2.4.6 Establish procedures to analyze maintenance actions for fielded systems to determine if the diagnostic capability is performing within specified requirements and take corrective measures. Define data collection requirements to conduct these analyses. Data collection shall be integrated with similar data collection procedures, such as those for reliability and maintainability and logistic support analysis and shall be compatible with specified data systems in use by the military user organizations.

101.2.5 Develop a testability program plan which describes how the testability program will be conducted. The plan must also include the time phasing of each task and relationships to other tasks. Diagnostic issues which relate to reliability, maintainability, logistics, human engineering, safety, and training shall also be addressed in those individual plans.

101.3 TASK INPUT.

101.3.1 Identifications of each task which is required to be performed as part of the program.\*

101.3.2 Identification of the time period over which each task is to be conducted.\*

101.3.3 Identification of approval procedures for plan updates.\*

101.3.4 Identification of deliverable data items.\*

101.3.5 Identification of items to be demonstrated.\*

101.3.5.1 Identification of existing maintenance data collection systems in use by the using command.\*

101.4 TASK OUTPUT.

101.4.1 Testability program plan if specified as a stand-alone plan. When required to be a part of another engineering or management plan, such as the Systems Engineering Management Plan (SEMP), use the appropriate, specified DID.

\* To be specified by the requiring authority.

## **TASK 102**

#### TESTABILITY REVIEWS

102.1 <u>PURPOSE</u>. To establish a requirement for the performing activity to (1) provide for all official review of testability design information in a timely and controlled manner, and (2) conduct in-process testability design reviews at specified dates to ensure that the program is proceeding in accordance with the contract requirements and program plans (see 6.3).

#### 102.2 TASK DESCRIPTION.

102.2.1 Include the formal review and assessment of the testability program as an integral part of each system program review (such as system design review, preliminary design review, critical design review, etc.) specified by the contract. Reviews shall cover all pertinent aspects of the testability program such as:

- (a) Status and results of testability-related tasks.

- (b) Documentation of task results.

- (c) Testability-related requirements in specifications.

- (d) Testability design, cost, or schedule problems.

102.2.2 Conduct and document testability design reviews with performing activity personnel, subcontractors, and suppliers. Coordinate and conduct these reviews in conjunction with reliability, maintainability, and logistic support reviews whenever possible. Inform the requiring authority in advance of each review. Utilize MIL-STD-1521 and program review criteria contained in MIL-STD-470, MIL-STD-785, and MIL-STD-1388-1. Design reviews shall cover all pertinent aspects of the design, such as the following:

- (a) Review the impact of the selected diagnostic concept on readiness, life cycle costs, manpower, and training.

- (b) Review performance monitoring, built-in test, off-line test and

- maintenance aid performance requirements and constraints to ensure that they are complete and consistent.

- (c) Review the rationale for the inherent testability criteria and weighting factors selected.

- (d) Review the testability techniques employed by the design groups. Identify design guides or procedures used. Describe any testability analysis procedures or automated tools to be used.

- (e) Review the extent to which testability criteria are being met. Identify any technical limitations or cost considerations inhibiting full implementation.

- (f) Review adequacy of failure mode data as a basis for test design. Assess adequacy of testability/FMEA data interface.

- (g) Review integration among BIT hardware, BIT software, and operational software efforts. Review BIT interface to operator and maintenance personnel.

## MIL-STD-2165A

- (h) Review BIT fault detection and fault isolation measures to be used. Identify models used and model assumptions. Identify any methods to be used for automatic test generation and test grading.

- (i) Review BIT fault detection and fault isolation performance to determine if BIT specifications are met. Review efforts to improve BIT performance through improved tests or item redesign. Assess adequacy of testability/maintainability data interfaces.

- (j) Review testability parameters to be included in the maintainability demonstration. Identify procedures by which testability concerns are included in demonstration plans and procedures.

- (k) Review compatibility of signal characteristics at test points with planned test equipment. Assess adequacy of data interface between testability and support and test equipment organizational elements.

- Review completeness and consistency of performance monitoring, BIT and off-line test performance.

- (m) Review approach and methodology to ensure that as test and evaluation of the system progresses, problems presented by new failure modes, test voids. ambiguities, and test tolerance difficulties are recognized and defined and solutions are traceable to diagnostic software and manual procedures updates.

- (n) Review approaches to monitoring production testing and field maintenance actions to determine fault detection and fault isolation effectiveness.

- (o) Review plans for evaluating impact on the diagnostic capability for engineering change proposals.

102.3 TASK INPUT.

102.3.1 Identification of amount of time to be devoted to the testability program at each formal review and the level of technical detail to be provided.\*

102.3.2 Identification of level of participation desired by the requiring authority in internal and subcontractor design reviews.\*

102.4 TASK OUTPUT.

102.4.1 Results of testability assessments as an integral part of system program review documentation (see 102.2.1).

102.4.2 Results of testability design reviews, including action items pending (see 102.2.2).

\* To be specified by the requiring authority.

# TASK SECTION 200

# DESIGN AND ANALYSIS

## TASK 201

## DIAGNOSTIC CONCEPTS AND TESTABILITY REQUIREMENTS

201.1 <u>PURPOSE</u>. To evaluate alternative diagnostic concepts and (1) recommend system test and testability requirements which best implement selected diagnostic concepts and (2) allocate those requirements to subsystems and items.

201.2 TASK DESCRIPTION.

201.2.1 Derive and establish system-level diagnostic needs. This includes:

- (a) Identifying those system mission and performance requirements which directly require diagnostic functions (such as, safety, mission critical).

- (b) Translating those system mission and performance requirements into diagnostic needs which support the mission scenario and system 'design and conform to the system's operational constraints.

201.2.2 Derive alternative diagnostic concepts which satisfy mission requirements and provide a complete (100 percent) diagnostic capability at each level of maintenance. Include for each level of maintenance varying degrees of BIT, manual and automatic testing, technical information delivery, personnel skill levels, and training concepts, along with deferred, preventive, and scheduled maintenance concepts. Considerations include:

- (a) Identification of standard, existing, or planned, or existing and planned diagnostic resources (such as, family of testers, maintenance alds) that have potential benefits. Identify resource limitations.

- (b) Identification of diagnostic problems on similar systems which should be avoided.

- (c) Identification of technology advancements that can be exploited in system development and diagnostic element development which have the potential for increasing diagnostic effectiveness, reducing diagnostic costs, or enhancing system availability.

201.2.3 Evaluate alternative diagnostic capability concepts. Identify the selected diagnostic concept. The evaluation shall include:

- (a) A determination of the sensitivity of system readiness parameters to variations in the diagnostic mix and to variations in key testability/diagnostic parameters.

- (b) A determination of the sensitivity of life cycle costs to variations in the key testability/diagnostic parameters, mix. and placement of diagnostic resources.

- (c) An estimation of the impact of alternative diagnostic concepts on direct maintenance man-hours per operating hour, job classifications, skill levels, or other diagnostic measures, required at each level of maintenance.

(d) An estimation of risk associated with each concept.

201.2.4 Recommend system-level fault detection and isolation requirements for inclusion in system specifications, including those requirements addressed in paragraph 201.3.4.

201.2.5 Allocate system-level testability requirements to configuration item specifications based on reliability, criticality considerations, technology risks, and the potential efficiency and effectiveness of the diagnostic capability. Allocation shall address all diagnostic elements which constitute the diagnostic capability (that is, test, technical information, and personnel).

201.2.6 Recommend off-line test fault detection and isolation requirements for each item designated as a unit under test for inclusion in CI development specifications.

201.3 TASK INPUT.

201.3.1 Mission and performance requirements and operational constraints from weapon system statement of need and MIL-STD-1388-1. task 201. (Needed for 201.2.1)

201.3.2 Supportability analysis data in accordance with MIL-STD-1388-1 (201 through 204 and 301 and 302) or other method approved by the requiring authority. (Needed for 201.2.2)

201.3.3 Reliability allocation from task 202 of MIL-STD-785. (Needed for 201.2.5)

201.3.4 Specific numeric diagnostic and testability requirements not subject to requirements trade-offs.\* (Needed for 201.2.1, 201.2.4, and 201.2.5)

201.3.5 Human engineering analysis and requirements, such as from MIL-H-46855. (Needed for 201.2.2, 201.2.3, and 201.2.5)

201.4 TASK OUTPUT.

201.4.1 Description of selected diagnostic capability tradeoff methodology; evaluation criteria, models used, and analysis results (see 201.2.3 and 6.3).

201.4.2 Recommended diagnostic and testability monitoring requirements for system specification (see 201.2.4 and 201.2.5).

201.4.3 Recommended diagnostic and testability requirements for each configuration item specification (see 201.2.6).

\* To be specified by the requiring authority.

## **TASK 202**

#### INHERENT TESTABILITY DESIGN AND ASSESSMENT

202.1 <u>PURPOSE</u>. To incorporate testability design practices into the design of a system or equipment early in the design phase and to assess the extent to which testability is incorporated.

202.2 TASK DESCRIPTION.

202.2.1 Institute testability design concepts as an integral part of the system or equipment design process.

202.2.2 Incorporate appropriate testability design concepts into the preliminary design for each item. Provide inputs to system engineering on the impact of system architecture alternatives on inherent diagnostic capability. Recommend diagnostic architecture considerations, such as testability bus. system-level BIT, onboard diagnostic data collection, and sensor locations.

202.2.3 Select testability design criteria from appendix B to be implemented in the design. Tailor criteria and add new criteria for the specific design. Include criteria for UUT compatibility with off-line ATE.

202.2.4 Analyze and evaluate the selected testability concepts of the system or equipment design in a qualitative manner to ensure that the design will support the required level of testing. Conduct an analysis of the inherent (intrinsic) testability of the design. The analysis identifies the presence or absence of hardware features which facilitate testing and identifies problem areas. The method of appendix B shall be applied to each item identified for inherent testability assessment by the requiring authority. Methods, such as dependency modeling analysis of the design, can be utilized to optimize test point placement and partitioning strategies.

202.2.5 Modify the design, until the inherent testability equals or exceeds the threshold value. If achieving the threshold is not possible or cost effective, but fault detection and fault isolation requirements can be met, supporting data shall be prepared.

202.3 TASK INPUT.

202.3.1 System or equipment design data.

202.3.2 Identification of items to be included in inherent testability analysis (see appendix B).\*

202.3.3 For each item included, the inherent testability threshold value to be achieved.\* Guidance for establishing a threshold value is given in appendix B, 50.2.4.1.

#### MEL-STD-2165A

202.4 TASK\_OUTPUT.

202.4.1 Testability features integrated into system or equipment design (see 202.2.1, 202.2.2, and 202.2.4).

202.4.2 Description of testability design tradeoffs and testability features selected for implementation (see 202.2.2, 202.2.4, and 6.3).

202.4.3 For each item included, assignment of a weighting factor and scoring method for each testability criterion (see appendix B and 202.2.3).

202.4.4 Inherent testability assessment (see 202.2.3 and 6.3).

\* To be specified by the requiring authority.

#### TASK 203

#### TEST DESIGN AND ASSESSMENT

203.1 <u>PURPOSE</u>. To design the embedded and external test capability for a system or equipment which will satisfy testability performance requirements; to assess the level of test effectiveness which will be achieved for a system or equipment design; and to ensure effective integration and compatibility of this test capability with other diagnostic elements.

203.2 TASK DESCRIPTION.

203.2.1 Incorporate testability, including built-in test, into the detailed design for each item.

203.2.2 Identify and define the methodology to be used for predicting fault detection and fault isolation performance levels at the system test level and the item test level.

203.2.3 Analyze the prime system design to ensure that all system-level functions are exercised by testing (such as, BIT, performance monitoring) to the extent specified, and that the testing function has been effectively integrated with other system-level diagnostic resources (such as, maintenance aids, technical publications). Ensure that performance monitoring functions and display formats provide the operator with appropriate information. Particular attention should be given to the separation of hardware faults from software problems.

203.2.4 Develop system-level BIT hardware and software, integrating the built-in test capabilities of each subsystem/item.

203.2.5 Predict the level of BIT fault detection for the overall system based on the BIT detection predictions, weighted by failure rate, of the individual items, including Government-furnished equipment (GFE). Predict the level of fault isolation for the overall system provided by system-level test.

203.2.6 Conduct an analysis of the test effectiveness of shop tests for each CI and for each physical partition of the CI designated at a UUT. Item built-in test and external ATE tests shall be included in this analysis. Ensure that the testing function has been effectively integrated with other shop diagnostic resources (such as, technical publication, management information systems).

203.2.7 For both system-level and shop-level analyses:

(a) Identify the failures of each component and the failures between components which correspond to the specific failure modes for each item to be tested. These failures represent the predicted failure population and are the basis for test derivation (BIT and off-line test) and test effectiveness evaluation. Maximum use shall be

made of a failure modes and effects analysis (FMEA) from Task 204 of HIL-STD-470, if a FMEA is required. The FMEA requirements may have to be modified or supplemented to provide the level of detail needed.

- (b) Model components and interconnections for each item so that the predicted failure population may be accurately modeled. The performing activity shall develop or select models which are optimum, considering accuracy required, cost of test generation and simulation, standardization, and commonality. Analyze and evaluate UUT compatibility with off-line ATE. (Appendix D provides requirements for off-line ATE compatibility).

- (c) Analyze and evaluate the effectiveness of planned testing based on the predicted failure population. The analysis shall give particular emphasis to fault detection and fault isolation for critical and high failure rate items and interconnections. The test effectiveness data shall be used to guide redesign of equipment and test programs, as required, and to assist in the prediction of spares requirements.

- (d) Prepare justification for any classes of faults which are poorly isolated, when using the developed test stimuli, and submit to the requiring authority for review. Prepare additional or alternative diagnostic approaches. Identify hard-to-test-faults to the LSA process.

203.2.8 Iterate the design of the item built-in test until each predicted test effectiveness value equals or exceeds the specified value.

203.2.9 Iterate the design of the item external test until each predicted test effectiveness value equals or exceeds the specified value.

203.2.10 Assemble cost data associated with BIT and design for testability on a per unit basis (such as, additional hardware, increased modularity, and additional connector pins). Extract and summarize cost data associated with the implementation of the testability program, test generation efforts, and production test. Provide test effectiveness predictions as inputs to maintainability and logistic tasks.

203.2.11 Implement procedures for vertical test traceability to ensure compatibility of testing among all levels of testing, including factory testing. . These procedures shall address both the compatibility of testing tolerances among levels and the compatibility of testing environments.

203.3 TASK INPUT.

203.3.1 Identification of items to be included in test effectiveness predictions.\*

203.3.2 System or item design data.

203.3.3 BIT and external test requirements.

#### MIL-STD-2165A

203.3.4 Identification of failure modes and failure rates for each item from task 204 of MIL-STD-470.

203.3.5 Test effectiveness data for GFE.\*

203.3.6 Corrective action recommendations from the maintainability demonstration.

#### 203.4 TASK OUTPUT.

203.4.1 Built-in test features integrated into the system or item design which meet testability and maintainability requirements. (203.2.1, 203.2.4, 203.2.5)

203.4.2 Description of methodologies, models, and tools to be used in item and system test effectiveness predictions (see 203.2.1).

203.4.3 Description of built-in test and testability features for each item designed as a UUT, in appropriate test requirements document (see 203.2.1).

203.4.4 Test effectiveness prediction for each item: data provided in support of task 205 of MIL-STD-470 and task 401 of MIL-STD-1388-1 (see 203.2.5, 203.2.6, and 6.3).

203.4.5 System test effectiveness prediction from information provided in support of task 205 of MIL-STD-470 (see 203.2.4, 203.2.7 and 6.3).

203.4.6 Description of vertical test traceability and design integration (see 203.2.11 and 6.3).

\* To be specified by the requiring authority.

# MÍL-STD-2165A

# APPENDIX A

# TESTABILITY PROGRAM GUIDANCE

# CONTENTS

Page

# Paragraph

| 10                                                                                                                                   | SCOPE                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 10.1                                                                                                                                 | Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21                                                                         |

| 10.1                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| 20.                                                                                                                                  | APPLICABLE DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                                                                      | 21                                                                         |

| 20.1                                                                                                                                 | Government documents                                                                                                                                                                                                                                                                                                                                                                                                                      | 21                                                                         |

| 20.1.1                                                                                                                               | Specifications and standards                                                                                                                                                                                                                                                                                                                                                                                                              | 21                                                                         |

| 20.1.2                                                                                                                               | Other Government documents, drawings, and                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

|                                                                                                                                      | publications                                                                                                                                                                                                                                                                                                                                                                                                                              | 21                                                                         |

| 30.                                                                                                                                  | DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                               | 22                                                                         |

| 30.1                                                                                                                                 | Definitions                                                                                                                                                                                                                                                                                                                                                                                                                               | 22                                                                         |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| 40.                                                                                                                                  | GENERAL APPLICATION GUIDANCE                                                                                                                                                                                                                                                                                                                                                                                                              | 22                                                                         |

| 40.1                                                                                                                                 | Task selection criteria                                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                                         |

| 40.2                                                                                                                                 | System testability program                                                                                                                                                                                                                                                                                                                                                                                                                | 22                                                                         |

| 40.3                                                                                                                                 | Item testability program                                                                                                                                                                                                                                                                                                                                                                                                                  | 27                                                                         |

| 40.4                                                                                                                                 | Criteria for imposing a testability program                                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

|                                                                                                                                      | during the D&V phase                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                         |

| 40.5                                                                                                                                 | Equipment testability program                                                                                                                                                                                                                                                                                                                                                                                                             | 29                                                                         |

| 40.6                                                                                                                                 | Iterations                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                                                                         |

| 50.                                                                                                                                  | DETAILED APPLICATION GUIDANCE                                                                                                                                                                                                                                                                                                                                                                                                             | 29                                                                         |

| <i>J</i> <b>v</b> .                                                                                                                  | DETRILED RITLIORITOR OUTDIALOB                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

| 50.1                                                                                                                                 | Task 101, testability program planning                                                                                                                                                                                                                                                                                                                                                                                                    | 29                                                                         |

| • • •                                                                                                                                | Task 101, testability program planning                                                                                                                                                                                                                                                                                                                                                                                                    | 29<br>29                                                                   |

| 50.1                                                                                                                                 | Task 101, testability program planning<br>Scope<br>Submission of the plan                                                                                                                                                                                                                                                                                                                                                                 | 29<br>29<br>31                                                             |

| 50.1<br>50.1.1                                                                                                                       | Task 101, testability program planning         Scope         Submission of the plan         Plan phases                                                                                                                                                                                                                                                                                                                                   | 29<br>29<br>31<br>31                                                       |

| 50.1<br>50.1.1<br>50.1.2                                                                                                             | Task 101, testability program planningScopeSubmission of the planPlan phasesOrganizational interfaces                                                                                                                                                                                                                                                                                                                                     | 29<br>29<br>31<br>31<br>31                                                 |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3                                                                                                   | Task 101, testability program planning<br>Scope<br>Submission of the plan<br>Plan phases<br>Organizational interfaces<br>Testability effectiveness tracking                                                                                                                                                                                                                                                                               | 29<br>29<br>31<br>31<br>31<br>31                                           |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4                                                                                         | Task 101, testability program planning<br>Scope<br>Submission of the plan<br>Plan phases<br>Organizational interfaces<br>Testability effectiveness tracking<br>Task 102, testability review                                                                                                                                                                                                                                               | 29<br>29<br>31<br>31<br>31<br>31<br>31<br>32                               |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4<br>50.1.5<br>50.2<br>50.2.1                                                             | Task 101, testability program planningScopeSubmission of the planPlan phasesOrganizational interfacesTestability effectiveness trackingTask 102, testability reviewType of review                                                                                                                                                                                                                                                         | 29<br>29<br>31<br>31<br>31<br>31<br>32<br>32                               |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4<br>50.1.5<br>50.2<br>50.2.1<br>50.2.1.1                                                 | Task 101, testability program planningScopeSubmission of the planPlan phasesOrganizational interfacesTestability effectiveness trackingTask 102, testability reviewType of reviewProgram reviews                                                                                                                                                                                                                                          | 29<br>29<br>31<br>31<br>31<br>31<br>32<br>32<br>32                         |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4<br>50.1.5<br>50.2<br>50.2.1<br>50.2.1.1<br>50.2.1.1                                     | Task 101, testability program planningScopeSubmission of the planPlan phasesOrganizational interfacesTestability effectiveness trackingTask 102, testability reviewType of reviewProgram reviewsTestability design reviews                                                                                                                                                                                                                | 29<br>29<br>31<br>31<br>31<br>31<br>32<br>32<br>32<br>32                   |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4<br>50.1.5<br>50.2<br>50.2.1<br>50.2.1.1                                                 | Task 101, testability program planningScopeSubmission of the planPlan phasesOrganizational interfacesTestability effectiveness trackingTask 102, testability reviewType of reviewProgram reviewsTestability design reviewsAdditional data review                                                                                                                                                                                          | 29<br>29<br>31<br>31<br>31<br>31<br>32<br>32<br>32                         |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4<br>50.1.5<br>50.2<br>50.2.1<br>50.2.1.1<br>50.2.1.1                                     | Task 101, testability program planningScopeSubmission of the planPlan phasesOrganizational interfacesTestability effectiveness trackingTask 102, testability reviewType of reviewProgram reviewsTestability design reviewsAdditional data review                                                                                                                                                                                          | 29<br>29<br>31<br>31<br>31<br>32<br>32<br>32<br>32<br>32                   |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4<br>50.1.5<br>50.2<br>50.2.1<br>50.2.1.1<br>50.2.1.2<br>50.2.2                           | Task 101, testability program planning<br>Scope<br>Submission of the plan<br>Plan phases<br>Organizational interfaces<br>Testability effectiveness tracking<br>Task 102, testability review<br>Type of review<br>Program reviews<br>Testability design reviews<br>Additional data review<br>Task 201, diagnostic concept and<br>testability requirements                                                                                  | 29<br>29<br>31<br>31<br>31<br>31<br>32<br>32<br>32<br>32                   |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4<br>50.1.5<br>50.2<br>50.2.1<br>50.2.1.1<br>50.2.1.2<br>50.2.2                           | Task 101, testability program planningScopeSubmission of the planPlan phasesOrganizational interfacesTestability effectiveness trackingTask 102, testability reviewType of reviewProgram reviewsTestability design reviewsAdditional data reviewTask 201, diagnostic concept andtestability requirementsTask 202, inherent testability design                                                                                             | 29<br>29<br>31<br>31<br>31<br>32<br>32<br>32<br>32<br>32<br>32<br>33       |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4<br>50.1.5<br>50.2<br>50.2.1<br>50.2.1.1<br>50.2.1.2<br>50.2.2<br>50.3<br>50.4           | Task 101, testability program planning<br>Scope<br>Submission of the plan<br>Plan phases<br>Organizational interfaces<br>Testability effectiveness tracking<br>Task 102, testability review<br>Type of review<br>Program reviews<br>Testability design reviews<br>Additional data review<br>Task 201, diagnostic concept and<br>testability requirements<br>Task 202, inherent testability design<br>and assessment                       | 29<br>29<br>31<br>31<br>31<br>32<br>32<br>32<br>32<br>32<br>32<br>33<br>33 |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4<br>50.1.5<br>50.2<br>50.2.1<br>50.2.1.1<br>50.2.1.2<br>50.2.2<br>50.2.2<br>50.3<br>50.4 | Task 101, testability program planning<br>Scope<br>Submission of the plan<br>Plan phases<br>Organizational interfaces<br>Testability effectiveness tracking<br>Task 102, testability review<br>Program reviews<br>Testability design reviews<br>Additional data review<br>Task 201, diagnostic concept and<br>testability requirements<br>Task 202, inherent testability design<br>and assessment<br>Task 203, test design and assessment | 29<br>29<br>31<br>31<br>31<br>32<br>32<br>32<br>32<br>32<br>32<br>33       |

| 50.1<br>50.1.1<br>50.1.2<br>50.1.3<br>50.1.4<br>50.1.5<br>50.2<br>50.2.1<br>50.2.1.1<br>50.2.1.2<br>50.2.2<br>50.3<br>50.4           | Task 101, testability program planning<br>Scope<br>Submission of the plan<br>Plan phases<br>Organizational interfaces<br>Testability effectiveness tracking<br>Task 102, testability review<br>Type of review<br>Program reviews<br>Testability design reviews<br>Additional data review<br>Task 201, diagnostic concept and<br>testability requirements<br>Task 202, inherent testability design<br>and assessment                       | 29<br>29<br>31<br>31<br>31<br>32<br>32<br>32<br>32<br>32<br>32<br>33<br>33 |

# MIL-STD-2165A

# APPENDIX A

CONTENTS - (Continued)

÷.,

<u>Page</u>

# FIGURES

-- --

| Figure | <ol> <li>System testability program flow diagram</li></ol>                      | 24<br>28<br>30<br>35<br>36 |

|--------|---------------------------------------------------------------------------------|----------------------------|

|        | TABLES                                                                          |                            |

| Table  | I Task application guidance matrix                                              | 27                         |

|        | II. LSA interface (task 201 diagnostic concept<br>and testability requirements) | 37<br>38                   |

|        | III. Maintainability and safety interface                                       | 38<br>39                   |

## APPENDIX A

#### TESTABILITY PROGRAM GUIDANCE

10. SCOPE

10.1 <u>Furpose</u>. This appendix provides rationale and guidance for the selection and tailoring of tasks to define a testability program which meets established program objectives. No contractual requirements are contained in this appendix. This appendix is not a mandatory part of the standard. The information contained herein is intended for guidance only.

20. APPLICABLE DOCUMENTS

20.1 <u>Government documents</u>.

20.1.1 <u>Specifications and standards</u>. The following specifications, standards, and handbooks form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DODISS) and supplement thereto, cited in the solicitation.

SPECIFICATION

MILITARY MIL-H-46855

- Human Engineering Requirements for Military Systems, Equipment and Facilities

STANDARD

MILITARY MIL-STD-882

- System Safety Program Requirements

(Unless otherwise indicated, copies of federal and military specifications, standards, and handbooks are available from the Standardization Documents Order Desk, Bldg. 4D, 700 Robbins Avenue, Philadelphia, PA 19111-5094.)

20.1.2 <u>Other Government documents, drawings, and publications</u>. The following other Government documents, drawings, and publications form a part of this document to the extent specified herein. Unless otherwise specified, the issues are those cited in the solicitation.

NAVMATP 9405 Joint Service Built-In Test Design Guide. DARCOM 34-1 AFLCP 800-39 AFSCP 800-39 NAVMC 2721, 19 March 1981

MIL-STD-2165A APPENDIX A

TECHNICAL REPORTS

Rome Air Development Center September 1990 RADC-TR-90-239

Rome Air Development Center December 1979 RADC-TR-79-309 Testability/Diagnostic Design Encyclopedia

BIT/External Testing Figures of Merit and Demonstration Techniques

30. DEFINITIONS

30.1 <u>Definitions</u>. The definitions included in MIL-STD-1309, MIL-STD-721, and appendix C shall apply.

40. GENERAL APPLICATION GUIDANCE

40.1 <u>Task selection criteria</u>. The selection of tasks which can materially aid the attainment of testability requirements is a difficult problem for both Government and industry organizations faced with severe funding and schedule constraints. This appendix provides guidance for the selection of tasks based upon identified program needs. Once appropriate testability program tasks have been selected, each task shall be tailored in terms of timing, comprehensiveness and end products to meet the overall program requirements.

MIL-STD-2165 is a programmatic standard which defines the task requirements for conducting a testability program within a system or equipment development program. MIL-STD-2165 is comprised of a series of tasks which may be selectively applied, for the specific system being developed and the phase of development. The tasks include program administration and control tasks and design and analysis tasks. Each task has a number of subtasks. These subtasks are the key to the tailoring of the testability program. Subtasks may be called out in statements of work. This defines the work to be accomplished within the testability program.

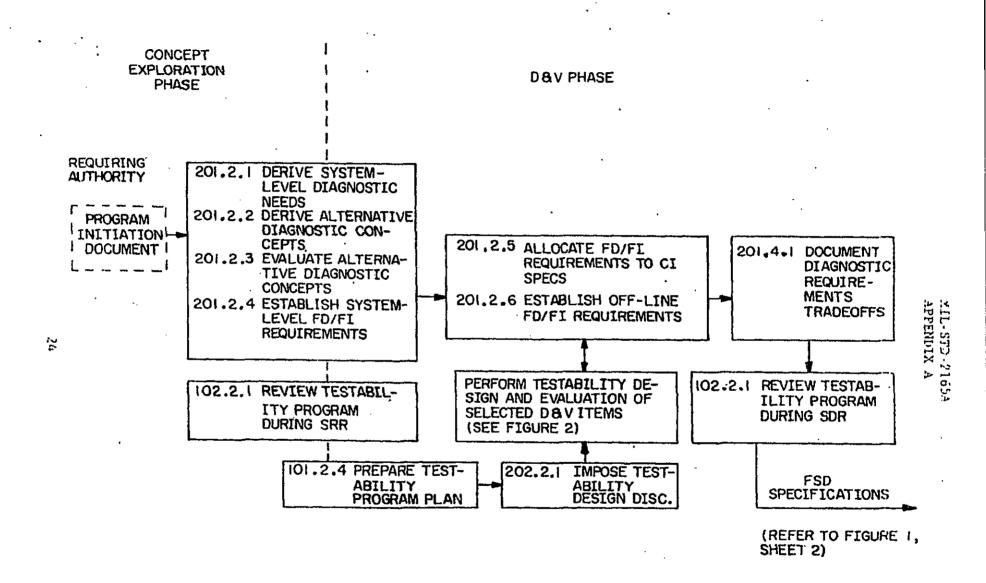

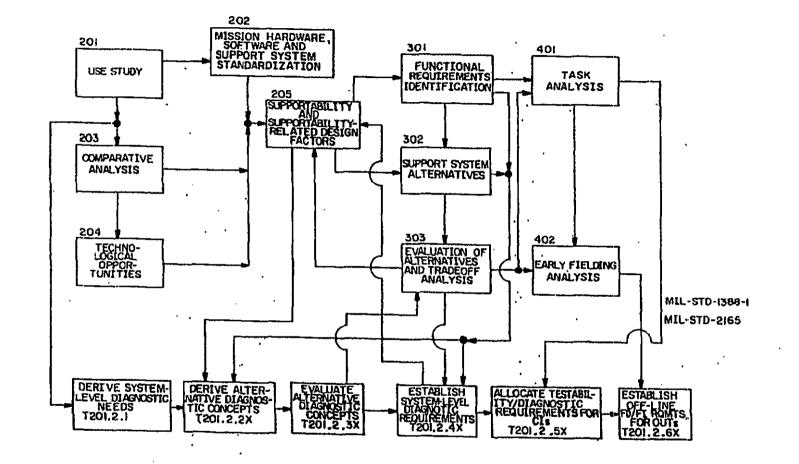

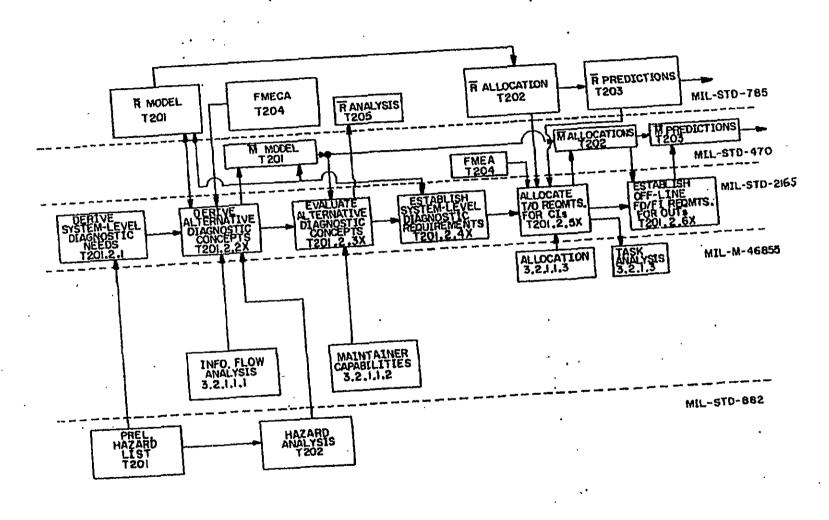

40.2 <u>System testability program (see figure 1)</u>. For major systems, the testability tasks for each program phase are summarized in table I and listed below.

(a) Concept exploration phase.

- (1) Develop testability program plan (see task 101).

- (2) Establish system-level fault detection and isolation requirements (see task 201).

1.7 .

(3) Conduct testability reviews, as part of system requirements review (see task 102).

- (b) Demonstration and validation phase.

- (1) Develop testability program plan (see task 101).

- (2) Allocate diagnostic requirements (see task 201).

- (3) Impose testability design discipline (see task 202).

- (4) Conduct testability reviews as part of system design reviews (see task 102).

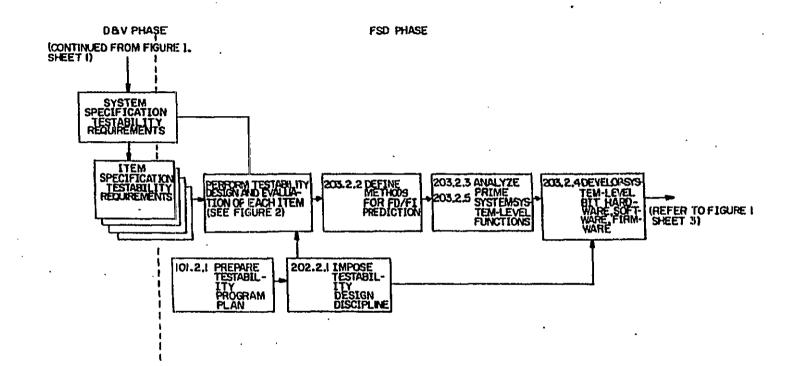

- (c) Full-scale development phase.

- (1) Develop testability program plan (see task 101).

- (2) Incorporate testability features into full-scale development items and evaluate effectiveness (see task 202 and 203).

- (3) Conduct testability reviews as part of preliminary and critical design reviews (see task 102).

- (4) Ensure compatibility of diagnostic elements (see task 203).

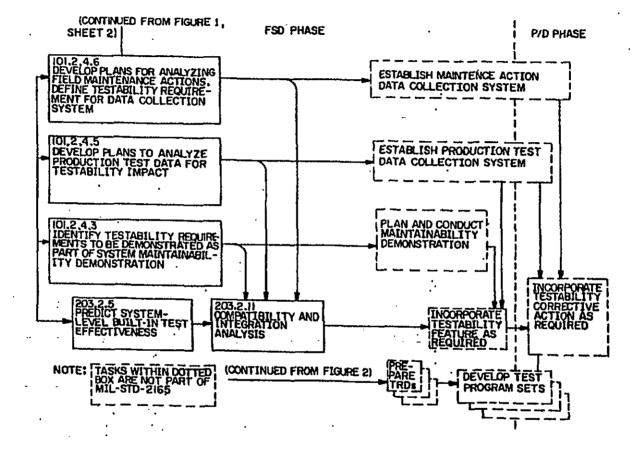

- (d) Production and Deployment Phase

- (1) Collect data on achieved testability effectiveness.

- (2) Take corrective action.

# FIGURE 1. System testability program flow diagram.

3

ŧ

| TASK |                                                      | PROGRAM PHASE    |     |      |     |

|------|------------------------------------------------------|------------------|-----|------|-----|

|      |                                                      | · CE             | D&V | ED/M | P/D |

| 101  | Testability program planning                         | G                | G   | G    | N/A |

| 102  | Testability reviews                                  | G                | G   | G    | · S |

| 201  | Diagnostic concepts and testability requirements     | G                | G   | G    | N/A |

| 202  | Inherent testability design<br>and assessment        | N/A              | S   | G    | S   |

| 203. | Testability detail design<br>and analysis assessment | N/A <sup>.</sup> | s   | ∵ G  | S   |

## TABLE I. Task application guidance matrix.

S - Electively applicable to high-risk items during D&V, or to design changes during P/D D&V - Demonstration and validation ED/M - Engineering development and manufacturing P/D - Production/Deployment

1/D - 11000001010 00p109.2011

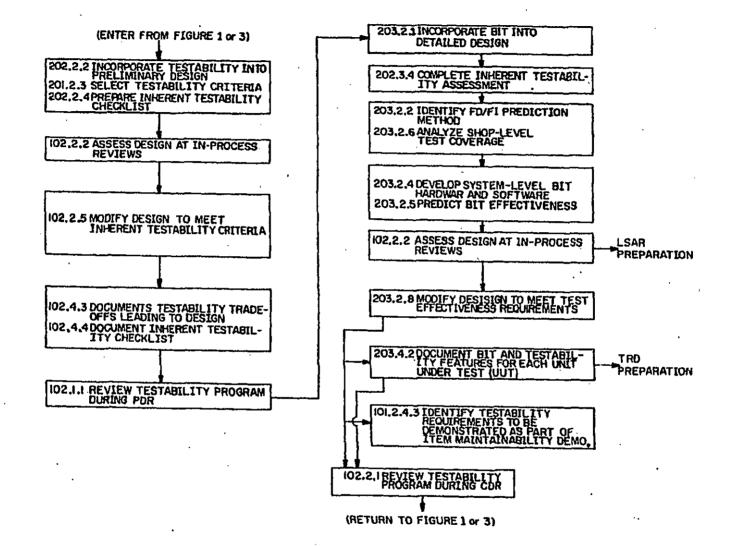

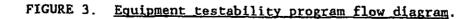

40.3 <u>Item testability program (see figure 2)</u>. For all items, whether developed as a subsystem under a system acquisition program or developed under an equipment acquisition program, the testability tasks are listed below:

- (a) Preliminary design.

- (1) Develop testability program plan, if a plan was not developed as part of a system acquisition program (see task 101).

- (2) Incorporate testability features into preliminary design (see task 202).

- (3) Develop inherent testability checklist for each item (see task 202).

- (4) Conduct testability review as part of preliminary design review (see task 102).

(b) Detail design.

- (1) Predict inherent testability for each item (see task 202).

- (2) Incorporate testability features into detail design (see task 203).

- (3) Predict test effectiveness for each item (see task 203).

- (4) Conduct testability review as part of the critical design review (see task 102).

40.4 <u>Criteria for imposing a testability program during the D&V phase</u>. During D&V phase, a formal testability program should be applied to the system integration effort and, in addition, shall be selectively applied to those subsystems which present a high risk in testing. The high risk aspect of test design may be a result of:

- (a) A criticality of function to be tested,

- .(b) Difficulty of achieving desired test quality at an affordable cost,

- (c) Difficulty of defining appropriate testability measures or demonstrations for technology being tested,

- (d) Large impact on maintainability if expected test quality, automation, throughput, and other requirements, are not achieved, or

- (e) High probability that modifications to the subsystem during ED/M will be limited.

40.5 <u>Equipment testability program (see figure 3)</u>. For the acquisition of less-than-major systems or individual equipments, the testability tasks are listed below.

- (a) Establish system or equipment testability requirements. (Performed by requiring authority using the process defined in task 201.)

- (b) Develop testability program plan (see task 101).

- (c) Incorporate testability features into items and evaluate effectiveness (see 40.3).

. . .

(d) Collect data on achieved testability effectivenesss (performed by requiring authority using figure 1, sheet 3 as guidance):

40.6 <u>Iterations</u>. Certain tasks contained in this standard are highly iterative in nature and recur at various times during the acquisition cycle, proceeding to lower levels of hardware indenture and greater detail in the classical systems engineering manner.

50. DETAILED APPLICATION GUIDANCE

This section provides detailed guidance for conducting each testability task.

50.1 Task 101, testability program planning.

50.1.1 <u>Scope</u>. The testability program plan is the basic tool for establishing and executing an effective testability program. The testability program plan should document what testability tasks are to be accomplished, how each task will be accomplished, when they will be accomplished, and how the results of the task will be used. The testability program plan may be a stand-alone document, but preferably should be included as part of the systems engineering management plan (SEMP), if one is required. Plans assist the requiring authority in evaluating the prospective performing activities approach to, and understanding of, the testability task requirements and the organizational structure for performing testability tasks. The testability program plan should be closely coordinated with the maintainability program plan and the LSA plan.

30

M1L-STD-2165A APPENDIX A

50.1.2 <u>Submission of the plan</u>. When requiring a testability program plan, the requiring authority should allow the performing activity to propose specifically tailored tasks with supporting rationale to show overall program benefits. The testability program plan should be a dynamic document that reflects current program status and planned actions. Accordingly, procedures shall be established for updates and approval of updates by the requiring authority when conditions warrant. Program schedule changes, test results, or testability task results may dictate a change in the testability program plan, in order for it to be used effectively as a management document.