ECSS-Q-70-38A 26 October 2007

# Space product assurance

High-reliability soldering for surface-mount and mixed technology

ECSS Secretariat ESA-ESTEC Requirements & Standards Division Noordwijk, The Netherlands

| Published by: | ESA Requirements and Standards Division<br>ESTEC, P.O. Box 299,<br>2200 AG Noordwijk,<br>The Netherlands |

|---------------|----------------------------------------------------------------------------------------------------------|

| ISSN:         | 1028-396X                                                                                                |

| Price:        | € 30                                                                                                     |

| Printed in:   | The Netherlands                                                                                          |

| Copyright:    | @2007 by the European Space Agency for the members of ECSS                                               |

# Foreword

This Standard is one of the series of ECSS Standards intended to be applied together for the management, engineering and product assurance in space projects and applications. ECSS is a cooperative effort of the European Space Agency, national space agencies and European industry associations for the purpose of developing and maintaining common standards.

Requirements in this Standard are defined in terms of what shall be accomplished, rather than in terms of how to organize and perform the necessary work. This allows existing organizational structures and methods to be applied where they are effective, and for the structures and methods to evolve as necessary without rewriting the standards.

The formulation of this Standard takes into account the existing ISO 9000 family of documents.

This Standard has been prepared by the ECSS-Q-70-38 Working Group, reviewed by the former ECSS Product Assurance Panel and the ECSS Executive Secretriat and approved by the ECSS Technical Authority.

(This page is intentionally left blank)

# Introduction

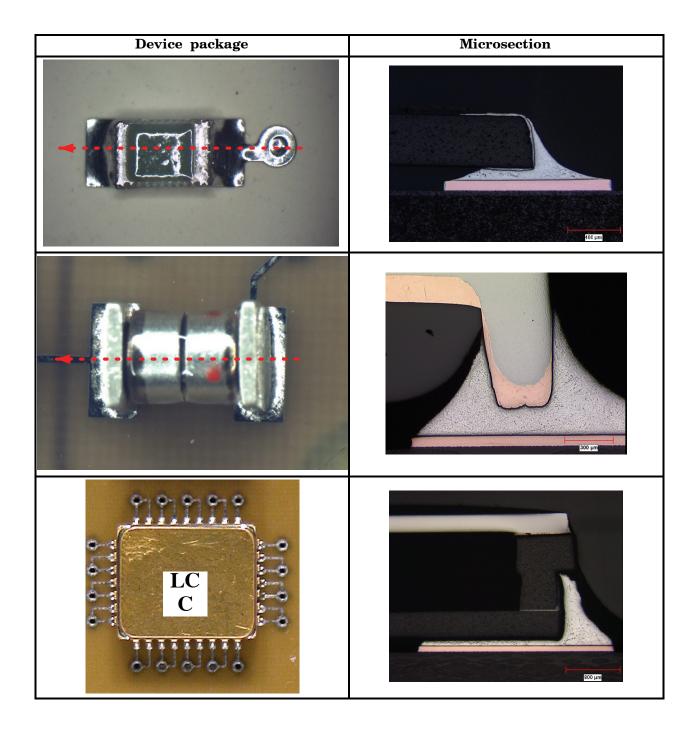

This Standard prescribes requirements for electrical connections of leadless and leaded surface mounted devices (SMD) on spacecraft and associated equipment, utilising a range of substrate assemblies and employing solder as the interconnection media. The principal types of SMDs can be gathered in the following families:

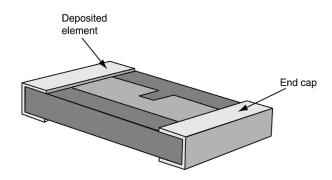

| Rectangular and square end-capped or end-me-<br>tallized device with rectangular body<br>e.g. end capped chip resistors and end capped chip<br>capacitors.                                                                                                                                                      |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

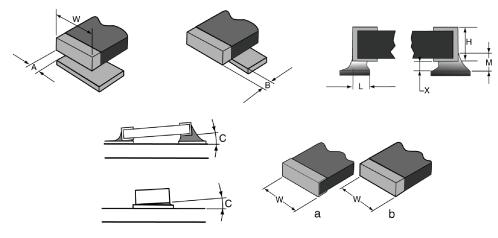

| <b>Bottom terminated chip device</b><br>This type of device has metallised terminations on<br>the bottom side only.                                                                                                                                                                                             |             |

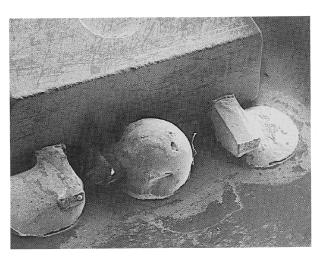

| <b>Cylindrical or square end-capped devices with</b><br><b>cylindrical body</b><br>e.g. MELF.                                                                                                                                                                                                                   | GHB         |

| <b>Castellated chip carrier device</b><br>The main component of this type is leadless ceramic<br>chip carrier (LCCC).                                                                                                                                                                                           |             |

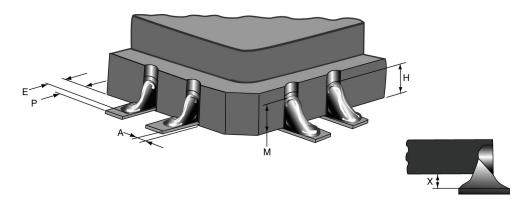

| <b>Device with round, flattened, ribbon "L" and</b><br><b>gull-wing leads</b><br>e.g. small-outline transistor (SOT), small-outline<br>package (SO), flat pack and quad flat pack (QFP).<br>This family also comprises devices for through-hole<br>mounting that have been reconfigured to surface<br>mounting. | STITUTE OF  |

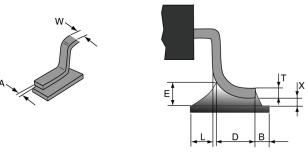

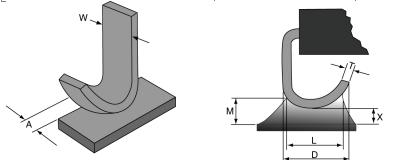

| <b>"J" leaded device</b><br>e.g. ceramic leaded chip carriers (CLCC) and plastic<br>leaded chip carriers (PLCC).                                                                                                                                                                                                | CUCCC ANNUN |

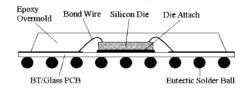

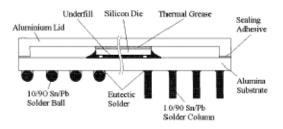

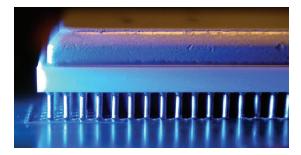

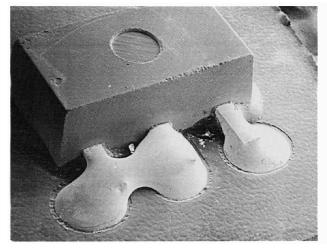

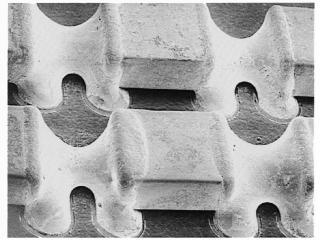

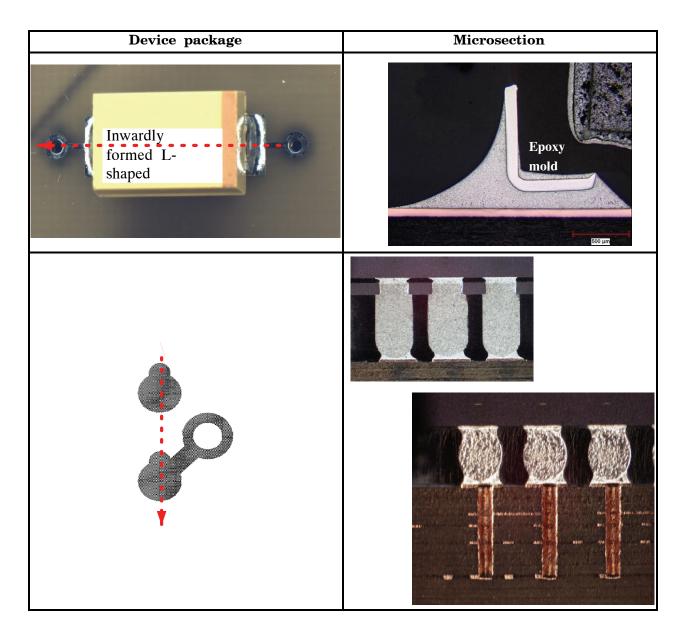

| Area array devices<br>These devices are leadless (no leads). The intercon-<br>nections between solder pads on the devices and<br>solder pads on the PCB consist entirely of solder.<br>The devices have either solder balls (Ball Grid<br>Array – BGA) or solder columns (Column Grid<br>Array – CGA) applied to the solder pads on the<br>devices prior to mounting on a PCB (normally done<br>by the device manufacturer). The solder balls on the<br>BGAs can consist of either eutectic solder or high<br>temperature solder $(5 \% - 10 \% \text{ Sn})$ whereas the<br>solder columns on the CGAs always consist of high<br>temperature solder. Although BGAs are usually<br>presented as a device family, there exist a large<br>number of BGA devices with wide-ranging prop-<br>erties. The vast majority of BGA devices are non-<br>hermetic. |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

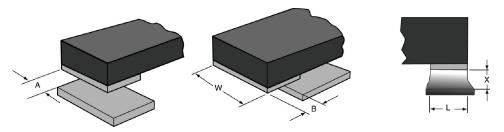

| Device with Inward formed L-shaped leads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| e.g. moulded tantalum chip capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| Device with flat lug leads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| This package has flat leads extending from the sides.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

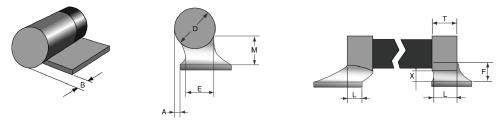

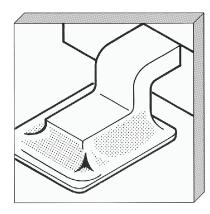

| <b>Leaded device with thermal plane termination</b><br>e.g. Diode PAcKage (DPAK).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DPAK |

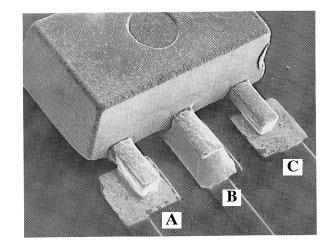

| <b>Leadless device with thermal plane termination</b><br>This SMD package consists of three terminal pads,<br>ceramic housing, and lid brazed together to form a<br>hermetic semiconductor die carrier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EL   |

# Contents

| Fore  | preword                                                                                                                                                                                                                            | <br>3                                                                                                      |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Intro | troduction                                                                                                                                                                                                                         | <br>5                                                                                                      |

| 1     | Scope                                                                                                                                                                                                                              | <br>13                                                                                                     |

| 2     | Normative references                                                                                                                                                                                                               | <br>15                                                                                                     |

| 3     | Terms, definitions and abbreviations3.1Terms and definitions3.2Abbreviated terms                                                                                                                                                   | <br><b>17</b><br>17<br>18                                                                                  |

| 4     | Principles of reliable soldered connections                                                                                                                                                                                        | <br>19                                                                                                     |

| 5     | Process identification document (PID)5.1General5.2Production control5.3Process identification document updating                                                                                                                    | <br><b>21</b><br>21<br>21<br>22                                                                            |

| 6     | Preparatory conditions6.1Calibration6.2Facility cleanliness6.3Environmental conditions6.4Precautions against static charges6.5Lighting requirements6.6Equipment and tools6.7Soldering machines and equipment6.8Ancillary equipment | <ul> <li>23</li> <li>23</li> <li>23</li> <li>23</li> <li>23</li> <li>23</li> <li>24</li> <li>26</li> </ul> |

| 7     | Material selection7.1General7.2Solder                                                                                                                                                                                              | <br><b>29</b><br>29<br>29                                                                                  |

|    | 7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9<br>7.10               | Flux                                                                                                                                                                                                                                                                           | 30<br>31<br>31<br>31<br>31<br>31<br>32<br>33        |

|----|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 8  | Preparc<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5                   | Ation for soldering<br>Preparation of devices and terminals<br>Preparation of solder bit<br>Handling<br>Storage<br>Baking of PCBs and moisture sensitive components                                                                                                            | <b>35</b><br>35<br>35<br>35<br>35<br>35             |

| 9  | Mountin<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7     | Ang of devices prior to soldering<br>General requirements<br>Lead bending and cutting requirements<br>Mounting of terminals to PCBs<br>Lead attachment to through holes<br>Mounting of components to terminals<br>Mounting of connectors to PCBs<br>Surface mount requirements | <b>37</b><br>37<br>37<br>37<br>37<br>37<br>37<br>37 |

| 10 | Attachr                                                      | nent of conductors to terminals, solder cups and cables                                                                                                                                                                                                                        | 41                                                  |

| 11 | Solderii                                                     | ng to terminals and printed circuit boards                                                                                                                                                                                                                                     | 42                                                  |

|    | 11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8 | General<br>Solder application to terminals<br>Solder applications to PCBs<br>Wicking<br>Soldering of SMDs<br>Tall profile devices<br>Staking of solder assembly<br>Underfill                                                                                                   | <b>43</b> 43 43 43 43 43 50 50 50                   |

|    | 11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8 | General<br>Solder application to terminals<br>Solder applications to PCBs<br>Wicking<br>Soldering of SMDs<br>Tall profile devices<br>Staking of solder assembly                                                                                                                | 43<br>43<br>43<br>43<br>43<br>50<br>50              |

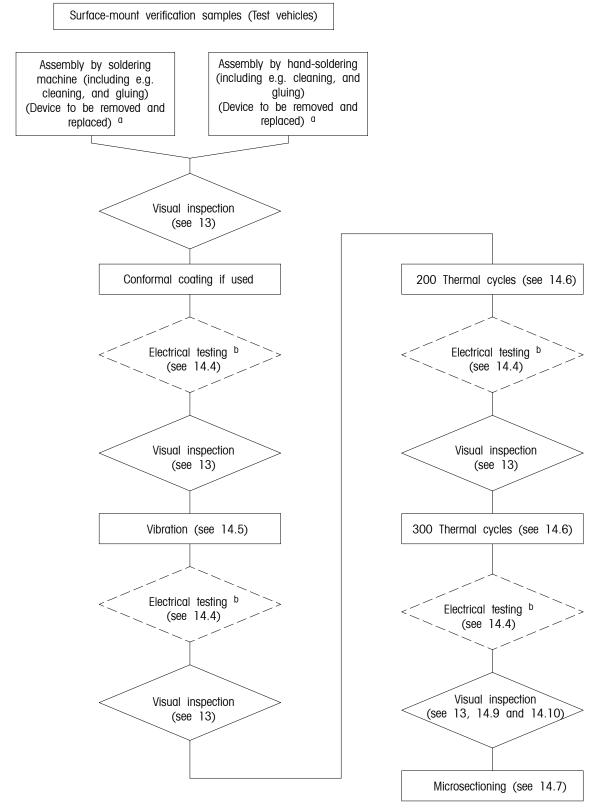

| 14  | Verifica    | tion procedure                                                          | 55         |

|-----|-------------|-------------------------------------------------------------------------|------------|

|     | 14.1        | General                                                                 | 55         |

|     | 14.2        | Verification by similarity                                              | 56         |

|     | 14.3        | Verification test programme                                             | 56         |

|     | 14.4        | Electrical testing of passive components                                | 59         |

|     | 14.5        | Vibration                                                               | 59         |

|     | 14.6        | Temperature cycling test                                                | 59         |

|     | 14.7        |                                                                         | 59         |

|     | 14.8        | Dye penetrant test                                                      | 59         |

|     | 14.9        | Special verification testing for conformally coated area array packages | 60         |

|     | 14.10       | Failures after verification testing                                     | 60         |

|     | 14.11       | Approval of verification                                                | 61         |

|     | 14.12       | Withdrawal of approval status                                           | 62         |

|     |             |                                                                         | 02         |

| 15  | Quality     | assurance                                                               | 63         |

| 15  | 15.1        |                                                                         | 63         |

|     | 15.1        | General                                                                 | 63         |

|     |             |                                                                         |            |

|     | 15.3        |                                                                         | 63         |

|     | 15.4        |                                                                         | 63         |

|     | 15.5        | Traceability                                                            | 63         |

|     | 15.6        | Workmanship standards                                                   | 63         |

|     | 15.7        |                                                                         | 63         |

|     | 15.8        | Operator and inspector training and certification                       | 63         |

|     | 15.9        | Quality records                                                         | 64         |

| - / |             |                                                                         | <i>.</i> - |

| 10  |             | and X-ray workmanship standards                                         | 65         |

|     | 16.1        | Workmanship illustrations for standard SMDs                             | 65         |

|     | 16.2        | Workmanship illustrations for ball grid array devices                   | 71         |

|     | 16.3        | Workmanship illustrations for column grid array devices                 | 75         |

|     | 16.4        |                                                                         | 81         |

|     | 16.5        | Accept and reject criteria after environmental testing                  | 83         |

| •   |             |                                                                         |            |

| Anr | •           | ormative) Verification approval                                         | 89         |

|     | A.1         | General                                                                 | 89         |

|     | A.2         | Methodology of approval                                                 | 89         |

|     |             |                                                                         |            |

| Anr | nex B (info | ormative) Examples of SMT summary tables                                | 93         |

| _   |             |                                                                         |            |

| Anr | •           | ormative) Soldering of area array devices                               | 99         |

|     | C.1         | General                                                                 | 99         |

|     | C.2         | Solder joint requirements                                               | 99         |

|     | C.3         | Removal and replacement of area array devices                           | 102        |

|     | C.4         |                                                                         | 103        |

|     | C.5         | Verification testing                                                    | 105        |

|     | C.6         | References                                                              | 105        |

| Anr | nex D (inf  | ormative) Example of an SMT audit report                                | 107        |

| Δnr | ex F (inf/  | ormative) Additional information                                        | 115        |

|     | E.1         | X-Ray inspection equipment (to 6.8.7)                                   | 115        |

|     | E.1<br>E.2  | Melting temperatures and choice                                         | 115        |

|     | L . L       |                                                                         | 110        |

| ECSS-Q-70-38A<br>26 October 2007 | Ecs |

|----------------------------------|-----|

| Bibliography                     | 117 |

# Figures

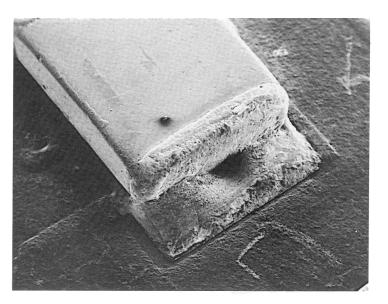

| Figure 1: | Exposed element                                                                                                       | 39 |

|-----------|-----------------------------------------------------------------------------------------------------------------------|----|

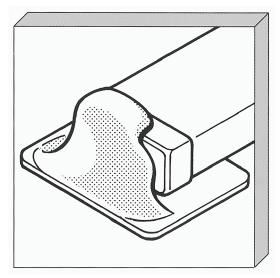

| Figure 2: | Mounting of rectangular and square end-capped and end-metallized                                                      |    |

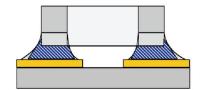

|           | devices                                                                                                               | 44 |

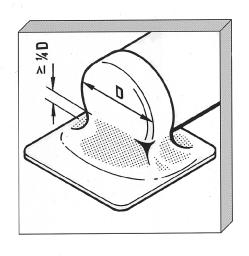

| Figure 3: | Mounting of bottom terminated chip devices                                                                            | 45 |

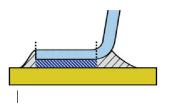

| Figure 4: | Mounting of cylindrical end-capped devices                                                                            | 45 |

| Figure 5: | Mounting of castellated chip carrier devices                                                                          | 46 |

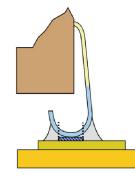

| Figure 6: | Mounting of devices with round, flattened, ribbon, "L" and gull-wing leads $\ldots$                                   | 47 |

| Figure 7: | Mounting of devices with "J" leads                                                                                    | 48 |

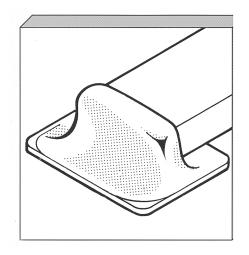

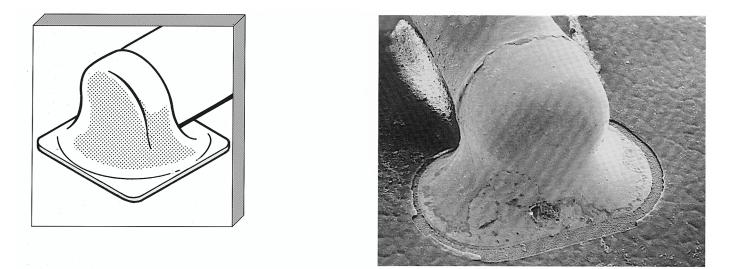

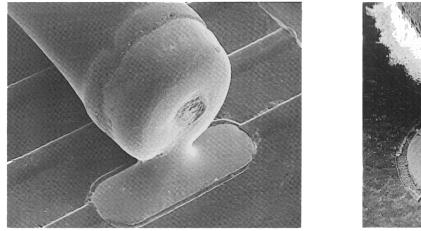

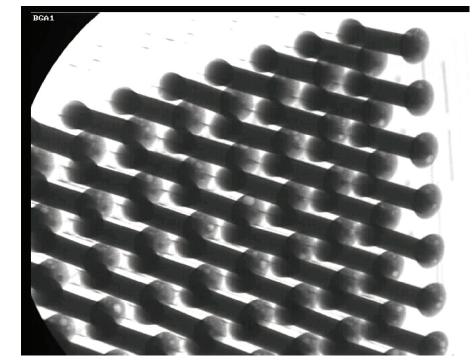

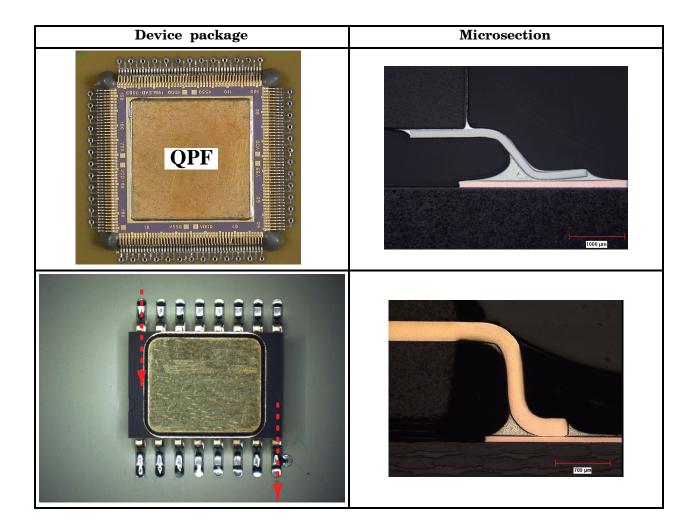

| Figure 8: | Typical plastic ball grid array (PBGA)                                                                                | 49 |

| Figure 9: | Typical ceramic area array showing ball grid array configuration on left and column grid array on right (CBGA & CCGA) | 49 |

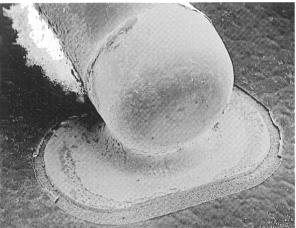

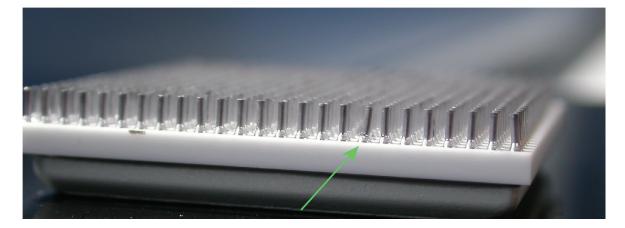

| Figure 10 | : Typical assembled CCGA device                                                                                       | 50 |

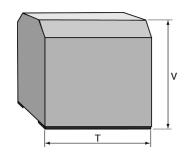

| Figure 11 | : Dimensions of tall profile components                                                                               | 50 |

| Figure 12 | : Verification programme flow chart                                                                                   | 58 |

| Figure 13 | : Illustrations defining critical zone in solder fillet                                                               | 61 |

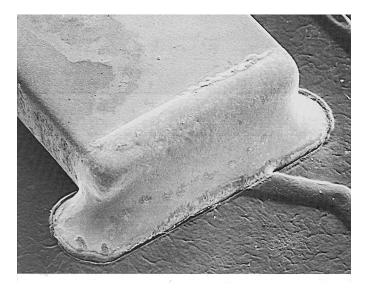

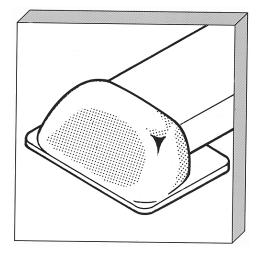

| Figure 14 | : Preferred solder (see also Table 3)                                                                                 | 65 |

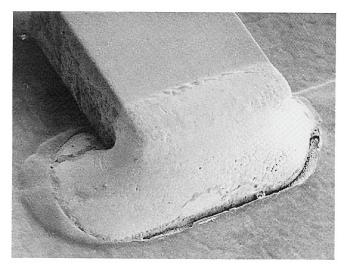

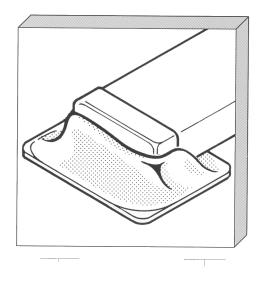

| Figure 15 | : Acceptable, maximum solder (see also Table 3)                                                                       | 66 |

| Figure 16 | : Unacceptable, poor wetting (see also Table 3)                                                                       | 66 |

| Figure 17 | : Unacceptable - Less than 75 $\%$ wetting of terminal edges (see also Table 3) .                                     | 67 |

| Figure 18 | : Acceptable, minimum solder - Terminal wetted along end, face and sides                                              |    |

|           | (see also Table 5)                                                                                                    | 68 |

| -         | : Preferred solder (see also Table 5)                                                                                 | 68 |

| Figure 20 | : Unacceptable - Excessive solder (see also Table 5)                                                                  | 69 |

| Figure 21 | : Unacceptable - Insufficient solder (see also Table 5)                                                               | 69 |

| Figure 22 | : Example of flattened leads                                                                                          | 70 |

| Figure 23 | : Unacceptable - Excessive solder (middle joint)                                                                      | 70 |

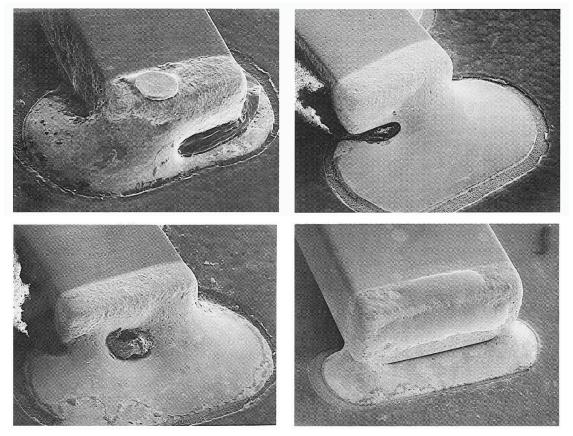

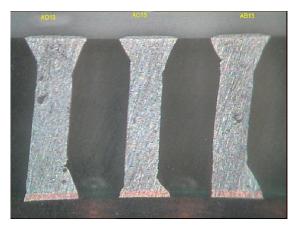

| Figure 24 | : Examples of unacceptable soldering                                                                                  | 71 |

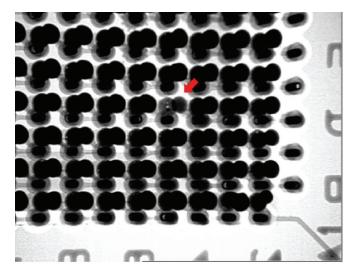

| Figure 25 | : Angled-transmission X-radiograph showing solder paste shadow due to partial reflow: Reject                          | 71 |

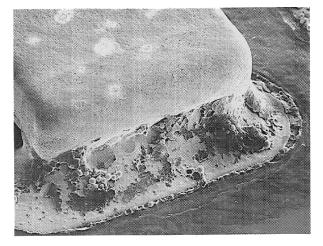

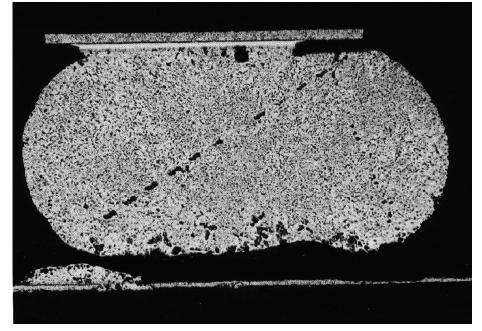

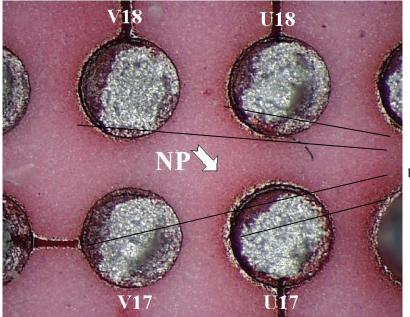

| Figure 26 | : Micrograph showing                                                                                                  | 71 |

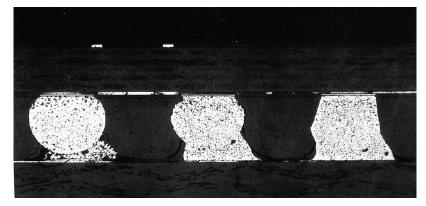

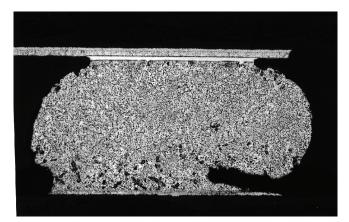

| Figure 27 | : Microsection showing partial reflow of solder paste: Reject                                                         | 72 |

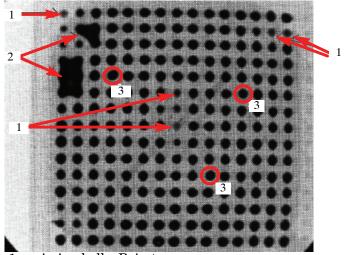

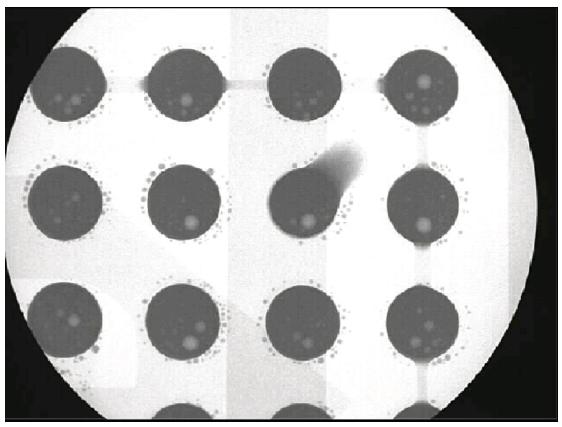

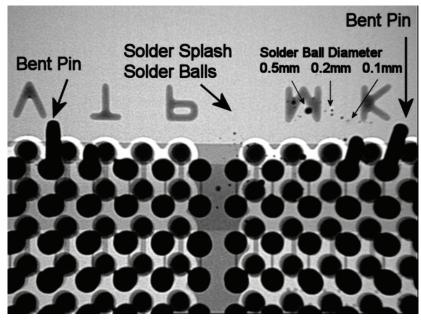

| Figure 28 | Perpendicular transmission X-radiograph showing unacceptable defects                                                  | 72 |

| Figure 29 | : Perpendicular transmission X-radiograph showing non-wetted pad                                                      | 73 |

| Figure 30 | : Angled transmission X-radiograph showing non-wetted pad: Reject                                                     | 73 |

| Figure 31 | : Microsection through a ball showing non-wetting of solder to pad: Reject $\ldots$                                   | 74 |

| Figure 32 | : Microsection through ball showing partial wetting of solder to pad: Reject                                          | 74 |

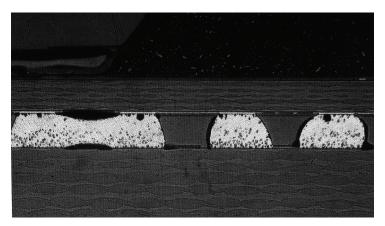

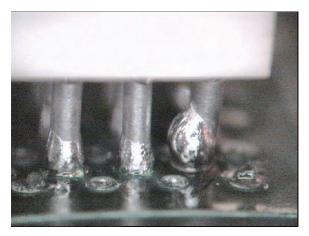

| Figure 33 | : Microsection through ball showing solder bridge: Reject                                                             | 74 |

| Figure 34 | : X-radiograph showing many small voids and solder balls: Reject                                                      | 75 |

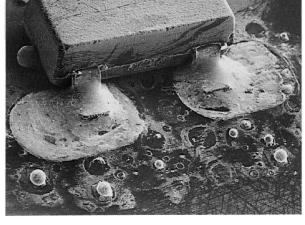

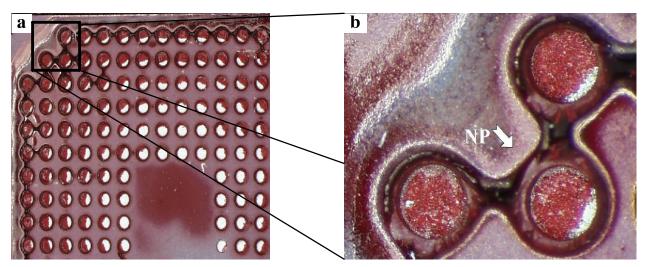

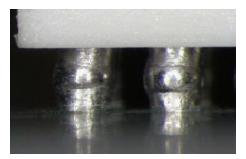

| Figure 35: | Underside view showing                                                                                          | 75  |

|------------|-----------------------------------------------------------------------------------------------------------------|-----|

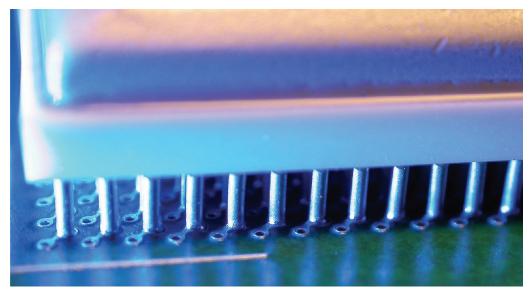

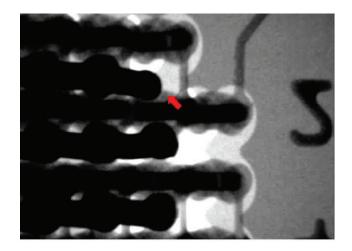

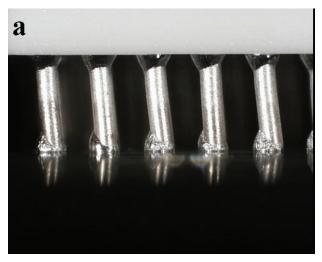

| Figure 36: | Side view showing column column by more than $5^\circ$ : Reject                                                 | 76  |

| Figure 37: | CGA mounted on PCB showing perpendicular columns centrally placed on pads: Target condition                     | 76  |

| Figure 38: | CGA mounted on PCB showing columns tilted $< 5^{\circ}$ : Accept                                                | 77  |

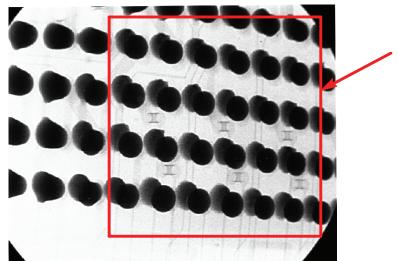

| Figure 39: | X-radiograph of CGA mounted on PCB                                                                              | 77  |

| Figure 40: | X-radiograph of CGA mounted on PCB showing missing column: Reject                                               | 78  |

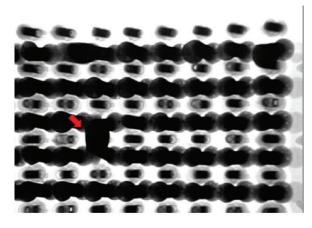

| Figure 41: | X-radiograph of CGA mounted on PCB showing insufficient solder: Reject                                          | 78  |

| Figure 42: | X-radiograph of CGA mounted on PCB showing solder bridge: Reject                                                | 78  |

| Figure 43: | X-radiograph of CGA showing excessive voiding in solder fillets at base of columns: Reject                      | 79  |

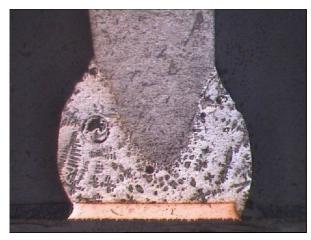

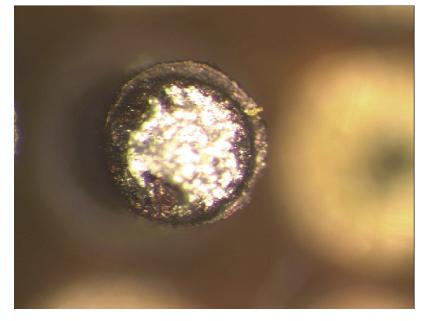

| Figure 44: | Microsection of CGA mounted on PCB                                                                              | 79  |

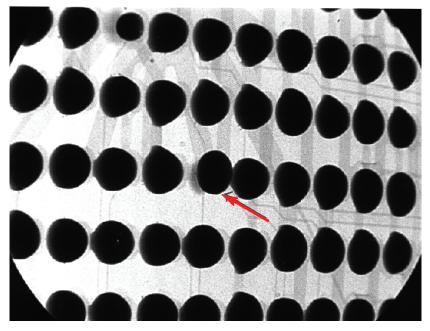

| Figure 45: | Micrograph of CGA mounted on PCB                                                                                | 80  |

| Figure 46: | Micrograph of CGA mounted on PCB                                                                                | 80  |

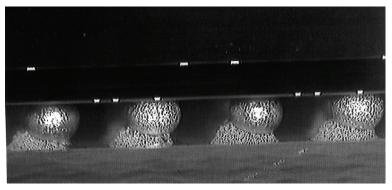

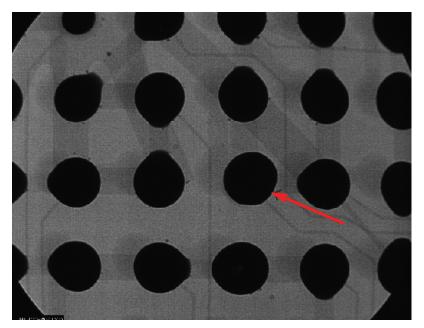

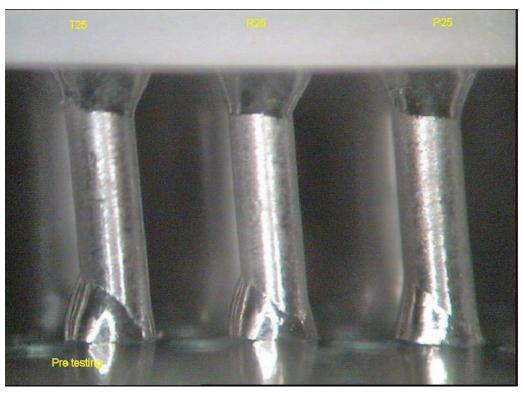

| Figure 47: | Microsection of CGA mounted on PCB showing minimum solder: Acceptable                                           | 80  |

| Figure 48: | Microsection of CGA mounted on PCB showing maximum solder: Acceptable                                           | 81  |

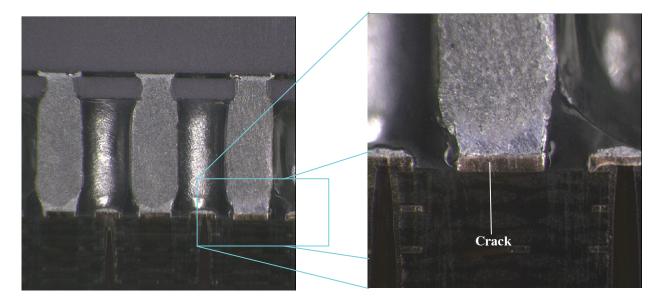

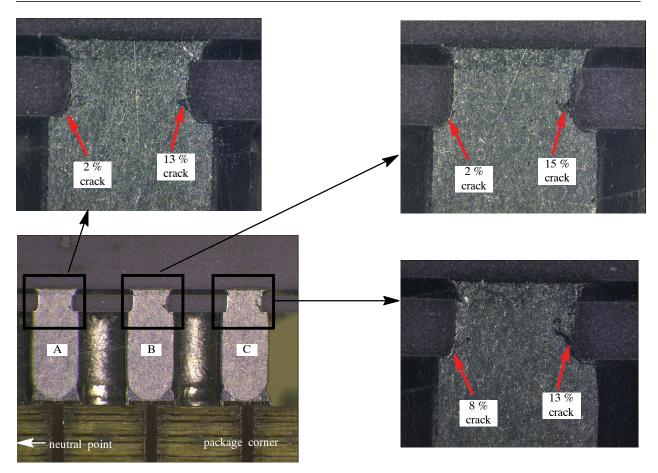

| Figure 49: | Sample after verification sample testing: Microsection of CGA mounted on PCB showing crack in the solder fillet | 83  |

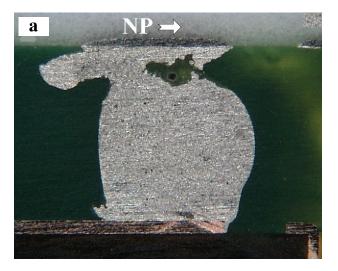

| Figure 50: | Microsection of a CGA showing a crack                                                                           | 84  |

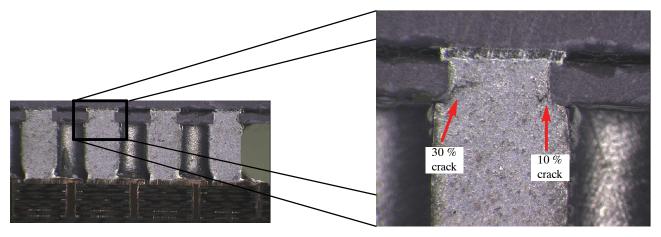

| Figure 51: | Microsection of CGA showing cracks                                                                              | 84  |

| Figure 52: | Microsection of CGA showing cracks                                                                              | 85  |

| Figure 53: | Microsection of CGA showing cracks                                                                              | 86  |

| Figure 54: | Micrography of CBGA after dye penetration testing                                                               | 87  |

| Figure 55: | Micrography of CBGA after dye penetration testing                                                               | 87  |

| Figure 56: | Micrography of a column of CBGA after dye penetration testing                                                   | 88  |

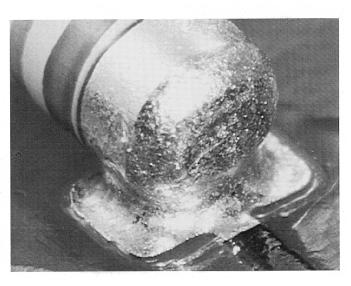

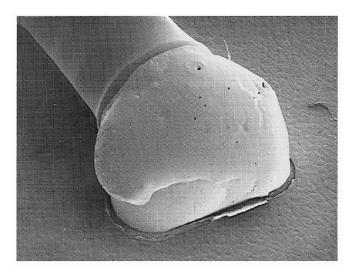

| Figure C-1 | : Typical CBGA solder joint (high melting point balls)                                                          | 100 |

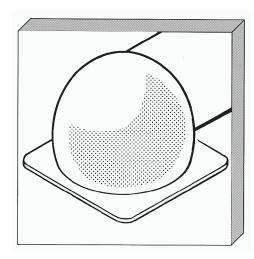

| Figure C-2 | 2: Tilted columns to a CBGA                                                                                     | 101 |

# Tables

| Table 1:  | Chemical composition of spacecraft solders                                                                    | 30  |

|-----------|---------------------------------------------------------------------------------------------------------------|-----|

| Table 2:  | Guide for choice of printed circuit boards and substrates                                                     | 31  |

| Table 3:  | Dimensional and solder fillet requirements for rectangular and square end capped devices                      | 44  |

| Table 4:  | Dimensional and solder fillet requirements for bottom terminated chip devices                                 | 45  |

| Table 5:  | Dimensional and solder fillet requirements for cylindrical end-capped devices                                 | 45  |

| Table 6:  | Dimensional and solder fillet requirements for castellated chip carrier devices                               | 46  |

| Table 7:  | Dimensional and solder fillet requirements for devices with round, flattened, ribbon, "L" and gull-wing leads | 47  |

| Table 8:  | Dimensional and solder fillet requirements for devices with "J" leads                                         | 48  |

| Table 9:  | Dimensional and solder fillet requirements for area array devices                                             | 49  |

| Table E-1 | : Guide for choice of solder type                                                                             | 115 |

(This page is intentionally left blank)

# Scope

This Standard defines the technical requirements and quality assurance provisions for the manufacture and verification of high-reliability electronic circuits based on surface mounted device (SMD) and mixed technology.

The Standard defines acceptance and rejection criteria for high-reliability manufacture of surface-mount and mixed-technology circuit assemblies intended to withstanding normal terrestrial conditions and the vibrational g-loads and environment imposed by space flight.

The proper tools, correct materials, design and workmanship are covered by this document. Workmanship standards are included to permit discrimination between proper and improper work.

The assembly of leaded devices to through-hole terminations and general soldering principles are covered in ECSS-Q-70-08.

Requirements related to printed circuit boards are contained in ECSS-Q-70-10 and ECSS-Q-70-11. The substrates covered by this document are divided into five classes in accordance with their average X and Y coefficient of thermal expansion (CTE).

The mounting and supporting of components, terminals and conductors prescribed herein applies to assemblies designed to operate within the temperature limits of -55 °C to +85 °C.

For temperatures outside this normal range, special design, verification and qualification testing is performed to ensure the necessary environmental survival capability.

Special thermal heat sinks are applied to devices having high thermal dissipation (e.g. junction temperatures of 110 °C, power transistors) in order to ensure that solder joints do not exceed 85 °C.

Verification of SMD assembly processes is made on test vehicles (surface mount verification samples). Temperature cycling ensures the operational lifetime for spacecraft. However, mechanical testing only indicates SMD reliability as it is unlikely that the test vehicle represents every flight configuration.

Examples of the method for achieving SMD verification approval and guidelines for the soldering of area array devices are given in the Annexes.

This Standard does not cover the qualification and acceptance of the EQM and FM equipment with surface-mount and mixed-technology.

The qualification and acceptance tests of equipment manufactured in accordance with this Standard are covered by ECSS-E-10-03.

(This page is intentionally left blank)

\_\_\_\_\_

# Normative references

The following normative documents contain provisions which, through references in this text, constitute provisions of this ECSS Standard. For dated references, subsequent amendments to, or revisions of any of these publications do not apply. However, parties to agreements based on this ECSS Standard are encouraged to investigate the possibility of applying the most recent editions of the normative documents indicated below. For undated references, the latest edition of the publication referred to applies.

| ECSS-P-001B       | ECSS — Glossary of terms                                                                                                                                                  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ECSS-M-50B        | $\label{eq:space} \begin{array}{l} \text{Space project management} & \text{Information/documentation} \\ \text{management} \end{array}$                                   |

| ECSS-Q-20B        | Space product assurance — Quality assurance                                                                                                                               |

| ECSS-Q-20-09B     | Space product assurance — Nonconformance control system                                                                                                                   |

| ECSS-Q-60B        | Space product assurance — Electrical, electronic and electromechanical $\left( EEE\right)$ components                                                                     |

| ECSS-Q-60-05A     | $\label{eq:space} \begin{array}{l} \mbox{Space product assurance} & - \mbox{Generic procurement requirements for hybrid microcircuits} \end{array}$                       |

| ECSS-Q-70B        | Space product assurance — Materials, mechanical parts and processes $% \left( {{{\rm{A}}_{{\rm{A}}}} \right)$                                                             |

| ECSS-Q-70-01A     | ${\it Space \ product \ assurance - Clean liness \ and \ contamination \ control}$                                                                                        |

| ECSS-Q-70-02A     | $\label{eq:space} \begin{array}{l} \mbox{Space product assurance} & - \mbox{A thermal vacuum outgassing} \\ \mbox{test for the screening of space materials} \end{array}$ |

| ECSS-Q-70-08A     | Space product assurance — The manual soldering of high–reliability electrical connections                                                                                 |

| ECSS-Q-70-10A     | Space product assurance — Qualification of printed circuit boards                                                                                                         |

| ECSS-Q-70-11A     | Space product assurance — Procurement of printed circuit boards                                                                                                           |

| ECSS-Q-70-71A     | Space product assurance — Data for selection of space materials                                                                                                           |

| MIL-STD-883 Metho | od 2009.8                                                                                                                                                                 |

(This page is intentionally left blank)

# Terms, definitions and abbreviations

# 3.1 Terms and definitions

For the purposes of this document, the terms and definitions given in ECSS-P-001 and the following apply.

#### 3.1.1

#### approval authority

entity that reviews and accepts the verification programme, evaluating the test results and grants the final approval

#### 3.1.2

#### co-planarity

maximum distance between lowest and highest termination when device rests on flat surface

#### 3.1.3

#### electrical clearance

spacing between non-common electrical conductors on external layers of a printed circuit board assembly

NOTE The distance between conductors depends on the design voltage and DC or AC peaks. Any violation of minimum electrical clearance as a result of a nonconformance is a defect condition.

#### 3.1.4

#### scavenging (leaching)

basis metal or metallization partly or wholly dissolved in melted solder during a soldering operation

#### 3.1.5

#### selective plating

tin-lead plated solder pads connected to gold plated copper tracks

NOTE It is usually related to RF circuits

#### 3.1.6

#### solder balling (solder balls)

numerous spheres of solder having not melted in with the joint form and being scattered around the joint area normally attached by flux residues

NOTE Can be caused by incorrect preheating or poor quality solder.

# 3.1.7

#### tombstoning

$chip \, components \, lifting \, off \, one \, of \, their \, two \, terminal \, pads \, causing \, the \, chip \, to \, stand \, up \, \, like \, a \, tombstone.$

NOTE Normally caused by:

- bad design where one pad reaches solder reflow temperature before the other;

- different quantities of solder paste on each pad;

- different solderability of one pad or one termination with respect to the other.

#### 3.1.8

#### underfill

encapsulant material deposited between a device and substrate used to reduce the mechanical stress resulting from a mismatch in the coefficient of thermal expansion (CTE) between the device and the substrate

#### 3.1.9

#### dynamic wave soldering machine

system that achieves wave soldering and which consists of stations for fluxing, preheating, and soldering by means of a conveyer

# 3.2 Abbreviated terms

The following abbreviated terms are defined and used within this document:

| BGAball grid arrayCBGAceramic ball grid arrayCGAcolumn grid arrayCCGAceramic column grid arrayCLCCceramic leaded chip carrierCTEcoefficient of thermal expansionJEDECJoint Electron Device Engineering CouncilLCCCleadless ceramic chip carrierMELFmetal electrode face bondedNOTEAlso known as minimelf or micromelfMCGAmultichip column grid arrayPCBprinted circuit boardPLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mounted deviceSMTsurface.mount technologySOsmall outlineSOTsmall outline transistorTOtransistor outline | Abbreviation | Meaning                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------|

| CGAcolumn grid arrayCCGAceramic column grid arrayCLCCceramic leaded chip carrierCTEcoefficient of thermal expansionJEDECJoint Electron Device Engineering CouncilLCCCleadless ceramic chip carrierMELFmetal electrode face bondedNOTEAlso known as minimelf or micromelfMCGAmultichip column grid arrayPCBprinted circuit boardPLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mounted deviceSMTsurface-mount technologySOsmall outlineSOTsmall outline transistor                                                                  | BGA          | ball grid array                           |

| CCGAceramic column grid arrayCLCCceramic leaded chip carrierCTEcoefficient of thermal expansionJEDECJoint Electron Device Engineering CouncilLCCCleadless ceramic chip carrierMELFmetal electrode face bondedMCGAmultichip column grid arrayPCBprinted circuit boardPLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mount deviceSMTsurface mount technologySOsmall outline deviceSOTsmall outline transistor                                                                                                                        | CBGA         | ceramic ball grid array                   |

| CLCCceramic leaded chip carrierCTEcoefficient of thermal expansionJEDECJoint Electron Device Engineering CouncilLCCCleadless ceramic chip carrierMELFmetal electrode face bondedMCGAmultichip column grid arrayPCBprinted circuit boardPLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mount deviceSMTsurface-mount technologySOsmall outlineSOTsmall outline transistor                                                                                                                                                            | CGA          | column grid array                         |

| CTE coefficient of thermal expansion<br>JEDEC Joint Electron Device Engineering Council<br>LCCC leadless ceramic chip carrier<br>MELF metal electrode face bonded<br>NOTE Also known as minimelf or micromelf<br>MCGA multichip column grid array<br>PCB printed circuit board<br>PLCC plastic leaded chip carrier<br>PID process identification document<br>QFP quad flat pack<br>r.m.s. root-mean-square<br>SMD surface mounted device<br>SMT surface-mount technology<br>SO small outline<br>SOD small outline device                                                                               | CCGA         | ceramic column grid array                 |

| JEDECJoint Electron Device Engineering CouncilJEDECJoint Electron Device Engineering CouncilLCCCleadless ceramic chip carrierMELFmetal electrode face bondedNOTEAlso known as minimelf or micromelfMCGAmultichip column grid arrayPCBprinted circuit boardPLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mount deviceSMTsurface-mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                  | CLCC         | ceramic leaded chip carrier               |

| LCCCleadless ceramic chip carrierMELFmetal electrode face bondedNOTEAlso known as minimelf or micromelfMCGAmultichip column grid arrayPCBprinted circuit boardPLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mounted deviceSMTsurface small outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                              | СТЕ          | coefficient of thermal expansion          |

| MELFmetal electrode face bonded<br>NOTE Also known as minimelf or micromelfMCGAmultichip column grid arrayPCBprinted circuit boardPLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mounted deviceSMTsurface-mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                        | JEDEC        | Joint Electron Device Engineering Council |

| NOTEAlso known as minimelf or micromelfMCGAmultichip column grid arrayPCBprinted circuit boardPLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mount ed deviceSMTsunface mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                           | LCCC         | leadless ceramic chip carrier             |

| MCGAmultichip column grid arrayPCBprinted circuit boardPLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mounted deviceSMTsunface-mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                                                                   | MELF         | metal electrode face bonded               |

| PCBprinted circuit boardPLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mounted deviceSMTsurface-mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                                                                                                  |              | NOTE Also known as minimelf or micromelf  |

| PLCCplastic leaded chip carrierPIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mounted deviceSMTsurface-mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                                                                                                                          | MCGA         | multichip column grid array               |

| PIDprocess identification documentQFPquad flat packr.m.s.root-mean-squareSMDsurface mounted deviceSMTsurface-mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                                                                                                                                                         | РСВ          | printed circuit board                     |

| QFPquad flat packr.m.s.root-mean-squareSMDsurface mounted deviceSMTsurface-mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                                                                                                                                                                                           | PLCC         | plastic leaded chip carrier               |

| r.m.s.root-mean-squareSMDsurface mounted deviceSMTsurface-mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PID          | process identification document           |

| SMDsurface mounted deviceSMTsurface-mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | QFP          | quad flat pack                            |

| SMTsurface-mount technologySOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | r.m.s.       | root-mean-square                          |

| SOsmall outlineSODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SMD          | surface mounted device                    |

| SODsmall outline deviceSOTsmall outline transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SMT          | surface-mount technology                  |

| <b>SOT</b> small outline transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SO           | small outline                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SOD          | small outline device                      |

| TO transistor outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SOT          | small outline transistor                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ТО           | transistor outline                        |

# Principles of reliable soldered connections

The following are the general principles to ensure reliable soldered connections:

- Reliable soldered connections are the result of proper design, control of tools, materials, processes and work environments, and workmanship performed in accordance to verified and approved procedures, inspection control and precautions.

- The basic design concepts to ensure reliable connections and to avoid solder joint failure are as follows:

- Stress relief is an inherent part of the design, which reduces detrimental thermal and mechanical stresses on the solder connections.

- Where adequate stress relief is not possible materials are so selected that the mismatch of thermal expansion coefficients is a minimum at the constraint points in the device mounting configuration.

- The assembled substrates are designed to allow easy inspection.

- Since only the outer row of solder joints to area array packages can be visually inspected, inner rows are inspected using X-ray techniques. To facilitate X-ray inspection of the solder joints to BGAs, the solder pads have a teardrop design.

- Circuit designs for area array devices, (e.g. BGA, CGA) have clearance around the perimeter of these packages to ensure that reflow nozzles can perform rework or repair operations (see ECSS-Q-70-28 [12]). The clearance depends on the equipment used for reworking and the height of adjacent components.

- NOTE Unpopulated areas on the underside of the substrate assist indirect heating for removal of these packages. See also Annex C, subclause C.3.

- Soldering to gold using tin-lead alloy can cause failure.

(This page is intentionally left blank)

# Process identification document (PID)

# 5.1 General

#### 5.1.1 Purpose

The purpose of the PID is to ensure that a precise reference is established for the assembly processes approved in accordance with this Standard.

The PID provides a standard reference against which any anomalies occurring after the approval can be examined and resolved.

#### 5.1.2 Document preparation

The supplier shall prepare the PID according to subclause 5.1.3.

#### 5.1.3 Content

- a. The PID shall comprise

- (a) the assembly design configuration

- (b) materials and components used in manufacture

- (c) all manufacturing assembly processes and production controls

- (d) all inspection steps with associated methods.

- NOTE This ensures that all future assemblies supplied by the manufacturer are manufactured according to procedures that are identical to those for which approval was granted.

- b. All processes and procedures shall be verified and approved.

#### 5.1.4 Approval

- a. The PID shall be submitted to the approval authority

- b. The Approval authority shall approve the PID.

# 5.2 Production control

a. The PID shall contain a production flow chart which identifies all individual processes, inspections and a summary table that compiles all verified surface mount components and materials

NOTE See Annex B for examples.

b. The points of application of quality controls shall be identified.

- c. The flow chart shall present the processes, inspections and quality controls schematically in their correct sequence and, for each operation, make reference to the corresponding documents.

- d. The issue number and date of documents applicable at the time of preparation of the flow chart shall be stated.

- e. The following symbols shall be used to prepare the chart:

for process and assembly operations  $% \left( f_{i}, f$

for inspection and test operations

for quality control operations

# 5.3 Process identification document updating

- a. The PID shall be managed in accordance with ECSS-M-50.

- b. A PID shall represent the current verified manufacturing processes and production controls.

- c. Any proposed changes to the PID shall be agreed by the Approval authority.

- d. The supplier shall identify the need for additional testing to be approved by the Approval authority.

- e. The PID, the summary table and the relevant applicable documents shall be re-issued and agreed by the Approval authority.

# **Preparatory conditions**

6.1 Calibration

Records of tool calibration and verification shall be maintained.

# 6.2 Facility cleanliness

ECSS-Q-70-08A, subclause 5.1 shall apply.

# 6.3 Environmental conditions

ECSS-Q-70-08A, subclause 5.2 shall apply.

# 6.4 Precautions against static charges

ECSS-Q-70-08A, subclause 5.3 shall apply.

# 6.5 Lighting requirements

ECSS-Q-70-08A, subclause 5.4 shall apply.

# 6.6 Equipment and tools

#### 6.6.1 Brushes

ECSS-Q-70-08A, subclause 5.5.1 shall apply.

#### 6.6.2 Pliers

ECSS-Q-70-08A, subclause 5.5.2 shall apply.

#### 6.6.3 Bending tools

ECSS-Q-70-08A, subclause 5.5.4 shall apply.

## 6.6.4 Clinching tools

$\rm ECSS-Q\mathchar`-Q\mathchar`-Q\mathchar`-0.08A,$  subclause 5.5.5 shall apply.

## 6.6.5 Insulation strippers

$\rm ECSS-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\mathchar`-Q\$

# 6.6.6 Soldering tools

ECSS-Q-70-08A, subclause 5.5.9 shall apply.

#### 6.6.7 Soldering irons and resistance soldering equipment

- a. ECSS-Q-70-08A, subclause 5.5.7 shall apply.

- b. For surface mounted devices, the soldering tip shall not exceed 340  $^{\circ}$ C.

- NOTE Based on the component manufacturer's recommendations, solder iron can be substituted by applying, for instance, hot air in order to avoid thermal shock.

#### 6.6.8 Non-contact heat sources

ECSS-Q-70-08A, subclause 5.5.8 shall apply.

#### 6.6.9 Solder pots and baths

ECSS-Q-70-08A, subclause 7.1.6 shall apply.

# 6.7 Soldering machines and equipment

# 6.7.1 General

- a. Machines and equipment used to solder surface mount devices:

- 1. leadless and leaded devices specifically designed for surface mounting,

- 2. components initially designed for insertion mounting,

shall either be a type incorporating dynamic single or dual solder wave, or be of the solder reflow type.

- b. The soldering machine shall be grounded in order to avoid electrostatic discharge.

- c. The supplier shall ensure that the soldering conditions do not exceed the values given by the individual component data sheets (e.g. maximum temperature to avoid internal melting, removal of marking ink, degradation of encapsulating plastic).

- d. Temperature and time profiles for assembly shall be identified by the supplier and approved by the approval authority.

#### 6.7.2 Dynamic wave-solder machines

Dynamic soldering machines shall be of automatic type and of a design offering the following:

- a. Controllable preheating to drive off volatile solvents and to avoid thermal shock damage to the PCB and component packages.

- b. The capacity to maintain the solder temperature at the printed circuit board assembly to within 5  $^{\circ}$ C of the established bath temperature throughout the duration of any continuous soldering run when measured 3,0 mm below the surface of the wave.

- c. A wave system that limits shadowing and allows solder fillet formation.

- d. Carriers made from a material that cannot contaminate, degrade or damage the printed circuit board or substrate nor transmit vibrations or shock stress from the conveyors to a degree permitting physical, functional or electrostatic damage to devices, board or substrate during transport through preheating, soldering and cooling stages.

- e. An extraction system, either integral or separate, conforming to the requirements of subclauses 6.2 and 6.3.

## 6.7.3 Condensation (vapour phase) reflow machines

Condensation reflow machines shall conform to the following requirements:

- a. Not transmit a movement or vibration into the assemblies being soldered that result in misalignment of parts or disturbed solder joints.

- b. Be capable of preheating an assembly with solder paste to the temperature recommended by the solder paste manufacturer prior to soldering.

- c. Use a reflow fluid whose boiling point is a minimum of 12  $\,^{\rm o}{\rm C}$  above the melting point of the solder being used.

- d. Maintain the preselected temperature to within  $\pm 5$  °C in the reflow zone during soldering.

- e. Include an extraction system that conforms to subclauses 6.2 and 6.3.

## 6.7.4 Hot gas reflow machines

Hot gas reflow machines shall conform to the following requirements:

- a. Does not transmit movement or vibration to the assemblies being soldered which result in misalignment of parts or disturbed solder joints.

- b. Preheats an assembly with solder paste to the temperature recommended by the solder paste manufacturer prior to soldering.

- c. Heats the area of the assembly to be soldered to a preselected temperature between 220  $^{\rm o}{\rm C}$  and 250  $^{\rm o}{\rm C}$  as measured on the substrate surface.

- d. Prevents the reflow of adjacent components.

- e. Maintains the preselected reflow temperature within  $\pm 5~^{\rm o}{\rm C}$  as measured at the substrate surface.

# 6.7.5 Shorted bar and parallel gap resistance reflow machines

Resistance reflow machines shall be of a design such that the system meets the following requirements:

- a. Does not impart mechanical damage to the component leads.

- b. Provides "time at temperature" control type of power supply.

- c. Maintains the shorted bar or component lead to a preselected temperature that is a minimum of  $12 \, {}^{\circ}\text{C}$  above the melting point of the solder being used.

- d. Maintains the dwell time at temperature to within 5 % of the preset value.

- e. Provides a repeatable down force to within 15 % of the preset value.

- f. Provides a system (e.g. an optical feature) to ensure that the shorted bar or electrode alignment with the component lead foot is within 20 % of the nominal lead foot length.

#### 6.7.6 Convection and radiation reflow systems

Convection and radiation reflow machines shall be of design such that the system meets the following requirements:

- a. Provides a controlled temperature profile and does not transmit movement or vibration into the assembly being soldered.

- b. Preheats an assembly with solder paste to the temperature recommended by the solder paste manufacturer prior to soldering.

- c. Heats the area of the assembly to be soldered using focused or unfocussed energy, to a preselected temperature that is a minimum of  $12 \,^{\circ}C$  above the melting point of the solder being used as measured at laminate or substrate surface.

d. Maintains the preselected temperature to within 6  $^{\rm o}{\rm C}$  in the reflow zone during soldering.

# 6.7.7 Other equipment for reflow soldering

Other solder reflow systems can be approved for use by the Approval authority. This approval shall be subject to compliance with subclauses 6.7.1 to 6.7.6.

# 6.8 Ancillary equipment

## 6.8.1 General

$Equipment \ shall \ not \ generate, \ induce \ or \ transmit \ electrostatic \ charges \ to \ devices \ being \ placed.$

## 6.8.2 Solder deposition equipment

- a. Equipment used to deposit solder pastes shall be of a screening, stencilling, dispensing, roller coating or dotting type.

- b. Equipment shall apply pastes of a viscosity and quantity such that the positioned device is retained on the board before and during soldering operations, ensuring self-centring and solder fillet formation.

- c. Equipment used to apply solder preforms shall ensure alignment of the preform with the land or device lead and termination.

# 6.8.3 Automatic device placement equipment

- a. Automatic or computer controlled equipment used for device placement shall be of the coordinate-driven pick-and-place type or of the robotic type.

- b. The placement equipment used shall be of a type that:

- 1. prevents device or board damages

- 2. indexes devices with respect to the circuit

- 3. aligns the device leads or castellations with the board terminal areas.

# 6.8.4 Cleaning equipment and systems

ECSS-Q-70-08A, subclauses 11.1 and 11.2 shall apply.

#### 6.8.5 Cleanliness testing equipment

ECSS-Q-70-08A, subclause 11.3.1 shall apply.

#### 6.8.6 Magnification aids

Subclause 13.1 shall apply.

#### 6.8.7 X-ray inspection equipment

- a. X-ray inspection shall not damage the components.

- b. X-ray equipment shall be calibrated in order to evaluate the total dose received by the components during the inspection.

- NOTE In order to minimize the dose given to the component, it is good practice to:

- Record the total dose received.

- Use off-line image analysis as much as possible.

- Use filters, optimizing the direction of the X-ray beam and masking sensitive areas.

- c. The resolution of the X-ray equipment shall be able to detect solder balls having a diameter of 0,03 mm.

d. The sensitivity shall be demonstrated by means of actual 0,03 mm diameter solder balls, stuck to adhesive tape, attached to the multilayer board assembly being inspected.

NOTE For guidelines, see C.4.3 and E.1 for X-ray inspection.

#### 6.8.8 Metallographic equipment

The metallographic equipment shall enable mounting, cross-sectioning and polishing of the solder interconnections.

(This page is intentionally left blank)

# Material selection

# 7.1 General

Material selection shall be performed in accordance with ECSS-Q-70-71.

# 7.2 Solder

# 7.2.1 Form

- a. Solder paste, ribbon, wire and preforms shall be used provided that the alloy and flux meet the requirements in subclause 7.2.2.

- b. Alloy for use in solder baths shall be supplied as ingots (without flux).

# 7.2.2 Composition

- a. The solder alloy shall have a composition specified in Table 1, unless approved by the Approval authority.

- NOTE 1 See ISO 9453 for further details.

- NOTE 2 The solder alloy used depends upon the application. See Annex E.2 for Guide for choice of solder type.

#### 7.2.3 Solder paste

- a. Solder paste shall conform to the requirements of subclause 7.2.1.

- NOTE The solder ball size and flux percentage are selected depending on the process employed, i.e. screen, stencil or needle application.

- b. The metal purity shall be as specified in Table 1.

| ESA                        | Sn               | Pb     | In               | Sb    | Ag               | Bi    | Cu    | Fe    | Zn    | AI    | As    | Cd    | Other |

|----------------------------|------------------|--------|------------------|-------|------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| designation                | min % -<br>max % | max %  | min % -<br>max % | max % | min % -<br>max % | max % |

| 63 tin<br>solder           | 62,5-63,5        | remain | -                | 0,05  | -                | 0,10  | 0,05  | 0,02  | 0,001 | 0,001 | 0,03  | 0,002 | 0,08  |

| 62 tin<br>silver<br>loaded | 61,5-62,5        | remain | -                | 0,05  | 1,8-2,2          | 0,10  | 0,05  | 0,02  | 0,001 | 0,001 | 0,03  | 0,002 | 0,08  |

| 60 tin<br>solder           | 59,5-61,5        | remain | -                | 0,05  | -                | 0,10  | 0,05  | 0,02  | 0,001 | 0,001 | 0,03  | 0,002 | 0,08  |

| 96 tin<br>solder           | remain           | 0,10   | -                | 0,05  | 3,5-4,0          | 0,10  | 0,05  | 0,02  | 0,001 | 0,001 | 0,03  | 0,002 | 0,08  |

| 75 indium<br>lead          | max. 0,25        | remain | 74,0-76,0        | 0,05  | -                | 0,10  | 0,05  | 0,02  | 0,001 | 0,001 | 0,03  | 0,002 | 0,08  |

| 70 indium<br>lead          | 0,00-0,10        | remain | 69,3-70,7        | 0,05  | -                | 0,10  | 0,05  | 0,02  | 0,001 | 0,001 | 0,03  | 0,002 | 0,08  |

| 50 indium<br>lead          | 0,00-0,10        | remain | 49,5-50,5        | 0,05  | -                | 0,10  | 0,05  | 0,02  | 0,001 | 0,001 | 0,03  | 0,002 | 0,08  |

| 10 tin lead                | 9,0-10,5         | remain | -                | 0,05  | -                | 0,10  | 0,05  | 0,02  | 0,001 | 0,001 | 0,03  | 0,002 | 0,08  |

# Table 1: Chemical composition of spacecraft solders

## 7.2.4 Maintenance of paste purity

- a. When purchased premixed or mixed in house, the purity of solder paste shall be maintained.

- b. Manufacturers' instructions shall be applied for the handling and storage of containers of solder paste purchased premixed.

- c. Refrigerated solder paste shall reach room temperature before opening the container.

- d. Neither paste purchased premixed nor paste mixed in-house shall be used if the use-by date or shelf life recommended by the manufacturer of the paste or paste constituents has expired.

- e. When the solder paste's shelf life has expired (see ECSS-Q-70-22 [11]), it shall not be used unless:

- 1. relifing is performed

- 2. tests that include visual inspection and viscosity measurements (according to the manufacturer's recommendations) are passed successfully.

- f. When relifing is performed, and the material passes the specified tests, the new shelf life shall be half the initial shelf life.

- g. Tools used for removing solder paste from the container shall not contaminate the paste dispensed or that remaining within.

# 7.3 Flux

## 7.3.1 Rosin based flux

ECSS-Q-70-08A, subclause 6.2.1 shall apply.

#### 7.3.2 Corrosive acid flux

ECSS-Q-70-08A, subclause 6.2.2 shall apply.

#### 7.3.3 Flux controls for wave-soldering equipment