ESA PSS-01-606 Issue 1 July 1986

# The capability approval programme for hermetic thick-film hybrid microcircuits

Prepared by: Product Assurance Division European Space Research and Technology Centre Noordwijk, The Netherlands

european space agency / agence spatiale européenne 8-10, rue Mario-Nikis, 75738 PARIS 15, France

÷

\*

Published by ESA Publications Division, ESTEC. Printed in the Netherlands ESA Price Code: El ISSN 0379-4059 Copyright C 1986 by European Space Agency

A construction of the second

#### ABSTRACTS

This specification defines the general requirements for capability approval of a manufacturing line for Hermetic Thick Film Hybrid Microcircuits.

. •

iii

ŧ

•

.

(blank page)

Downloaded from http://www.everyspec.com

۷

ESA PSS-01-606, Issue 1 (July 1986)

# TABLE OF CONTENTS

.

| 1.     | SCOPE                                | 1  |

|--------|--------------------------------------|----|

| 2.     | GENERAL                              | 2  |

| 2.1    | Introduction                         | 2  |

| 2.2    | Applicable Documents                 | 2  |

| 2.3    | Reference Documents                  | 3  |

| 2.4    | Definitions                          | 3  |

| 2.5    | Access to Manufacturing Facilities   | 3  |

| 2.5.1  | Checklist                            | 4  |

| 2.6    | Capability Survey                    | 4  |

| 2.6.1  | Organisation and Management          | 5  |

| 2.6.2  | Assessment of Design Rules           | 5  |

| 2.7    | Product Assurance Requirements       | 5  |

| 2.7.1  | Organisation and Responsibilities    | 5  |

| 2.7.2  | Quality and Reliability Requirements | 6  |

| 2.8    | Lay-out of Facilities                | 6  |

| 2.9    | Line Survey                          | 6  |

| 2.9.1  | Production Documents                 | 7  |

| 2.9.2  | Process Flow-chart                   | 7  |

| 2.9.3  | Travelling Documents                 | 8  |

| 2.9.4  | Process Control Chart                | 8  |

| 2.9.5  | Process Documentation                | 9  |

| 2.9.6  | Traceability                         | 9  |

| 2.10   | Location of Processing Areas         | 9  |

| 2.11   | Work Areas                           | 10 |

| 2.11.1 | General Requirements                 | 10 |

| 2.11.2 | Environmental Control                | 10 |

| 2.12   | Handling of Substrat <b>es</b>       | 10 |

| 2.13   | Purity of Materials                  | 11 |

+

.

÷

•

٠

# TABLE OF CONTENTS (continued)

| 3.    | EVALUATION PHASE                               | 13 |

|-------|------------------------------------------------|----|

| 3.1   | General                                        | 13 |

| 3.2   | Evaluation Testing                             | 14 |

| 3.2.1 | Selection of Techniques                        | 14 |

| 3.2.2 | Sequence of Operations for Selection,          | 19 |

|       | Manufacture and Testing of Test Structures     |    |

| 3.2.3 | Test Structures for Evaluation                 | 19 |

| 3.2.4 | Test Structures and Applicable Test Programmes | 19 |

| 3.2.5 | Description and Lay-out of Test Substrates     | 23 |

| 3.2.6 | Evaluation Test Plans                          | 47 |

| 3.2.7 | Description of Tests                           | 54 |

| 3.2.8 | Detail Specifications of Test Structures       | 58 |

| 3.2.9 | Failure Analysis                               | 61 |

| 3.3   | Evaluation Report                              | 61 |

| 3.3.1 | Analysis of Results                            | 61 |

| 3.3.2 | Corrective Actions                             | 61 |

| 3.3.3 | Process Identification Document                | 62 |

| 3.4   | Completion of Evaluation Phase                 | 62 |

| 4.    | CAPABILITY APPROVAL TESTING PHASE              | 63 |

| 4.1   | General                                        | 63 |

| 4.2   | Process Identification Document                | 63 |

| 4.3   | Detail Specifications                          | 68 |

| 4.4   | Manufacture of Test Structures                 | 68 |

| 4.5   | Added-on Components                            | 68 |

| 4.6   | Rework                                         | 68 |

| 4.7   | Lot Production Reports                         | 68 |

| 4.8   | Test Plan                                      | 69 |

| 4.9   | Capability Approval Testing                    | 70 |

Downloaded from http://www.everyspec.com

ESA PSS-01-606, Issue 1 (July 1986)

TABLE OF CONTENTS (continued)

| 4.9.1  | Hermetic Thick Film Hybrid Microcircuits                         | 70 |

|--------|------------------------------------------------------------------|----|

| 4.9.2  | Thick Film Chip Carrier Boards                                   | 78 |

| 4.10   | Test Review                                                      | 83 |

| 4.10.1 | Data Presentation                                                | 83 |

| 4.10.2 | Failure Criteria and Classification                              | 84 |

| 4.11   | Capability Approval                                              | 86 |

| 5.     | MAINTENANCE, SUSPENSION AND WITHDRAWAL OF<br>CAPABILITY APPROVAL | 87 |

| 5.1    | Maintenance of Capability Approval                               | 87 |

| 5.2    | Suspension of Capability Approval                                | 88 |

| 5.3    | Withdrawal of Capability Approval                                | 88 |

| Table 1 - Environmental Requirements                    | 12 |

|---------------------------------------------------------|----|

| Table 2 - Main Techniques                               | 16 |

| Table 3 - Mountings and Encapsulation                   | 16 |

| Table 4 - Permitted Combinations of Main Techniques and | 17 |

| Mounting or Encapsulation Methods for Definition        |    |

| of Test Structures                                      |    |

| Table 5 - Subtechniques                                 | 18 |

| Table 6 - Test Substrates and Procedures                | 20 |

\_\_\_\_

vii

:

.

•

# TABLE OF CONTENTS (Continued)

| Table | 7  | - | Type Designations and Numbers of Test Structures to be manufactured and Applicable Test Plans | 21 |

|-------|----|---|-----------------------------------------------------------------------------------------------|----|

| Table | 8  | - | Test Procedures                                                                               | 55 |

| Table | 9  | - | Example of PID - Section 10 Information                                                       | 67 |

| Table | 10 | - | Number of test structures for capability Approval                                             | 70 |

|       |    |   | (Hermetic Hybrids)                                                                            |    |

| Table | 11 | - | Test Methods for Hermetic Hybrids                                                             | 75 |

| Table | 12 | - | Test Methods for CCB's                                                                        | 81 |

|       |    |   |                                                                                               |    |

| Figure 1 | -   | Test Structure 'A', General Purpose Hybrid           | 24 |

|----------|-----|------------------------------------------------------|----|

|          |     | Technique                                            |    |

| Figure 2 | *** | General Lay-out of Pattern for Test Structure        | 30 |

|          |     | B1 - Multilayer Printing                             |    |

| Figure 3 | -   | Definition of Test Structure B1 Areas                | 31 |

| Figure 4 | -   | Line and Resistor Dimensions for Test Structure B1   | 32 |

| Figure 5 | -   | Details of Area 1 - Metallized Areas of Test         | 33 |

|          |     | Structure B1                                         |    |

| Figure 6 | -   | Details of Area 2 - Serially Connected Feed-throughs | 34 |

|          |     | of Test Structure B1                                 |    |

| Figure 7 | -   | Details of Area 3 - Feed-throughs over Each Other -  | 35 |

|          |     | Test Structure B1                                    |    |

| Figure 8 | -   | Details of Area 4 - Resistors on Top Layer - Test    | 36 |

|          |     | Structure B1                                         |    |

•

TABLE OF CONTENTS (Continued)

| Figure | 9-1 | - | Test Structure B2 - Multilayer Component Attachment | 39 |

|--------|-----|---|-----------------------------------------------------|----|

| Figure | 9-2 | - | Test Structure B2 - Example of Lay-out              | 40 |

| Figure | 10  | - | Test Structure C1 - High Power and High Current     | 43 |

|        |     |   | Circuits                                            |    |

| Figure | 11  | - | Test Structure D1 - High Voltage Hybrid Circuits    | 46 |

| Figure | 12  | - | Test Plan 1                                         | 48 |

| Figure | 13  | - | Test Plan 2                                         | 49 |

| Figure | 14  | - | Test Plan 3                                         | 50 |

| Figure | 15  | - | Test Plan 4                                         | 51 |

| Figure | 16  | - | Test Plan 5                                         | 52 |

| Figure | 17  | - | Test Plan 6                                         | 53 |

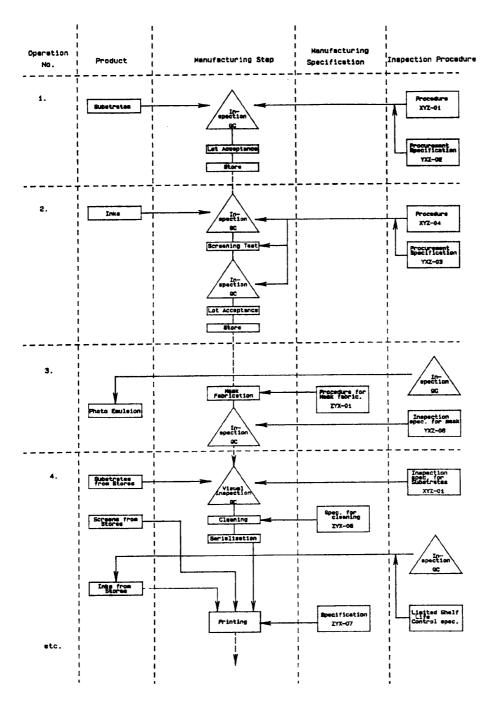

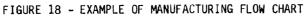

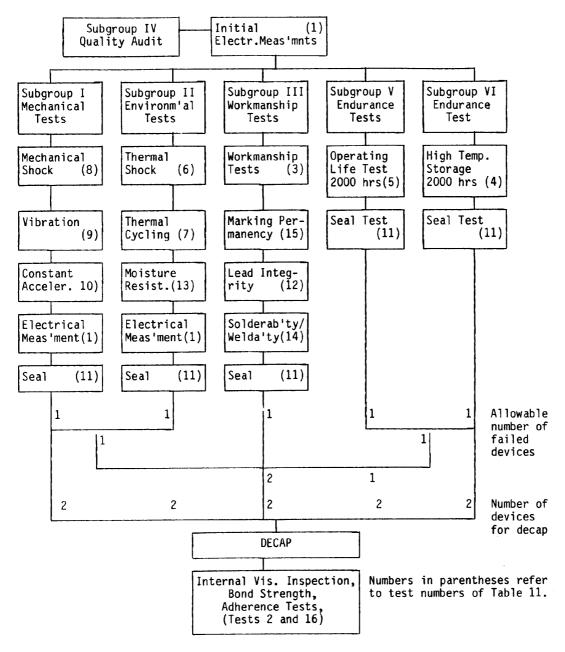

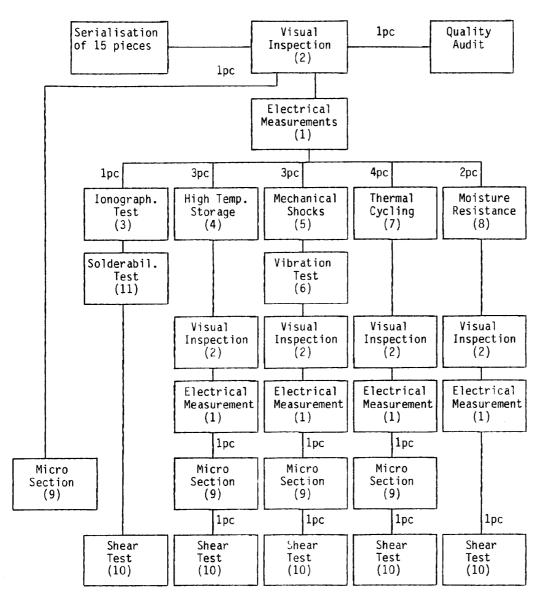

| Figure | 18  | - | Example of Manufacturing Flow-chart                 | 64 |

| Figure | 19  | - | Test Plan for Hermetic Hybrids                      | 71 |

| Figure | 20  | - | Test Plan for CCB's                                 | 80 |

|        |     |   |                                                     |    |

ANNEX A - Definitions

89

•.

---

ï

•

.

(blank page)

х

1

#### 1. SCOPE

This specification defines the general requirements for capability approval of a manufacturing line for Hermetic Thick Film Hybrid Microcircuits. For procurement requirements, see ESA PSS-01-608.

ESA approval mandate will be exercised upon conclusion of the Evaluation Phase and at the end of the programme.

Before the Evaluation Phase can commence, the manufacturer shall define the capability approval domain by specifying the processes, materials and techniques involved in the technology for which approval is sought.

### 2. GENERAL

#### 2.1 INTRODUCTION

The manufacturer shall have and implement a quality and reliability programme compatible with this specification. The review of this programme by ESA is part of the capability approval.

The manufacturer shall be responsible for the performance of tests and inspections required by this specification. All of these tests and inspections shall be performed at the plant of the manufacturer and approved by the manufacturer's Quality Assurance organisation. The use of external facilities and/or services is subject to prior ESA approval.

ESA, or its designated representative, reserves the right to participate in, or execute, survey, audits, reviews and source inspections as well as to witness any tests and to have resident or temporary personnel at the manufacturer's plant during the programme period. Participation by ESA, or its designated representative, in any approval activities shall never be considered as substitution for, or release from, the manufacturer's responsibilities.

The manufacturer shall grant personnel of ESA, and/or of its designated representative, free access to any documentation, hardware and facilities listed in the Process Identification Document (PID).

#### 2.2 APPLICABLE DOCUMENTS

The following documents are applicable to the extent specified herein.

ESA PSS-01- 60 Component Selection, Procurement and Control for ESA Spacecraft and Associated Equipment.

| ESA PSS-01- 70  | Materials and Process Selection and Quality Control |

|-----------------|-----------------------------------------------------|

|                 | for ESA Spacecraft and Associated Equipment,        |

| ESA PSS-01-201  | Contamination and Cleanliness Control,              |

| ESA PSS-01-608, | Generic Specification for Hybrid Microcircuits,     |

| ESA PSS-01-702, | A Thermal Vacuum Test for the Screening of Space    |

|                 | Materials,                                          |

| ESA PSS-01-708, | The Manual Soldering of High Reliability            |

|                 | Electrical Connections,                             |

| ESA PSS-01-716, | The Listing and Approval Procedure for Materials    |

|                 | and Processes,                                      |

| ESA PSS-01-722, | The Control of Limited Life Materials,              |

| MIL-STD-202,    | Test Methods for Electronic and Electrical          |

|                 | Component Parts,                                    |

| MIL-STD-883,    | Test Methods and Procedures for Microelectronics,   |

| MIL-STD-38510,  | Microcircuits, General Specification for,           |

| QRC-06C,        | Checklist for Thick Film Hybrid Microcircuit        |

|                 | Manufacturers and Line Survey.                      |

2.3 REFERENCE DOCUMENTS

ESA PSS-01-610, Design Guidelines for Thick Film Hybrid Microcircuits.

#### 2.4 DEFINITIONS

The definitions listed in Annex A shall apply.

# 2.5 ACCESS TO MANUFACTURING FACILITIES

·······

To enable the survey team of ESA, or its delegated representative, to carry out the capability survey and line survey, the manufacturer shall grant free access to the facilities concerned. He shall also enable the team to witness any development, engineering, production and quality assurance operations involved in the processes for which approval is sought. 4

ESA PSS-01-606, Issue 1 (July 1986)

#### 2.5.1 Checklist

To facilitate the evaluation procedure, ESA will apply Checklist ESA QRC-06C.

#### 2.6 CAPABILITY SURVEY

The purpose of this survey is to assess the following aspects of the manufacturer's organisation:

- General organisation and management,

- Quality and Reliability Assurance organisation, including definition of authority and effectiveness,

- Facilities and capabilities of the plant in which the thick film hybrid microcircuits will be manufactured and tested,

- Nonconformance control.

Before and/or during the actual survey, the manufacturer shall provide ESA with any documentation which may assist the survey team in the execution of its tasks. As a minimum, this documentation shall include:

- An organigram delineating authority, responsibility and interrelationship between Engineering, Production, Quality and Reliability Assurance, Procurement and Management;

- Expertise of all key personnel employed in the Production and Product Assurance Departments;

- A list of contracts with ESA and/or national space agencies for component evaluation and qualification;

- The name(s) and location(s) of any other plant(s) of the manufacturer where electronic parts are produced according to the same, or a similar, technology as applied to the hybrid microcircuits for which qualification is sought;

- A flow-chart and any available procedures relative to the processes and controls applied in the production of the devices to be evaluated and approved.

5

#### 2.6.1 Organisation and Management

The manufacturer shall clearly define his policy on:

- Authority and responsibility of Quality and Reliability management vis-à-vis general management;

- Support requested by the Research and Development Department from Engineering and/or Quality Assurance personnel;

- Employee motiviation (bonus scheme, incentives, operator training and certification, etc.).

#### 2.6.2 Assessment of Design Rules

For assessment of the design of the Hermetic Thick Film Hybrid Microcircuits, the manufacturer shall provide ESA with the design rules he proposes to apply. General design guidelines are given in ESA PSS-01-610.

2.7 PRODUCT ASSURANCE REQUIREMENTS

#### 2.7.1 Organisation and Responsibilities

The manufacturer shall have an effective Quality and Reliability organisation, suitable facilities and competent Product Assurance personnel with a sufficient degree of independence from the company's design and manufacturing functions to deal objectively with the Product Assurance aspects of the hybrid microcircuits in compliance with the applicable ESA documents.

The Quality and Reliability organisation shall have direct and unimpeded access to higher management, to which it shall report regularly on the status and adequacy of the programme.

The Quality Assurance organisation shall be responsible for the implementation of all requirements of this specification and the execution

of this programme to the satisfaction of the customer. He shall present to the customer only those items/documents which he determines to be in full compliance with those requirements of this and all applicable specifications listed that concern the customer.

#### 2.7.2 Quality and Reliability Requirements

The manufacturer shall establish and implement a Quality and Reliability programme which fully complies with all of the applicable ESA PSS specifications. Special attention shall be paid to:

- Training of operators/inspectors,

- Definition of workmanship standards,

- Reliability engineering activities,

- Configuration Control,

- Quality Assurance activities according to PSS-01-20,

- Materials and Process selection according to PSS-01-70 and PSS-01-716.

### 2.8 LAY-OUT OF FACILITIES

The manufacturer shall provide ESA with the lay-out of the facilities to be surveyed, showing the location of each production area, the cleanliness standards and dust count frequency applicable to each area and operation, and including a list of equipment, specifying its accuracy and calibration frequency.

#### 2.9 LINE SURVEY

During this survey, which will comprise all aspects of the production line, special attention will be paid to those processes, process steps, materials, piece parts and controls that are involved in the manufacture of the devices concerned. The manufacturer shall demonstrate to ESA the methods evolved on the basis of in-house experience for investigation and optimisation of all processes for which approval is sought.

6

7

For the purpose of this survey, the subject test structures will be divided according to the major processes performed in the three main production areas of a hybrid microcircuit manufacturing facility, viz.:

#### a) Thick Film Network

This is often called the pure thick film circuit and requires basically the print and fire technique, resistor trimming, without additions or encapsulation;

#### b) Thick Film Hybrid Assembly

This involves the adding on of chips or other circuits and their connection to the substrate;

#### c) Encapsulation or Mounting of Microcircuit

This involves the encapsulation of the substrate or its mounting onto a base-plate or similar structure.

#### 2.9.1 Production Documents

All documents related to the processes for which capability approval is sought shall be made available to ESA. Any proprietary documents shall be included, but marked as such.

2.9.2 Process Flow-chart (PID)

This chart shall show the sequence of production and inspection steps. Inspections shall include each measurement, test or visual examination performed. The flow-chart shall also show:

number, issue and revision date of the specification applicable to each production and inspection step;

- department, division or section responsible for each operation involved in the processing, production and quality control;

- point at which statistical control records are applied.

The issue and revision date of the above mentioned documents may be listed separately.

2.9.3 Travelling Documents

The manufacturer shall prepare and use a travelling document for each lot. This document shall show as a minimum:

- lot identification,

- operation,

- date of each operation,

- number in/out at each operation,

- operator identification,

- nonconformance references.

2.9.4 Process Control Chart

The process control chart shall show as a minimum:

- title of relevant process,

- name or code number of station at which it is used,

- lot identification,

- dates recorded,

- number of items inspected,

- identification of equipment adjustment,

- percentage of defective devices,

- average nominal values,

- average limits.

8

Downloaded from http://www.everyspec.com

ESA PSS-01-606, Issue 1 (July 1986)

9

#### 2.9.5 Process Documentation

The manufacturer shall prepare and maintain documents for incoming inspection, production, quality assurance and process control such as specifications and procedures establishing:

- materials and piece parts,

- operations,

- equipment,

- calibration methods,

- measurements,

- tests,

- inspections,

- tolerances.

These documents and any revisions thereof shall be available at all times to operating personnel and, upon request, shown to the evaluating and qualifying authority.

#### 2.9.6 Traceability

The manufacturer shall record the manufacturing data and material history of all units processed according to this specification and maintain these records for a minimum of five years.

#### 2.10 LOCATION OF PROCESSING AREAS

The manufacturer shall specify the location where each of the key processing steps is performed. The evaluating authority shall be notified of any changes in these locations to determine if re-evaluation is required.

2.11 WORK AREAS

2.11.1 General Requirements

The devices concerned shall be produced in a controlled area. This implies that:

- only authorized personnel shall have access to such area and that within such area:

- personnel shall wear protective clothing,

- smoking, drinking and eating shall be prohibited,

- housekeeping shall be according to a written schedule,

- equipment shall be compatible with the cleanliness standard required in the controlled area.

2.11.2 Environmental Control

The manufacturer shall specify for each process step:

- relative humidity,

- temperature,

- particle count.

He shall demonstrate the manner in which these conditions are controlled taking into account the relevant requirements defined in Table 1 and Specification ESA PSS-01-201.

2.12 HANDLING OF SUBSTRATES

The manufacturer shall furnish evidence that adequate provisions are in force for the careful handling and storage of substrates throughout production cycle. Any damage to substrates shall be recorded together with details of the station and/or stage of operation at which the damage occurred.

11

#### 2.13 PURITY OF MATERIALS

The manufacturer shall keep records to verify that the materials used in production are of a consistent purity level and meet the application requirements.

# ESA PSS-01-606 Issue 1 (July 1986

÷

÷

#### TABLE 1 - ENVIRONMENTAL REQUIREMENTS

| Process Step                                                                  | Cleanliness<br>Class               | Humidity<br>(% RH)                 | Temperature<br>(°C)                |  |

|-------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|--|

| Wet photoresist processes<br>for mask work, etc.                              | 10 000                             | To be specified<br>by manufacturer | To be specified<br>by manufacturer |  |

| Areas where wet printing paste work is performed                              | 10 000                             | 50 ± 5                             | 25 +0<br>-5                        |  |

| Areas where firing and<br>soldering work is per-<br>formed                    | 100 000                            | 50 ± 5                             | To be specified<br>by manufacturer |  |

| Semiconductor chip mount-<br>ing work and wire-bonding<br>manufacturer        | 10 000                             | 50 ± 5                             | To be specified<br>by manufacturer |  |

| Mounting of encapsulated<br>components on ceramic<br>substrates               | To be specified<br>by manufacturer | To be specified<br>by manufacturer | To be specified<br>by manufacturer |  |

| Precap visual inspection and final sealing areas                              | 100                                | 50 ± 5                             | To be specified by manufacturer    |  |

| Cleaning of "open" circuit<br>types and packaging into<br>sealed plastic bags | 10 000                             | 50 ± 5                             | To be specified<br>by manufacturer |  |

| Other process steps                                                           | To be specified<br>by manufacturer | To be specified<br>by manufacturer | To be specified<br>by manufacturer |  |

Temperature and humidity shall be controlled and continuously recorded. Cleanliness class shall be checked regularly during production.

13

3 EVALUATION PHASE

#### 3.1 GENERAL

The Evaluation Phase shall consist of:

#### a) Capability Survey

This survey is made to assess a manufacturer's general capability in the production of reliable circuits.

#### b) Line Survey

This survey consists of an analysis of a manufacturer's technology and production line based on applied processes and controls and a detailed study of all available test data for the identification of critical processes and controls.

#### c) Evaluation Testing

This involves respectively the selection, production and testing of test structures for determination of their stress limits and weaknesses.

#### d) Corrective Actions

If, as a result of evaluation testing, the test structures show weaknesses or deficiencies, the manufacturer shall take any corrective actions required by ESA.

#### e) ESA Approved Capability Domain

After all required corrective actions have been implemented to the full satisfaction of ESA, ESA will approve the manufacturer's

capability domain as defined in the PID at the end of this phase. This approval will enable the manufacturer to start the next phase of the programme.

#### 3.2 EVALUATION TESTING

Evaluation testing shall comprise four sequential steps, viz.:

- Selection of techniques, processes and materials to be certified;

- Based on the selection specified above, manufacture of test structures or circuits;

- Testing of test structures or circuits;

- Evaluation of test results.

#### 3.2.1 Selection of Techniques

On the basis of the processes, materials and techniques proposed by the manufacturer for approval, the manufacturer shall propose the main techniques and type of encapsulation, define the test structures and draw up the test plans in accordance with the requirements of this specification.

Tables 2 and 3 show respectively the possible main techniques and encapsulation or mounting methods. Only certain combinations of main techniques and encapsulation or mounting methods shall be permitted; these are shown in Table 4 together with the type designations of the corresponding test structures.

The manufacturer shall be free to choose which of the different subtechniques applicable to a specific main technique he wishes to use. However, the lay-out and content of the corresponding test structure shall be agreed with ESA. The selection shall be made before commencing manufacture of the test structures. Table 5 lists the various subtechniques.

14

The manufacturer shall draw up a list of processes and select the raw materials, piece parts and added-on or applied materials, and ascertain their conformance to the design, quality and procurement requirements defined in this specification and ESA Specifications PSS-01-60, PSS-01-70 and PSS-01-608, as relevant. Alternatively, he shall prove their suitability for space application by other documentary evidence.

Each process step shall be chosen solely on the basis of the materials, techniques and controls applied at the time of evaluation. A preliminary Process Identification Document (PID) shall be prepared for the processes and procedure to be applied. The PID shall list all constituent materials and piece parts.

The manufacturer shall ensure that all materials and processes for which certification is sought are adequately covered by the programme. Prior to its implementation, this programme shall be submitted to ESA for approval.

ł

,

÷

.

TABLE 2 - MAIN TECHNIQUES

| A | General purpose hybrid circuits in 1- or 2-layer technique.<br>Power dissipation: 0.2 W or less per cm <sup>2</sup> substrate.<br>Terminal current : 1 A or less                                                                |  |  |  |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| В | B Multilayer hybrid circuits with 3 or more conductor layers.<br>Power dissipation: 0.2 W or less per cm <sup>2</sup> substrate.<br>Terminal current 1 A or less                                                                |  |  |  |  |

| C | High-power and high-current hybrid circuits for power-supply<br>and power-conditioning circuits etc., with continuous power<br>dissipation more than 0.2 W per cm <sup>2</sup> substrate or terminal<br>currents more than 1 A. |  |  |  |  |

| D | High-voltage hybrid circuits, voltage dividers etc. for<br>more than 1000 V.                                                                                                                                                    |  |  |  |  |

# TABLE 3 - MOUNTINGS AND ENCAPSULATION

| Q | Unencapsulated and unmounted substrates                            |  |  |  |  |

|---|--------------------------------------------------------------------|--|--|--|--|

| R | Substrate mounted on simple metal-plate structure                  |  |  |  |  |

| S | Substrate mounted in hermetically sealed low-power metal package   |  |  |  |  |

| γ | Substrate mounted in hermetically sealed low-power ceramic package |  |  |  |  |

| U | Substrate mounted in hermetically sealed high-power metal package  |  |  |  |  |

17

# TABLE 4 - PERMITTED COMBINATIONS OF MAIN TECHNIQUES AND MOUNTING OR ENCAPSULATION METHODS FOR DEFINITION OF TEST STRUCTURES

| Main      | Mounting or Encapsulation |             |                |                |                |

|-----------|---------------------------|-------------|----------------|----------------|----------------|

| Technique | Q                         | R           | S              | Т              | U              |

| A         | QA1                       | RA1         | SA1            | TA1            | Not applicable |

| В         | QB1 and QB2               | RB1 and RB2 | SB1 and SB2    | TB1 and TB2    | Not applicable |

| С         | Not applicable            | RC1         | Not applicable | Not applicable | UC1            |

| D         | QD1                       | RD1         | Not applicable | TD1            | Not applicable |

Example

SA1 is a type A1 test substrate (covering general-purpose low-power hybrid circuitry) mounted in a hermetically sealed low-power metal package.

Definition of Main Techniques: See Table 2.

Definition of Mounting and Encapsulation Methods Q to U: See Table 3.

Definition of Test Substrates A1 to D1: See Table 6.

ş

÷

TABLE 5 - SUBTECHNIQUES

| I    | 1-or 2-layer conductor                  |  |  |  |  |  |

|------|-----------------------------------------|--|--|--|--|--|

| II   | Multilayer conductor                    |  |  |  |  |  |

| III  | Printed resistors                       |  |  |  |  |  |

| IV   | Protective covering                     |  |  |  |  |  |

| ٧    | Printed capacitors                      |  |  |  |  |  |

| VI   | Cross-over by wire bonding              |  |  |  |  |  |

| VII  | Termination with wire-leads             |  |  |  |  |  |

| VIII | Mounting of encapsulated components     |  |  |  |  |  |

| IX   | Mounting of resistor or capacitor chips |  |  |  |  |  |

| X    | Mounting of chip-carriers               |  |  |  |  |  |

| XI   | Chip and wire bonding                   |  |  |  |  |  |

| XII  | Substrate mounting on metal plate       |  |  |  |  |  |

| XIII | Substrate mounting in package           |  |  |  |  |  |

19

- 3.2.2 Sequence of Operations for Selection, Manufacture and Testing of Test Structures

- The manufacturer shall propose and submit to ESA for approval those processes that he wishes to adopt.

- Joint agreement by ESA and the manufacturer on subtechniques (see Table 5).

- Joint agreement by ESA and the manufacturer on main techniques and mounting or encapsulation methods.

- Preparation by the manufacturer of the applicable documentation and lay-outs of test structures.

- Manufacture and testing of test structures, preparation of report.

ESA may require to monitor certain tests.

- Destructive Physical Analysis (DPA) of control devices by ESA or an independent test laboratory.

- 3.2.3 Test Structures for Line Evaluation

The test structures to be manufactured shall:

- be based on the processes selected,

- be such that they are representative of the technology involved,

- be in accordance with the controls, limits and constraints agreed between ESA and the manufacturer,

- meet the requirements of this specification,

- be tested for any weakness, so that restraints of the applied processes and technologies may be determined, and

- take into account any inherent criticalities.

3.2.4 Test Structures and Applicable Test Programmes

Table 6 specifies the test substrates to be used in the manufacture of the different test structures and refers to the paragraphs in which details are described.

Table 7 shows type designations and numbers of test structures to be manufactured for evaluation testing together with the applicable test plans set out in Paragraph 3.2.6.

# TABLE 6 - TEST SUBSTRATES AND PROCEDURES

| Substrate | Description                                                                                                                                                                                                                                                                                              | Para    |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| A1        | Substrate for manufacture of general-purpose low-power<br>hybrid microcircuit:-<br>- 1- or 2-layer printed conductors,<br>- printed resistors,<br>- capacitors and cross-overs,<br>- attachment of terminals,<br>- passive and active components.<br>Applicable subtechniques to be chosen from Table 5. | 3.2.5.1 |

| B1        | Substrate for multilayer printing techniques                                                                                                                                                                                                                                                             | 3.2.5.2 |

| 82        | Substrate for component attachment on multilayer circuits                                                                                                                                                                                                                                                | 3.2.5.2 |

| C1        | Substrate for high-power and high-current hybrid technique                                                                                                                                                                                                                                               | 3.2.5.3 |

| D1        | Substrate for high-voltage hybrid technique                                                                                                                                                                                                                                                              | 3.2.5.4 |

20

21

# TABLE 7 - TYPE DESIGNATIONS AND NUMBERS OF TEST STRUCTURES TO BE MANUFACTURED AND APPLICABLE TEST PLANS

| Description                                                      | Test      | No. of Pcs to   | Test Plan | Example                     |  |

|------------------------------------------------------------------|-----------|-----------------|-----------|-----------------------------|--|

| Example                                                          | Structure | be manufactured | No.       | L Xallip Te                 |  |

| General-purpose low-power<br>hybrid, unencapsulated              | QA1       | 13              | 1         |                             |  |

| General-purpose low-power<br>hybrid, on metal plate              | RA1       | 13              | 1         |                             |  |

| General-purpose low-power<br>hybrid in metal package             | SA1       | 11              | 2         | Mounting or<br>package type |  |

| .ow-power hybrid in<br>ceramic package                           | TA1       | 11              | 2         |                             |  |

| Multilayer network,<br>unencapsulated                            | QB1       | 13              | 1         | definition                  |  |

| Multilayer network with components attached                      | QB2       | 13              | 1         | see Table 3                 |  |

| Multilayer network on<br>metal plate                             | RB1       | 13              | 1         | Q A1                        |  |

| Multilayer network with<br>attached components on<br>metal plate | RB2       | 13              | 1         | Substrate<br>type           |  |

| Multilayer network in<br>metal package                           | SB1       | 11              | 2         | Definition<br>see Table 6   |  |

| Multilayer with attached<br>components in metal package          | SB2       | 11              | 2         |                             |  |

TABLE 7 continued on next page.

1

2

÷

# TABLE 7 - TYPE DESIGNATIONS AND NUMBERS OF TEST STRUCTURES TO BE MANUFACTURED AND APPLICABLE TEST PLANS (Continued)

| Description                                                          | Test      | No. of Pcs to   | Test Plan | Framalo      |  |

|----------------------------------------------------------------------|-----------|-----------------|-----------|--------------|--|

| Example                                                              | Structure | be manufactured | No.       | Example      |  |

| Multilayer network in<br>ceramic package                             | TB1       | 11              | 2         | See previous |  |

| Multilayer network with<br>attached components in<br>ceramic package | TB2       | 11              | 2         | page         |  |

| High-power hybrid on<br>metal plate                                  | RC1       | 13              | 3         |              |  |

| High-power hybrid in<br>metallic package                             | UC1       | 11              | 4         |              |  |

| High-voltage hybrid,<br>unencapsulated                               | QD1       | 13              | 5         |              |  |

| High-voltage hybrid<br>on metal plate                                | RD1       | 13              | 5         |              |  |

| High-volt <mark>age hy</mark> brid<br><sup>i</sup> n ceramic package | TD1       | 11              | 6         |              |  |

22

23

3.2.5 Description and Lay-out of Test Substrates

The following paragraphs describe the lay-out of test substrates A, B, C, D and E. As a guideline, the test structures described and illustrated in the following paragraphs have been implemented on  $25 \times 50$  mm substrates. The manufacturer may however choose different dimensions according to the technology for which capability approval is sought.

Any commercially available added-on parts required for assembly shall be as far as possible equivalent to space-qualified parts.

The manufacturer shall adhere to the specified patterns unless the technology involved requires deviation. In such case, the revised drawing of the pattern shall be submitted to ESA for approval.

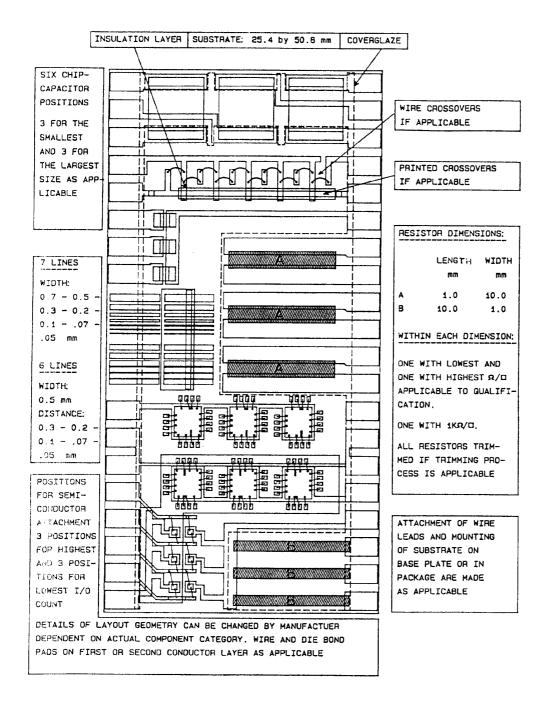

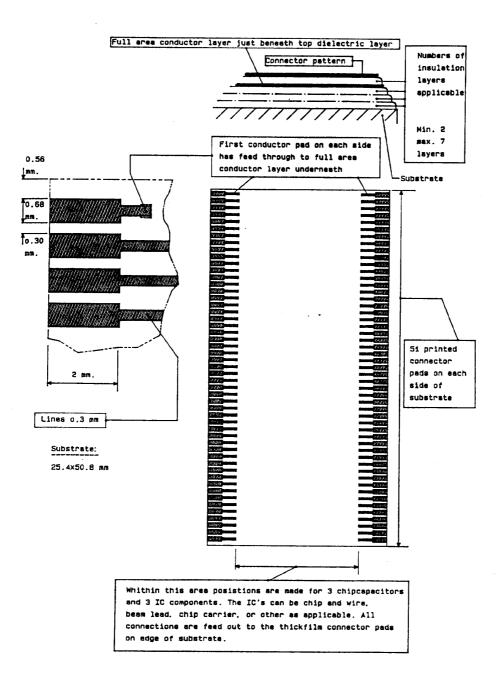

3.2.5.1 Test Structure A for Low-Power Hybrid Technique

This pattern is illustrated in Figure 1 and specifies printed resistors and conductors, a special pattern of thin lines placed closely together for evaluation of mask and printing quality, positions for attached chip capacitors and active components as well as a pattern for wire and printed crossovers.

With reference to the subtechniques listed in Table 5, only those sections of the pattern that are required shall be implemented.

FIGURE 1 - TEST STRUCTURE 'A', GENERAL PURPOSE HYBRID TECHNIQUE

24

25

#### Rules for Endurance Testing

For evaluation purposes, the following rules shall be applied when subjecting Test Structure 'A' to Test No. 5, "Endurance Testing" of Table 8

# Thick Film Resistors

'A' Resistors: 0.25 W, maximum 20 V d.c.;

'B' Resistors: 0.25 W, maximum 250 V d.c.,

Load Cycle : 90 minutes on; 30 minutes off.

#### Semiconductors

No load.

#### Chip Capacitors

No load.

#### Printed Capacitors and Cross-overs

100 V d.c., continuous.

Depending on the technology, the substrate may be mounted or unmounted, on a base-plate or in a package.

If applicable, solder leads may be used.

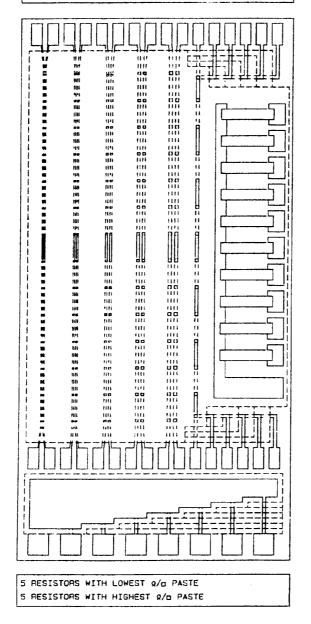

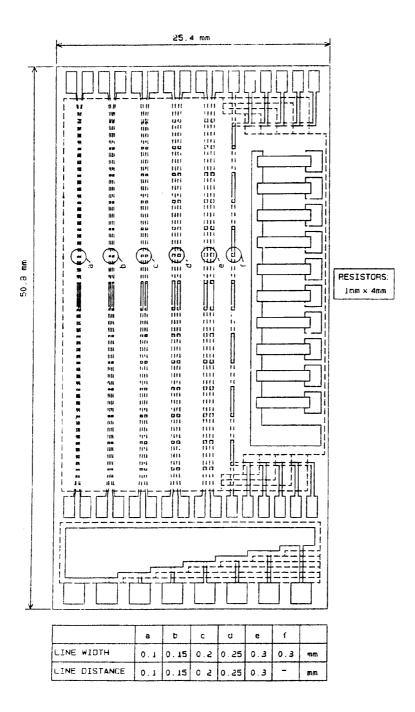

3.2.5.2 Test Structures 'B1' and 'B2' - Multilayer Printing Technique and Component Attachment to Multilayer Circuits

Patterns are illustrated in Figures 2 to 9 inclusive.

#### a) Test Pattern 'B1' covering Printing Technique

#### Test Philosophy

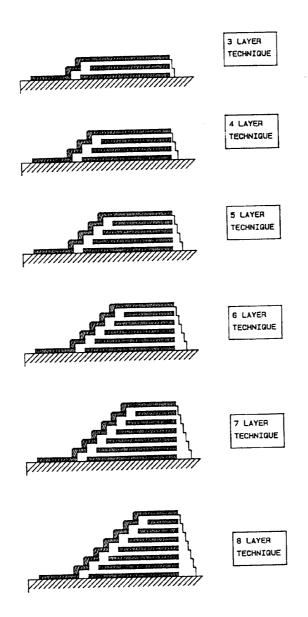

The test pattern covers the range of 0.1 to 0.3 mm line widths and distances in combination with a number of conductive layers which may vary between 3 and 8. Before evaluation and capability approval, the manufacturer shall select the number of conductor layers and prepare the test patterns accordingly.

The permitted minimum line width and distance cannot be chosen in advance. The graduated set of lines of the test pattern decreases in width and distance and only the test result will prove the minimum width of the lines which can be achieved by the manufacturer.

Approval is usually granted for the larger line width following the one which passed the printing test without failures.

#### Line Widths

Generally, line widths and distances less than 0.1 mm are not considered suitable for high reliability space application. Although even 0.1 mm is close to the allowable limit, this width has been included because it will provide evidence of possible limitations of the manufacturer's printing technique. The upper limit of 0.3 mm is considered to be the minimum requirement to be met by a process line intended for the production of multilayer hybrids.

27

#### Number of Layers

Also covered by the test pattern are 3 to 8 conductive layers, 1- and 2-layer circuits being covered by type 'A' patterns. In view of the present state of the art, circuits with more than 8 layers are not considered suitable for space application.

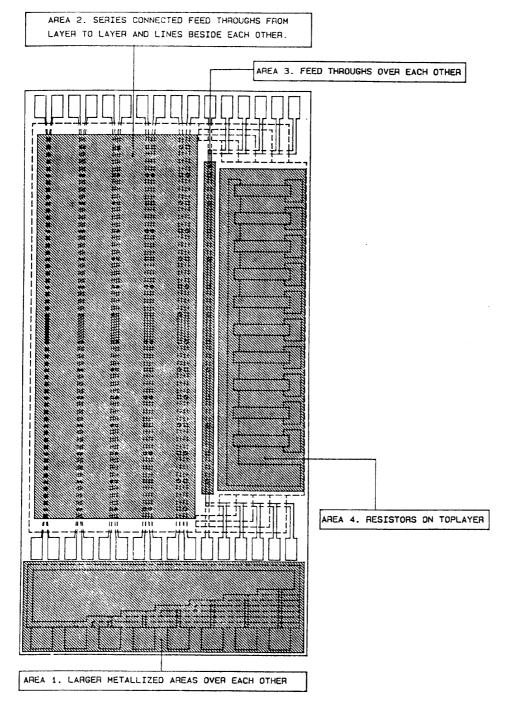

#### Printing Alignment

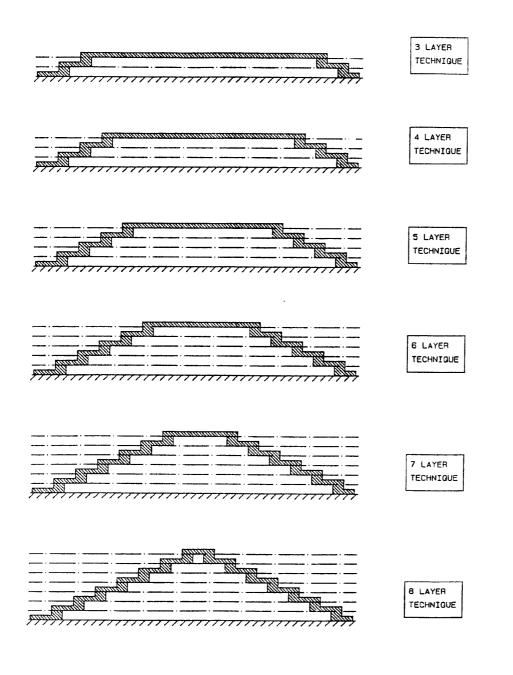

Printing alignment often creates a problem when feed-throughs have to be made linking the lines of several independent layers, especially when the lines are thin. This problem is reflected by Figure 6, area 2 of Figure 3, showing pairs of lines with decreasing widths running across all layers from bottom to top and back again.

#### Printing Irregularities Around Feed-throughs

The frequent occurrence of printing irregularities around feedthroughs is due to small misalignments and the differences in thickness of dielectric layers and fill-up dots of conductors.

A similar printing problem may arise when lines and feed-throughs are positioned on top of each other over several layers (see area 3 of Figures 3 and 7).

As the positioning of several feed-throughs directly on top of each other is not only very difficult, but also considered to be bad design practice, the test pattern specifies broken feedthrough lines alternating with straight lines from layer to layer.

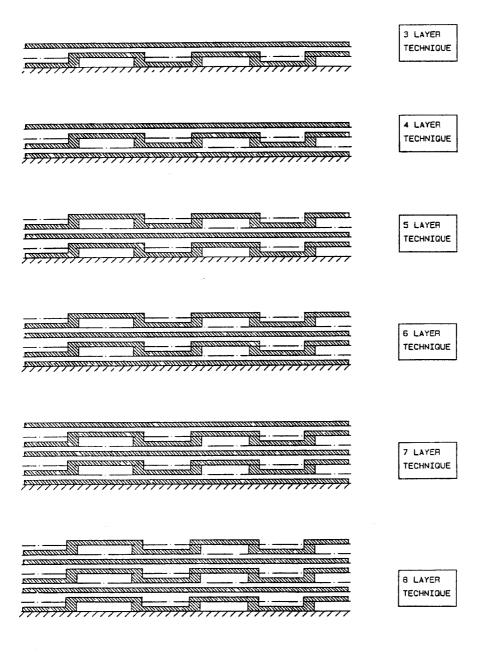

#### Pinholes and Insulation Resistance

Multilayer circuits frequently fail because pinholes or contamination by conductive particles in the dielectric layers result in low dielectric strength or direct short-circuit between conductive layers. Another problem may be created by some dielectric hygroscopic pastes which must be covered by a glass passivation layer to prevent humidity absorption and reduction of insulation resistance.

Area 1 of Figure 3 and Figure 5 shows how both problems are solved by printing successive metallised areas one over the other.

Lines over Steps

The printing of lines over successive steps is normally avoided and, especially where thinner lines are required, it is good design practice to keep the line at one single level. However, in special cases, wider lines running over steps of insulation layer may be necessary (see Area 1 of Fig. 3 and Fig. 5).

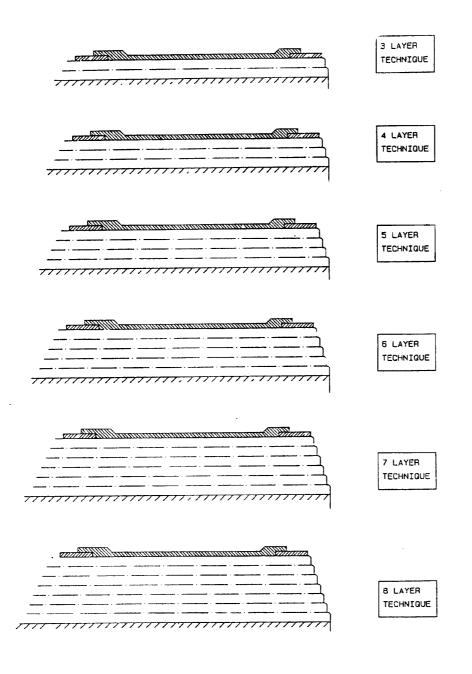

#### Resistors

Although multilayer hybrids are frequently pure connection patterns for digital integrated circuit chips, some printed resistors may be required. As shown in Figures 3 and 4, these are usually placed on top of the circuit (Area 4).

Five resistors are made using the lowest, and five using the highest, /square paste to be tested. No trimming is permitted of resistors printed on dielectric.

#### Direction of Printing

Alignment around feed-throughs is often made difficult by stretch in the printing masks as a result of friction during printing. This problem becomes even more complicated when printing is performed <u>perpendicularly</u> to very thin line systems. Unfortunately, it is practically impossible for all printing to run parallel to the lines of a system because some will always be perpendicular to others or at

28

29

least at an angle of 45°, depending on the printing technique. For this reason, it is a mandatory requirement that THE DIRECTION OF PRINTING (IN WHICH SQUEEGEE RUNS) SHALL ALWAYS BE PERPENDICULAR TO, OR AT A 45° ANGLE WITH, THE LENGTH OF THE TEST PATTERN

# Packaging

Depending on the mounting or encapsulation method, test structures may be mounted on a base-plate, unmounted or encapsulated in hermetically sealed packages.

2

THE PATTERN CAN BE COVERED BY A COVER GLAZE LAYER IF APPLICABLE

FIGURE 2 - GENERAL LAY-OUT OF PATTERN FOR TEST STRUCTURE B1 - MULTILAYER PRINTING

FIGURE 4 - LINE AND RESISTOR DIMENSIONS FOR TEST STRUCTURE B1

# FIGURE 5 - DETAILS OF AREA 1 - METALLISED AREAS OF TEST STRUCTURE B1

# FIGURE 6 - DETAILS OF AREA 2 - SERIALLY CONNECTED FEED-THROUGHS OF TEST STRUCTURE B1

35

FIGURE 7 - DETAILS OF AREA 3 - FEED-THROUGHS OVER EACH OTHER -TEST STRUCTURE B1

FIGURE 8 - DETAILS OF AREA 4 - RESISTORS ON TOP LAYER - TEST STRUCTURE B1

37

## Endurance Testing

For evaluation of Test Structure B1, the following rules shall be applicable to Test 5, "Endurance Testing" specified in Table 8 and Para 3.2.6:

•

#### Thick Film Resistors

0.1 W, maximum 100 V d.c. Load cycle: 90 minutes on, 30 minutes off.

## Area 1 - Large Metallised Areas

100 V d.c. continuous over each insulation layer.

## Area 2 - Serially Connected Feed-throughs

100 V d.c. continuous between each pair of lines.

# Area 3 - Feed-throughs over each other

100 V d.c. continuous over each insulation layer.

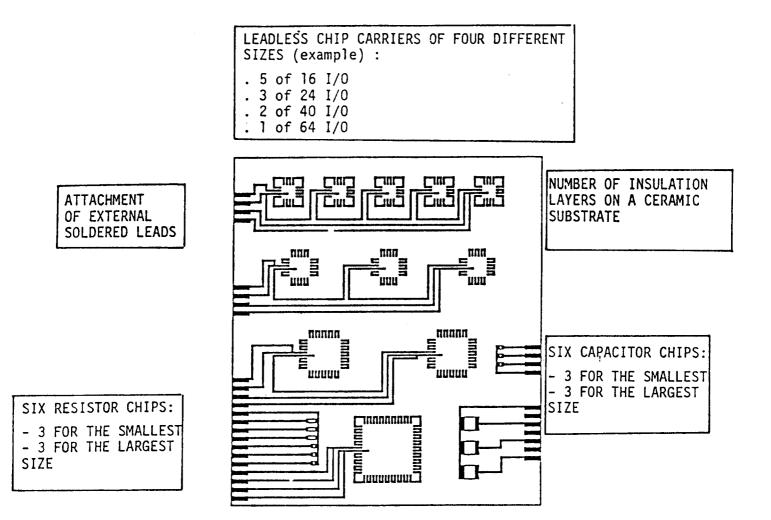

# b) Test Structure B2, covering Component Attachment

A generic lay-out of the pattern is given in Fig. 9.1. The manufacturer shall design the lay-out applicable to his own technology. The following suggestions are to be considered as an example.

Substrate : 25.4 x 50.8 mm.

#### Components:

The components which can be attached to the thick-film network are usually of the following types:

- Active chips eutectically or epoxy-bonded directly to the substrate;

- Active chips as above, but attached to an open carrier (ceramic or molytab);

- Passive chips (capacitors or resistors) glued, soldered or wirebonded to the substrate;

- Chip-carriers (leadless or leaded).

As a general rule, some components of both the smallest and largest size of each type shall be attached. If there is not enough space to accommodate all of the component types, they may be distributed over several test structures.

Figure 9.2 shows an example of a detailed lay-out of test pattern B2.

38

FIGURE 9-1 - TEST STRUCTURE B2 - MULTILAYER COMPONENT ATTACHMENT

١

FIGURE 9-2 - TEST STRUCTURE B2 - EXAMPLE OF LAY-OUT

## Printing Layers

The chosen number of dielectric layers shall be printed over the entire substrate. The pattern for capacitor and IC mounting shall be printed on top of these dielectric layers. Immediately underneath the top dielectric layer, there shall be a conductive layer to enable dielectric testing of the overlying component attachment pattern.

#### Packaging

Depending on the mounting or encapsulation method to be qualified, the test structure may be mounted on a baseplate, unmounted or encapsulated in a hermetically sealed package. If a hermetically sealed package is used, there shall be sufficient internal connections to permit the electrical testing of the attached components.

#### Rules for Endurance Testing

For evaluation of Test Structure B2, the following rules shall be applicable to Test 5, "Endurance Testing" specified in Table 8 and Para 3.2.6.

#### Top Insulation Layer

100 V d.c. continuous between top conductor layer with all terminals connected together and conductor layer printed immediately underneath.

#### Semiconductor Components and Chip Capacitors

No electrical load.

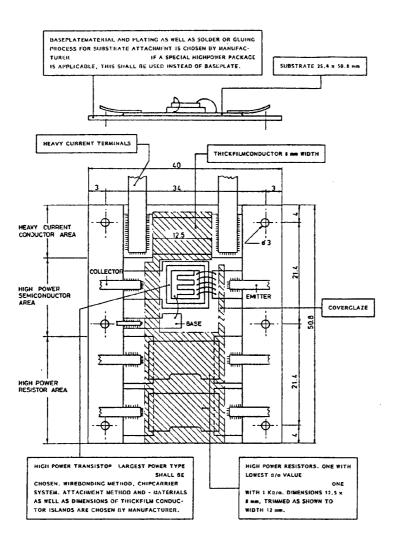

# 3.2.5.3 Test Structure C1 covering High-Power and High-Current Circuits

The relevant test pattern is shown in Figure 10 and details:

- A pair of high-power resistors, one having the lowest  $\Omega$ /square value to be qualified and the other with a non-critical mean  $\Omega$ /square value of 1 k $\Omega$ /square.

- A position for the mounting of a high-power semiconductor component and the applicable chip-carrier and connection system. The type with the highest power dissipation shall be used.

- A high-current conductor circuit consisting of a 8 x 12.5 mm conductor area with termination.

# Packaging

For non-hermetic encapsulation, the substrate shown in Figure 10 shall be mounted on a metallic baseplate.

For hermetic encapsulation, the substrate together with the applicable internal connections and feed-throughs shall be mounted in the relevant package.

FIGURE 10 - TEST STRUCTURE C1 - HIGH-POWER AND HIGH-CURRENT CIRCUITS

# Rules for Endurance Testing

For evaluation of Test Structure C1, the following rules shall be applicable to Test 5, "Endurance Testing" specified in Table 8 and Para 3.2.6.

#### Thick Film Resistors

Each resistor shall be loaded with 60 W d.c. or a.c. Load cycle: 90 minutes on, 30 minutes off.

## High Power Transistor

1.2 W d.c. per  $mm^2$  area of silicon chip.

#### Heavy Current Circuit

16 A d.c. or a.c.

#### Mounting

The test structure shall be mounted on a water-cooled heat-sink having a surface temperature of +25 °C.

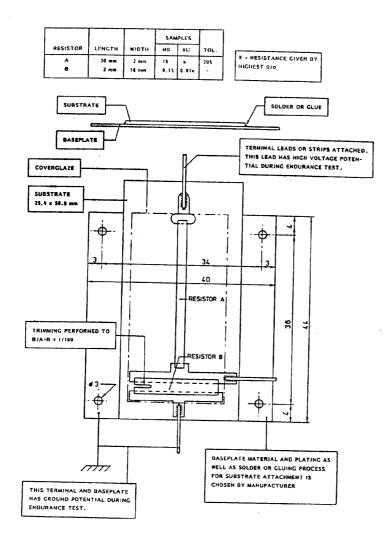

## 3.2.5.4 Test Structure D1 covering High Voltage Circuits

The reason why Figure 11 shows the test pattern of a simple voltage divider system is that the main problems of a thick film high voltage circuit are created by resistors whose stability and accuracy are affected by temperature and voltage coefficient when used in precision voltage dividers.

44

45

Two versions of the circuit shall be made: one with a resistance paste giving resistor 'A' a value of 15 M $\Omega$  and the other with the highest  $\Omega$ /square resistance paste. The voltage dividing ratio for trimming resistor 'B' shall be 100 : 1.

#### Package and Mounting Method

The substrate may be unmounted, mounted on a metal baseplate (see Figure 11) or mounted in a ceramic package with the applicable internal connection. If solder leads are used, they may be attached as shown.

#### Rules for Endurance Testing

For evaluation of Test Structure D1, the following rule shall be applicable to Test 5, "Endurance Testing" specified in Table 8, Para 3.2.6.

#### Thick Film Resistor - Voltage Divider

Load: 3 W, maximum 7500 V d.c.; Load Cycle: 90 minutes on, 30 minutes off.

FIGURE 11 - TEST STRUCTURE D1 - HIGH-VOLTAGE HYBRID CIRCUITS

46

47

#### 3.2.6 Evaluation Test Plans

Testing, analysis of test results and presentation of the evaluation test programme shall be in accordance with the test plan and tables specified herein for each test structure. All structures and devices submitted to testing shall be clearly identified by serial numbers.

Upon completion of testing, all devices, test and inspection results, including a summary of all failure analysis results, shall be submitted to ESA. All measurements shall be recorded.

If verification of measuring equipment is required, the control devices shall serve for reference purposes.

If termination and/or area identification numbers differ from those referenced in this specification, the manufacturer shall provide ESA with a cross-reference table.

The following test plans are applicable to the test structures specified in Table 7.

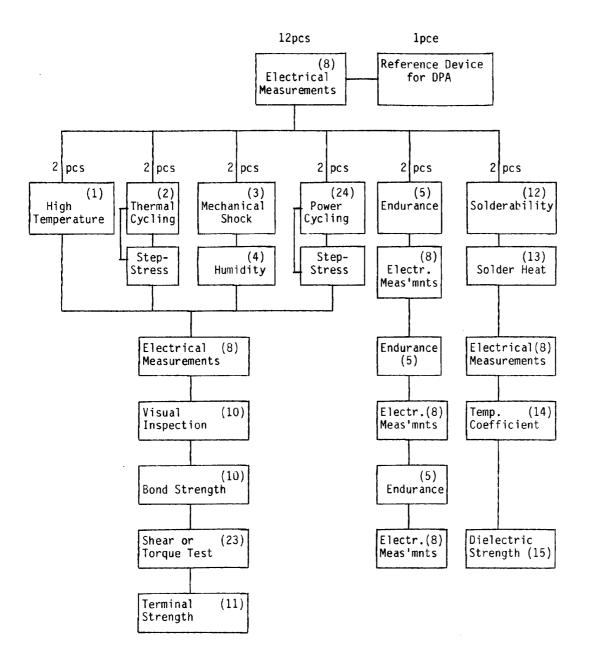

NOTE: Numbers in parentheses refer to test numbers of Table 8.

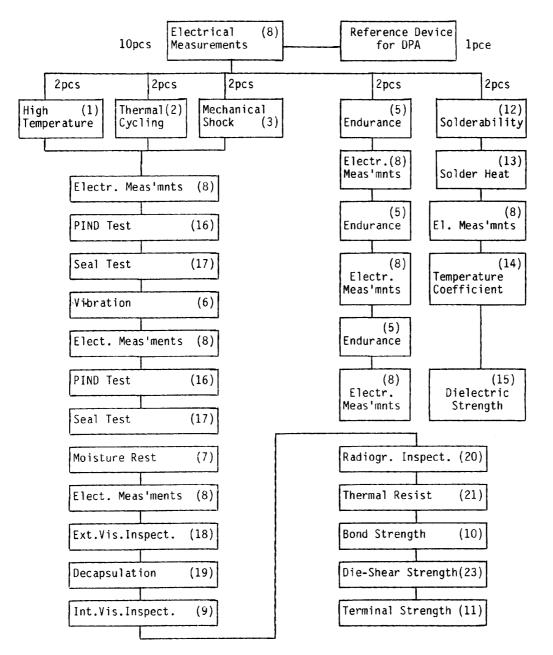

FIGURE 12 - TEST PLAN 1

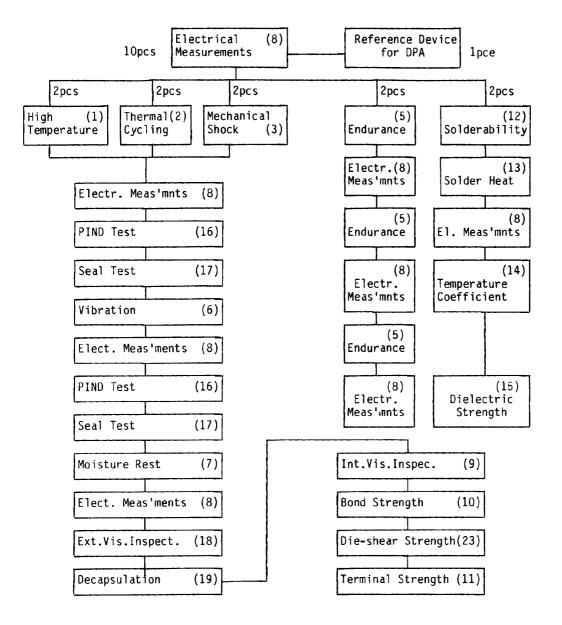

NOTE: Numbers in parentheses refer to test numbers in Table 8.

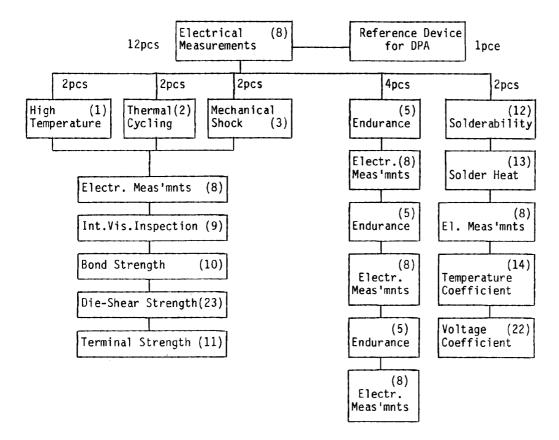

FIGURE 13 - TEST PLAN 2

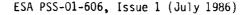

NOTE: Numbers in parentheses refer to test numbers of Table 8.

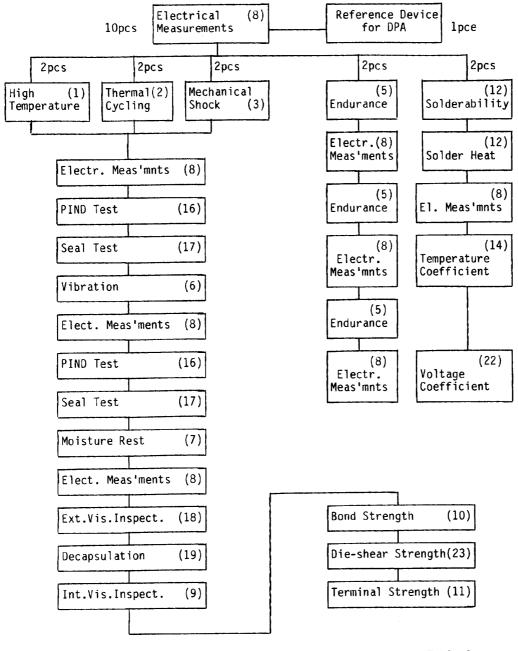

FIGURE 14 - TEST PLAN 3

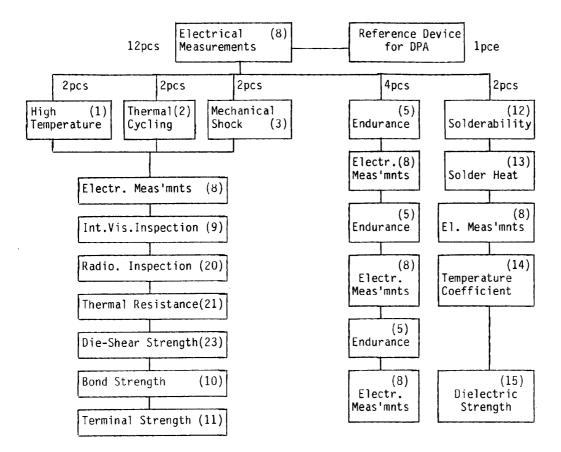

$\underline{\text{NOTE}}$ : Numbers in parentheses refer to test numbers of Table 8.

FIGURE 15 - TEST PLAN 4

NOTE: Numbers in parentheses refer to test numbers of Table 8.

FIGURE 16 - TEST PLAN 5

<u>NOTE</u>: Numbers in parentheses refer to test numbers of Table 8. FIGURE 17 - TEST PLAN 6

54

ESA PSS-01-606, Issue 1 (July 1986)

# 3.2.7 Description of Tests

The test procedures pertinent to Test Plans 1 to 6 inclusive are listed in Table 8 together with reference to the applicable MIL specifications. The number of each test corresponds to that shown in the test plans.

Table 8 shall be used in conjunction with the supplementary test instructions specified for each of the individual test structures listed in Para 3.2.4.

| []  |                               |                |      |                                                                                                                                                                                                                    |

|-----|-------------------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Test                          | MIL-STD/Method |      | Test Conditions and Remarks                                                                                                                                                                                        |

| 1   | High Temperature<br>Storage   | 883            | 1008 | Condition 'B': +125° C; 2000 hours.                                                                                                                                                                                |

| 2   | Thermal Cycling               | 883            | 1010 | Condition 'B', 100 cycles per step<br>up to 500 cycles or failure                                                                                                                                                  |

| 3   | Mechanical Shock              | 883            | 2002 | Condition 'C', as per detail spec.                                                                                                                                                                                 |

| 4   | Humidity                      | 202            | 103B | Duration 2000 hours, no voltage                                                                                                                                                                                    |

| 5   | Endurance                     | 202            | 108A | Temperature: +125° C, Condition 'F'<br>2000 hours. Electrical load as<br>specified in relevant test structure                                                                                                      |

| 6   | Vibration                     | 883            | 2007 | Condition 'B', 50g. Test item shall<br>be glued to the vibration fixture                                                                                                                                           |

| 7   | Moisture Resistance           | 883            | 1004 | 10V d.c. between all terminals con-<br>nected together and package;<br>+ on terminals                                                                                                                              |

| 8   | Electrical Measure-<br>ments  | 202            |      |                                                                                                                                                                                                                    |

|     | - Resistance                  |                | 303  | Test accuracy: ± 0.05%. Printed<br>Resistors                                                                                                                                                                       |

|     | - Capacitance                 |                | 305  | F = 1 MHz; Test accuracy on<br>C = ± 0.1%. Registration of loss<br>factor down to 0.001. Printed<br>Capacitors and Chips                                                                                           |

|     | - Insulation<br>Resistance    |                | 302  | Condition 'A', 100V. The test items<br>are the same as specified for<br>Test 15, "Dielectric Strength"                                                                                                             |

|     | - Semiconductor<br>Components |                |      | Functional test. Electrical opera-<br>tional conditions shall be normal<br>ones for component concerned. To be<br>specified after joint agreement by<br>ESA and manufacturer.<br>For test points, see Para 3.4.3.1 |

| TA | BL | E | 8 | - | TEST | PROCEDURES | , |

|----|----|---|---|---|------|------------|---|

|----|----|---|---|---|------|------------|---|

TABLE 8 continued on next page.

3

•

•

.

| No. | Test                                                   | MIL-STD/Method |      | Test Conditions and Remarks                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------------------------------------------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | Internal Visual<br>Inspection                          | 883            | 2017 | Not applicable to hermetically seal-<br>ed semiconductor components attached<br>to substrate                                                                                                                                                                                                                                                                                                                                         |

| 10  | Bond Strength                                          | 883            | 2011 | Wire-bonds: Test Condition 'D'                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11  | Terminal Strength                                      | 883            | 2044 | $\begin{array}{l} \hline Flexible lead; soldered to\\ \hline Thick Film\\ \hline Condition 'A'; Force = 30 x Q\\ (Newton); Q = lead (mm^2)\\ \hline Flexible and Semi-flexible Leads in\\ \hline Packages\\ \hline As above.\\ \hline Rigid Feed-throughs in Packages\\ \hline D \leqslant 1 mm: as above.\\ \hline Rigid Feed-throughs in Packages\\ \hline D > 1 mm: Condition 'C1;\\ \hline Torque 1.5 N.cm\\ \hline \end{array}$ |

| 12  | Solderability<br>(Ext. termination)                    | 202            | 208  | Three terminals per test item                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13  | Soldering Heat<br>(Ext. termination)                   | 202            | 210  | Condition 'B'. Three terminals per<br>test item. Visual inspection by<br>microscope (Magnification X4) to<br>verify that terminals, glass seals,<br>connection to thick film substrate<br>or substrate itself are not damaged.                                                                                                                                                                                                       |

| 14  | Temperature Co-<br>efficient (of<br>printed resistors) | 202            | 304  | Maximum temperature: +125°C;<br>Minimum ": -55°C                                                                                                                                                                                                                                                                                                                                                                                     |

| 15  | Dielectric Strength                                    | 202            | 301  | Test Voltages<br>Thick film pattern (all terminals<br>connected together) to plate on<br>reverse side of substrate, to base-<br>plate or package: 200V d.c.<br>Printed capacitors, cross-overs and<br>between layers in multilayer system:<br>100V d.c.                                                                                                                                                                              |

| 16  | Particle Impact<br>Noise Detection<br>(PIND)           | 883            | 2020 | Condition A                                                                                                                                                                                                                                                                                                                                                                                                                          |

TABLE 8 - TEST PROCEDURES (Continued)

TABLE 8 continued on next page.

| π | JRES (Continued)                                                                                                                               |

|---|------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Test Conditions and Remarks                                                                                                                    |

|   | Step 1: Condition A1 or A2;<br>Step 2: Packages with lids of 3<br>and less: Condition C2;<br>Packages with lids of 3<br>and more: Condition C1 |

TABLE 8 - TEST PROCEDU

| No. | Test                          | MIL-STD/Method   |                            | Test Conditions and Remarks                                                                                                                                                                                                                                               |

|-----|-------------------------------|------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17  | Seal Test                     | 883              | 1014                       | Step 1: Condition A1 or A2;<br>Step 2: Packages with lids of 3 cm <sup>2</sup><br>and less: Condition C2;<br>Packages with lids of 3 cm <sup>2</sup><br>and more: Condition C1                                                                                            |

| 18  | External Visual<br>Inspection | 883              | 2009                       |                                                                                                                                                                                                                                                                           |

| 19  | Decapsulation                 | Lid sl<br>packag | nall be rem<br>ge is not c | oved in such a way that interior of<br>ontaminated                                                                                                                                                                                                                        |

| 20  | Radiographic<br>Inspection    | 883              | 2012                       |                                                                                                                                                                                                                                                                           |

| 21  | Thermal Resistance            | 883              | 1012                       | Test Structure C1 only<br>The thermal resistances of the<br>- Thick Film Resistors,<br>- Semiconductor Chips,<br>- High Current Conductor<br>are to be determined.<br>The temperatures on internal con-<br>nection strips and package feed-<br>throughs shall be measured |

| 22  | Voltage Coefficient           | 202              | 309                        | During endurance testing, test<br>voltage corresponds to load voltage<br>(see Test 5)                                                                                                                                                                                     |

| 23  | Die-shear Strength            | 883              | 2019                       | Shall be performed also on chip capa-<br>citors, chip resistors and leadless<br>chip carriers attached to the sub-<br>strate. Alternatively, torque test<br>may be performed on leadless chip<br>carriers                                                                 |

| 24  | Power Cycling                 | -                | -                          | All components to be powered at<br>nominal power dissipation level.<br>Power shall be switched on and off<br>500 times (cycles). Lapse time for<br>each cycle shall be 3x time constant.<br>Power shall be increased in steps up<br>to failure.                           |

58

ESA PSS-01-606, Issue 1 (July 1986)

# 3.2.8 Detail Specifications of Test Structures

The manufacturer shall write a detail specification of each test structure to be evaluated. Each specification shall contain tables of the detailed electrical measurements to be performed before and after exposure to environmental tests. The following details shall be stated:

# a) Line-printing quality

Statement of minimum line-width and line-distance.

# b) Thick Film Resistors

| Manufacturing tolerance<br>Maximum change during test          |    | ± 20% (untrimmed), ± 1% (trimmed);<br>± 2%; |

|----------------------------------------------------------------|----|---------------------------------------------|

| Maximum temperature coefficien<br>calculated for any range be- | nt |                                             |

| tween two test temperatures                                    | :  | As specified by the manufacturer;           |

| Maximum voltage coefficient                                    | :  | As specified by the manufacturer;           |

| Visual Inspection                                              | :  | As per MIL-STD-883.                         |

c) Capacitors, Thick Film, Printed

| Manufacturing tolerance       | : | ± 20%;                   |

|-------------------------------|---|--------------------------|

| Maximum change during test    | : | ± 2%;                    |

| Maximum change of loss factor | : | 1.5 x initial value;     |

| during test                   |   |                          |

| Insulation resistance         | : | $10^{10}\Omega$ minimum; |

| Dielectric strength           | : | As per MIL-STD-202;      |

| Visual Inspection             | : | As per MIL-STD-883.      |

Downloaded from http://www.everyspec.com

ESA PSS-01-606, Issue 1 (July 1986)

5**9**

# d) Capacitors, Attached Chips

Maximum loss factor:As specified by chip manufacturer;Maximum change of loss factorduring test:1.5 x initial value;Insulation resistance:10<sup>10</sup> minimum;Dielectric strength:As per MIL-STD-202;Bond strength:As per MIL-STD-883;Visual inspection:As per MIL-STD-883.

# e) Printed Cross-overs and Multilayer Systems

| Insulation resistance | : 10 <sup>10</sup> Ωminimum; |

|-----------------------|------------------------------|

| Dielectric strength   | : As per MIL-STD-202;        |

| Visual inspection     | : As per MIL-STD-883.        |

# f) Semiconductors, Attached

| Electrical functional test | : | Test limit to be agreed jointly by |

|----------------------------|---|------------------------------------|

|                            |   | manufacturer and ESA;              |

| Bond strength              | : | As per MIL-STD-883;                |

| Visual inspection          | : | As per MIL-STD-883.                |

# g) Wire Cross-overs, Internal Connections

| Bond strength     | : | As per MIL-STD-883; |

|-------------------|---|---------------------|

| Visual inspection | : | - ditto -           |

# h) External Connections and Leads

| Terminal strength | : | - ditto -           |

|-------------------|---|---------------------|

| Visual inspection | : | - ditto -           |

| Solderability     | : | As per MIL-STD-202; |

| Soldering heat    | : | - ditto -           |

1

4

.

.

# i) Assembly and Package

| Internal visual inspection | : | As per MIL-STD-883 |

|----------------------------|---|--------------------|

| External visual inspection | : | - ditto -          |

| PIND test                  | : | - ditto -          |

| Seal test                  | : | - ditto -          |

| Radiographic inspection    | : | - ditto -          |

# j) Thermal Characteristics of High Power Structures

Thermal resistance to heat sink of:

| Each thick film resistor<br>Semiconductor chip | :<br>: |                                                           |

|------------------------------------------------|--------|-----------------------------------------------------------|

|                                                |        | connections.                                              |

| Temperature of connection<br>leads             |        | Maximum 100° C for welded or wire-<br>bonded connections. |

(\*)  $\mbox{cm}^2$  area of thick film resistor or semiconductor chip.

| k) | Structures with Base-plate                    |   |                                                                                                              |

|----|-----------------------------------------------|---|--------------------------------------------------------------------------------------------------------------|

|    | Visual inspection                             | : | As per MIL-STD-883;                                                                                          |

|    | Radiographic inspection<br>(power structures) | : | Area of void(s) under dissipative<br>source shall not be more than 25%<br>of the area of that source.        |

|    |                                               |   | Total void area (sum of all voids<br>at substrate/base-plate interface)<br>shall not exceed 25% of substrate |

|    | Insulation resistance                         | : | area.<br>Minimum 10 <sup>10</sup> Ω.                                                                         |

60

61

#### 3.2.9 Failure Analysis

All failed items shall be subjected to failure analysis. The applied procedure shall enable determination of the cause of failure, failure mode and any corrective action required. A detailed test report of all failed items shall be submitted to ESA.

# 3.3 EVALUATION REPORT

The manufacturer shall produce an Evaluation Report in compliance with this specification and signed on behalf of the company.

#### 3.3.1 Analysis of Results

At the end of the Evaluation Phase, ESA will analyse the results of:

- Line survey,

- Evaluation testing.

Based on the outcome of this review, ESA will decide whether the manufacturer may proceed to the next phase of the programme or whether any corrective actions are required.

#### 3.3.2 Corrective Actions

ESA may recommend certain modifications in the manufacturer's organisation, the production line and/or processes. If the manufacturer wishes to proceed to the next phase, he shall implement such modifications.

If major changes are deemed necessary, ESA may require repetition of certain evaluation tests and/or re-evaluation of test results.

62

ESA PSS-01-606, Issue 1 (July 1986)

3.3.3 Process Identification Document (PID)

The manufacturer shall establish a PID, specifying the agreed procedures for manufacturing control. Details of the contents of the PID are given in Para 4.2.

3.4 COMPLETION OF EVALUATION PHASE

Upon satisfactory completion of the Evaluation Phase, ESA will agree the definition of the manufacturer's capabilities and give its consent to proceed to capability approval testing.

63

#### 4. CAPABILITY APPROVAL TESTING PHASE

4.1 GENERAL

The Capability Approval Testing Phase shall cover all tests approved by ESA upon completion of the Evalution Phase and consist of:

- the freezing of the processes, process and inspection documents, and materials defined in the Process Identification Document (PID) and

- the manufacture and testing of either test structures or actual circuit types.

#### 4.2 PROCESS IDENTIFICATION DOCUMENT (PID)

Prior to the manufacture of the test structures to be subjected to testing, the manufacturer shall prepare the PID and agree its contents with ESA. The PID shall be divided into sections according to the following guidelines referencing each process to be applied:

#### Section 1

- Cover page, showing title of PID, issue number and date, and if applicable - revision letter and date;

- Revision list, showing revised pages and dates of revision,

- List of contents, showing PID sections.

## Section 2